#### US011616841B2

## (12) United States Patent

Tutuianu et al.

# (54) REMOTE MAPPING OF CIRCUIT SPEED VARIATION DUE TO PROCESS, VOLTAGE AND TEMPERATURE USING A NETWORK OF DIGITAL SENSORS

(71) Applicant: Taiwan Semiconductor

Manufacturing Company Limited,

Hsinchu (TW)

(72) Inventors: Bogdan Tutuianu, The Hills, TX (US);

Osamu Takahashi, Round Rock, TX

(US)

(73) Assignee: Taiwan Semiconductor

Manufacturing Company Limited,

Hsinchu (TW)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 306 days.

(21) Appl. No.: 16/784,482

(22) Filed: Feb. 7, 2020

#### (65) Prior Publication Data

US 2021/0250405 A1 Aug. 12, 2021

(51) **Int. Cl.**

| H04L 67/12 | (2022.01) |

|------------|-----------|

| G01R 31/28 | (2006.01) |

| G01K 1/02  | (2021.01) |

| G01R 31/14 | (2006.01) |

| G01K 3/14  | (2006.01) |

(52) U.S. Cl.

CPC ...... *H04L 67/12* (2013.01); *G01R 31/14* (2013.01); *G01R 31/2874* (2013.01); *G01K* 1/026 (2013.01); *G01K 2003/145* (2013.01); *G01K 2213/00* (2013.01)

## (10) Patent No.: US 11,616,841 B2

(45) Date of Patent: Mar. 28, 2023

#### (58) Field of Classification Search

None

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 7,086,058    | B2         | 8/2006  | Luick             |           |

|--------------|------------|---------|-------------------|-----------|

| 10,132,695   | B2         | 11/2018 | Leighton, II      |           |

| 10,747,258   | B1*        | 8/2020  | Freund            | G06F 1/12 |

| 2004/0037346 | <b>A</b> 1 | 2/2004  | Rusu et al.       |           |

| 2006/0161373 | A1         | 7/2006  | Mangrulkar et al. |           |

| (Continued)  |            |         |                   |           |

#### FOREIGN PATENT DOCUMENTS

| EP | 3506548 A1    | 7/2019      |  |

|----|---------------|-------------|--|

| KR | 20180034528 A | 4/2018      |  |

|    | (Conti        | (Continued) |  |

Primary Examiner — Brent A. Fairbanks

(74) Attorney, Agent, or Firm — The Marbury Law Group, PLLC

### (57) ABSTRACT

A digital sensor network is overlaid on an integrated circuit for identifying and mapping hotspots in the integrated circuit. The digital sensor network may include a plurality of digital sensors distributed within an area of an integrated circuit component of an integrated circuit. Each of the plurality of digital sensors may include a ring oscillator and may be configured to output a counter value of a ring oscillator counted over a designated period. A sensor network control unit may be provided that is communicatively connected to the plurality of digital sensors via a communication circuit. The sensor network control unit may be configured to receive a plurality of counter values including the counter value from each of the plurality of digital sensors and identify a hotspot within the area of the integrated circuit.

#### 20 Claims, 10 Drawing Sheets

#### **References Cited** (56)

#### U.S. PATENT DOCUMENTS

| 2006/0238267 A1* | 10/2006 | Bienek H01L 23/34        |

|------------------|---------|--------------------------|

|                  |         | 374/E7.042               |

| 2008/0002757 A1* | 1/2008  | Kosta G01K 7/425         |

|                  |         | 374/170                  |

| 2008/0205110 A1  | 8/2008  | Boeve                    |

| 2011/0191776 A1* | 8/2011  | Bose G06F 9/46           |

|                  |         | 718/102                  |

| 2012/0096288 A1  | 4/2012  | Bates et al.             |

| 2013/0278241 A1  | 10/2013 | Chen et al.              |

| 2017/0074729 A1* | 3/2017  | Coutts G06F 1/206        |

| 2017/0089769 A1* | 3/2017  | Krishnaswamy G01K 15/005 |

| 2017/0199089 A1* | 7/2017  | Fritchman                |

| 2018/0073933 A1* | 3/2018  | Keskin G06F 1/206        |

| 2018/0143862 A1* | 5/2018  | Saeidi G06F 9/5044       |

| 2019/0317547 A1  | 10/2019 | Savoj et al.             |

#### FOREIGN PATENT DOCUMENTS

| TW | 200533928 A | 10/2005 |

|----|-------------|---------|

| TW | 201122498 A | 7/2011  |

| TW | 201333500 A | 8/2013  |

| TW | 201337277 A | 9/2013  |

| TW | 201842348 A | 12/2018 |

| TW | 201939048 A | 10/2019 |

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2

FIG. 4

FIG. 5

Mar. 28, 2023

FIG. 6A

FIG. 6B

Mar. 28, 2023

FIG. 6C

FIG. 6D

FIG. 7

FIG. 8

## REMOTE MAPPING OF CIRCUIT SPEED VARIATION DUE TO PROCESS, VOLTAGE AND TEMPERATURE USING A NETWORK OF DIGITAL SENSORS

#### BACKGROUND

The electronic circuits operating contemporary electronic device have become incredibly powerful. The circuits often are capable of performing a large number of calculations per 10 second enabling sophisticated functionality and applications. However, these circuits operate, the circuits demand more voltage and/or current to power their operations. As the current demands increases, the temperature of the circuit (due to the increased current across the resistance) increases. 15 As the temperature of the circuit increases, the overall performance of the circuit may degrade. Therefore, the monitoring of the temperature of a circuit may be useful. When a temperature of a circuit is determined to rise above certain thresholds, steps may be taken to offload certain 20 functions and/or calculations from particular circuits that may be approaching or over threshold temperatures so that the circuit may properly cool off.

Traditional process, voltage and temperature on-chip monitoring is done with very accurate analog circuits that 25 are very large, require their own power supply and can be placed sparsely on the chip. Due to the size, power requirements, voltage or temperature sensors are often placed far from the critical circuits and cannot be used to directly measure the speed, voltage or temperature inside the critical 30 areas.

#### BRIEF DESCRIPTION OF THE DRAWINGS

herein and constitute part of this specification, illustrate example embodiments of various embodiments, and together with the general description given above and the detailed description given below, serve to explain the features of the claims. Aspects of the present disclosure are best 40 understood from the following detailed description when read with the accompanying figures. It is noted that, in accordance with the standard practice in the industry, various features are not drawn to scale. In fact, the dimensions of the various features may be arbitrarily increased or 45 reduced for clarity of discussion.

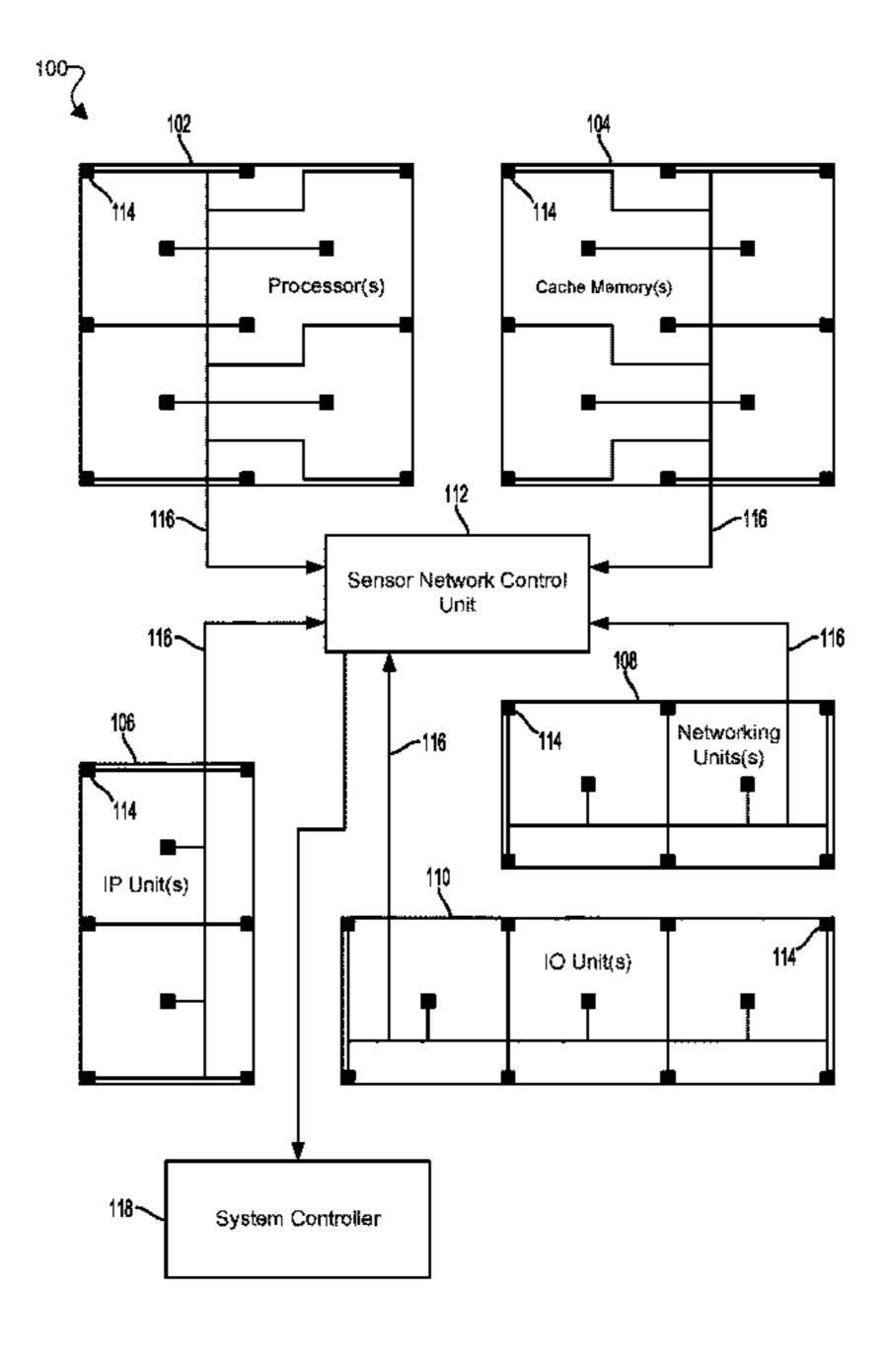

- FIG. 1 is a component block diagram illustrating an example digital sensor network on an integrated circuit for implementing various embodiments.

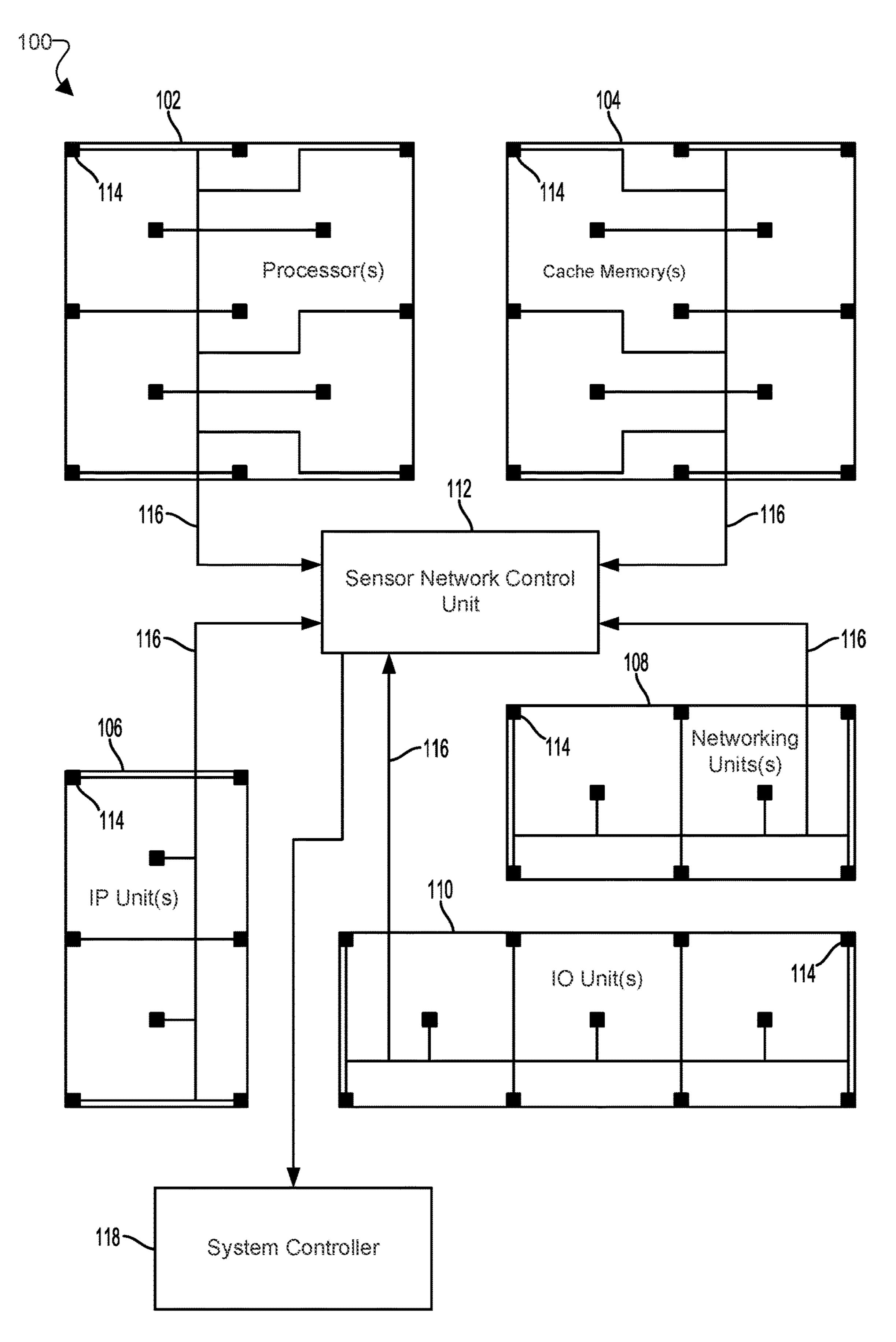

- FIG. 2 is a component block diagram illustrating an 50 example digital sensor suitable for implementing various embodiments.

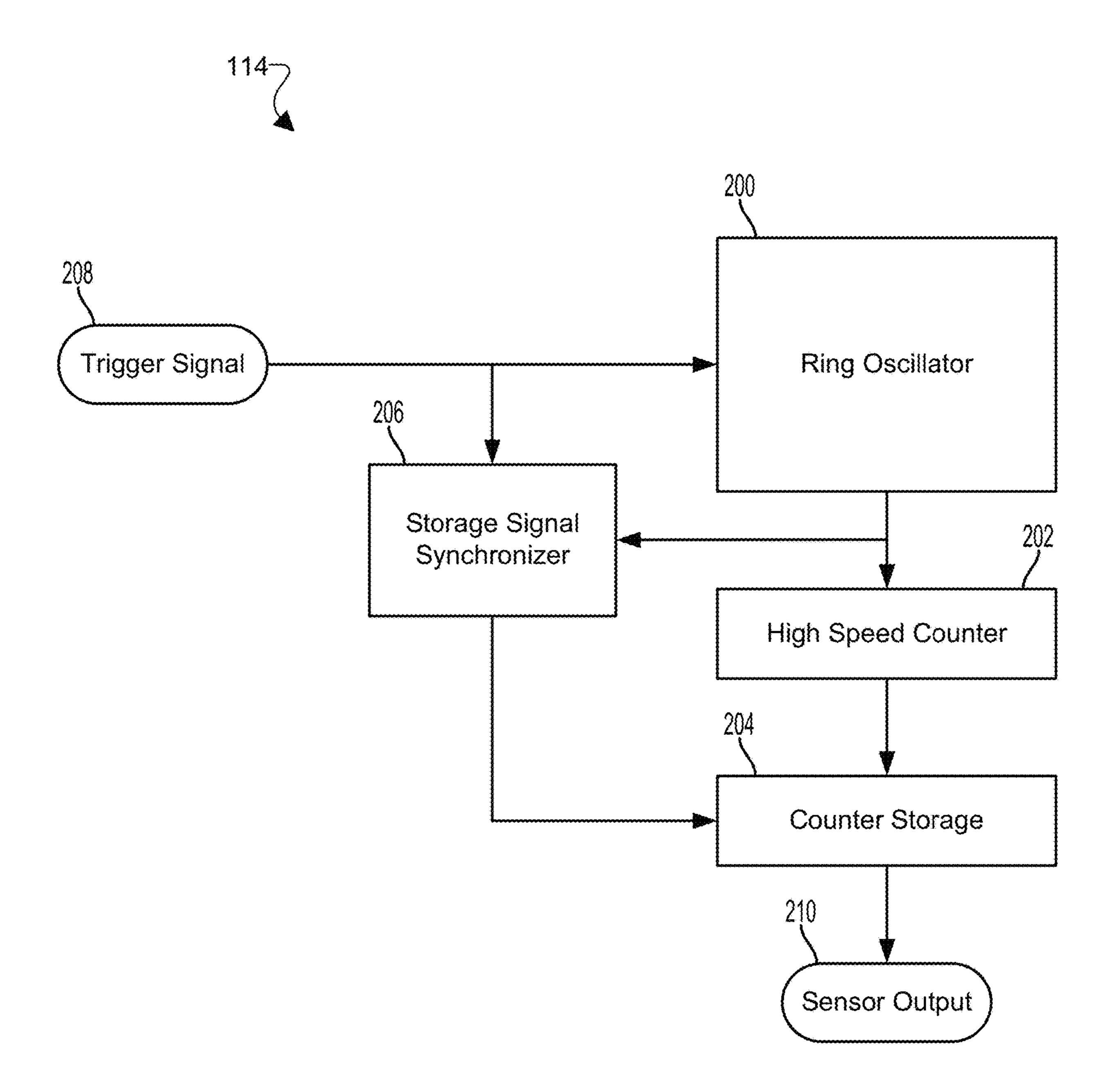

- FIG. 3 is a process flow diagram illustrating a method for sensing an environmental condition at a digital sensor according to an embodiment.

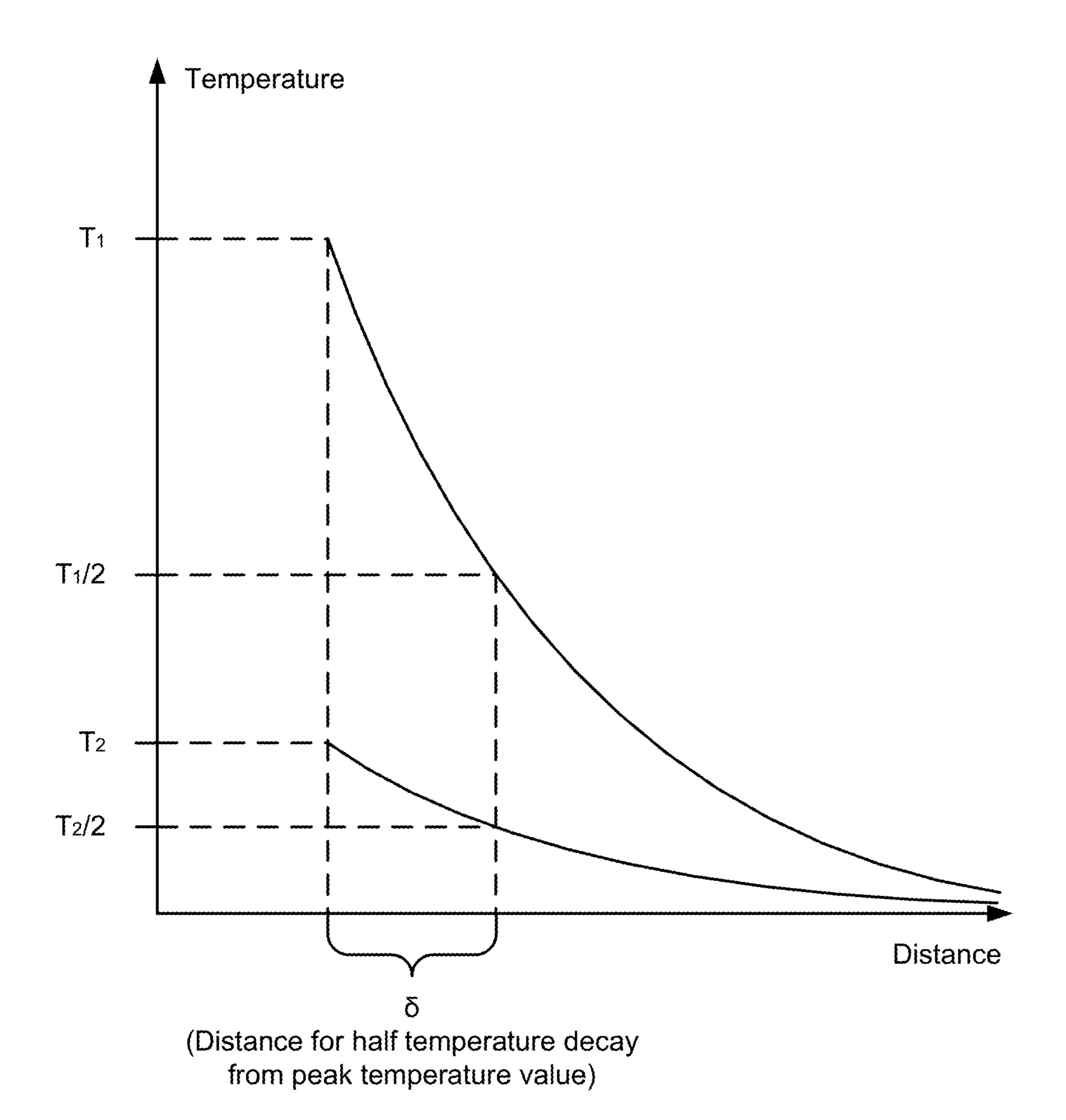

- FIG. 4 is a graph diagram illustrating temperature decay on an integrated circuit.

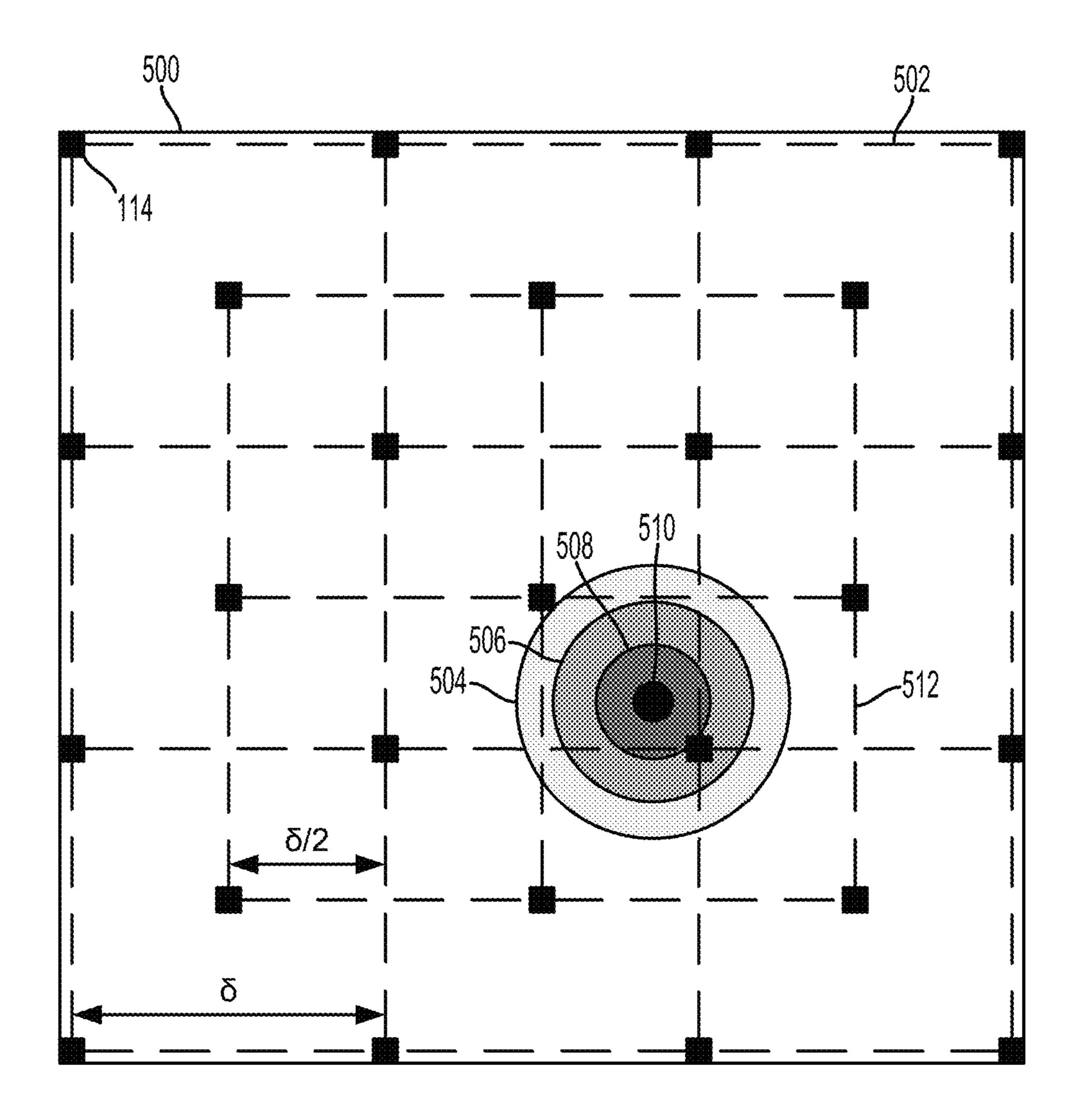

- FIG. 5 is a component block diagram illustrating an example digital sensor network on an integrated circuit suitable for implementing various embodiments.

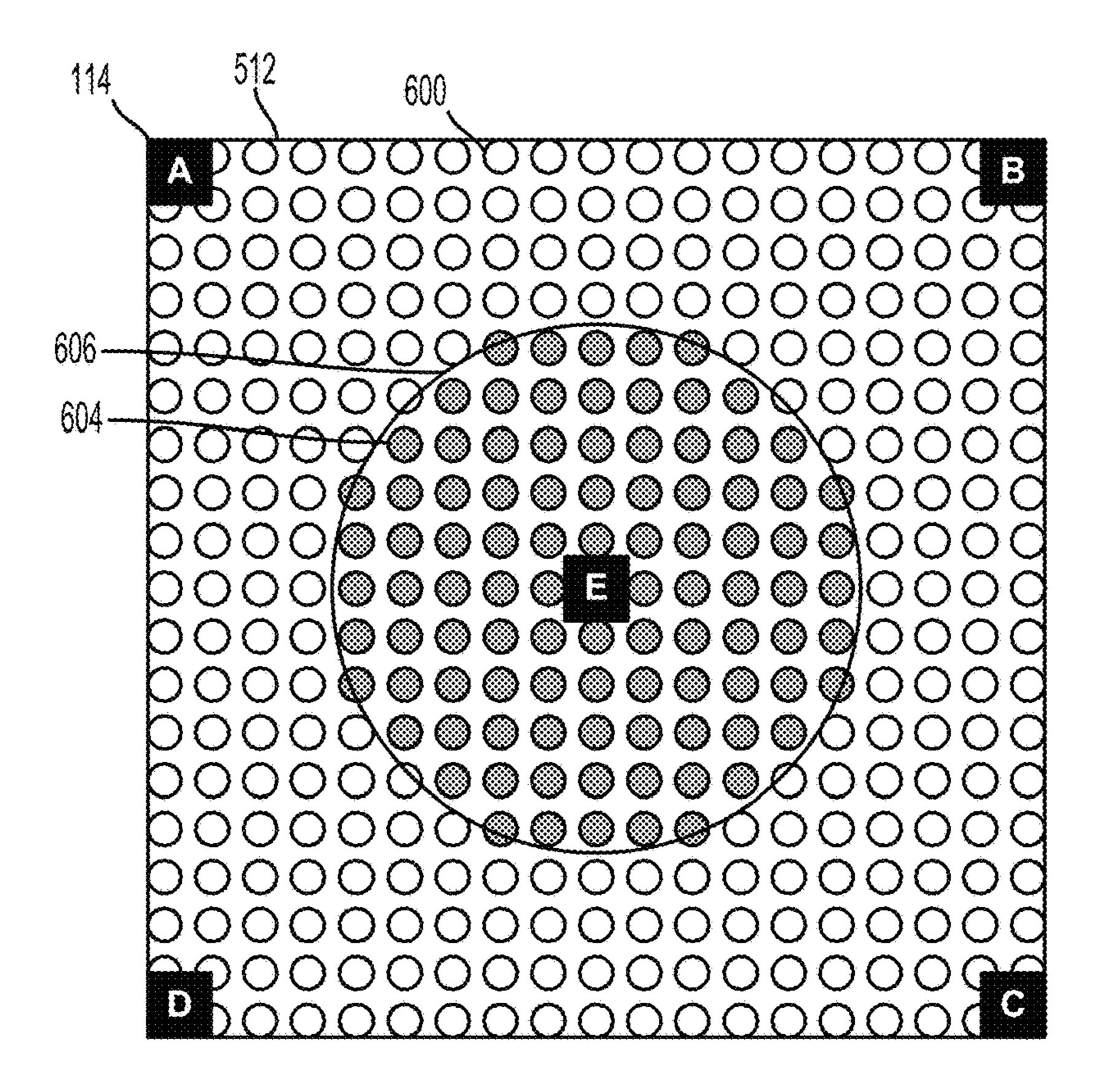

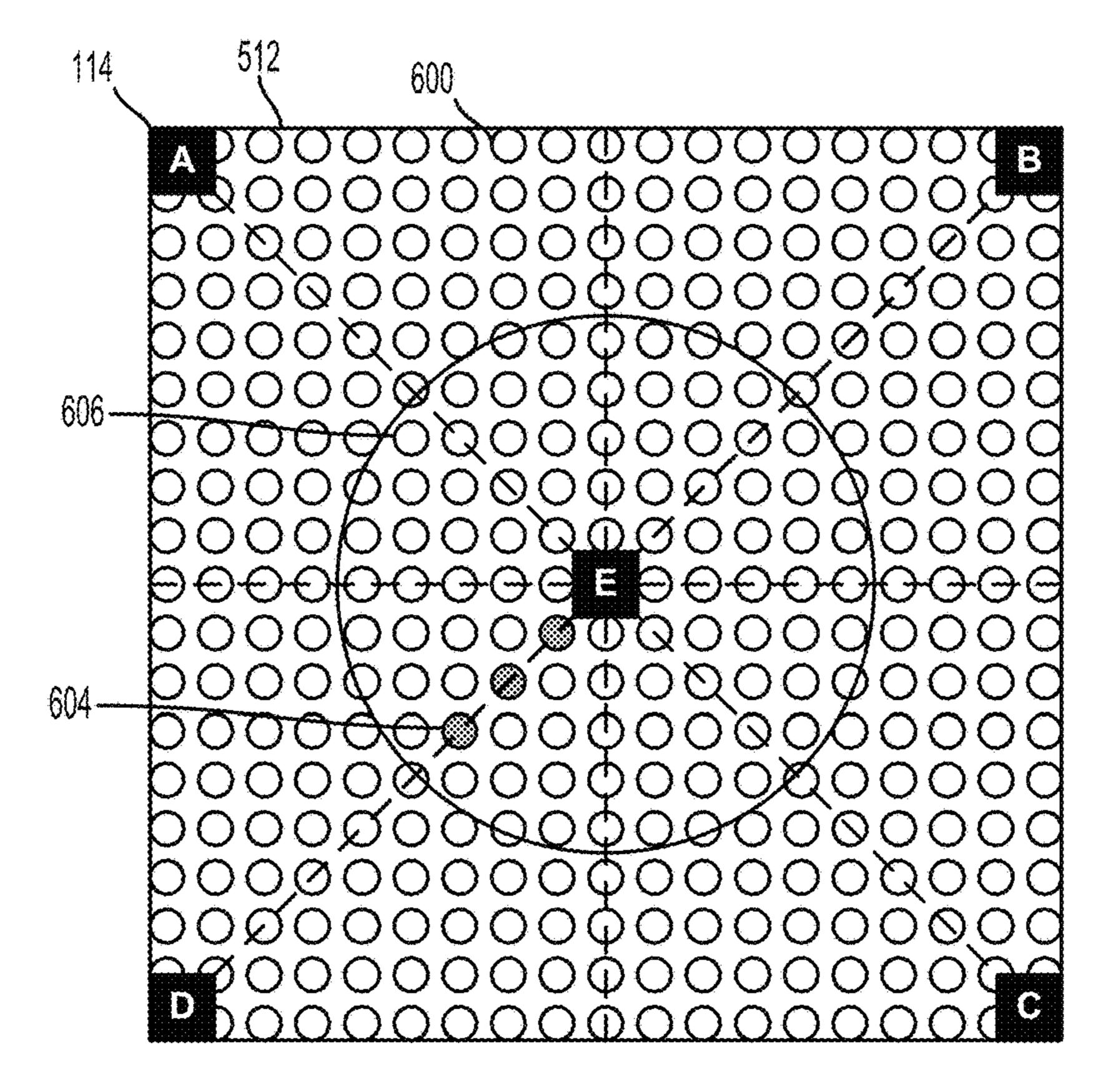

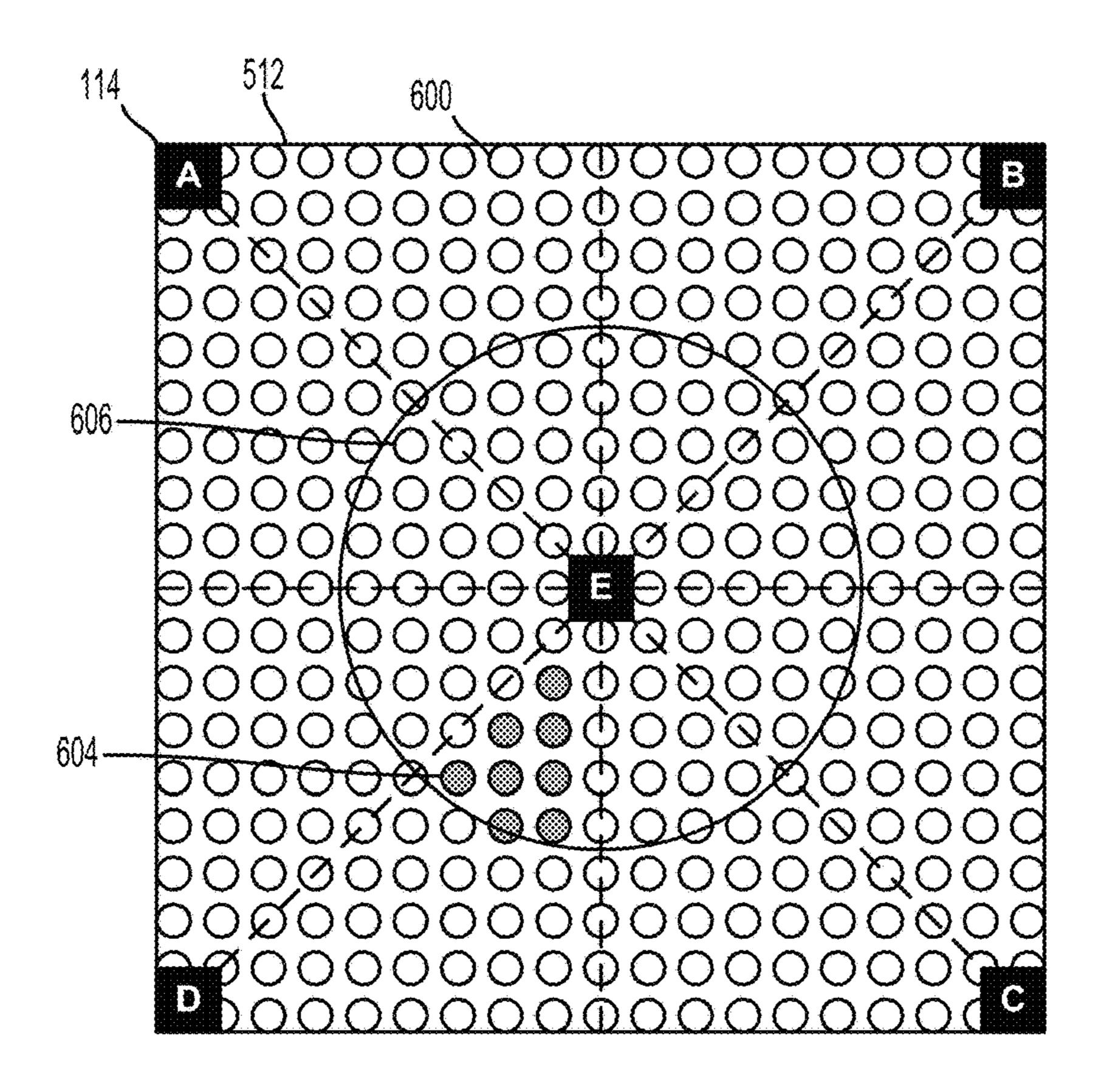

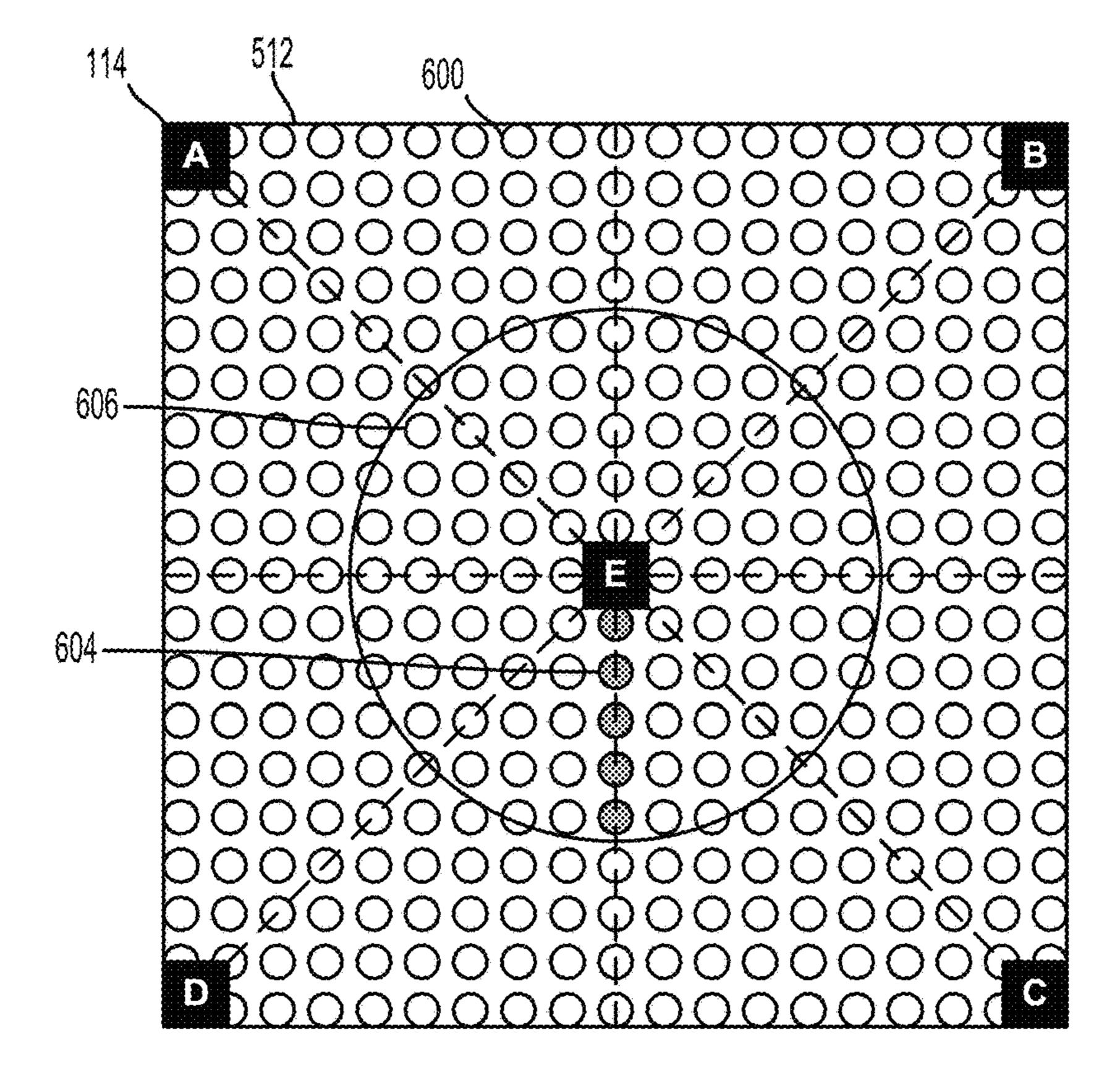

- FIGS. 6A-6D are a component block diagrams illustrating examples of a critical tile of a digital sensor network on an integrated circuit suitable for implementing various embodiments.

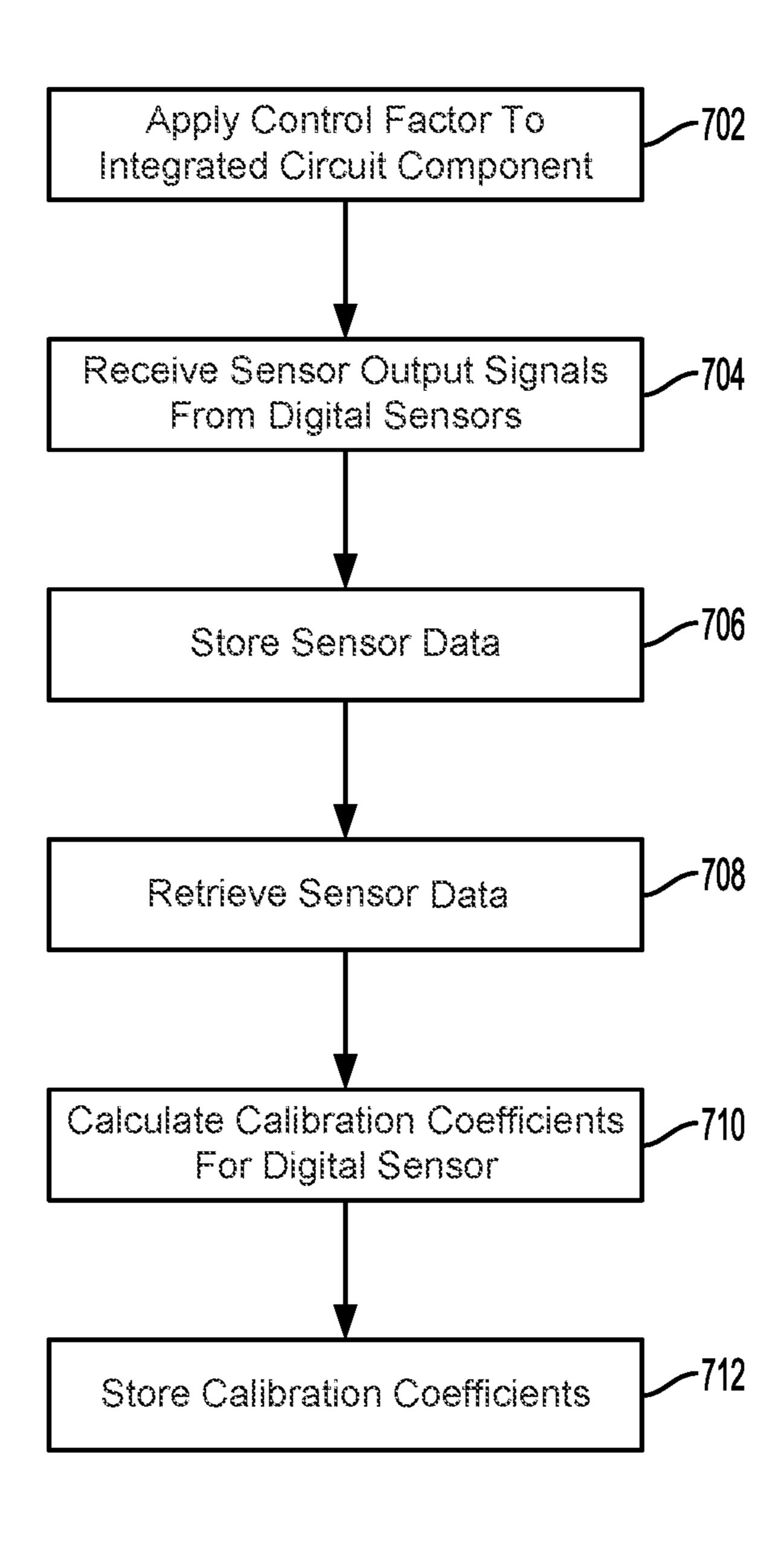

- FIG. 7 is a process flow diagram illustrating a method for 65 self-calibration of a sensor network control unit according to an embodiment.

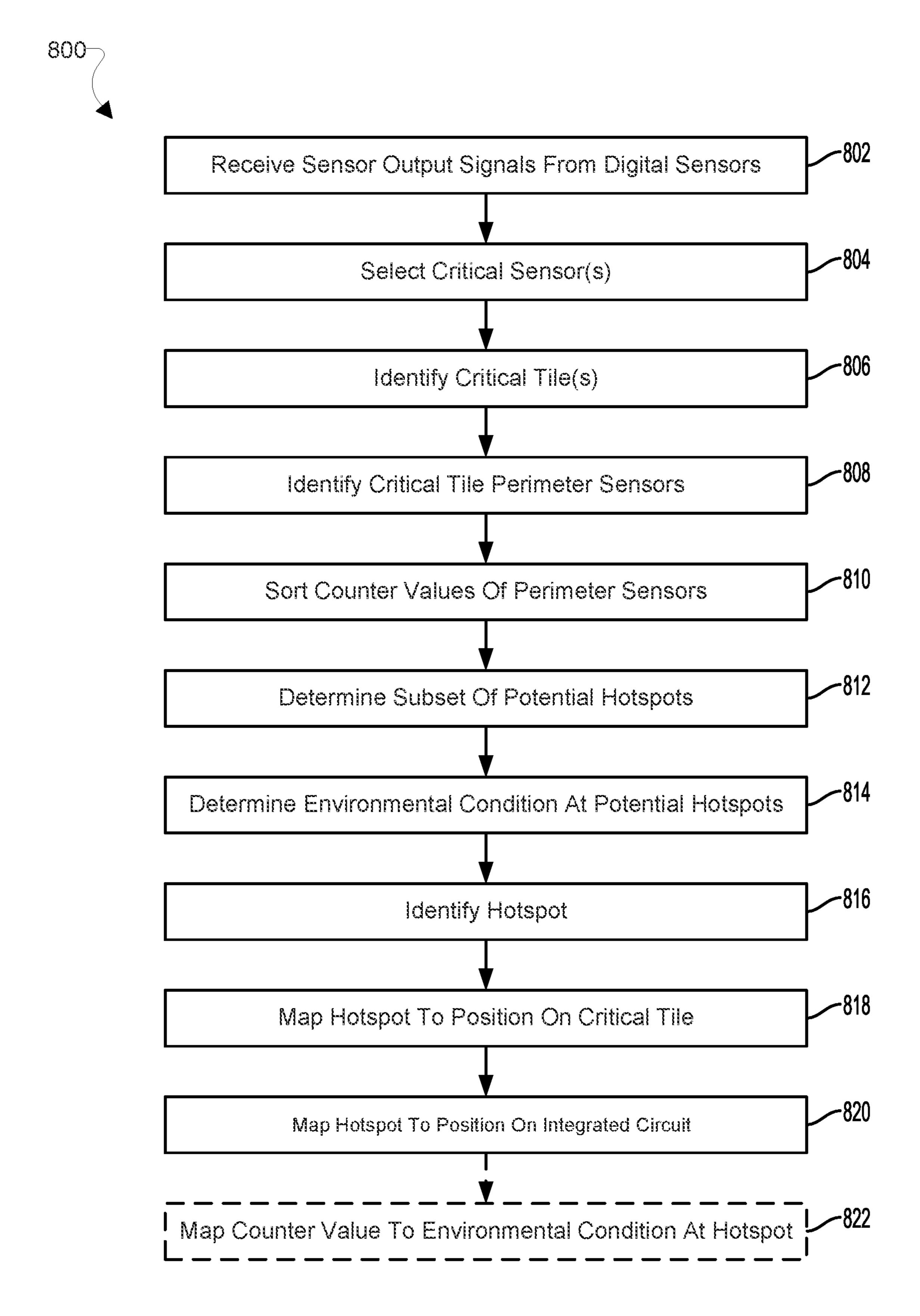

- FIG. 8 is a process flow diagram illustrating a method for identifying and mapping hotspots according to an embodiment.

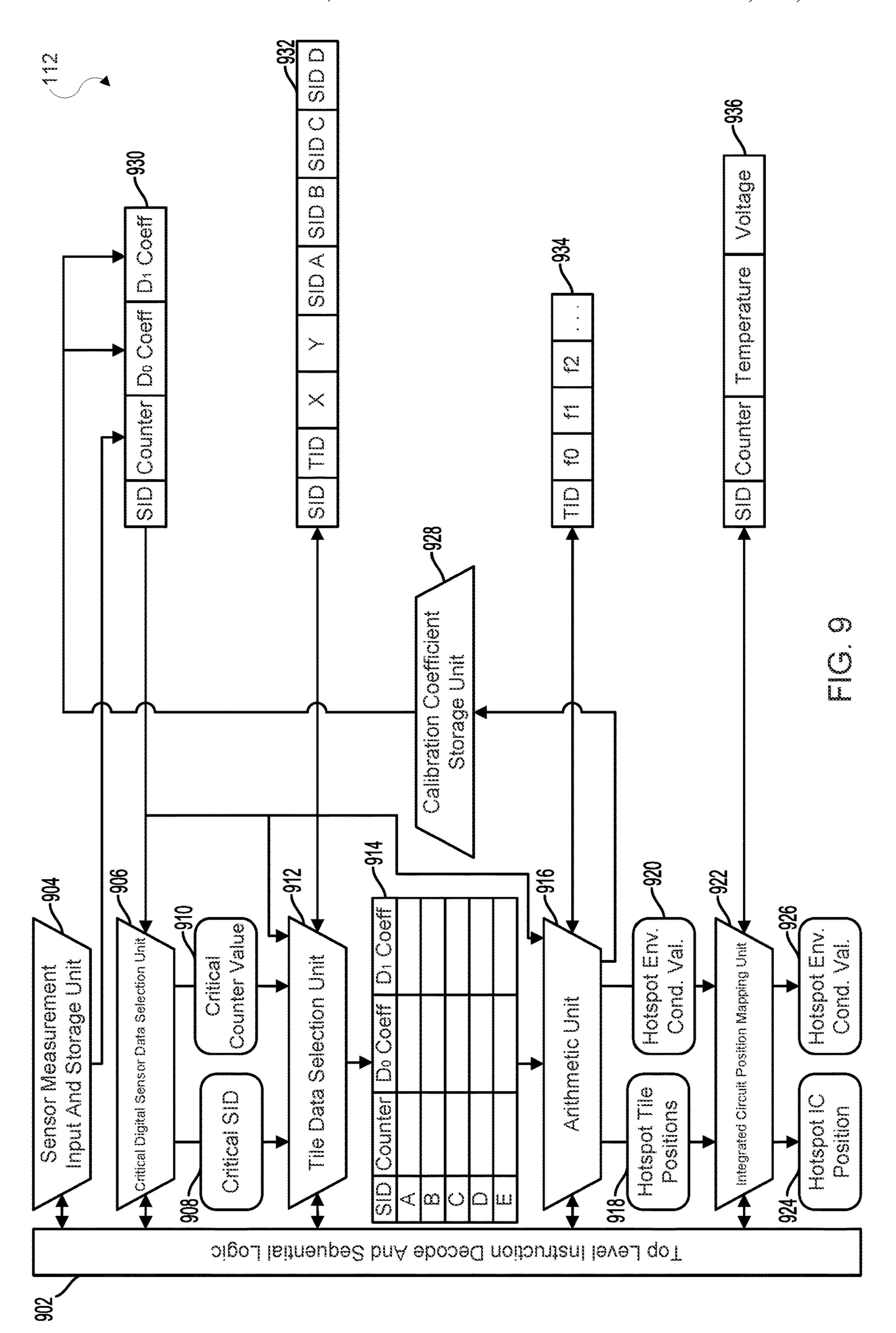

- FIG. 9 is a component block and process flow diagram illustrating an example sensor network control unit suitable for implementing various embodiments.

#### DETAILED DESCRIPTION

The following disclosure provides many different embodiments, or examples, for implementing different features of the provided subject matter. Specific examples of components and arrangements are described below to simplify the present disclosure. These are, of course, merely examples and are not intended to be limiting. The various embodiments will be described in detail with reference to the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts. References made to particular examples and implementations are for illustrative purposes, and are not intended to limit the scope of the claims.

Further, spatially relative terms, such as "beneath," "below," "lower," "above," "upper" and the like, may be used herein for ease of description to describe one element or feature's relationship to another element(s) or feature(s) as illustrated in the figures. The spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. The apparatus may be otherwise oriented (rotated 90) degrees or at other orientations) and the spatially relative descriptors used herein may likewise be interpreted accordingly.

The terms "processor," "processor core," "controller," and "control unit" are used interchangeably herein, unless The accompanying drawings, which are incorporated 35 otherwise noted, to refer to any one or all of a softwareconfigured processor, a hardware-configured processor, a general purpose processor, a dedicated purpose processor, a single-core processor, a homogeneous multi-core processor, a heterogeneous multi-core processor, a core of a multi-core processor, a microprocessor, a central processing unit (CPU), a graphics processing unit (GPU), a digital signal processor (DSP), etc., a controller, a microcontroller, a field programmable gate array (FPGA), an application-specific integrated circuit (ASIC), other programmable logic devices, discrete gate logic, transistor logic, and the like. A processor may be an integrated circuit, which may be configured such that the components of the integrated circuit reside on a single piece of semiconductor material, such as silicon.

Various embodiments may include devices, methods, and processing devices implementing such methods for remote mapping of circuit speed variation due to process, voltage, and/or temperature using a network of digital sensors. Some embodiments may include a network of digital sensors 55 distributed in a symmetrical pattern on an integrated circuit. Each digital sensor may generate and output sensor signals representing process, voltage, and/or temperature measurements at a digital sensor. Some embodiments may include a sensor network control unit receiving the sensor signals, 60 identifying a critical digital sensor of the digital sensor network and a critical tile to which the critical digital sensor belongs, determining and mapping a hotspot, a location of peak process, voltage, and/or temperature measurement, in the critical tile, and mapping the hotspot on the integrated circuit. Some embodiments may include a self-calibration process of the sensor network control unit to adjust for variations in the digital sensors.

Conventional means and methods for monitoring temperature or voltage/process speed include using large analog sensors that are too big to be placed within the actual circuits of components of an integrated circuit. Rather, the analog sensors are typically placed outside of the area of the 5 components of the integrated circuit. The size and placement of the analog sensors may impact the speed at which the analog sensors can make their measurements. Moreover, the size and placement of the analog sensors may require a separate power supply for the analog sensors. While the analog sensors are capable of making accurate measurements of temperature at the sensors, the size of the analog sensor often restricts its placement to either location remote from the circuit itself or in areas that can only allow for overall measurements of temperature of the entire component as opposed to discrete areas within subsection of the integrated circuit. Thus, adjustments in response to the measured temperature are made on the same scale as the size of the critical area. Put another way, the operations of the 20 entire components may be modified as opposed to more granular modification of subsection of the component. For similar reasons, analog sensor measurements for voltage/ process speed are generally used for bring-up and initial speed testing of the component of the integrated circuit, and 25 not used for management of the component during operation. Determinations of the adjustments to be made based on the analog sensor measurements are implemented in software, which increases the reaction time to the analog sensor measurements and is often too slow for modern integrated 30 circuits. Conventional analog sensors are typically located far from critical areas and cannot pinpoint the source of heat or voltage drop. For that reason, conventional systems and sensors assume a worst case envelope to ensure that the approaches are crude and pessimistic.

The disadvantages of analog sensors may be overcome through the use of a network of smaller, discrete, digital sensors distributed uniformly or quasi-uniformly on portions of or all of an integrated circuit. The digital sensors may be 40 small enough to be to be placed within the area of a component of the integrated circuit, providing a finer granularity of measurements of process, temperature, and/or voltage than capable with the analog sensors on the integrated circuit. The finer granularity of the digital sensors may 45 increase the accuracy of the location of the measurements of process, temperature, and/or voltage within components of the integrated circuit as compared to the measurements by an analog circuit. The digital sensors may be smaller than analog sensors, in part, because the digital sensors may not 50 need a dedicated voltage supply. While the accuracy of the digital sensors may not be as accurate as an analog sensor, the digital sensor may be orders of magnitude faster in making measurements than the corresponding analog sensors.

A sensor network control unit may interpret the measurements of the digital sensors, detect a critical area of a component of the integrated circuit, construct a local map of a temperature and/or voltage gradient in the critical area, and identify a location of a peak temperature and/or voltage in 60 the critical area and on the integrated circuit. In some embodiments, the sensor network control unit may be a hardware circuit configured to implement the functionality of the sensor network control unit. A hardware circuit based sensor network control unit may be able to use the finer 65 granularity measurements of the digital sensors to not only locate a peak temperature and/or voltage more accurately on

the integrated circuit, but also determine the measurements faster than a software for interpreting measurements of an analog circuit.

The sensor network control unit may further implement a self-calibration process that may adjust values used by the sensor network control unit operations to account for variations in the digital sensors. Such variations in the digital sensors may be the result of manufacturing variances or degradation of components over time. The self-calibration process may use a reference of a typical design performance characteristic of the digital sensors and measurements from the digital sensors under controlled conditions to calculate calibration coefficients for digital sensors that provide measurements that vary from the typical design performance 15 characteristic. The calibration coefficients may be used in the calculations for constructing a local map of a temperature and/or voltage gradient in the critical area, and identifying a location of a peak temperature and/or voltage in the critical area and on the integrated circuit.

Determining the locations of peak temperature and/or voltage, with the finer level of granularity and faster speed afforded by the network of digital sensors and the sensor network control unit, may provide means for detecting a temperature or a voltage draw in any circuit of the integrated circuit that may affect the performance and/or longevity of the integrated circuit. The information determined by the network of digital sensors and the sensor network control unit may be used to accurately control circuits within components of the integrated circuit, rather than entire components of integrated circuits, to mitigate the effects of the peak temperature and/or voltage on the circuit without having to sacrifice the use of the remainder of the component.

FIG. 1 illustrates an example digital sensor network on an integrated circuit is functional. Such conventional 35 integrated circuit suitable for implementing various embodiments. An integrated circuit may include various components, such as any number and combination of processors 102, cache memories 104, Intellectual Property (IP) units 106 (which may include any special purpose logic block/ unit/core circuit that may be integrated into the system), networking units 108, input/output (IO) units 110, and/or system controllers 118. In addition, the integrated circuit may include a digital sensor network 100 that may include any number and combination of digital sensors 114 placed throughout the integrated circuit and sensor network control units **112**.

> The digital sensors 114, described further herein with reference to FIG. 2, may be placed on the integrated circuit substrate between circuits of the integrated circuit components 102, 104, 106, 108, 112. In some embodiments, the digital sensors 114 may be distributed uniformly within an area of an integrated circuit component 102, 104, 106, 108, 112. In some embodiments, locations of circuits of the integrated circuit component 102, 104, 106, 108, 112 may 55 not allow a uniform distribution of the digital sensors 114 within the area of an integrated circuit component 102, 104, 106, 108, 112, and the digital sensors 114 may be distributed quasi-uniformly within the area of an integrated circuit component 102, 104, 106, 108, 112. A quasi-uniform distribution may be a distribution as close as possible to a uniform distribution given layout restrictions by circuits of the integrated circuit component 102, 104, 106, 108, 112 being located where a digital sensor 114 may be located in a uniform distribution. Both uniform and quasi-uniform distributions may be designed so as to not disrupt the circuit design of the integrated circuit component 102, 104, 106, 108, 112. Each digital sensor 114 may measure process

speed, temperature, and/or voltage for circuits within a sensing range of the digital sensor 114 by reacting to conditions within the sensing range of the digital sensor 114.

Each digital sensor 114 may be communicatively connected to a sensor network control unit 112 by a communication circuit 116. In some embodiments, the communication circuit 116 may be an individual communication line between the digital sensor 114 and a dedicated input pin at the sensor network control unit 112 associated with the digital sensor 114 and a sensor identifier of the digital sensor 10 114. The sensor identifier may indicate to the sensor network control unit 112 from which digital sensors 114 the measurement is transmitted. The digital sensor 114 may transmit a measurement value to the dedicated input pin at the sensor network control unit 112 via the individual communication 15 line. In some embodiments, the communication circuit 116 may be a communication bus between multiple digital sensors 114 and the sensor network control unit 112. The digital sensor 114 may transmit a measurement value and a sensor identifier to the sensor network control unit 112 via 20 the communication bus. In some embodiments, the digital sensor 114 may write the measurement value and/or the sensor identifier directly to a memory (not shown), such as a register or cache, accessible by the sensor network control unit 112. In some embodiments, the digital sensor 114 may 25 write the measurement value and/or the sensor identifier to a dedicated address for the digital sensor **114** in the sensor network control unit accessible memory. In some embodiments, the digital sensor 114 may write the measurement value and/or the sensor identifier to a first available address 30 in the sensor network control unit accessible memory.

The sensor network control unit 112 may receive the measurement value and/or the sensor identifier from the digital sensor 114 via the communication circuit 116. In some embodiments, the sensor network control unit 112 may 35 write the measurement value and/or the sensor identifier to the sensor network control unit accessible memory (not shown). In some embodiments, the sensor network control unit 112 may write the measurement value and/or the sensor identifier to an address in the sensor network control unit 40 accessible memory associated with the dedicated input pin. In some embodiments, the sensor network control unit 112 may write the measurement value and/or the sensor identifier to an address in the sensor network control unit accessible memory associated with the sensor identifier. In some 45 embodiments, the sensor network control unit 112 may write the measurement value and/or the sensor identifier to a first available address the sensor network control unit accessible memory.

The sensor network control unit 112 may retrieve mea- 50 surement values and sensor identifiers from the sensor network control unit accessible memory, and may use the retrieved measurement values and sensor identifiers to identify a critical group of digital sensors 114, referred to herein as a critical tile **512** and described further with reference to 55 FIG. 5. The sensor network control unit 112 may retrieve and use other data, from any number and combination of sensor network control unit accessible memories, such as the measurement values, the sensor identifiers of the critical tile, tile identifiers, positions of tiles on the integrated circuit, 60 calibration coefficients, and fitting matrix coefficients, all described further herein with reference to FIGS. 7-9. The sensor network control unit 112 may implement various arithmetic operations, such as multiply-add operations, using the other data to determine a hotspot, a location of 65 peak process, voltage, and/or temperature measurement and described further with reference to FIGS. 6-9, in the critical

6

tile, and map the hotspot to the on the integrated circuit. The hotspot may be mapped to a location within an area of the critical tile, which may be a subarea of an area of a component 102, 104, 106, 108, 112 of the integrated circuit. The sensor network control unit 112 may output the location of the hotspot and the process speed, temperature, and/or voltage of the hotspot to a system controller 118.

The system controller 118 may take adequate steps to adjust the process speed, temperature, and/or voltage of the hotspot. For example, the system controller 118 may reduce a frequency of a portion of the component 102, 104, 106, 108, 112 located at the hotspot, transfer processing work load from portion of the component 102, 104, 106, 108, 112 located at the hotspot to another portion (e.g., another processing core) of the component 102, 104, 106, 108, 112, etc.

The sensor network control unit 112 may also selfcalibrate to account for manufacturing variances and degradation of the digital sensors 114. The sensor network control unit 112 may implement a self-calibration process that may compare measurements taken by the digital sensors 114 under controlled conditions, such as processing load and designated frequency, and received from the digital sensors 114 with a reference of a typical design performance characteristic of the digital sensors 114. The comparison may be calculations, described further herein with reference to FIGS. 8 and 9, configured to output calibration coefficients for the digital sensors 114. Calibration coefficients may be calculated for each digital sensor 114 and stored in a sensor network control unit memory in a manner associating the calibration coefficients with the digital sensor 114. The calibration coefficients may be used in calculations of the process speed, temperature, and/or voltage of a hotspot to adjust for manufacturing variances and degradation of the digital sensors 114. The hotspot calculated using the calibration coefficients may be used to identify a location of the hotspot, map the hotspot in the critical tile, and map the hotspot on the integrated circuit.

FIG. 2 illustrates an example digital sensor suitable for implementing various embodiments. A digital sensor 114 may include a ring oscillator 200, a high speed counter 202, a counter storage 204, and a store signal synchronizer 206. These components of the digital sensor 200, 202, 204, 206 may be sized to allow the digital sensor 114 to be placed in a uniform or quasi-uniform distribution within an area of a component of an integrated circuit (e.g., processor 102, cache memory 104, IP unit 106, networking unit 108, IO unit 110 in FIG. 1, integrated circuit component 500 in FIG. 5). While a typical analog temperature sensor may have an area of 200 μm<sup>2</sup>, a digital sensor **114** may have a much smaller area. For example, a digital sensor **114** may use nanometer scale transistor technology, such as 5 nm fin field effect transistor (FinFET) technology, and may have an area of 10.6 μm<sup>2</sup>. The digital sensor **114** may react to environmental conditions, such as heat or voltage, within a sensor range, measure an effect if the environmental condition on the digital sensor 114, and output the measurement as a measurement representing a process speed, a temperature, and/or a voltage. Herein, the terms "measurement," "measurement value," and "counter value" are used interchangeably to indicate output data of a digital sensor 114 representing the environmental condition effect on the digital sensor 114.

The ring oscillator 200 may include an input pin at which the ring oscillator 200 may receive a trigger signal 208. The trigger signal 208 may be a digital signal that may indicate to the digital sensor 114 when to measure and when not to measure the environmental condition in the sensor range of

the digital sensor 114. For example, a rising edge of the trigger signal 208 may indicate to the digital sensor 114 to start measuring the environmental condition and a high value of the trigger signal 208 may indicate to the digital sensor 114 to continue measuring the environmental condition. Similarly, a falling edge of the trigger signal 208 may indicate to the digital sensor 114 to stop measuring the environmental condition and a low value of the trigger signal 208 may indicate to the digital sensor 114 to continue to not measure the environmental condition. In some 1 embodiments, the indications of the rising edge and the high value of the trigger signal 208 and the falling edge and low value of the trigger signal 208 may be reversed. In some embodiments, the trigger signal 208 may be an analog signal for which a first voltage or current may indicate to the digital 15 sensor 114 to start measuring the environmental condition and to continue measuring the environmental condition. Similarly, a second voltage or current of the trigger signal 208 may indicate to the digital sensor 114 to stop measuring the environmental condition and to continue to not measure 20 the environmental condition. For clarity, the examples herein are described using the rising edge and high value of the trigger signal 208 to indicate to the digital sensor 114 to start and maintain measuring the environmental condition, and the falling edge and low value of the trigger signal **208** 25 to indicate to the digital sensor 114 to stop and maintain not measuring the environmental condition. The trigger signal 208 may be controlled to elapse a designated period between signaling to the digital sensor 114 to start and stop measuring the environmental condition. The period may be designated 30 programmatically and/or by a user.

For the digital sensor **114** to measure the environmental condition, the ring oscillator 200 may receive the rising edge and/or high value of the trigger signal 208. In response receiving the rising edge and/or high value of the trigger 35 signal 208, the ring oscillator 200 may oscillate a ring oscillator signal and output the oscillating ring oscillator signal to a high speed counter 202 and to a storage signal synchronizer **206**. The ring oscillator signal may be a digital signal that may oscillate between high and low values. In 40 some embodiments, the ring oscillator 200 may use the trigger signal 208 to power the ring oscillator 200 and/or as an input for the ring oscillator signal. A speed at which the ring oscillator 200 may oscillate the ring oscillator signal may be affected by the environmental condition the digital 45 sensor 114 measures. For example, the ring oscillator 200 being in a higher temperature environment may be affected in a manner that may cause the ring oscillator 200 to oscillate the ring oscillator signal slower relative to being in a lower temperature environment. In the foregoing example, 50 the terms higher temperature and lower temperature may be relative to each other and/or to a temperature threshold. In high voltage applications, where performance may degrade in response to temperature increase, temperature accuracy may be important, and the digital sensor 114 may be 55 configured to detect small changes in temperature. For example, the digital sensor 114 may be configured to detect a change in temperature by single digit degrees Celsius in a nanosecond measurement timescale, such as at least 2° C. in a measurement time of 10 ns. In low voltage applications, 60 where performance may rapidly degrade in relation to voltage drop, voltage accuracy may be important, and the digital sensor 114 may be configured to detect small voltage drops. For example, the digital sensor 114 may be configured to detect a voltage drop of single digit millivolts in a 65 nanosecond measurement timescale, such as at least 1 mV change at a low end of a voltage range in a measurement

8

time of 10 ns. The ring oscillator 200 and the high speed counter 202 may be communicatively connected by a communication circuit. The ring oscillator 200 may output the ring oscillator signal to the high speed counter 202 via the communication circuit. The ring oscillator 200 and the storage signal synchronizer 206 may be communicatively connected by a communication circuit. The ring oscillator 200 may output the ring oscillator signal to the high speed counter 202 via the communication circuit. In some embodiments, the high speed counter 202 and the storage signal synchronizer 206 may be communicatively connected in parallel to the ring oscillator 200 via a shared communication circuit.

The high speed counter 202 may receive the ring oscillator signal from the ring oscillator 200 via the communication circuit. The ring oscillator signal may indicate to the high speed counter 202 when to increment a counter value of the ring oscillator signal. For example, a rising edge and/or a high value may indicate to the high speed counter **202** to increment the counter value, and a falling edge and/or a low value may indicate to the high speed counter 202 to stop incrementing the counter value. For clarity, the examples herein are described using the ring oscillator signal as in the foregoing example, however, in some embodiments, the indications of the ring oscillator signal to the high speed counter 202 may be reversed. In some embodiments, the high speed counter 202 may increment the counter value once in response to a rising edge and/or a high value of the ring oscillator signal. In some embodiments, the high speed counter 202 may repeatedly increment the counter value in response to a high value of the ring oscillator signal. In some embodiments, the high speed counter 202 may store the counter value to a counter storage 204, such as a register, accessible by the high speed counter 202 after each increment of the counter value. In some embodiments, the high speed counter 202 may store the counter value to the counter storage 204 in response to a falling edge and/or a low value of the ring oscillator signal. The high speed counter 202 may be communicatively connected to the counter storage 204 by a communication circuit. The high speed counter 202 may output the counter value signal to the counter storage 204 via the communication circuit. The counter storage 204 may receive the counter value from the high speed counter 202 via the communication circuit and store the counter value.

A storage signal synchronizer 206 may also receive the trigger signal 208 and interpret a falling end and/or low value of the trigger signal 208 to indicate to the digital sensor 114 to stop measurement. The storage signal synchronizer 206 may receive the ring oscillator signal from the ring oscillator 200 via the communication circuit. In response to receiving the falling edge and/or low value of the trigger signal 208 and the falling edge and/or low value of the ring oscillator signal, the storage signal synchronizer 206 may output a clear counter signal to the counter storage 204. In other words, the storage signal synchronizer 206 may align the trigger signal 208 with the ring oscillator signal to output the clear counter signal at an end of a measurement period for the digital sensor 114. The clear counter signal may be a digital signal that may alternate between high and low values, and may be the same type or an inverted type of digital signal value as the trigger signal 208 and/or the ring oscillator signal. In some embodiments, the clear counter signal may be generated from the trigger signal 208 and/or the ring oscillator signal. In some embodiments, the clear counter signal may be generated and/or selected in response to the trigger signal 208 and/or the ring oscillator signal. The

storage signal synchronizer 206 and the counter storage 204 may be communicatively connected by a communication circuit. The storage signal synchronizer 206 may output the clear counter signal to the counter storage 204 via the communication circuit.

The counter storage 204 may receive the clear counter signal from the storage signal synchronizer 206 via the communication circuit. The clear counter signal may indicate to the counter storage 204 when to output a sensor output signal 210, which may include the stored counter 10 value and/or a identifier for the digital sensor 114, to a sensor network control unit (e.g., sensor network control unit 112 in FIGS. 1 and 9) via a communication circuit (e.g., communication circuit 116 in FIG. 1). In some embodiments, the clear counter signal may further indicate to the counter 15 storage 204 to clear the stored counter value. For example, a rising edge and/or a high value of the clear counter signal may indicate to the counter storage 204 to output a sensor output signal 210 and/or to clear the stored counter value. For clarity, the examples herein are described using the clear 20 counter signal as in the foregoing example, however, in some embodiments, the counter storage 204 may rather respond similarly to a falling edge and/or a low value of the clear counter signal.

FIG. 3 illustrates a method 300 for sensing an environ- 25 mental condition at a digital sensor according to an embodiment. The method 300 may be implemented in dedicated hardware (e.g., digital sensor 114 in FIGS. 1, 2 and 5-6D, ring oscillator 200, high speed counter 202, counter storage 204, store signal synchronizer 206 in FIG. 2). In order to 30 encompass the alternative configurations enabled in various embodiments, the hardware implementing the method 300 is referred to herein as a "sensing device." The method 300 is described herein with reference to certain structural ele-However, other suitable structural elements are contemplated within the scope of the disclosure for performing the operations described with reference to blocks 302-324 of the method 300.

In block 302, a sensing device may receive a trigger signal 40 (e.g., trigger signal **208** in FIG. **2**). The trigger signal may be a digital signal that may indicate to the sensing device when to measure and when not to measure the environmental condition in a sensor range of the sensing device. For example, a rising edge of the trigger signal may indicate to 45 the sensing device to start measuring the environmental condition and a high value of the trigger signal may indicate to the sensing device to continue measuring the environmental condition. Similarly, a falling edge of the trigger signal may indicate to the sensing device to stop measuring 50 the environmental condition and a low value of the trigger signal may indicate to the sensing device to continue to not measure the environmental condition. The falling edge and/ or low value of the trigger signal may also partially indicate to the sensing device to output a sensor output signal (e.g., 55) sensor output signal 210 in FIG. 2) and clear a storage device (e.g., counter storage 204 in FIG. 2) of the sensing device. In some embodiments, the indications of the rising edge and the high value of the trigger signal and the falling edge and low value of the trigger signal 208 may be reversed. In some 60 embodiments, the trigger signal may be an analog signal for which a first voltage or current may indicate to the sensing device to start measuring the environmental condition and to continue measuring the environmental condition. Similarly, a second voltage or current of the trigger signal may indicate 65 to the sensing device to stop measuring the environmental condition and to continue to not measure the environmental

**10**

condition. The second voltage or current, or a third voltage or current, of the trigger signal may also partially indicate to the sensing device to output the sensor output signal and clear the storage device of the sensing device. For clarity, the examples herein are described using the rising edge and high value of the trigger signal to indicate to the sensing device to start and maintain measuring the environmental condition, and the falling edge and low value of the trigger signal to indicate to the sensing device to stop and maintain not measuring the environmental condition. These triggering methods are provided as examples, other methods to trigger the sensing device to start or stop measuring environmental conditions are within the contemplated scope of disclosure. The trigger signal may be controlled to elapse a designated period between signaling to the sensing device to start and stop measuring the environmental condition. The period may be designated programmatically and/or by a user. In some embodiments a ring oscillator 200 and/or a storage signal synchronizer 206 of a digital sensor 114 may receive a trigger signal in block 302.

In determination block 304, the sensing device may determine whether the trigger signal indicates to the sensing device to measure the environmental condition. In other words, the sensing device may determine whether the received trigger signal is a rising edge of the trigger signal or a high value of the trigger signal. The sensing device may determine whether the received trigger signal is a rising edge or a high value using various known means. In some embodiments, the ring oscillator 200 and/or the store signal synchronizer 206 may determine whether the trigger signal indicates to the sensing device to measure the environmental condition in determination block 304.

In response to determining that the trigger signal indicates ments for purposes of illustration and ease of reference. 35 to the sensing device to measure the environmental condition (i.e., determination block 304="Yes"), the sensing device may oscillate a ring oscillator signal in block 306. The ring oscillator signal may be a digital signal that may oscillate between high and low values. The ring oscillator signal may indicate to the sensing device when to increment a counter value of the ring oscillator signal. For example, a rising edge and/or a high value may indicate to the sensing device to increment the counter value, and a falling edge and/or a low value may indicate to the sensing device to stop incrementing the counter value. For clarity, the examples herein are described using the ring oscillator signal as in the foregoing example, however, in some embodiments, the indications of the ring oscillator signal to the sensing device may be reversed. In some embodiments, the sensing device may use the trigger signal to power the sensing device and/or as an input for the ring oscillator signal. In block 308, the sensing device may output the ring oscillator signal. In some embodiments, the ring oscillator 200 may oscillate a ring oscillator signal in block 306 and may output the ring oscillator signal in block 308.

> In block 310, the sensing device may receive the ring oscillator signal. In some embodiments, a high speed counter 202 and/or the storage signal synchronizer 206 may receive the ring oscillator signal in block 310. In block 312, the sensing device may increment a counter value. In some embodiments, the sensing device may increment the counter value once in response to a rising edge and/or a high value of the ring oscillator signal. In some embodiments, the sensing device may repeatedly increment the counter value in response to a high value of the ring oscillator signal. In some embodiments, the high speed counter 202 may increment a counter value in block 312.

In block 314, the sensing device may store the counter value. The sensing device may store the counter value to a counter storage, such as a register, accessible by the sensing device after each increment of the counter value. In some embodiments, the sensing device may store the counter 5 value to the counter storage in response to a falling edge and/or a low value of the ring oscillator signal. In some embodiments, the high speed counter 202 may store the counter value in block 314. Following storing the counter value in block 314, the sensing device may continue to 10 receive the trigger signal in block 302.

In response to determining that the trigger signal does not indicate to the sensing device to measure the environmental condition (i.e., determination block 304="No"), the sensing device may output the ring oscillator signal in block 316, 15 and the sensing device may receive the ring oscillator signal in block 318. In some embodiments, the ring oscillator 200 may output the ring oscillator signal in block 316 and the high speed counter 202 and/or the storage signal synchronizer 206 may receive the ring oscillator signal in block 318.

In determination block 320, the sensing device may determine whether the ring oscillator signal is a falling edge. The sensing device may determine whether the ring oscillator signal is a falling edge using various known means. In some embodiments, the storage signal synchronizer 206 25 may determine whether the ring oscillator signal is a falling edge in determination block 320. In response to determining that the ring oscillator signal is not a falling edge (i.e., determination block 320="No"), the sensing device may continue to output the ring oscillator signal in block 316.

In response to determining that the ring oscillator signal is a falling edge (i.e., determination block 320="Yes"), the sensing device may output a clear counter signal in block 322. In other words, the sensing device may align the trigger signal with the ring oscillator signal to output the clear 35 counter signal at an end of a measurement period for the sensing device. The clear counter signal may be a digital signal that may alternate between high and low values, and may be the same type or an inverted type of digital signal value as the trigger signal and/or the ring oscillator signal. 40 In some embodiments, the clear counter signal may be generated from the trigger signal and/or the ring oscillator signal. In some embodiments, the clear counter signal may be generated and/or selected in response to the trigger signal and/or the ring oscillator signal. The clear counter signal 45 may indicate to the sensing device when to output the sensor output signal, which may include the stored counter value and/or an identifier for the sensing device, to a sensor network control unit (e.g., sensor network control unit 112 in FIGS. 1 and 9). In some embodiments, the clear counter 50 signal may further indicate to the sensing device to clear the stored counter value. For example, a rising edge and/or a high value of the clear counter signal may indicate to the sensing device to output a sensor output signal and/or to clear the stored counter value. For clarity, the examples 55 herein are described using the clear counter signal as in the foregoing example, however, in some embodiments, the sensing device may rather respond similarly to a falling edge and/or a low value of the clear counter signal. In some embodiments, the storage signal synchronizer 206 may 60 output a clear counter signal in block 322.

In block 324, the sensing device may receive the clear counter signal. In block 326, the sensing device may output a sensor output signal. In block 328, the sensing device may clear the counter storage. In some embodiments, the counter 65 storage 204 may receive the clear counter signal in block 324, output a sensor output signal in block 326, and clear the

12

counter storage in block 328. Following clearing the counter storage in block 328, the sensing device may continue to receive the trigger signal in block 302.

FIG. 4 graphically illustrates temperature decay over distance on an integrated circuit. When an integrated circuit is operational, components of the integrated circuit (e.g., processor 102, cache memory 104, IP unit 106, networking unit 108, IO unit 110 in FIG. 1, integrated circuit component 500 in FIG. 5) may consume electrical power and generate heat. The heat may dissipate mainly through a substrate of the integrated circuit, such as silicon. The manner in which the temperature (T) decreases with distance away from a heat source (d<sub>0</sub>), such as a hotspot, on the integrated circuit, as measured from a location (d) (e.g., a digital sensor 114 in FIG. 1) on the integrated circuit, may be calculated using an exponentially decaying function:

$$T(d) = T(d_0)e^{\left(-\frac{(d-d_0)}{\delta}\right)}$$

(eq. 1)

where at a certain distance  $(\delta)$ , the temperature may be half of what it is at the heat source, regardless of the temperature of the heat source. As illustrated in the graph of FIG. **4**, a temperature  $(T_1 \text{ or } T_2)$  at a first distance  $(d_0)$  may be halved  $(T_1/2 \text{ or } T_2/2)$  at a second distance (d), when the first distance and the second distance are a certain distance  $(\delta)$  apart. A voltage discharge over distance may be calculated in the same manner by replacing temperature (T) for voltage (V):

$$V(d) = V(d_0)e^{\left(-\frac{(d-d_0)}{\delta}\right)}$$

(eq. 2)

where voltage discharge may decay by half over a certain distance ( $\delta$ ).

FIG. 5 illustrates an example of part of a digital sensor network within an area of an integrated circuit component suitable for implementing various embodiments. A digital sensor network (e.g., digital sensor network 100 in FIG. 1) may include portions that are configured to sense the environmental conditions for particular integrated circuit components 500 (e.g., processor 102, cache memory 104, IP unit 106, networking unit 108, IO unit 110 in FIG. 1). Placement of the digital sensors 114 may be uniformly or quasiuniformly distributed over an area of an integrated circuit component 500. Any number of digital sensors 114 may be distributed over the area of the integrated circuit component **500**. For clarity, the communication circuits (e.g., communication circuits 116 in FIG. 1), communicatively connecting the digital sensors 114 to a sensor network control unit (e.g., sensor network control unit 112 in FIGS. 1 and 9) are omitted from FIG. **5**.

Groups of the digital sensors 114 may be referred to as tiles 502. A tile may include any number of digital sensors 114 configured in a symmetrical or quasi-symmetrical pattern. As with a quasi-uniform distribution of digital sensors 114, a quasi-symmetrical pattern of digital sensors 114 may be a distribution as close as possible to a symmetrical pattern given layout restrictions by circuits of the integrated circuit component 500 being located where a digital sensor 114 may be located in a symmetrical pattern. Both uniform and quasi-symmetrical patterns may be designed to not disrupt the circuit design of the integrated circuit component 500. For example, a uniform and/or quasi-symmetrical distribu-

tion pattern of digital sensors 114 may be a grid-like distribution pattern of digital sensors **114** in which rows and columns of digital sensors 114 may be offset by half the distance  $\delta$  (e.g.,  $\delta/2$ ). A resulting tile pattern may be a square having a digital sensor 114 at each corner of the perimeter 5 of the square and a digital sensor 114 in the middle of the square. Each side of the square may be the distance  $\delta$ , at which temperature and/or voltage discharge may decay by half. The digital sensors 114 on the perimeter of the square may be spaced apart by the distance  $\delta$ . A distance between 10 the perimeter of the square and the digital sensor 114 in the middle of the square may be half the distance  $\delta$  ( $\delta/2$ ). Adjacent tiles 502 and/or overlapping tiles 502 may share digital sensors 114. A tile 502 in which a center digital sensors 114 is calculated to be the closest digital sensor 114 15 to a hotspot 510 may be referred to as a critical tile 512. In an example tile 502, the environmental condition may decreases by half over a millimeter scale distance, such as approximately 1 mm, through substrate heat dissipation. A distribution of digital sensors 114 having a 0.5 mm tile side 20 size may identify hotspots **510** with a precision of 31.5 mm. A common 64-bit integer multiplier may be approximately 40 mm×40 mm when formed in 5 nm transistor technology. A tile that is  $0.5 \text{ mm} \times 0.5 \text{ mm}$  may contain 150 64-bit multipliers. A 31.5 mm precision means that precisely which 25 specific multiplier is located at the hotspot may be identified. An area penalty due to the insertion of the sensors in such a tile distribution of the digital sensors **114** in the 64-bit integer multiplier may be 0.0125%.

A digital sensor 114 may more reliably measure a change 30 tion. in the environmental condition than another digital sensor 114 when the digital sensor 114 is closer to a hotspot than another digital sensor 114. Digital sensors 114 may be arranged in a grid-like pattern so that any hotspot 510 may occur in between digital sensors 114 of a critical tile 512 and 35 so that the sensor ranges of the digital sensors **114** overlap. Such a configuration of digital sensors 114 may guarantee that functional digital sensors 114 register a change in the environmental condition. From measurements sensed by the digital sensors 114 surrounding a hotspot 510 and knowing 40 how an environmental condition decays with distance on an integrated circuit, where the hotspot **510** is located and what peak environmental condition the hotspot 510 has may be calculated. For example, a hotspot **510**, whose temperature predictably decays over radial distance 504, 506, 508, may 45 occur between two digital sensors 114 of a critical tile 512, and may be sensed by any number of digital sensors 114 of the critical tile 512. A benefit of a grid-like distribution pattern of digital sensors 114 may be that for a given center digital sensor 114, the perimeter digital sensors 114 may be 50 uniquely defined. It may be preferred to have a uniform pattern of distribution of digital sensors 114 so that the measurements from each digital sensor 114 may be interpreted the same way. However, some critical functional blocks of the integrated circuit component 500 may not 55 allow precise placement of the digital sensors 114, resulting in a uniform pattern of distribution of digital sensors 114, having local "irregular" tiles 510. The concept and the mathematical processing of the measurement from such "irregular" tiles 510 may be the same as for regular tiles 510,  $_{60}$  ( $C_{each\ sensor}$ ), a system of equations may be constructed: only matrix coefficients may be different to adjust for the quasi-uniform distances. The sensor network control unit may have specific information for these irregular tiles 510.

The sensor network control unit may receive the measurements from the digital sensors 114 of the integrated 65 circuit component 500 and determine which digital sensor 114 out of the digital sensor network 100 has the highest

14

measurement among all. The sensor network control unit may identify the critical tile 512 by identifying which tile 502 has a center digital sensor 114 with a highest measurement. Identifying the critical tile **512** may identify the digital sensors 114 of the critical tile 512. The sensor network control unit may process the measurements of the digital sensors 114 of the critical tile 512, and produce the peak value of the environmental condition at the hotspot **510** and a location of the hotspot **510**.

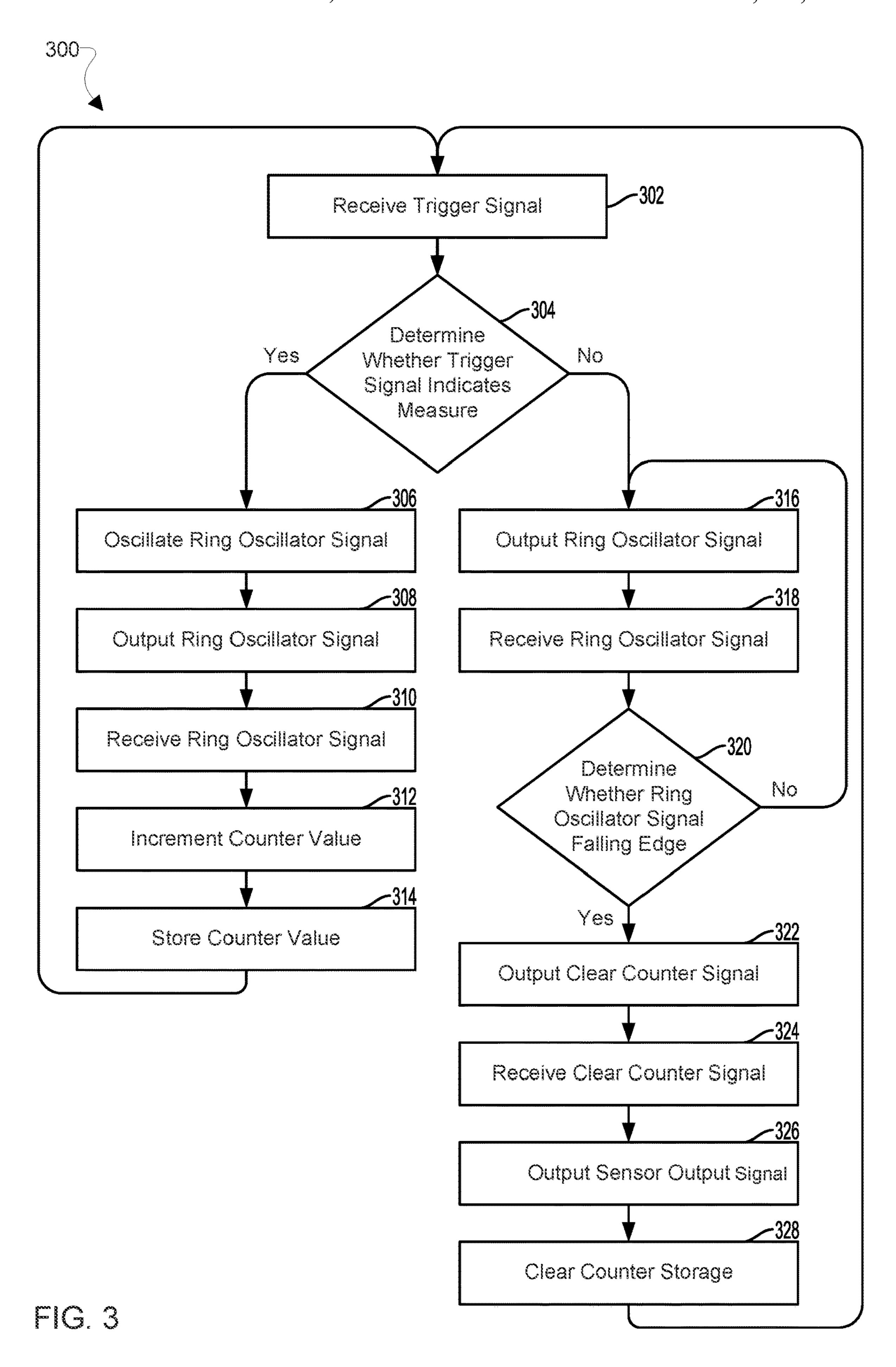

FIGS. 6A-6D illustrate examples of a critical tile 512 of a digital sensor network on an integrated circuit suitable for implementing various embodiments. A critical tile 512 may include any number of digital sensors 114 and a finite number of potential hotspots 600. The examples illustrated in FIGS. 6A-6D include the critical tile 512 having five digital sensors 114, where digital sensors A, B, C, and D are perimeter or corner digital sensors 114, and digital sensor E is a center digital sensor 114. In these examples, the number of potential hotspots 600 of the critical tile 512 may be a finite number N<sup>2</sup>, where there may be N number of potential hotspots 600 per row and column of potential hotspots 600. As described herein, a critical tile 512 may be any symmetrical or quasi-symmetrical shape and include any number of digital sensors 114. The shape and size of the critical tile 512 and placement of the digital sensors 114 may affect the number and/or layout of the potential hotspots 600 of the critical tile **512**. The examples illustrated in FIGS. **6A-6**D are not limiting on the scope of the claims or the specifica-

A series of equations may be used to determine features of a hotspot (e.g., hotspot **510** in FIG. **5**) of the critical tile **512**, including the environmental condition at the hotspot and the distance of the hotspot from the digital sensors 114 of the critical tile **512**. The equations are described herein with reference to the examples illustrated in FIGS. 6A-6D, but may be modified to accommodate different configured critical tiles 512.

The measurements at a digital sensor 114 ( $C_{sensor}$ ) of the critical tile 512 may be calculated as a function of the environmental condition  $(C_{potential\ hotspot})$  at the potential hotspots 600 and distance  $(d_{sensor, potential hotspot})$  between the digital sensor 114 and the potential hotspots:

$$C_{sensor} = \sum_{1}^{N} C_N \cdot e^{\left(\frac{d_{sensor,N}}{\delta}\right)}$$

(eq. 3)

The exponential term may be rewritten to simplify the equation:

$$C_{sensor} = \sum_{1}^{N} C_{N} \cdot \varphi_{sensor,N}$$

(eq. 4)

For each measurement of each of the digital sensors **114**

$$C_{each \ sensor} = \begin{bmatrix} C_A \\ \vdots \\ C_E \end{bmatrix} = F \cdot \begin{bmatrix} C_1 \\ \vdots \\ C_N \end{bmatrix} \text{ where } F = \begin{bmatrix} \varphi_{A,1} & \dots & \varphi_{A,N} \\ \vdots & \ddots & \vdots \\ \varphi_{E,1} & \dots & \varphi_{E,N} \end{bmatrix}$$

(eq. 5)

The system of equations for the measurements of each of the digital sensors 114 (eq. 5) may be solved for the environmental condition at each of the potential hotspots **600** ( $C_{each\ potential\ hotspot}$ ):

$$C_{each\ potential\ hotspot} = \begin{bmatrix} C_1 \\ \vdots \\ C_N \end{bmatrix} = F^{-1} \cdot \begin{bmatrix} C_A \\ \vdots \\ C_E \end{bmatrix}$$

(eq. 6)

However, the system of equations for the environmental condition at each of the potential hotspots 600 (eq. 6) may be under-determined and may not have a solution.

FIGS. 6A-6D illustrate a configuration for narrowing the 15 potential hotspots 600 to a number of the potential hotspots **600** for which the system of equations for the environmental condition at each of the potential hotspots 600 (eq. 6) may be solved. As described herein, a critical tile 512 is a tile (e.g., tile **502** in FIG. **5**) of a portion of a digital sensor 20 network (e.g., digital sensor network 100 in FIG. 1) for a particular integrated circuit component (e.g., processor 102, cache memory 104, IP unit 106, networking unit 108, IO unit 110 in FIG. 1, integrated circuit component 500 in FIG. 5) where a hotspot may be located closest to a center digital 25 sensor 114 (digital sensor E) than the perimeter digital sensors 114 (digital sensors A, B, C, and D). Therefore, as illustrated in FIG. 6A, for a critical tile 512, the potential hotspots 600 may be narrowed to the potential hotspots 604 within a half tile width diameter **606** from the center digital 30 sensor 114 (digital sensor E). Narrowing the potential hotspots 600 to the potential hotspots 604 within the half tile width diameter 606 may double the precision of the calculations for the environmental condition at a hotspot. This a hotspot to be discerned from other potential hotspots 604 separated by a distance on a micrometer scale. For example, this level of precision may allow for discernment of the environmental condition at a hotspot separated by a distance of 31.5  $\mu$ m on a tile of 0.5 mm.

FIGS. 6B-6D illustrate further narrowing the potential hotspots 604 based on comparison of measurements between the digital sensors 114 to determine which of the perimeter digital sensors 114 (digital sensors A, B, C, and D) are next closest to the hotspot after the center digital sensor 45 **114** (digital sensors E). Based on having five digital sensors 114, sorting the measurements of the digital sensors 114 may produce three different combinations per eighth of the half tile width diameter 606. For example, FIG. 6B illustrates a comparison the measurements of the digital sensors **114** may 50 indicate that the measurements of the digital sensors 114 may be ordered as E>D>C=A>B. With the potential hotspots 604 closest to center digital sensor E, then to the perimeter digital sensor D, and then equally to the perimeter digital sensor C and the perimeter digital sensor A, the 55 potential hotspots 604 may be narrowed to potential hotspots 604 within the half tile width diameter 606 and along an axis between center digital sensor E and perimeter digital sensor

For another example, FIG. 6C illustrates a comparison the 60 measurements of the digital sensors 114 may indicate that the measurements of the digital sensors 114 may be ordered as E>D>C>B>A. With the potential hotspots **604** closest to the center digital sensor E, then to the perimeter digital sensor D, and then to the perimeter digital sensor C, the 65 potential hotspots 604 may be narrowed to potential hotspots 604 within the half tile width diameter 606 and between an

**16**

axis between the center digital sensor E and the perimeter digital sensor D and an axis bisecting the potential hotspots 604 between the perimeter digital sensor D and the perimeter digital sensor C.

For another example, FIG. 6D illustrates a comparison the measurements of the digital sensors 114 may indicate that the measurements of the digital sensors 114 may be ordered as E>D=C>B=A. With the potential hotspots **604** closest to center digital sensor E and then equally to the perimeter digital sensor D and the perimeter digital sensor C, the potential hotspots 604 may be narrowed to potential hotspots 604 within the half tile width diameter 606 and along an axis bisecting the potential hotspots 604 between the perimeter digital sensor D and the perimeter digital sensor C.

The foregoing examples illustrated in FIGS. 6B-6D relate to the potential hotspots 604 in the eighth of the half tile width diameter 606 between the axis between the center digital sensor E and the perimeter digital sensor D and the axis bisecting the potential hotspots 604 between the perimeter digital sensor D and the perimeter digital sensor C. Similar comparisons of the digital sensors 114 resulting in different orders of the perimeter digital sensors 114 (A, B, C, and D), may similarly narrow the potential hotspots 604 in the other seven eighths of the half tile width diameter 606.

The system of equations for the environmental condition at each of the potential hotspots **600** (eq. 6) may be simplified to the equations for the potential hotspots **604**. The digital sensors 114 may provide sufficient information to solve the less complex system of equations for the environmental condition at each of the potential hotspots 604 (eq. 6).

FIG. 7 illustrates a method 700 for self-calibration of a sensor network control unit according to an embodiment. level of precision may allow the environmental condition at 35 The method 700 may be implemented in software executing in a processor (e.g., sensor network control unit 112 in FIGS. 1 and 9, system controller 116 in FIG. 1), in general purpose hardware, in dedicated hardware (e.g., sensor network control unit 112 in FIGS. 1 and 9), or in a combination of a 40 software-configured processor and dedicated hardware, such as a processor executing software (e.g., sensor network control unit 112 in FIGS. 1 and 9, system controller 116 in FIG. 1) within a digital sensor network (e.g., digital sensor network 100 in FIG. 1) that includes other individual components (e.g., processor 102, cache memory 104, IP unit 106, networking unit 108, IO unit 110 in FIG. 1, integrated circuit component 500 in FIG. 5), and various memory/ cache controllers. In order to encompass the alternative configurations enabled in various embodiments, the hardware implementing the method 700 is referred to herein as a "control device." The method 700 is described herein with reference to certain structural elements for purposes of illustration and ease of reference. However, other suitable structural elements are contemplated within the scope of the disclosure for performing the operations described with reference to blocks 702-712 of the method 700.

Digital sensors (e.g., digital sensor 114 in FIGS. 1, 2 and 5-6D) of a digital sensor network may be affected by manufacturing variances and/or degradation over time and may not perform as expected, such as not performing in accordance with an expected performance for a same type of digital sensor. A control device may implement a selfcalibration of the control device to be able to adjust for variances in performance of the digital sensors. In some embodiments, the self-calibration of the control device may be executed for any number and combinations of digital sensors in response to anomalous sensor data from any

number and combination of digital sensor, periodically, in response to a user prompt, etc.

In block 702, the control device may apply a control factor to an integrated circuit component. A control factor may be any combination of a workload, a voltage, a pro- 5 cessor frequency, processor, memory, and/or communication operations, etc. for which, when the integrated circuit component, a normal environmental condition for the integrated circuit component is known. The control device may apply a control factor to any number and combination of 10 integrated circuit components, such as integrated circuit components in an area of which digital sensors, that the control device is to be calibrated for, are distributed. In some embodiments, a sensor network control unit and/or a system controller may apply the control factor to the integrated 15 circuit component in block 702. In some embodiments, the processor 102, the sensor network control unit 112, the system controller 116, or other processing device (not shown), such as a processor separate from the digital sensor network 100 and/or the integrated circuit having the digital 20 sensor network 100, may apply the control factor to the integrated circuit component in block 702.

In block 704, the control device may receive sensor output signals from any number and combination of digital sensors of a digital sensor network. The control device may receive 25 sensor output signals from at least the digital sensors distributed within the area of the integrated circuit component to which the control factor is applied in block 702. Each sensor output signal may include sensor data of a counter value and/or an identifier for the digital sensor that output 30 the sensor output signal. In some embodiments, the sensor network control unit 112, including a sensor measurement input and storage unit (e.g., sensor measurement input and storage unit 904 in FIG. 9), may receive the sensor output signals from the digital sensors in block 704.

In block 706, the control device may store the sensor data of the sensor output signal. The control device may store the counter value and/or the identifier for the digital sensor that output the sensor output signal. The control device may store the sensor data to an integrated and/or accessible memory, 40 which may be implemented as any number and combination of volatile and/or non-volatile memory devices, such as a register, a cache, a random access memory (RAM), a read only memory (ROM), an electrically erasable programmable ROM (EEPROM), a flash memory, etc. The control device 45 may store the sensor data in a manner that associates the identifier for the digital sensor and the counter value from the digital sensor. In some embodiments, the identifier for the digital sensor stored to the memory may be received in the sensor output signal data or associated with a pin of the 50 control device on which the sensor output signal is received, and written to the memory as part of storing the sensor output signal data or preloaded in the memory. In some embodiments, the sensor network control unit 112, including a sensor data memory (e.g., sensor data memory **930** in FIG. 55 9), may store the sensor data of the sensor output signal in block **706**.

In block 708, the control device may retrieve the sensor data for a digital sensor. The control device may use the identifier of a digital sensor to retrieve sensor data for the 60 digital sensor from the memory. The identifier of the digital sensor may be the identifier for a digital sensor selected by the control device to use in a self-calibration of the control device. In some embodiments, the sensor network control unit 112, including an arithmetic unit (e.g., arithmetic unit 65 916 in FIG. 9), may retrieve the sensor data for the digital sensor in block 708.

18

In block **710**, the control device may calculate calibration coefficients for the digital sensor. For any distribution of digital sensors, the self-calibration process of the control device may use at least two sensor measurements for each digital sensor "i"  $(CS_1^i \text{ and } CS_2^i)$  to solve for the calibration coefficient values  $(d_0^i \text{ and } d_1^i)$  using known reference counter values  $(Cref_1^i \text{ and } Cref_2)$ :

$$d_0^i = \frac{CS_1^i \cdot Cref_2 - CS_2^i \cdot Cref_1}{Cref_2 - Cref_1}$$

(eq. 7)

$$d_1^i = \frac{CS_1^i - CS_2^i}{Cref_1 - Cref_s}$$

(eq. 8)

These calibration coefficient values  $(d_0^i \text{ and } d_1^i)$  may be expressed as matrices for multiple digital sensors, such as an array of  $d_0^i$  values may be notated as  $D_0$  and a diagonal matrix of  $d_1^i$  values may be notated as  $D_1$ . These calibration coefficients may be used to solve the system of equations for the environmental condition at each of the potential hotspots (eq. 6) while accounting for variances between the digital sensors. Knowing the reference sensor values for each of the digital sensors ( $C_{sensor\ reference}$ ) the following equation can be solved for the environmental condition at each of the potential hotspots ( $C_{each\ potential\ hotspot}$ ):

$$C_{sensor\ reference} = D_0 + D_1 \cdot C_{each\ sensor} = D_0 + D_1 \cdot F \cdot C_{each}$$

$$potential\ hotspot$$

(eq. 9)

Solving the above equation for the environmental condition at each of the potential hotspots ( $C_{each\ potential\ hotspot}$ ), the system of equations for the environmental condition at each of the potential hotspots (eq. 6) becomes:

$$\begin{array}{l} C_{each\ potential\ hotspot} = & (F^T \cdot F)^{-1} \cdot F^T \cdot D_1^{-1} \cdot (C_{sensor\ refer^-} \\ ence - D_0) \end{array}$$

(eq. 10)

where  $(F^T \cdot F)^{-1} \cdot F^T$  may be fixed and precomputed. In some embodiments, the sensor network control unit **112**, including the arithmetic unit **916**, may calculate the calibration coefficients for the digital sensor in block **710**.

In block 712, the control device may store the calibration coefficients. The calibration coefficients may be stored in a manner that associates each of the calibration coefficients with an appropriate identifier of the digital sensor for which the calibration coefficients were calculated. In some embodiments, the calibration coefficients may be stored in the same memory or a different memory than the stored sensor data in block 706. In some embodiments, the sensor network control unit 112, including the arithmetic unit 916, may store the calibration coefficients in block 712.

FIG. 8 illustrates a method 800 for identifying and mapping hotspots according to an embodiment. The method 800 may be implemented in software executing in a processor (e.g., sensor network control unit 112 in FIGS. 1 and 9), in general purpose hardware, in dedicated hardware (e.g., sensor network control unit 112 in FIGS. 1 and 9), or in a combination of a software-configured processor and dedicated hardware, such as a processor executing software (e.g., sensor network control unit 112 in FIGS. 1 and 9) within a digital sensor network (e.g., digital sensor network 100 in FIG. 1) that includes other individual components (e.g., processor 102, cache memory 104, IP unit 106, networking unit 108, IO unit 110 in FIG. 1, integrated circuit component 500 in FIG. 5), and various memory/cache controllers. In order to encompass the alternative configurations enabled in various embodiments, the hardware implementing the method 800 is referred to herein as a "control device." In

some embodiments, the method 800 may be implemented for any number and combination of integrated circuit components, including separately for multiple integrated circuit components and/or concurrently for multiple integrated circuit components. The method 800 is described herein with 5 reference to certain structural elements for purposes of illustration and ease of reference. However, other suitable structural elements are contemplated within the scope of the disclosure for performing the operations described with reference to blocks 802-822 of the method 800.

In block 802, a control device may receive sensor output signals from any number and combination of digital sensors (e.g., digital sensor 114 in FIGS. 1, 2, and 5-6D) of a digital sensor network. The control device may receive sensor output signals from the digital sensors distributed within the 15 areas of any number and combination of integrated circuit components. Each sensor output signal may include sensor data of a counter value and/or an identifier for the digital sensor that output the sensor output signal. In some embodiments, the sensor network control unit 112, including a 20 sensor measurement input and storage unit (e.g., sensor measurement input and storage unit 904 in FIG. 9), may receive the sensor output signals from the digital sensors in block **802**.

In block **804**, the control device may select any number of 25 critical digital sensors. In some embodiments, the control device may compare the counter values of the digital sensors with each other and determine which of the counter values is a critical counter value. A critical counter value may be a counter value at an extreme of a range of the compared 30 counter values. In some embodiments, the control device may compare the counter values to expected counter values for the digital sensors that have identifiers of the digital sensors associated with the compared counter values, and counter value. A critical counter value may be a counter value with a minimum or greatest deviation from an expected counter value. In some embodiments, the counter values may be adjusted by respective calibration coefficients prior to the comparisons. In some embodiments, the control 40 device may select any number and combination of critical counter values, including based on a number of critical counter values to select and/or a critical counter value threshold, selecting based on critical counter values that exceed the critical counter value threshold. A critical counter 45 value may be referred to as an extreme value of a comparison. The control device may identify an identifier of a digital sensor associated with a critical counter value as an identifier of a critical digital sensor. In some embodiments, the sensor network control unit 112, including a critical digital 50 sensor data selection unit (e.g., critical digital sensor data selection unit 906 in FIG. 9), may select the critical digital sensors in block 804.

In block 806, the control device may identify any number of critical tiles (e.g., critical tile 512 in FIGS. 5-6D). The 55 control device may use an identifier of a critical digital sensor to retrieve critical tile data from a memory. An identifier of a critical digital sensor may be for a center digital sensor of a tile (e.g., tile 502 in FIG. 5, critical tile **512** in FIGS. **5-6**D). The identifier of the critical digital 60 sensor may be associated with tile data, including an identifier of the tile. The control device may retrieve the identifier of the tile associated with the identifier of the critical digital sensor. The control device may identify the identifier of the tile associated with the identifier of the critical digital 65 sensor as an identifier of a critical tile. In some embodiments, the sensor network control unit 112, including a tile

**20**

data selection unit (e.g., tile data selection unit 912 in FIG. 9), may identify the critical tiles in block 806.

In block 808, the control device may identify perimeter digital sensors of the critical tiles. As above, the control device may use an identifier of a critical digital sensor to retrieve critical tile data from the memory. The identifier of the critical digital sensor may be associated with tile data, including an identifier of the tile and identifiers of perimeter digital sensors of the tile. In some embodiments, the control device may retrieve the identifiers of the perimeter digital sensors associated with the identifier of the critical digital sensor. The control device may identify the identifiers of the perimeter digital sensors associated with the identifier of the critical digital sensor as identifiers of the perimeter digital sensors of a critical tile. In some embodiments, the control device may retrieve the identifiers of the perimeter digital sensors associated with the identifier of a critical tile. The control device may identify the identifiers of the perimeter digital sensors associated with the identifier of the critical tile as identifiers of the perimeter digital sensors of the critical tile. In some embodiments, the sensor network control unit 112, including the tile data selection unit 912, may identify the perimeter digital sensors of the critical tiles in block 808.

In block 810, the control device may sort counter values of the perimeter digital sensors of the critical tiles. The control device may use the identifiers of the perimeter digital sensors of the critical tile to retrieve counter values associated with the identifiers of the perimeter digital sensors from a memory. The control device may sort the counter values of the perimeter digital sensors for each critical tile to narrow the locations of potential hotspots (e.g., potential hotspots 600, 604 in FIGS. 6A-6D) within each critical tile. In some embodiments, the control device may sort the counter values may determine which of the counter values is a critical 35 based on magnitude of the counter values in comparison to each other. In some embodiments, the control device may sort the counter values based on a magnitude of a deviation of the counter values from respective expected values. In some embodiments, the control device may use the identifiers of the perimeter digital sensors of the critical tile to retrieve calibration coefficients associated with the identifiers of the perimeter digital sensors from the memory. The retrieved counter values of the perimeter digital sensors may be adjusted by the respective calibration coefficients prior to the comparisons. The control device may sort the counter values into an order indicating to the control device which of the digital sensors of the critical tile is closer to a hotspot (e.g., hotspot **510**, in FIG. **5**) compared to the other digital sensors of the critical tile, with the center digital sensor being the closest, followed by the various perimeter digital sensors. In some embodiments, the sensor network control unit 112, including an arithmetic unit (e.g., arithmetic unit **916** in FIG. **9**), may sort the counter values of the perimeter digital sensors of the critical tiles in block 810.