### US011568918B2

### (12) United States Patent

Ayyapureddi et al.

# (54) APPARATUSES, SYSTEMS, AND METHODS FOR ANALOG ACCUMULATOR FOR DETERMINING ROW ACCESS RATE AND TARGET ROW ADDRESS USED FOR REFRESH OPERATION

(71) Applicant: MICRON TECHNOLOGY, INC.,

Boise, ID (US)

(72) Inventors: Sujeet Ayyapureddi, Boise, ID (US);

Raghukiran Sreeramaneni, Hyderabad

(IN)

(73) Assignee: Micron Technology, Inc., Boise, ID

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 17/170,616

(22) Filed: Feb. 8, 2021

### (65) Prior Publication Data

US 2021/0158851 A1 May 27, 2021

### Related U.S. Application Data

- (62) Division of application No. 16/548,027, filed on Aug. 22, 2019, now Pat. No. 10,964,378.

- (51) Int. Cl.

G11C 11/408 (2006.01)

G11C 11/406 (2006.01)

(Continued)

- (52) **U.S. Cl.**CPC ...... *G11C 11/408* (2013.01); *G11C 11/1655* (2013.01); *G11C 11/1657* (2013.01); (Continued)

### (10) Patent No.: US 11,568,918 B2

(45) Date of Patent: \*Jan

\*Jan. 31, 2023

### (58) Field of Classification Search

### (56) References Cited

#### U.S. PATENT DOCUMENTS

1,158,364 A 10/1915 Bibb 3,633,175 A 1/1972 Harper (Continued)

### FOREIGN PATENT DOCUMENTS

CN 1144434 A 3/1997 CN 1195173 A 10/1998 (Continued)

#### OTHER PUBLICATIONS

US 11,264,075 B2, 03/2022, Bell et al. (withdrawn) (Continued)

Primary Examiner — Mushfique Siddique (74) Attorney, Agent, or Firm — Dorsey & Whitney LLP

### (57) ABSTRACT

Embodiments of the disclosure are drawn to apparatuses, systems, and methods for analog row access rate determination. Accesses to different row addresses may be tracked by storing one or more received addresses in a slice of stack. Each slice includes an accumulator circuit which provides a voltage based on charge on a capacitor. When a row address is received, it may be compared to the row addresses stored in the stack, and if there is a match, the charge on the capacitor in the associated accumulator circuit is increased. Each slice may also include a voltage to time (VtoT) circuit which may be used to identify the highest of the voltages provided by the accumulator circuits. The row address stored in the slide with the highest voltage may be refreshed.

### 20 Claims, 8 Drawing Sheets

## US 11,568,918 B2 Page 2

| / <b>-</b> 4 \ | <b>-</b>                                |                  |                                      | 0.004.000                    | D.4         | 4 (2.0.4.5        |                                   |

|----------------|-----------------------------------------|------------------|--------------------------------------|------------------------------|-------------|-------------------|-----------------------------------|

| (51)           | Int. Cl.                                |                  | (AAAA                                | 9,324,398                    |             |                   | Jones et al.                      |

|                | G11C 15/04                              |                  | (2006.01)                            | 9,384,821<br>9,390,782       |             |                   | Bains et al.<br>Best et al.       |

|                | G11C 11/16                              |                  | (2006.01)                            | 9,330,782                    |             |                   | Narui et al.                      |

|                | G11C 11/4074                            |                  | (2006.01)                            | 9,424,907                    |             |                   | Fujishiro                         |

| (52)           | U.S. Cl.                                |                  |                                      | 9,484,079                    |             | 11/2016           | •                                 |

|                | CPC <i>G1</i>                           |                  | /406 (2013.01); G11C 11/4074         | 9,514,850                    |             | 12/2016           |                                   |

|                |                                         | (201)            | 3.01); <i>G11C 15/043</i> (2013.01)  | 9,570,143                    |             |                   | Lim et al.                        |

| ( <b></b>      |                                         |                  |                                      | 9,646,672<br>9,672,889       |             |                   | Kim et al.<br>Lee et al.          |

| (56)           | R                                       | keferen          | ces Cited                            | 9,685,240                    |             | 6/2017            |                                   |

|                | II C DA                                 | TENT             | DOCUMENTS                            | 9,691,466                    |             | 6/2017            | _                                 |

|                | U.S. IA                                 | XIIDINI          | DOCUMENTS                            | 9,697,913                    |             | 7/2017            | Mariani et al.                    |

|                | 5,291,198 A                             | 3/1994           | Dingwall et al.                      | 9,734,887                    |             | 8/2017            |                                   |

|                |                                         |                  | Balistreri et al.                    | 9,741,409<br>9,741,447       |             |                   | Jones et al.<br>Akamatsu          |

|                |                                         |                  | Sukegawa et al.                      | 9,747,971                    |             |                   | Bains et al.                      |

|                | , ,                                     | 6/1997<br>2/1007 |                                      | 9,761,297                    |             |                   | Tomishima                         |

|                | 5,699,297 A 17<br>5,768,196 A 6         |                  | Yamazaki et al.<br>Bloker et al      | 9,786,351                    | B2          | 10/2017           | Lee et al.                        |

|                | 5,933,377 A                             |                  |                                      | 9,799,391                    |             | 10/2017           |                                   |

|                | 5,943,283 A                             |                  |                                      | 9,805,782                    |             | 10/2017           |                                   |

|                | 5,970,507 A 10                          |                  | Kato et al.                          | 9,805,783<br>9,818,469       |             |                   | Kim et al.                        |

|                | / /                                     | 2/1999           |                                      | 9,847,118                    |             |                   |                                   |

|                | 6,002,629 A 17<br>6,011,734 A           |                  | Rim et al.<br>Pappert                | , ,                          |             |                   | Bains et al.                      |

|                |                                         |                  | Shirley                              | 9,865,328                    |             |                   | Desimone et al.                   |

|                |                                         | 4/2001           | •                                    | 9,922,694                    |             |                   | Akamatsu<br>Daing et al           |

|                | 6,310,806 B1 10                         | 0/2001           | Higashi et al.                       | 9,934,143<br>9,953,696       |             | 4/2018            | Bains et al.                      |

|                | ,                                       |                  | Gans et al.                          | 10,032,501                   |             |                   | Ito et al.                        |

|                | , ,                                     |                  | Towler et al.<br>Chen et al.         | 10,083,737                   | B2          | 9/2018            | Bains et al.                      |

|                | , ,                                     |                  | Ooishi                               | 10,090,038                   |             | 10/2018           |                                   |

|                | , ,                                     | 8/2002           |                                      | 10,134,461                   |             |                   | Bell et al. Jones et al.          |

|                | , ,                                     | 9/2002           |                                      | 10,153,031                   |             |                   | Akamatsu                          |

|                | , ,                                     |                  | Buti et al.                          | 10,170,174                   |             |                   | Ito et al.                        |

|                |                                         | 3/2003<br>9/2005 | Nataraj et al.<br>Kim                | 10,176,860                   |             |                   | Mylavarapu                        |

|                |                                         |                  | Sinha et al.                         | 10,210,925                   |             |                   | Bains et al.<br>Moon et al.       |

|                |                                         |                  | Fiscus et al.                        | 10,297,305<br>10,339,994     |             |                   | Ito et al.                        |

|                |                                         | 7/2006           |                                      | 10,381,327                   |             |                   | Ramachandra et al.                |

|                | , ,                                     |                  | Koshikawa et al.<br>Takahashi et al. | 10,387,276                   |             |                   | Ryu et al.                        |

|                |                                         |                  | Eto et al.                           | 10,446,216                   |             |                   | Oh et al.                         |

|                | 7,209,402 B2                            |                  | Shinozaki et al.                     | 10,490,251<br>10,600,462     |             | 11/2019<br>3/2020 | Augustine et al.                  |

|                | , ,                                     | 5/2007           |                                      | 10,600,491                   |             |                   | Chou et al.                       |

|                | 7,283,380 B1 10                         |                  | Srinivasan et al.<br>Lien G11C 15/00 | 10,607,686                   | B2          | 3/2020            | Akamatsu                          |

|                | 7,50 <del>4</del> ,675 D1 17            | 2/2007           | 365/49.1                             | 10,629,286                   |             |                   | Lee et al.                        |

|                | 7,319,602 B1                            | 1/2008           | Srinivasan et al.                    | 10,679,710<br>10,705,900     |             | 6/2020<br>7/2020  | Hirashima et al.                  |

|                | 7,444,577 B2 10                         |                  |                                      | , ,                          |             |                   | Shore et al.                      |

|                | ,                                       |                  | Dono et al.                          | , ,                          |             |                   | Jones et al.                      |

|                | 7,565,479 B2 <i>1</i> ,7,830,742 B2 1.  | 1/2009<br>1/2010 |                                      |                              |             |                   | Penney G11C 29/783                |

|                | 7,870,362 B2                            |                  |                                      | , ,                          |             |                   | Jones et al.                      |

|                |                                         |                  | Okayama et al.                       | 10,867,660<br>10,930,335     |             |                   |                                   |

|                | , ,                                     |                  | Kim et al.                           | 10,943,636                   |             |                   | Wu et al.                         |

|                |                                         | 3/2013<br>5/2013 | Yoko<br>Okahiro et al.               | 10,950,289                   |             |                   | Ito et al.                        |

|                | , ,                                     |                  | Iwamoto et al.                       | 10,964,378                   |             |                   | Ayyapureddi G11C 11/1657          |

|                | / /                                     |                  | Lin et al.                           | 11,011,215<br>11,043,254     |             |                   | Parry et al.<br>Enomoto et al.    |

|                | , ,                                     | 3/2014           |                                      | 11,139,015                   |             |                   | Brown et al.                      |

|                | , ,                                     |                  | Best et al.                          | , ,                          |             |                   | Morohashi et al.                  |

|                | 8,811,100 B2<br>8,862,973 B2 10         | 8/2014<br>0/2014 |                                      |                              |             |                   | Penney et al.                     |

|                | 8,938,573 B2                            |                  |                                      |                              |             |                   | Penney et al.<br>Jenkinson et al. |

|                | 9,032,141 B2                            |                  |                                      | , ,                          |             |                   | Enomoto et al.                    |

|                | , , , , , , , , , , , , , , , , , , , , |                  | Bell et al.                          | 11,257,535                   |             |                   | Shore et al.                      |

|                | ·                                       | 6/2015<br>7/2015 | Kang<br>Park                         | 11,264,096                   | B2          | 3/2022            | Schreck et al.                    |

|                | / /                                     |                  | Youn et al.                          | 11,322,192                   |             |                   | Morohashi et al.                  |

|                | 9,117,544 B2                            |                  |                                      | 11,361,808                   |             |                   | Bell et al.                       |

|                | 9,123,447 B2                            |                  |                                      | 2001/0008498<br>2002/0007476 |             | 7/2001<br>1/2002  | Coishi<br>Kishino                 |

|                | 9,153,294 B2 10                         |                  |                                      | 2002/0007470                 |             |                   | Matsuzaki et al.                  |

|                | 9,190,137 B2 1,<br>9,190,139 B2 1,      |                  |                                      | 2002/0080677                 |             |                   | Watanabe et al.                   |

|                | 9,251,885 B2                            |                  | •                                    | 2002/0181301                 |             | 12/2002           | Takahashi et al.                  |

|                | 9,286,964 B2                            | 3/2016           | Halbert et al.                       | 2003/0063512                 |             |                   | Takahashi et al.                  |

|                | , ,                                     |                  | Chun et al.                          | 2003/0067825<br>2003/0090400 |             | 4/2003<br>5/2003  | Shimano et al.                    |

|                | 9,311,985 B2                            | 7/2010           | LCC Ct al.                           | 200 <i>3/</i> 0030400        | $\Lambda$ 1 | 5/2003            | Dairei                            |

## US 11,568,918 B2 Page 3

| (56)                                | References Cited                          |           | 2011/0317462                 | A1*        | 12/2011            | Gyllenhammer                      | G11C 15/04<br>365/49.17 |

|-------------------------------------|-------------------------------------------|-----------|------------------------------|------------|--------------------|-----------------------------------|-------------------------|

| U.S. 1                              | PATENT DOCUMEN                            | NTS       | 2012/0014199                 |            | 1/2012             |                                   | 303/42.17               |

| 2002/0122201 4.1                    | 7/2002 I 4 1                              |           | 2012/0059984<br>2012/0151131 |            |                    | Kang et al.<br>Kilmer et al.      |                         |

| 2003/0123301 A1<br>2003/0193829 A1  | 7/2003 Jang et al. 10/2003 Morgan et al.  | 1         | 2012/0131131                 |            |                    | Riho et al.                       |                         |

|                                     | 12/2003 Violgan et al.                    | L•        | 2012/0254472                 |            |                    | Ware et al.                       |                         |

| 2004/0004856 A1                     | 1/2004 Sakimura et                        | al.       | 2013/0003467                 |            | 1/2013             |                                   |                         |

| 2004/0008544 A1                     |                                           | al.       | 2013/0003477<br>2013/0057173 |            |                    | Park et al.                       |                         |

| 2004/0022093 A1<br>2004/0052142 A1  | 2/2004 Lee<br>3/2004 Ikehashi et a        | .1        | 2013/003/1/3                 |            |                    | Yao et al.<br>Kavalipurapu et al. |                         |

| 2004/0032142 A1<br>2004/0114446 A1  | 6/2004 Takahashi et                       |           | 2013/0173971                 |            |                    | Zimmerman                         |                         |

| 2004/0130959 A1                     | 7/2004 Kawaguchi                          |           | 2013/0254475                 |            |                    | Perego et al.                     |                         |

| 2004/0174757 A1                     | 9/2004 Garverick et                       | al.       | 2013/0279284                 |            | 10/2013            | •                                 |                         |

| 2004/0184323 A1<br>2004/0213035 A1  | 9/2004 Mori et al. 10/2004 Cavaleri et a  | .1        | 2013/0304982 2014/0006703    |            |                    | Jung et al.<br>Bains et al.       |                         |

|                                     | 11/2004 Cavaler et al.                    |           | 2014/0006704                 |            |                    | Greenfield et al.                 |                         |

| 2005/0041502 A1                     | 2/2005 Perner                             |           | 2014/0013169                 |            |                    | Kobla et al.                      |                         |

| 2005/0105315 A1                     |                                           |           | 2014/0013185<br>2014/0050004 |            |                    | Kobla et al.<br>Mochida           |                         |

|                                     | 11/2005 Lee<br>12/2005 Remaklus et        | ล1        | 2014/0078841                 |            |                    | Chopra                            |                         |

| 2006/0083099 A1                     | 4/2006 Bae et al.                         | ar.       | 2014/0078842                 |            |                    | Oh et al.                         |                         |

| 2006/0087903 A1                     | 4/2006 Riho et al.                        |           | 2014/0078845                 |            | 3/2014             | •                                 |                         |

| 2006/0176744 A1                     |                                           |           | 2014/0089576<br>2014/0095780 |            |                    | Bains et al.<br>Bains et al.      |                         |

| 2006/0262616 A1<br>2007/0008799 A1  | 11/2006 Chen<br>1/2007 Done et al.        |           | 2014/0095786                 |            |                    | Moon et al.                       |                         |

| 2007/0014174 A1                     | 1/2007 Ohsawa                             |           | 2014/0119091                 |            |                    | You et al.                        |                         |

| 2007/0028068 A1                     | 2/2007 Golding et a                       | 1.        | 2014/0136763                 |            |                    | Li et al.                         |                         |

| 2007/0030746 A1<br>2007/0033339 A1  | 2/2007 Best et al. 2/2007 Best et al.     |           | 2014/0143473<br>2014/0177370 |            |                    | Kim et al.<br>Halbert et al.      |                         |

| 2007/0033339 A1<br>2007/0133330 A1  | 6/2007 Ohsawa                             |           | 2014/0177376                 |            | 6/2014             |                                   |                         |

| 2007/0230264 A1                     | 10/2007 Eto                               |           | 2014/0189215                 |            |                    | Kang et al.                       |                         |

|                                     | 10/2007 Miyamoto et                       | t al.     | 2014/0189228<br>2014/0219043 |            |                    | Greenfield et al.<br>Jones et al. |                         |

| 2007/0297252 A1<br>2008/0028260 A1  | 12/2007 Singh<br>1/2008 Oyagi et al.      |           | 2014/0219043                 |            |                    | Kobla et al.                      |                         |

| 2008/0023266 A1                     | 2/2008 Yoo et al.                         |           | 2014/0241099                 | A1         |                    | Seo et al.                        |                         |

| 2008/0062742 A1                     | 3/2008 Wang                               | _         | 2014/0254298                 |            | 9/2014             | -                                 |                         |

| 2008/0126893 A1                     |                                           | 1.        | 2014/0269021<br>2014/0281206 |            |                    | Yang et al.<br>Crawford et al.    |                         |

| 2008/0130394 A1<br>2008/0181048 A1  | 6/2008 Done et al.<br>7/2008 Han          |           | 2014/0281207                 |            |                    | Mandava et al.                    |                         |

| 2008/0224742 A1                     | 9/2008 Pomichter                          |           | 2014/0292375                 |            |                    | Angelini et al.                   |                         |

|                                     | 10/2008 Iida et al.                       |           | 2014/0293725<br>2014/0317344 |            | 10/2014<br>10/2014 | Best et al.                       |                         |

|                                     | 10/2008 Loeffler<br>11/2008 Atwal et al.  |           | 2014/0317344                 |            |                    | Youn et al.                       |                         |

|                                     | 12/2008 Atwar et al.<br>12/2008 Cavanna   | G06F 7/74 | 2014/0369109                 | A1         |                    | Lee et al.                        |                         |

|                                     |                                           | 711/108   | 2014/0379978                 |            |                    | Kim et al.                        |                         |

|                                     | 12/2008 Hummler et 12/2008 Wang et al.    | al.       | 2015/0049567<br>2015/0055420 |            | 2/2015<br>2/2015   | Bell et al.                       |                         |

| 2008/0310843 A1<br>2009/0021999 A1  | 1/2008 wang et al.<br>1/2009 Tanimura et  | al.       | 2015/0078112                 |            |                    | Huang                             |                         |

| 2009/0059641 A1                     | 3/2009 Jeddeloh                           |           | 2015/0089326                 |            |                    | Joo et al.                        |                         |

| 2009/0077571 A1                     |                                           |           | 2015/0155027<br>2015/0162067 |            |                    | Abe et al.<br>Kim et al.          |                         |

| 2009/0161457 A1<br>2009/0168571 A1  | 6/2009 Wakimoto 7/2009 Pyo et al.         |           | 2015/0170728                 |            |                    | Jung et al.                       |                         |

| 2009/0185440 A1                     | 7/2009 Lee                                |           | 2015/0199126                 |            | 7/2015             | Jayasena et al.                   |                         |

| 2009/0201752 A1                     | 8/2009 Riho et al.                        |           | 2015/0206572<br>2015/0213872 |            |                    | Lim et al.<br>Mazumder et al.     |                         |

| 2009/0213675 A1<br>2009/0251971 A1  | 8/2009 Shino                              |           | 2015/0213872                 |            | 7/2015             |                                   |                         |

| 2009/0231971 A1<br>2009/0296510 A1  | 10/2009 Futatsuyama 12/2009 Lee et al.    | •         | 2015/0228341                 |            |                    | Watanabe et al.                   |                         |

| 2010/0005217 A1                     | 1/2010 Jeddeloh                           |           | 2015/0243339                 |            |                    | Bell et al.                       |                         |

| 2010/0005376 A1                     | 1/2010 Laberge et a                       | 1.        | 2015/0255140<br>2015/0262652 |            | 9/2015<br>9/2015   | Song<br>Igarashi                  |                         |

| 2010/0054011 A1                     | 3/2010 Kim                                |           | 2015/0279441                 |            |                    | Greenberg et al.                  |                         |

| 2010/0074042 A1<br>2010/0080074 A1  | 3/2010 Fukuda et al<br>4/2010 Ohmaru et a |           | 2015/0279442                 |            | 10/2015            | •                                 |                         |

| 2010/0000071 A11<br>2010/0110809 A1 | 5/2010 Kobayashi e                        |           | 2015/0294711<br>2015/0340077 |            |                    | Gaither et al.<br>Akamatsu        |                         |

| 2010/0110810 A1                     | 5/2010 Kobayashi                          |           | 2015/0340077                 |            |                    |                                   |                         |

| 2010/0131812 A1                     | 5/2010 Mohammad                           |           | 2016/0019940                 | A1         | 1/2016             | Jang et al.                       |                         |

| 2010/0157693 A1                     | 6/2010 Iwai et al.                        |           | 2016/0027498                 |            |                    | Ware et al.                       |                         |

| 2010/0182863 A1<br>2010/0329069 A1  | 7/2010 Fukiage 12/2010 Ito et al.         |           | 2016/0027531<br>2016/0027532 |            | 1/2016             | Jones et al.<br>Kim               |                         |

| 2011/0026290 A1                     | 2/2010 Ro et al.                          |           | 2016/0042782                 |            |                    | Narui et al.                      |                         |

| 2011/0051530 A1                     | 3/2011 Kushida                            |           | 2016/0078845                 |            |                    | Lin et al.                        |                         |

| 2011/0055495 A1                     | 3/2011 Remaklus, J.                       | r. et al. | 2016/0078911                 |            |                    | Fujiwara et al.                   |                         |

| 2011/0069572 A1<br>2011/0122987 A1  | 3/2011 Lee et al. 5/2011 Neyer            |           | 2016/0078918<br>2016/0086649 |            |                    | Hyun et al.<br>Heng et al.        |                         |

| 2011/0122567 A1<br>2011/0216614 A1  | 9/2011 Hosoe                              |           | 2016/0086651                 |            | 3/2016             | . •                               |                         |

| 2011/0225355 A1                     | 9/2011 Kajigaya                           |           | 2016/0093402                 | <b>A</b> 1 | 3/2016             | Kitagawa et al.                   |                         |

| 2011/0286271 A1                     |                                           | 1         | 2016/0099043                 |            | 4/2016             | _                                 |                         |

| 2011/0310648 Al                     | 12/2011 Iwamoto et a                      | a1.       | 2016/0111140                 | Al         | 4/2016             | Joo et al.                        |                         |

## US 11,568,918 B2 Page 4

| (56)                               | Reference                   | es Cited                       | 2019/0207                           |          |                  | Ben-Tovim et al.                                |

|------------------------------------|-----------------------------|--------------------------------|-------------------------------------|----------|------------------|-------------------------------------------------|

| U.S                                | . PATENT I                  | OCUMENTS                       | 2019/0228<br>2019/0228<br>2019/0228 | 813 A1   | 7/2019           | Jones et al.<br>Nale et al.<br>Morohashi et al. |

| 2016/0125021 4.1                   | 5/2016 T                    | D4-1                           | 2019/0228                           |          |                  | Morohashi                                       |

| 2016/0125931 A1<br>2016/0133314 A1 | 5/2016 I<br>5/2016 F        | Hwang et al.                   | 2019/0243                           |          |                  | Cha et al.                                      |

| 2016/0140243 A1                    |                             | Adams et al.                   | 2019/0252                           |          |                  | Rios et al.                                     |

| 2016/0163372 A1                    | 6/2016 I                    | Lee et al.                     | 2019/0267                           |          |                  | Ito et al.                                      |

| 2016/0172056 A1                    | 6/2016 H                    |                                | 2019/0279°<br>2019/0333             |          | 9/2019           | Shin et al.                                     |

| 2016/0180917 A1                    |                             | Chishti et al.                 | 2019/0333                           |          |                  | Smith et al.                                    |

| 2016/0180921 A1<br>2016/0196863 A1 | 6/2016 J<br>7/2016 S        | ~                              |                                     |          |                  | Smith et al.                                    |

| 2016/0202926 A1                    | 7/2016 E                    |                                | 2019/0348                           | 103 A1   | 11/2019          | Jeong et al.                                    |

| 2016/0211008 A1                    | 7/2016 E                    | Benedict et al.                | 2019/0348                           |          |                  | Shin et al.                                     |

| 2016/0225433 A1                    |                             | Bains et al.                   | 2019/0349                           |          |                  | Koh et al.<br>Kuramorl et al.                   |

| 2016/0225461 A1<br>2016/0336060 A1 |                             | Tuers et al.                   | 2019/0302                           |          |                  | Cha et al.                                      |

| 2016/0330000 A1<br>2016/0343423 A1 |                             |                                | 2019/0385                           |          |                  | Koo et al.                                      |

| 2017/0011792 A1                    |                             |                                | 2019/0385                           |          |                  | Morohashi et al.                                |

| 2017/0076779 A1                    |                             | Bains et al.                   | 2019/0386                           |          |                  | Wang et al.                                     |

| 2017/0092350 A1                    |                             | Halbert et al.                 | 2020/0005<br>2020/0075              |          |                  | Ito et al.<br>Tokutomi et al.                   |

| 2017/0117030 A1<br>2017/0133085 A1 |                             | Fisch et al.<br>Zim et al      | 2020/0073                           |          | 3/2020           |                                                 |

| 2017/0133063 A1<br>2017/0139641 A1 |                             |                                | 2020/0090                           | 760 A1   | 3/2020           | Purahmad et al.                                 |

| 2017/0140807 A1                    |                             |                                | 2020/0135                           |          |                  | Brown et al.                                    |

| 2017/0140811 A1                    | 5/2017 J                    |                                | 2020/0194                           |          |                  | Akamatsu<br>Salaurai et al                      |

| 2017/0148504 A1                    |                             | Saifuddin et al.               | 2020/01940<br>2020/02013            |          |                  | Sakurai et al.<br>Murali et al.                 |

| 2017/0177246 A1<br>2017/0186481 A1 |                             | Miller et al.<br>Oh et al      | 2020/02029                          |          |                  | Morohashi et al.                                |

| 2017/0130431 A1<br>2017/0213586 A1 |                             |                                | 2020/0211                           | 626 A1   |                  | Hiscock et al.                                  |

| 2017/0221546 A1                    |                             |                                | 2020/0211                           |          |                  | Okuma                                           |

| 2017/0263305 A1                    |                             |                                | 2020/0211                           |          |                  | Hiscock et al.                                  |

| 2017/0287547 A1                    | 10/2017 I                   | _                              | 2020/0251<br>2020/0294              |          |                  | Shore et al.<br>Brown et al.                    |

| 2017/0323675 A1<br>2017/0352399 A1 |                             | Yokoyama et al.                | 2020/03029                          |          |                  | Enomoto et al.                                  |

| 2017/0332333 A1<br>2017/0371742 A1 |                             | •                              | 2020/0321                           | 049 A1   |                  | Meier et al.                                    |

| 2017/0372767 A1                    |                             |                                |                                     |          |                  | Shore et al.                                    |

| 2018/0005690 A1                    | 1/2018 N                    | Morgan et al.                  |                                     |          |                  | Schreck                                         |

| 2018/0025770 A1                    | 1/2018 I                    |                                |                                     |          |                  | Penney et al. Penney G11C 15/04                 |

| 2018/0025772 A1<br>2018/0060194 A1 |                             |                                |                                     |          |                  | Hiscock et al.                                  |

| 2018/006134 A1                     |                             | •                              | 2021/0005                           |          |                  | Brown et al.                                    |

| 2018/0082737 A1                    |                             |                                | 2021/0020                           |          |                  | Ayyapureddi et al.                              |

| 2018/0084314 A1                    |                             | _ <b>-</b>                     | 2021/0020<br>2021/0026              |          |                  | Penney et al.<br>Park et al.                    |

| 2018/0090199 A1                    |                             | Kim et al.<br>Fomishima et al. | 2021/0020                           |          |                  | Ayyapureddi et al.                              |

| 2018/0096719 A1<br>2018/0102776 A1 |                             | Chandrasekar et al.            | 2021/0057                           |          |                  | Jenkinson et al.                                |

| 2018/0107417 A1                    |                             | Shechter et al.                | 2021/0057                           |          |                  | Wu G11C 11/40603                                |

| 2018/0114561 A1                    | 4/2018 F                    | Fisch et al.                   | 2021/0065                           |          |                  | Kim et al.                                      |

| 2018/0114565 A1                    |                             |                                | 2021/0065°<br>2021/0142°            |          |                  | Cheng et al. Schreck et al.                     |

| 2018/0158504 A1<br>2018/0182445 A1 | 6/2018 <i>A</i><br>6/2018 I |                                | 2021/0142                           |          |                  | Wu et al.                                       |

| 2018/0182443 A1<br>2018/0203621 A1 |                             |                                | 2021/0158                           | 861 A1   |                  | Jeong et al.                                    |

| 2018/0218767 A1                    |                             |                                | 2021/02019                          |          |                  | Khasawneh et al.                                |

| 2018/0261268 A1                    |                             | Hyun et al.                    | 2021/0225                           |          |                  | Enomoto et al.                                  |

| 2018/0294028 A1                    |                             |                                | 2021/0241<br>2021/0265              |          |                  | Hollis et al.<br>Ishizu et al.                  |

| 2018/0308539 A1<br>2018/0341553 A1 |                             | to et ar.<br>Koudele et al.    | 2021/0343                           |          |                  | Brown et al.                                    |

| 2018/0341333 A1<br>2018/0366182 A1 |                             | _                              | 2021/0350                           | 844 A1   | 11/2021          | Morohashi et al.                                |

| 2019/0013059 A1                    |                             |                                | 2021/0398                           |          |                  | Penney et al.                                   |

| 2019/0043558 A1                    |                             |                                | 2021/0407                           |          |                  | Penney et al.                                   |

| 2019/0051344 A1                    |                             |                                | 2022/0165                           | 347 AI   | 5/2022           | Pan                                             |

| 2019/0066759 A1<br>2019/0066762 A1 |                             |                                |                                     | EODEIC   | NI DATE          | NIT DOCI IN ADNITO                              |

| 2019/0088315 A1                    |                             | Saenz et al.                   |                                     | FOREIG   | N PAIE           | NT DOCUMENTS                                    |

| 2019/0088316 A1                    |                             | nuzuka et al.                  | CN                                  | 101038   | 3785 A           | 9/2007                                          |

| 2019/0096492 A1                    | 3/2019                      | _                              | CN                                  |          | 7972 A           | 11/2007                                         |

| 2019/0103147 A1<br>2019/0130961 A1 |                             | lones et al.<br>Rell et al     | CN                                  |          | 1554 A           | 12/2008                                         |

| 2019/0130961 A1<br>2019/0139599 A1 | 5/2019 E<br>5/2019 E        |                                | CN                                  |          | 3658 A           | 6/2009                                          |

| 2019/0139399 A1<br>2019/0147941 A1 |                             |                                | CN<br>CN                            |          | 2607 A<br>3058 A | 1/2010<br>6/2011                                |

| 2019/0147964 A1                    | 5/2019                      |                                | CN<br>CN                            |          | 8952 A           | 5/2011                                          |

| 2019/0161341 A1                    | 5/2019 H                    |                                | CN                                  |          | )546 A           | 2/2015                                          |

| 2019/0172518 A1                    |                             | Chen et al.                    | CN                                  |          | 0621 A           | 5/2017                                          |

| 2019/0196730 A1<br>2019/0198078 A1 | 6/2019 I                    |                                | CN                                  |          | 1516 A           | 4/2018                                          |

| 2019/0198078 A1<br>2019/0198090 A1 | 6/2019 I                    | Hoang et al.<br>Lee            | JP<br>JP                            | H0773    | 3682 A<br>5429 A | 3/1995<br>8/2005                                |

| 2019/0198099 A1                    |                             | Mirichigni et al.              | JP                                  | 2003-210 |                  | 12/2011                                         |

| 2019/0205253 A1                    |                             |                                | JP                                  |          | 1510 B2          | 1/2012                                          |

|                                    |                             |                                |                                     |          |                  |                                                 |

| (56) | References Cited |              |  |  |  |  |

|------|------------------|--------------|--|--|--|--|

|      | FOREIGN PATEN    | IT DOCUMENTS |  |  |  |  |

| JP   | 2013-004158 A    | 1/2013       |  |  |  |  |

| KR   | 20150002112 A    | 1/2015       |  |  |  |  |

| KR   | 20150002783 A    | 1/2015       |  |  |  |  |

| KR   | 20170058022 A    | 5/2017       |  |  |  |  |

| KR   | 1020180064940 A  | 6/2018       |  |  |  |  |

| KR   | 1020180085184 A  | 7/2018       |  |  |  |  |

| KR   | 20190048049 A    | 5/2019       |  |  |  |  |

| WO   | 2014120477       | 8/2014       |  |  |  |  |

| WO   | 2015030991 A1    | 3/2015       |  |  |  |  |

| WO   | 2017171927 A1    | 10/2017      |  |  |  |  |

| WO   | 2019222960 A1    | 11/2019      |  |  |  |  |

| WO   | 2020191222 A1    | 9/2020       |  |  |  |  |

| WO   | 2022108808 A1    | 5/2022       |  |  |  |  |

#### OTHER PUBLICATIONS

- U.S. Appl. No. 16/818,981 titled "Apparatuses and Methods for Staggered Timing of Targeted Refresh Operations", filed Mar. 13, 2020, pp. all.

- U.S. Appl. No. 16/824,460, titled "Semiconductor Device Performing Row Hammer Refresh Operation", filed Mar. 19, 2020, pp. all. U.S. Appl. No. 16/232,837, titled "Apparatuses and Methods for Distributed Targeted Refresh Operations", filed Dec. 26, 2018, pp. all.

- U.S. Appl. No. 16/818,989, titled "Semiconductor Device Performing Row Hammer Refresh Operation", filed Mar. 13, 2020, pp. all. U.S. Appl. No. 16/286,187 titled "Apparatuses and Methods for Memory Mat Refresh Sequencing", filed Feb. 26, 2019, pp. all.

- U.S. Appl. No. 16/084,119, titled "Apparatuses and Methods for Pure-Time, Self Adopt Sampling for Row Hammer Refresh Sampling", filed Sep. 11, 2018, pp. all.

- U.S. Appl. No. 16/375,716 titled "Apparatuses and Methods for Staggered Timing of Targeted Refresh Operations", filed Apr. 4, 2019; pp. all.

- U.S. Appl. No. 17/060,403 titled "Apparatuses and Methods for Adjusting Victim Data", filed Oct. 1, 2020, pp. all.

- U.S. Appl. No. 16/655,110 titled "Apparatuses and Methods for Dynamic Targeted Refresh Steals", filed Oct. 16, 2019, pp. all. International Application No. PCT/US19/64028, titled "Semiconductor Device Performing Row Hammer Refresh Operation", dated Dec. 2, 2019, pp. all.

- International Application No. PCT/US20/26689, titled "Apparatuses and Methods for Staggered Timing of Targeted Refresh Operations", dated Apr. 3, 2020, pp. all.

- U.S. Appl. No. 16/788,657, titled "Semiconductor Device Performing Row Hammer Refresh Operation", filed Feb. 12, 2020, pp. all. U.S. Appl. No. 17/153,555 titled "Apparatuses and Methods for Dynamically Allocated Aggressor Detection", filed Jan. 20, 2021, pp. all.

- U.S. Appl. No. 17/201,941 titled "Apparatuses and Methods for Sketch Circuits for Refresh Binning", filed Mar. 15, 2021, pp. all. U.S. Appl. No. 17/301,533 titled "Semiconductor Device Having Cam That Stores Address Signals", filed Apr. 6, 2021, pp. all.

- U.S. Appl. No. 16/208,217, titled "Semiconductor Device Performing Row Hammer Refresh Operation", filed Dec. 3, 2018, pp. all. U.S. Appl. No. 16/230,300, titled "Apparatuses and Methods for Staggered Timing of Targeted Refresh Operations", filed Dec. 21, 2018, pp. all.

- U.S. Appl. No. 16/290,730, titled "Semiconductor Device Performing Row Hammer Refresh Operation", filed Mar. 1, 2019, pp. all. U.S. Appl. No. 16/374,623, titled "Semiconductor Device Performing Row Hammer Refresh Operation", filed Apr. 3, 2019, pp. all. U.S. Appl. No. 16/431,641 titled "Apparatuses and Methods for Controlling Steal Rates", filed Jun. 4, 2019, pp. all.

- U.S. Appl. No. 16/459,507 titled "Apparatuses and Methods for Adjusting Victim Data", filed Jul. 1, 2019, pp. all.

- U.S. Appl. No. 16/783,063, titled "Apparatus and Methods for Triggering Row Hammer Address Sampling", filed Feb. 5, 2020.

- U.S. Appl. No. 16/268,818, titled "Apparatuses and Methods for Managing Row Access Counts", filed Feb. 6, 2019.

- U.S. Appl. No. 16/936,297 titled "Apparatuses and Methods for Managing Row Access Counts", filed Jul. 22, 2020.

- U.S. Appl. No. 16/546,152 titled "Apparatuses and Methods for Analog Row Access Tracking", filed Aug. 20, 2019.

- U.S. Appl. No. 16/548,027 titled "Apparatuses, Systems, and Methods for Analog Row Access Rate Determination", filed Aug. 22. 2019.

- U.S. Appl. No. 16/549,942 titled "Apparatuses and Methods for Lossy Row Access Counting", filed Aug. 23, 2019.

- U.S. Appl. No. 15/881,256 entitled 'Apparatuses and Methods for Detecting a Row Hammer Attack With a Bandpass Filter', filed Jan. 26, 2018.

- U.S. Appl. No. 16/425,525 titled "Apparatuses and Methods for Tracking All Row Accesses", filed May 29, 2019.

- U.S. Appl. No. 16/427,105 titled "Apparatuses and Methods for Priority Targeted Refresh Operations", filed May 30, 2019.

- U.S. Appl. No. 16/427,140 titled "Apparatuses and Methods for Tracking Row Access Counts Between Multiple Register Stacks", filed May 30, 2019.

- U.S. Appl. No. 16/537,981 titled "Apparatuses and Methods for Controlling Targeted Refresh Rates", filed Aug. 12, 2019.

- U.S. Appl. No. 17/154,945 titled "Apparatuses, Systems, and Methods for a Content Addressable Memory Cell", filed Jan. 21, 2021. U.S. Appl. No. 17/168,036 titled "Apparatuses and Methods for Analog Row Access Tracking", filed Feb. 4, 2021.

- U.S. Appl. No. 15/789,897, entitled "Apparatus and Methods for Refreshing Memory", filed Oct. 20, 2017; pp. all.

- U.S. Appl. No. 15/796,340, entitled: "Apparatus and Methods for Refreshing Memory", filed Oct. 27, 2017; pp. all.

- U.S. Appl. No. 16/237,291, titled "Apparatus and Methods for Refreshing Memory", filed Dec. 31, 2018.

- U.S. Appl. No. 16/427,330 titled "Apparatuses and Methods for Storing Victim Row Data", filed May 30, 2019.

- U.S. Appl. No. 16/549,411 titled "Apparatuses and Methods for Dynamic Refresh Allocation", filed Aug. 23, 2019.

- U.S. Appl. No. 17/102,266, titled "Apparatuses and Methods for Tracking Word Line Accesses", filed Nov. 23, 2020.

- PCT Application No. PCT/US18/55821 "Apparatus and Methods for Refreshing Memory" filed Oct. 15, 2018., pp. all.

- Kim, et al., "Flipping Bits in MemoryWithout Accessing Them: An Experimental Study of DRAM Disturbance Errors", IEEE, Jun. 2014, 12 pgs.

- Stout, Thomas et al., "Voltage Source Based Voltage-to-Time Converter", IEEE, downloaded Jul. 2020, p. All.

- U.S. Appl. No. 17/375,817 titled "Apparatuses and Methods for Monitoring Word Line Accesses", filed Jul. 14, 2021, pp. all.

- U.S. Appl. No. 17/443,056 titled "Apparatuses and Methods for Multiple Row Hammer Refresh Address Sequences", filed Jul. 20, 2021, pp. all.

- U.S. Appl. No. 17/007,069 titled "Apparatuses and Methods for Providing Refresh Addresses", filed Aug. 31, 2020, pp. all.

- U.S. Appl. No. 17/456,849 titled "Apparatuses, Systems, and Methods for Main Sketch and Slim Sketch Circuitfor Row Address Tracking", filed Nov. 29, 2021.

- U.S. Appl. No. 17/565,119 titled "Apparatuses and Methods for Row Hammer Counter Mat", filed Dec. 29, 2021.

- U.S. Appl. No. 17/565,187 titled "Apparatuses and Methods for Row Hammer Counter Mat", filed Dec. 29, 2021.

- U.S. Appl. No. 17/444,925 titled "Apparatuses and Methods for Countering Memory Attacks", filed Aug. 12, 2021, pp. all pages of application as filed.

- U.S. Appl. No. 17/446,710 titled "Apparatuses. Systems, and Methods for Determining Extremum Numerical Values", filed Sep. 1, 2021, pp. all pages of application as filed.

- U.S. Appl. No. 17/470,883 titled "Apparatuses and Methods for Tracking Victim Rows", filed Sep. 9, 2021, all pages of application as filed.

- U.S. Appl. No. 17/932,206, titled, "Apparatuses and Methods for Dynamically Allocated Aggressor Detection" filed Sep. 14, 2022; pp. all pages of application as filed.

### (56) References Cited

### OTHER PUBLICATIONS

U.S. Appl. No. 17/822,033, titled, "Apparatuses and Methods for Tracking Word Line Accesses" filed Aug. 24, 2022, pp. all pages of application as filed. [English Abstract] Zheng, Bin, et al., "Design of Built-in DRAM for TFT-LCD Driver Chip LCD and display," Issue 4, Aug. 15, 2009; pp. all.

<sup>\*</sup> cited by examiner

Company of the Compan

FIG. 4

Jan. 31, 2023

FIG. 6

# APPARATUSES, SYSTEMS, AND METHODS FOR ANALOG ACCUMULATOR FOR DETERMINING ROW ACCESS RATE AND TARGET ROW ADDRESS USED FOR REFRESH OPERATION

### CROSS-REFERENCE TO RELATED APPLICATION(S)

This application is a divisional of U.S. patent application Ser. No. 16/548,027 filed Aug. 22, 2019 and issued as U.S. Pat. No. 10,964,378 on Mar. 30, 2021. The aforementioned application, and issued patent, is incorporated herein by reference, in its entirety, for any purpose.

### **BACKGROUND**

Information may be stored on individual memory cells of the memory as a physical signal (e.g., a charge on a capacitive element). The memory may be a volatile memory, <sup>20</sup> and the physical signal may decay over time (which may degrade or destroy the information stored in the memory cells). It may be necessary to periodically refresh the information in the memory cells by, for example, rewriting the information to restore the physical signal to an initial value. <sup>25</sup>

As memory components have decreased in size, the density of memory cells has greatly increased. An autorefresh operation may be carried out where a sequence of memory cells are periodically refreshed. Repeated access to a particular memory cell or group of memory cells (often referred to as a 'row hammer') may cause an increased rate of data degradation in nearby memory cells. It may be desirable to identify and refresh memory cells affected by the row hammer in a targeted refresh operation in addition to the auto-refresh operation.

### BRIEF DESCRIPTION OF THE DRAWINGS

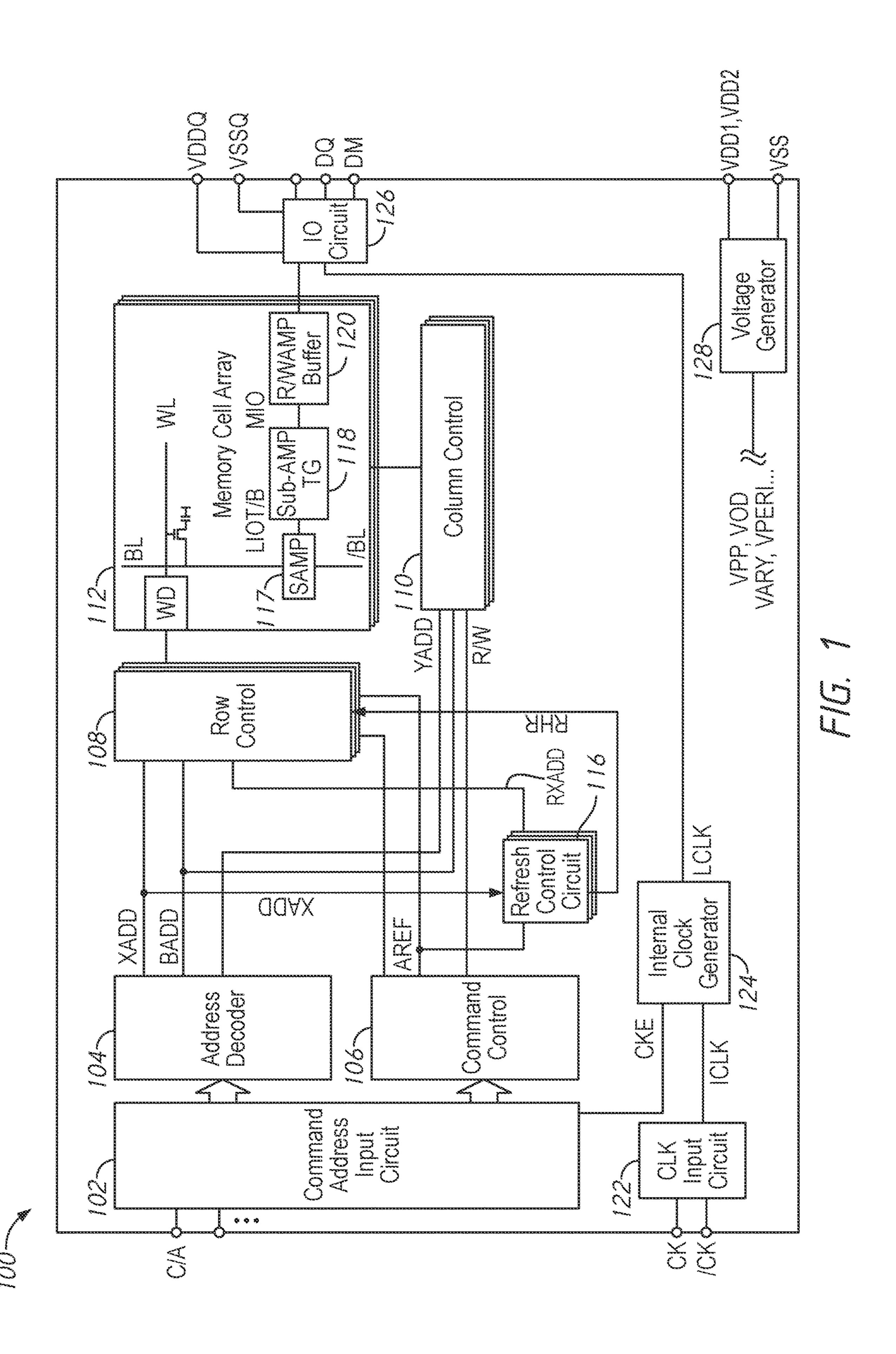

FIG. 1 is a block diagram of a semiconductor device according to at least one embodiment of the disclosure.

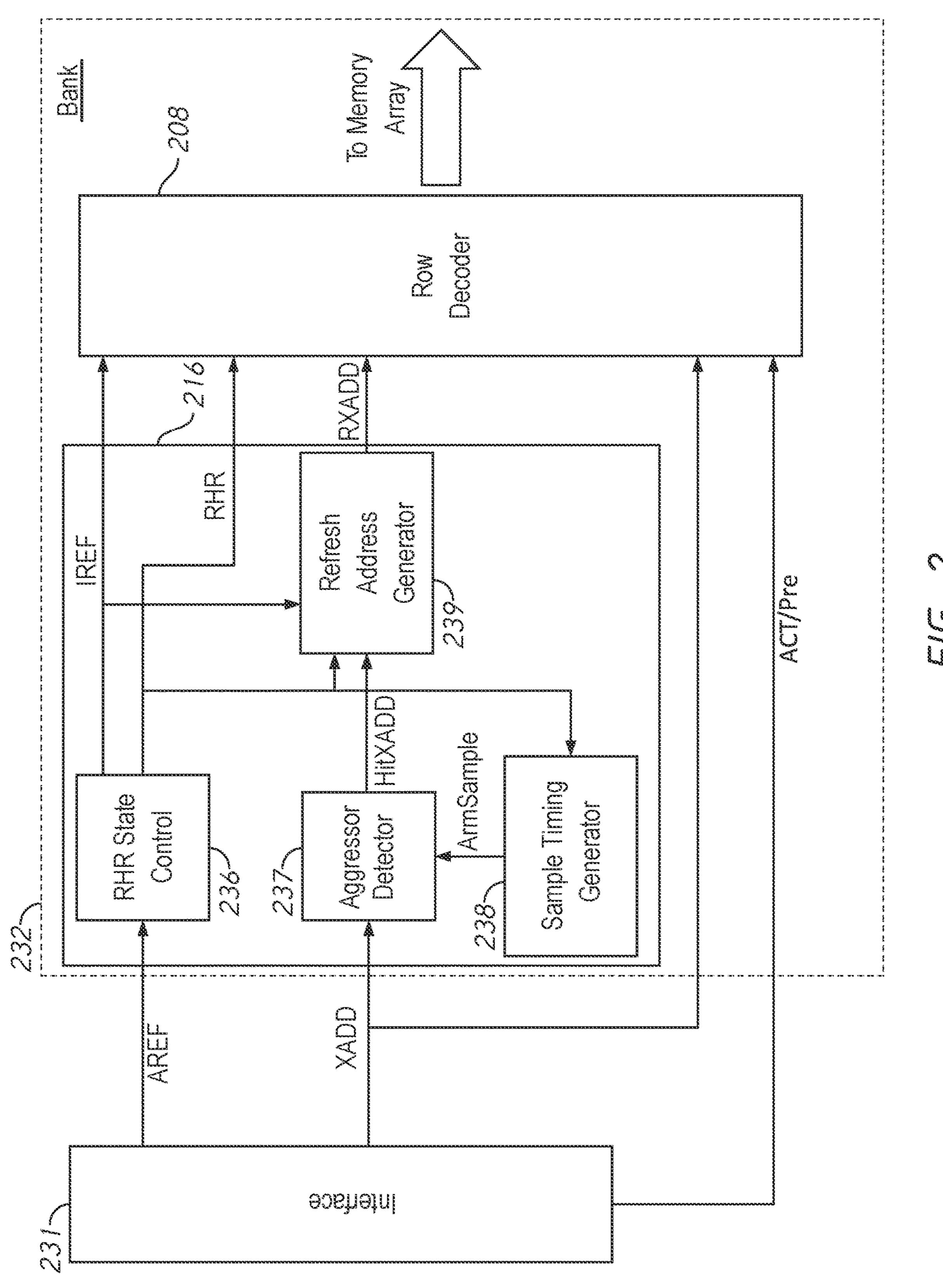

FIG. 2 is a block diagram of a refresh control circuit according to an embodiment of the present disclosure.

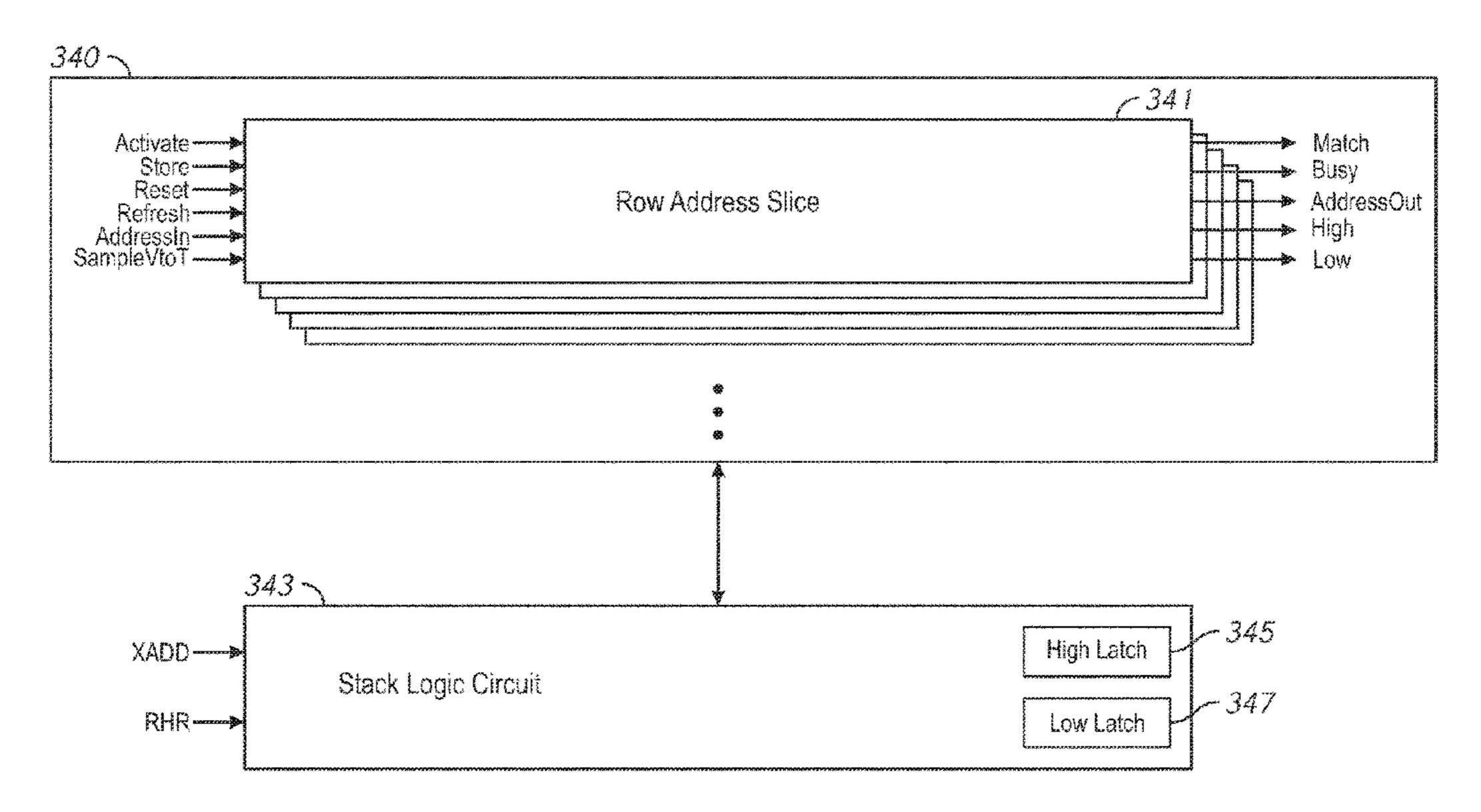

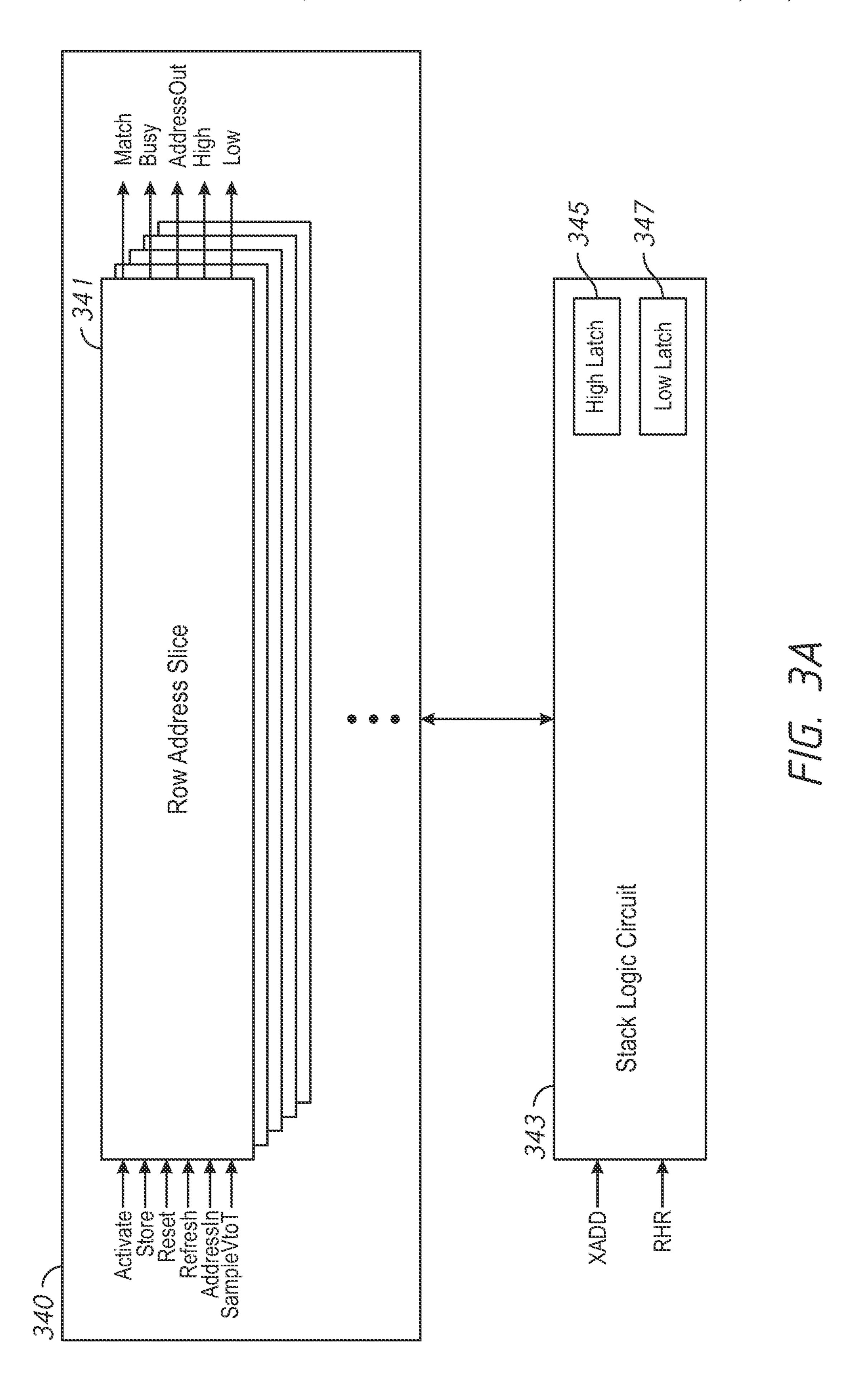

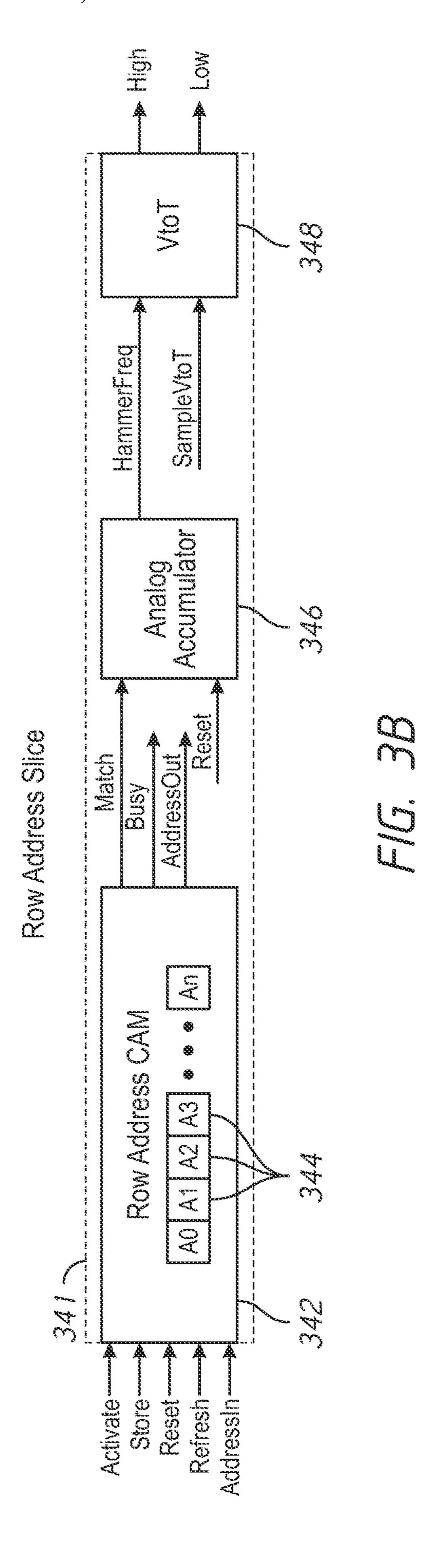

FIGS. 3A-3B are block diagrams of a stack and slices of the stack, respectively, according to an embodiment of the present disclosure.

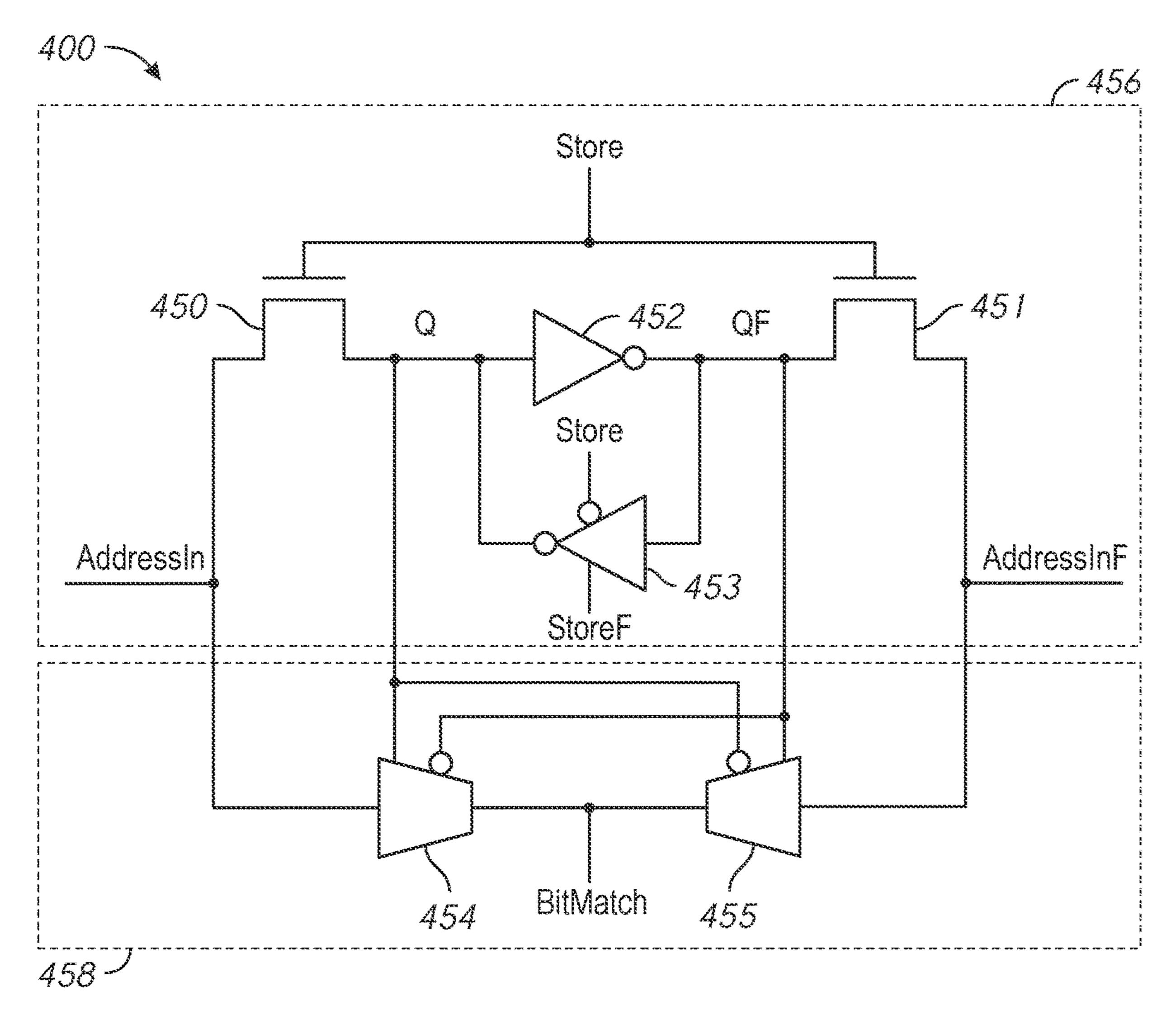

FIG. 4 is a schematic diagram of a content addressable memory (CAM) cell according to an embodiment of the present disclosure.

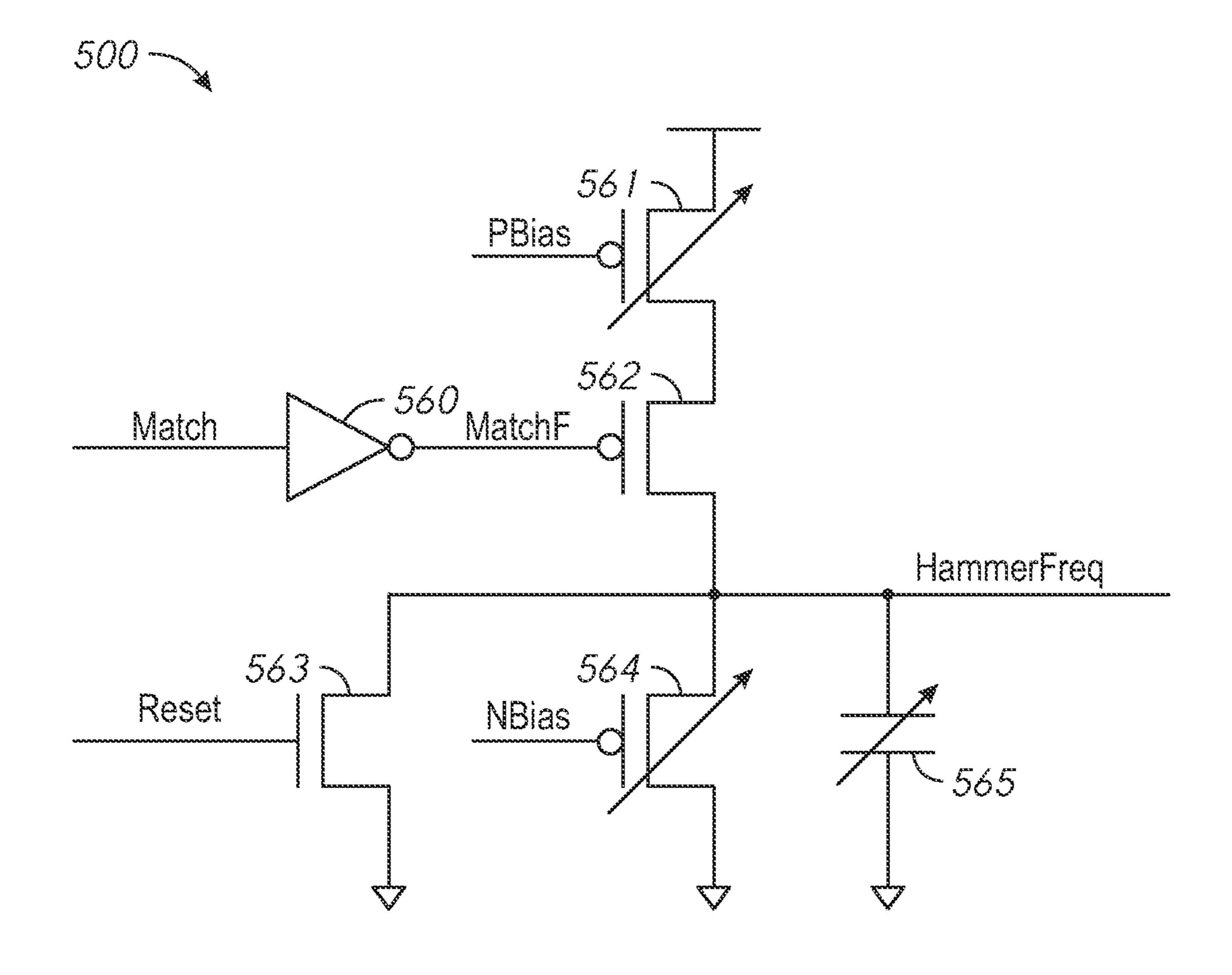

FIG. **5** is a schematic diagram of an example accumulator circuit according to an embodiment of the present disclo- 50 sure.

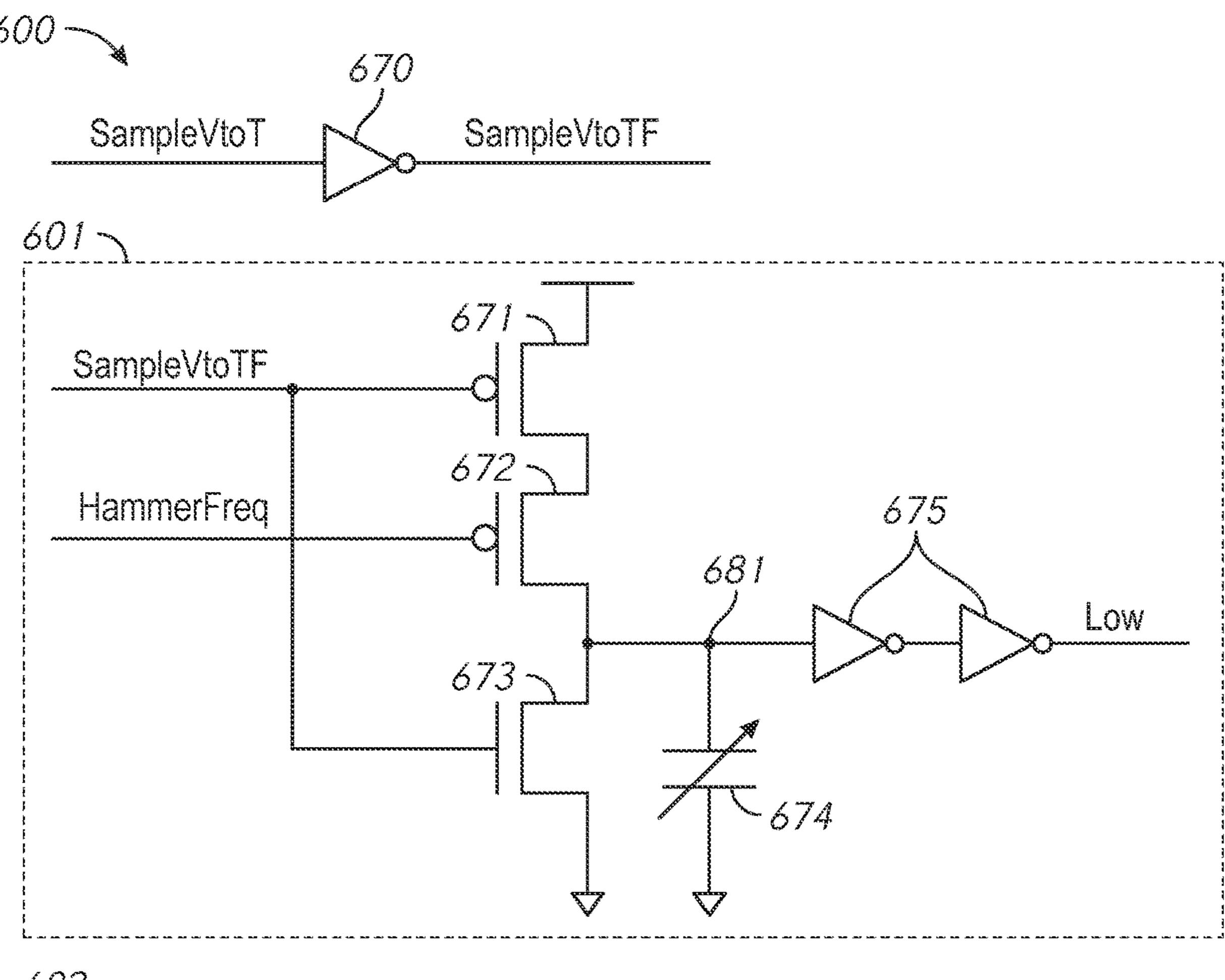

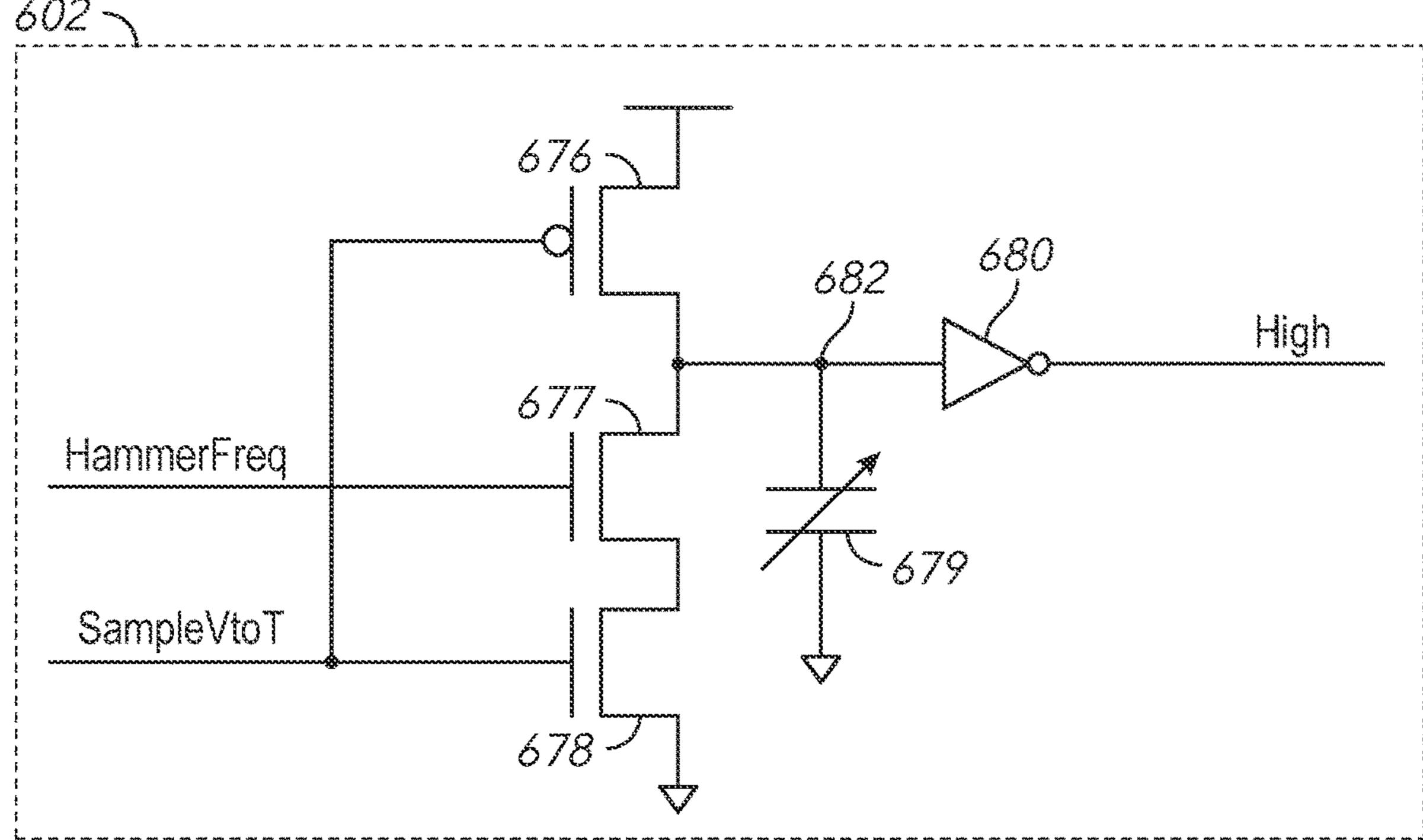

FIG. **6** is a schematic diagram of a voltage to time (VtoT) circuit according to an embodiment of the present disclosure.

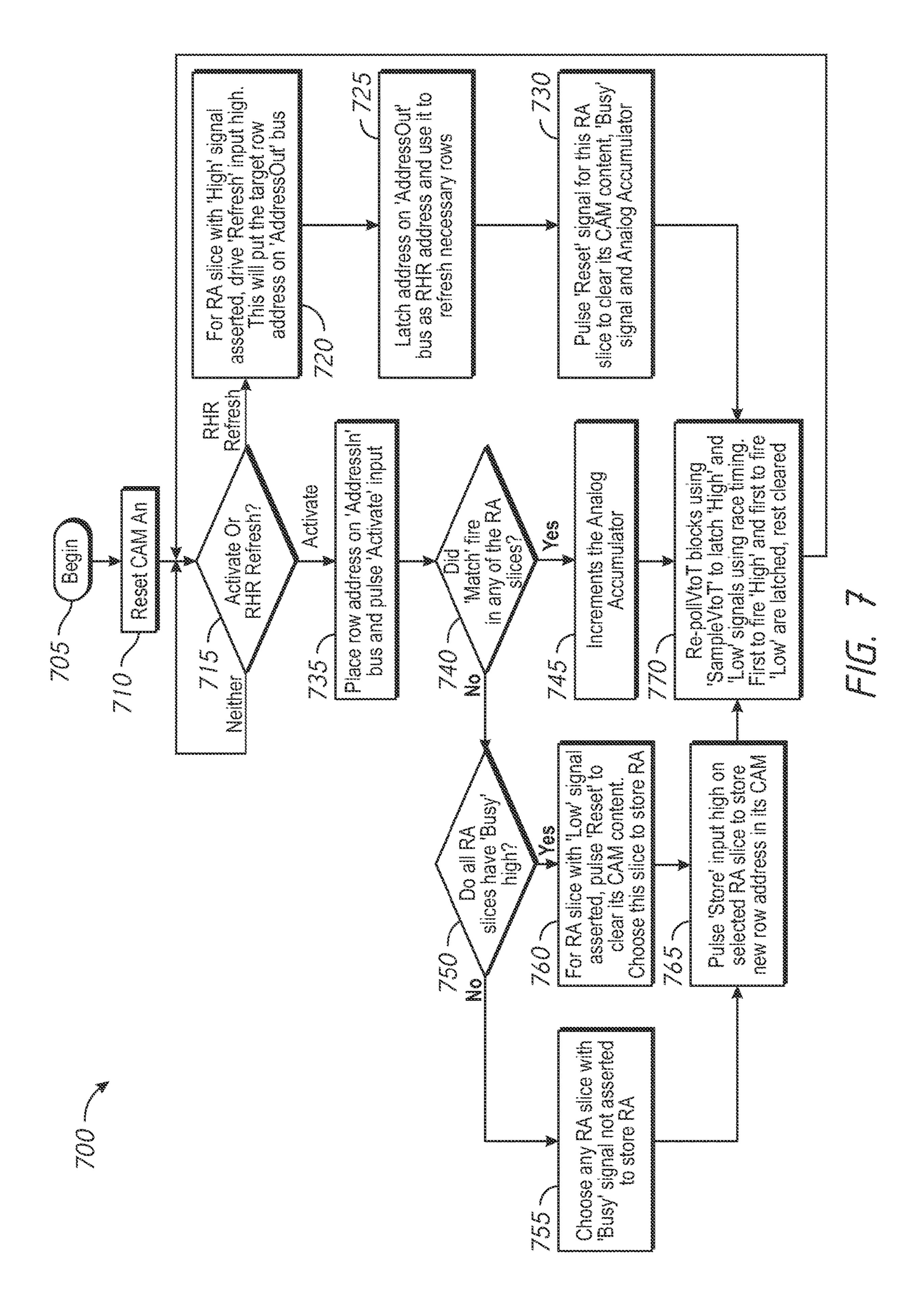

FIG. 7 is a flow chart of a method of analog row access rate determination according to an embodiment of the present disclosure.

### DETAILED DESCRIPTION

The following description of certain embodiments is merely exemplary in nature and is in no way intended to limit the scope of the disclosure or its applications or uses. In the following detailed description of embodiments of the present systems and methods, reference is made to the 65 accompanying drawings which form a part hereof, and which are shown by way of illustration specific embodi-

2

ments in which the described systems and methods may be practiced. These embodiments are described in sufficient detail to enable those skilled in the art to practice presently disclosed systems and methods, and it is to be understood that other embodiments may be utilized and that structural and logical changes may be made without departing from the spirit and scope of the disclosure. Moreover, for the purpose of clarity, detailed descriptions of certain features will not be discussed when they would be apparent to those with skill in the art so as not to obscure the description of embodiments of the disclosure. The following detailed description is therefore not to be taken in a limiting sense, and the scope of the disclosure is defined only by the appended claims.

A memory device may include a plurality of memory cells. The memory cells may store information (e.g., as one or more bits), and may be organized at the intersection of word lines (rows) and bit lines (columns). Each word line of the memory device may be associated with a row address. When a given word line is accessed, a row address may be provided which specifies which row is being accessed.

Information in the memory cells may decay over time. The memory cells may be refreshed on a row-by-row basis to preserve information in the memory cells. During a refresh operation, the information in one or more rows may be rewritten back to the respective rows to restore an initial value of the information. Repeated accesses to a given row (e.g., an aggressor row) may cause an increased rate of information decay in nearby rows (e.g., victim rows). Victim rows may be refreshed as part of a targeted refresh operation. It may be important to track accesses to word lines of the memory in order to perform targeted refresh operations before information is lost in the victim rows. Tracking accesses as a binary number (e.g., with a counter) may require a relatively large amount of space on a chip. It may be desirable to track accesses in a manner which requires a minimal amount of space and power.

The present disclosure is drawn to apparatuses, systems, and methods for analog row access rate determination. 40 When a row is accessed, its row address may be compared the row addresses stored in the files (e.g., registers) of a stack (e.g., register stack, data storage unit). If there is a match, a match signal may be provided to an accumulator circuit associated with that file. The accumulator circuit includes a 45 capacitor, and responsive to the match signal an amount of charge is added to the capacitor. The accumulator circuit may also allow the charge to drain out of the capacitor over time. The accumulator circuit may provide a voltage based on the current charge on the capacitor. Accordingly, the voltage may represent a rate at which the row stored in the associated file is accessed. Each file may also be associated with a voltage to time (VtoT) circuit, which may use the voltage provided by the associated accumulator circuit to determine which of the files includes an address with a fastest access rate and/or a slowest access rate.

FIG. 1 is a block diagram of a semiconductor device according to at least one embodiment of the disclosure. The semiconductor device 100 may be a semiconductor memory device, such as a DRAM device integrated on a single semiconductor chip.

The semiconductor device 100 includes a memory array 112. In some embodiments, the memory array 112 may include of a plurality of memory banks. Each memory bank includes a plurality of word lines WL, a plurality of bit lines BL and/BL, and a plurality of memory cells MC arranged at intersections of the plurality of word lines WL and the plurality of bit lines BL and/BL. The selection of the word

line WL is performed by a row control 108 and the selection of the bit lines BL and BL is performed by a column control 110. In some embodiments, there may be a row control 108 and column control 110 for each of the memory banks.

The bit lines BL and/BL are coupled to a respective sense amplifier (SAMP) 117. Read data from the bit line BL or/BL is amplified by the sense amplifier SAMP 117, and transferred to read/write amplifiers 120 over complementary local data lines (LIOT/B), transfer gate (TG) 118, and complementary main data lines (MIO). Conversely, write data outputted from the read/write amplifiers 120 is transferred to the sense amplifier 117 over the complementary main data lines MIO, the transfer gate 118, and the complementary local data lines LIOT/B, and written in the memory cell MC coupled to the bit line BL or/BL.

The semiconductor device 100 may employ a plurality of external terminals that include command and address (C/A) terminals coupled to a command and address bus to receive commands and addresses, clock terminals to receive clocks 20 CK and/CK, data terminals DQ to provide data, and power supply terminals to receive power supply potentials VDD, VSS, VDDQ, and VSSQ.

The clock terminals are supplied with external clocks CK and/CK that are provided to a clock input circuit 122. The external clocks may be complementary. The clock input circuit 122 generates an internal clock ICLK based on the CK and/CK clocks. The ICLK clock is provided to the command control 106 and to an internal clock generator 124. The internal clock generator 124 provides various internal clocks LCLK based on the ICLK clock. The LCLK clocks may be used for timing operation of various internal circuits. The internal data clocks LCLK are provided to the input/output circuit 126 to time operation of circuits included in the input/output circuit 126, for example, to data receivers to time the receipt of write data.

The C/A terminals may be supplied with memory addresses. The memory addresses supplied to the C/A terminals are transferred, via a command/address input 40 circuit 102, to an address decoder 104. The address decoder 104 receives the address and supplies a decoded row address XADD to the row control 108 and supplies a decoded column address YADD to the column control 110. The address decoder 104 may also supply a decoded bank 45 address BADD, which may indicate the bank of the memory array 118 containing the decoded row address XADD and column address YADD. The C/A terminals may be supplied with commands. Examples of commands include timing commands for controlling the timing of various operations, 50 access commands for accessing the memory, such as read commands for performing read operations and write commands for performing write operations, as well as other commands and operations. The access commands may be associated with one or more row address XADD, column 55 address YADD, and bank address BADD to indicate the memory cell(s) to be accessed.

The commands may be provided as internal command signals to a command control 106 via the command/address input circuit 102. The command control 106 includes circuits to decode the internal command signals to generate various internal signals and commands for performing operations. For example, the command control 106 may provide a row command signal to select a word line and a column command signal to select a bit line.

The device 100 may receive an access command which is a row activation command ACT. When the row activation

4

command ACT is received, a bank address BADD and a row address XADD are timely supplied with the row activation command ACT.

The device 100 may receive an access command which is a read command. When a read command is received, a bank address and a column address are timely supplied with the read command, read data is read from memory cells in the memory array 112 corresponding to the row address and column address. The read command is received by the command control 106, which provides internal commands so that read data from the memory array 112 is provided to the read/write amplifiers 120. The read data is output to outside from the data terminals DQ via the input/output circuit 126.

The device 100 may receive an access command which is a write command. When the write command is received, a bank address and a column address are timely supplied with the write command, write data supplied to the data terminals DQ is written to a memory cells in the memory array 112 corresponding to the row address and column address. The write command is received by the command control 106, which provides internal commands so that the write data is received by data receivers in the input/output circuit 126. Write clocks may also be provided to the external clock terminals for timing the receipt of the write data by the data receivers of the input/output circuit 126. The write data is supplied via the input/output circuit 126 to the read/write amplifiers 120, and by the read/write amplifiers 120 to the memory array 112 to be written into the memory cell MC.

The device 100 may also receive commands causing it to carry out refresh operations. A refresh signal AREF may be a pulse signal which is activated when the command control 106 receives a signal which indicates a refresh command. In some embodiments, the refresh command may be externally issued to the memory device 100. In some embodiments, the refresh command may be periodically generated by a component of the device. In some embodiments, when an external signal indicates a self-refresh entry command, the refresh signal AREF may also be activated. The refresh signal AREF may be activated once immediately after command input, and thereafter may be cyclically activated at desired internal timing. Thus, refresh operations may continue automatically. A self-refresh exit command may cause the automatic activation of the refresh signal AREF top and return to an IDLE state.

The refresh signal AREF is supplied to the refresh control circuit 116. There may be a refresh control circuit 116 associated with each bank. The refresh control circuits 116 may receive the refresh signal AREF in common, and may generate and provide one or more refresh row address(es) RXADD in order to perform one or more refresh operations in the associated memory bank. In some embodiments, a subset of the memory banks may be given refresh commands. For example, one or more additional signals may indicate which of the refresh control circuits 116 should provide refresh address(es) responsive to AREF. In another example, AREF may only be provided to refresh control circuits 116 which are associated with the subset of memory banks which are refreshing.

Focusing on the operation of a given refresh control circuit, the refresh control circuit **116** supplies a refresh row address RXADD to the row control **108**, which may refresh one or more wordlines WL indicated by the refresh row address RXADD. The refresh control circuit **116** may control a timing of the refresh operation based on the refresh signal AREF. In some embodiments, responsive to an activation of AREF, the refresh control circuit **116** may generate

one or more activations of a pump signal, and may generate and provide a refresh address RXADD for each activation of the pump signal (e.g., each pump).

Since the various refresh control circuits are coupled in common to AREF, multiple memory banks of the device **100** 5 may simultaneously perform refresh operations. Each refresh control circuit **116** may be controlled to change details of the refreshing address RXADD (e.g., how the refresh address is calculated, the timing of the refresh addresses), or may operate based on internal logic. The 10 refresh control circuit **116** may direct the associated memory bank to perform different types of refresh operation based on the provided refresh address RXADD.

One type of refresh operation may be an auto-refresh operation. Responsive to an auto-refresh operation the 15 memory bank may refresh a group of rows of the memory, and then may refresh a next group of rows of the memory bank responsive to a next auto-refresh operation. The refresh control circuit 116 may provide a refresh address RXADD which indicates a group of wordlines in the memory bank. 20 The refresh control circuit 116 may generate a sequence of refresh addresses RXADD such that over time the auto-refresh operation may cycle through all the wordlines WL of the memory bank. The timing of refresh operations may be such that each wordline is refreshed with a frequency based 25 on a normal rate of data degradation in the memory cells.

Another type of refresh operation may be a targeted refresh operation. Repeated access to a particular row of memory (e.g., an aggressor row) may cause an increased rate of decay in neighboring rows (e.g., victim rows) due, for 30 example, to electromagnetic coupling between the rows. In some embodiments, the victim rows may include rows which are physically adjacent to the aggressor row. In some embodiments, the victim rows may include rows further away from the aggressor row. Information in the victim rows 35 may decay at a rate such that data may be lost if they aren't refreshed before the next auto-refresh operation of that row. In order to prevent information from being lost, it may be necessary to identify aggressor rows and then carry out a targeted refresh operation where a refresh address RXADD 40 associated with one or more associated victim rows is refreshed.

The refresh control circuit **116** may track accesses to various wordlines of the memory. The refresh control circuit **116** may receive the row address RXADD and may compare 45 it to previously received addresses. The refresh control circuit **116** includes a stack which includes a number of slices. Each slice includes a file configured to store a row address, an accumulator circuit which provides a voltage proportional to a rate at which the address in the file has been 50 received, and a voltage to time (VtoT) circuit which may be used to determine which of the accumulator circuits in the stack is providing the highest voltage. The row address associated with the highest voltage (e.g., the fastest rate of accesses) may have its victims refreshed as part of a targeted 55 refresh operation.

In some embodiments, the refresh control circuits 116 may perform multiple refresh operations responsive to each occurrence of AREF. Each refresh control circuit 116 may generate a number of 'pumps' (e.g., activations of a pump 60 signal) responsive to receiving an activation of AREF. Each pump, in turn, may cause the refresh control circuit 116 to provide a refresh address RXADD, and trigger a refresh operation as indicated by the refresh address RXADD. A given refresh control circuit 116 may provide auto-refresh 65 addresses responsive to some of the pumps and targeted refresh addresses responsive to some of the pumps generated

6

from a given activation of AREF. In some embodiments, the refresh control circuit 116 may perform auto-refresh operations for a certain number of pumps, and then may perform targeted refresh operations for a certain number of pumps. In some embodiments, auto-refresh operations and targeted refresh operations may be dynamically assigned to the pumps. For example, if there are no rows waiting to be refreshed as part of a targeted refresh operation, pumps which would have been used for a targeted refresh operation may be used for an auto-refresh operation instead.

The power supply terminals are supplied with power supply potentials VDD and VSS. The power supply potentials VDD and VSS are supplied to an internal voltage generator circuit 128. The internal voltage generator circuit 128 generates various internal potentials VPP, VOD, VARY, VPERI, and the like based on the power supply potentials VDD and VSS supplied to the power supply terminals. The internal potential VPP is mainly used in the row control 108, the internal potentials VOD and VARY are mainly used in the sense amplifiers SAMP included in the memory array 112, and the internal potential VPERI is used in many peripheral circuit blocks.

The power supply terminals are also supplied with power supply potentials VDDQ and VSSQ. The power supply potentials VDDQ and VSSQ are supplied to the input/output circuit 126. The power supply potentials VDDQ and VSSQ supplied to the power supply terminals may be the same potentials as the power supply potentials VDD and VSS supplied to the power supply terminals in an embodiment of the disclosure. The power supply potentials VDDQ and VSSQ supplied to the power supply terminals may be different potentials from the power supply potentials VDD and VSS supplied to the power supply terminals in another embodiment of the disclosure. The power supply potentials VDDQ and VSSQ supplied to the power supply terminals are used for the input/output circuit 126 so that power supply noise generated by the input/output circuit 126 does not propagate to the other circuit blocks.

FIG. 2 is a block diagram of a refresh control circuit according to an embodiment of the present disclosure. The refresh control circuit 216 may implement the refresh control circuit 116 of FIG. 1 in some embodiments. Certain internal components and signals of the refresh address control circuit 216 are shown to illustrate the operation of the refresh address control circuit 216. The dotted line 232 is shown to represent that in certain embodiments, each of the components (e.g., the refresh address control circuit 216 and row decoder 208) may correspond to a particular bank of memory, and that these components may be repeated for each of the banks of memory. Thus, there may be multiple refresh address control circuits 216 and row decoders 208. For the sake of brevity, only components for a single bank will be described.

An interface 231 may provide one or more signals to an address refresh control circuit 216 and row decoder 208. The refresh address control circuit 216 may include a sample timing generator 238, an aggressor detector circuit 237, a row hammer refresh (RHR) state controller 236 and a refresh address generator 239. The interface 231 may provide one or more control signals, such as an auto-refresh signal AREF, and a row address XADD. The RHR state control 236 may determine if an auto-refresh or a targeted refresh operation should be performed. The RHR state control circuit 236 may indicate different refresh operations in different banks in order to stagger the targeted and auto-refresh operations between the banks.

The example refresh control circuit **216** of FIG. **2** includes a sampling circuit which may be used to sample the row address XADD each time a sampling signal ArmSample is activated. As the row address XADD changes over time, the aggressor detector 237 may only pay attention to the subset of row addresses XADD which coincide with an activation of the sampling signal ArmSample. The sampling signal ArmSample may be provided by the sample timing generator 238 with one or more of periodic timing, random timing, pseudo-random timing, and/or semi-random timing. In other embodiments, the sample timing generator 238 and the sampling signal ArmSample may be omitted, and the aggressor detector 237 may receive all of the row addresses XADD provided by the interface 231.

In the embodiment, shown in FIG. 2, the aggressor detector circuit 237 may sample the current row address XADD responsive to an activation of ArmSample. The sampled address XADD may be compared to previously sampled addresses stored in the aggressor detector circuit 20 237. The aggressor detector circuit 237 may provide one or more of the stored addresses to the refresh address generator 239 as the matched address HitXADD. The RHR state controller 236 may provide the signal RHR to indicate that a row hammer refresh operation (e.g., a refresh of the victim 25 rows corresponding to an identified aggressor row) should occur. The RHR state controller 236 may also provide an internal refresh signal IREF, to indicate that an auto-refresh operation should occur. The RHR state controller 236 may be used to control the timings of targeted refresh operations 30 and auto-refresh operations. The activations of IREF and RHR may represent activations of the pump signal.