### US011309013B2

# (12) United States Patent

# Moon et al.

## MEMORY DEVICE FOR REDUCING RESOURCES USED FOR TRAINING

Applicant: Samsung Electronics Co., Ltd.,

Suwon-si (KR)

Inventors: Byongmo Moon, Seoul (KR);

Beomyong Kil, Suwon-si (KR); Jihye

Kim, Hwaseong-si (KR)

(73) Assignee: Samsung Electronics Co., Ltd.,

Gyeonggi-do (KR)

Subject to any disclaimer, the term of this Notice:

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

Appl. No.: 17/130,493

Dec. 22, 2020 (22)Filed:

(65)**Prior Publication Data**

> US 2021/0343325 A1 Nov. 4, 2021

#### (30)Foreign Application Priority Data

| Apr. 29, 2020 | (KR) | 10-2020-0052587 |

|---------------|------|-----------------|

| Jul. 22, 2020 | (KR) | 10-2020-0091254 |

Int. Cl. (51)

G11C 5/14 (2006.01)G11C 11/4074 (2006.01)G11C 8/18 (2006.01)G11C 11/4076 (2006.01)G11C 11/409 (2006.01)

U.S. Cl. (52)

CPC ...... *G11C 11/4074* (2013.01); *G11C 8/18* (2013.01); *G11C 11/409* (2013.01); *G11C 11/4076* (2013.01)

Field of Classification Search (58)

> CPC ... G11C 11/4074; G11C 8/18; G11C 11/4076; G11C 11/409

(10) Patent No.: US 11,309,013 B2

(45) Date of Patent:

Apr. 19, 2022

See application file for complete search history.

#### **References Cited** (56)

### U.S. PATENT DOCUMENTS

| 5,604,710 A * | 2/1997 | Tomishima G11C 5/025     |  |  |  |

|---------------|--------|--------------------------|--|--|--|

| 7,103,792 B2  | 9/2006 | Moon 365/201             |  |  |  |

| , ,           |        | MacWilliams G06F 12/0646 |  |  |  |

|               |        | 365/52                   |  |  |  |

| 8,725,976 B2  | 5/2014 | Cho et al.               |  |  |  |

| 9,720,439 B2  | 8/2017 | Tennant                  |  |  |  |

| (Continued)   |        |                          |  |  |  |

#### FOREIGN PATENT DOCUMENTS

| KR | 10-0454126 B     | 1 1 | 0/2004 |

|----|------------------|-----|--------|

| WO | WO-2014/115599 A | .1  | 7/2014 |

### OTHER PUBLICATIONS

Extended European Search Report dated Sep. 1, 2021 issued in corresponding European Application No. 21169529.1-1203.

Primary Examiner — Huan Hoang (74) Attorney, Agent, or Firm — Harness, Dickey & Pierce, P.L.C.

#### ABSTRACT (57)

A memory device includes: first power pins in a first power area and configured to receive a first power voltage; data pins configured to transmit or receive data signals, the data pins being arranged in a first region and in a second region each including the first power area; control pins configured to transmit or receive control signals in the first region and in the second region; second power pins in a second power area between the first region and the second region and configured to receive a second power voltage different from the first power voltage; and ground pins in the second power area and configured to receive a ground voltage.

## 20 Claims, 19 Drawing Sheets

# US 11,309,013 B2

Page 2

# (56) References Cited

### U.S. PATENT DOCUMENTS

<sup>\*</sup> cited by examiner

200 Device Controller Memory

FIG. 2

FIG. 4

FIG. 5

FIG. 6

FIG. 8

FIG. 9

FIG. 11

FIG. 13

300

FIG. 14

(PA2) Power Area 2 別 NDO N 8 \$3 400000  $\sim$ 202 **SS** PG5(PGA5) DPAR DERR **SS SOCO** 88 RDOS. **SS** d PG6(PGA6) 0023 **\$** 0024 Q 888 **DB**32 四 至 SS

FIG. 16

300 2 Core

FIG. 18

FIG. 19

# MEMORY DEVICE FOR REDUCING RESOURCES USED FOR TRAINING

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims priority under § 119 to a Korean Patent Application No. 10-2020-0052587 filed on Apr. 29, 2020, and a Korean Patent Application No. 10-2020-0091254 filed on Jul. 22, 2020, in the Korean Intellectual Property Office, the disclosures of each of which are incorporated herein in their entirety by reference.

#### BACKGROUND

Example embodiments relate to a semiconductor device, and more particularly, to a memory device for reducing resources used for training.

Electronic devices such as smartphones, graphics accelerators, and/or artificial intelligence (AI) accelerators process data using memory devices such as Dynamic Random Access Memory (DRAM). As the amount of data to be processed by the electronic devices increases, a memory device having high capacity and high bandwidth is required. In particular, in order to process data at high speed, the use of memory devices that provide wide input/output of a multi-channel interface method such as High Bandwidth Memory (HBM) has increased.

The memory device may exchange data with an external device (e.g., a host device or a memory controller) through <sup>30</sup> a plurality of data pins to provide high bandwidth. As the number of data pins of the memory device increases, the external device can process data at a high speed. However, when training is performed for each pin, the training may take a long time and resources used for training may increase <sup>35</sup> as the number of data pins increases.

# **SUMMARY**

Example embodiments may provide a memory device 40 capable of performing training for a plurality of data pins by each group to reduce training resources for the plurality of data pins.

According to some example embodiments, a memory device includes first power pins in a first power area and 45 configured to receive a first power voltage, data pins configured to transmit or receive data signals, the data pins in a first region and a second region, the first region and the second region each including a portion of the first power area, control pins configured to transmit or receive control 50 signals, the control pins in the first region and the second region, second power pins in a second power area between the first region and the second region, the second power pins configured to receive a second power voltage different from the first power voltage, and ground pins in the second power 55 area and configured to receive a ground voltage, The data pins and the control pins are divided into a plurality of pin groups, and a training value corresponding to each of the plurality of pin groups is based on training with regard to at least one pin from among pins of each of the plurality of pin 60 groups.

According to some example embodiments, a memory device includes a first pin group including a first data pin configured to transmit or receive a first data signal and a first control pin configured to transmit or receive a first control 65 signal, a second pin group including a second data pin configured to transmit or receive a second data signal and a

2

second control pin configured to transmit or receive a second control signal, a third control pin configured to receive a write data strobe signal, first power pins configured to receive a first power voltage, second power pins configured 5 to receive a second power voltage different from the first power voltage, ground pins configured to receive a ground voltage, and a write data strobe tree circuitry configured to transmit a first internal write data strobe signal with a first toggle timing to a first circuit block corresponding to the first pin group and to transmit a second internal write data strobe signal with a second toggle timing to a second circuit block corresponding to the second pin group, based on the write data strobe signal. The first power pins are located in a first power area positioned in each of a first region in which the 15 first pin group is located and a second region in which the second pin group is located. The second power pins are located in a second power area positioned between the first region and the second region. The ground pins being located in the second power area. The first toggle timing is different from the second toggle timing.

According to some example embodiments, a memory device includes a write data strobe pin configured to receive a write data strobe signal, a first group of pins configured to receive first data signals sampled based on the write data strobe signal, and a second group of pins configured to receive second data signals sampled based on the write data strobe signal. A first training value corresponding to the first group of pins is based on training with respect to a first pin from among the first pin groups, and a second training value corresponding to the second group of pins is based on training with respect to a second pin of the second group of pins.

According to some example embodiments, a memory system includes a memory device configured to receive a write data strobe signal through a write data strobe pin, to receive first data signals through pins of a first pin group corresponding to the write data strobe pin, and to receive second data signals through pins of a second pin group corresponding to the write data strobe pin, and a memory controller configured to transmit the first data signals to the memory device based on a first transmission timing determined through training with respect to one pin of the first pin group and to transmit the second data signals to the memory device based on a second transmission timing determined through training with respect to one pin of the second pin group while transmitting the toggling write data strobe signal to the memory device.

According to some example embodiments, a memory system includes a memory device configured to receive a write data strobe signal through a write data strobe pin, to transmit first data signals through a first pin group corresponding to the write data strobe pin, and to transmit second data signals through a second pin group corresponding to the write data strobe pin, and a memory controller configured to transmit the toggling write data strobe signal to the memory device, to sample the first data signals received from the memory device based on a first receiving timing determined through training with respect to one pin of the first pin group, and to sample the second data signals received from the memory device based on a second receiving timing determined through training with respect to one pin of the second pin group.

According to some example embodiments, a memory system includes an interposer substrate, a system-on-chip stacked on the interposer substrate and including at least one processor, and a memory device stacked on the interposer substrate and including (a) a buffer die configured to com-

municate first signals with the system-on-chip through a first bump group and to communicate second signals with the system-on-chip through a second bump group and (b) a plurality of core dies stacked on the buffer die through a silicon through electrode and each including memory cells. The system-on-chip is configured to communicate the first signals with the buffer die based on a first training result determined through training on a first bump of the first bump group, and to communicate the second signals with the buffer die based on a second training result determined through training with respect to a second bump of the second bump group.

According to some example embodiments, a Dynamic Random Access Memory (DRAM) device includes a clock 15 terminal configured to receive a clock signal, a data clock terminal configured to receive a data clock signal, and an m-number of unit blocks coupled to the data clock signal, each of the m-number of unit blocks on a monolithic silicon substrate and in a shifted and/or mirrored relationship with 20 other unit blocks, and each unit block including n-number of data terminals configured to respectively receive n-number of data signals, m and n are integers greater than or equal to three. Each of the m-number of unit blocks is configured to perform a data bus training affecting a timing window 25 between the data clock signal and a representative data signal, and the representative data signal is a representative one out of the n number of data signals in the unit block in which the data bus training is performed.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Some example embodiments of inventive concepts will be more clearly understood from the following detailed description taken in conjunction with the accompanying 35 drawings in which:

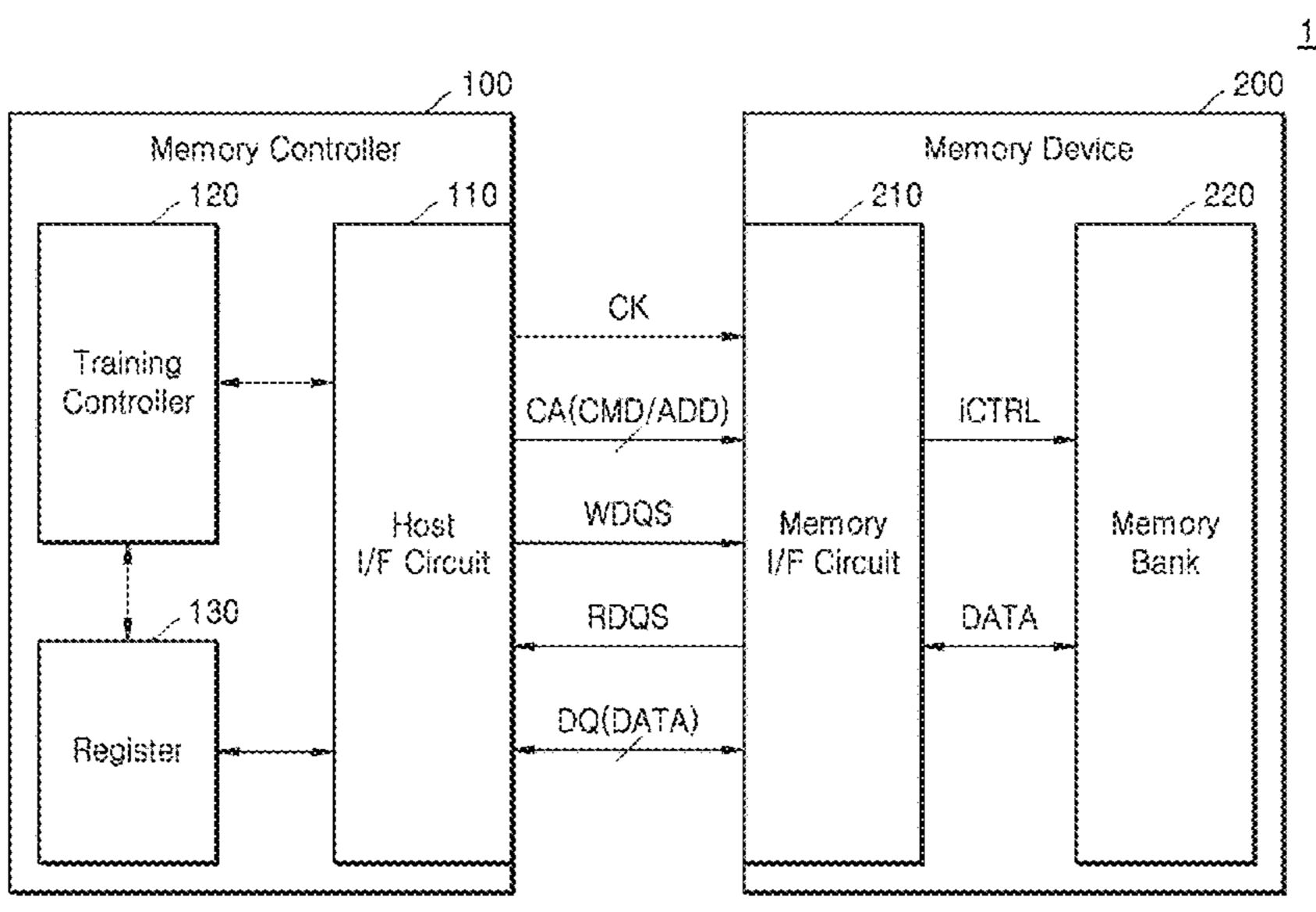

- FIG. 1 is a block diagram illustrating a memory system according to an example embodiment;

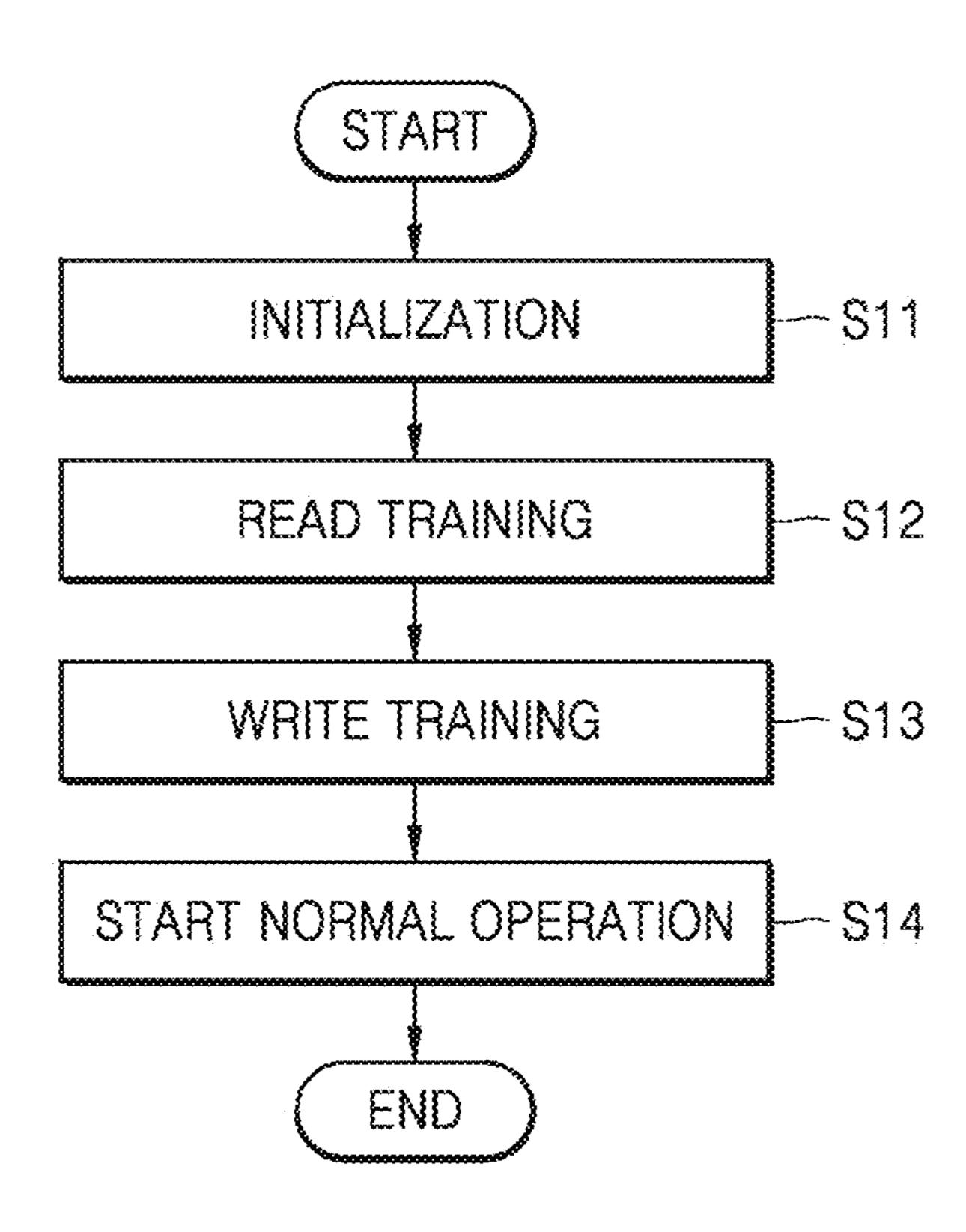

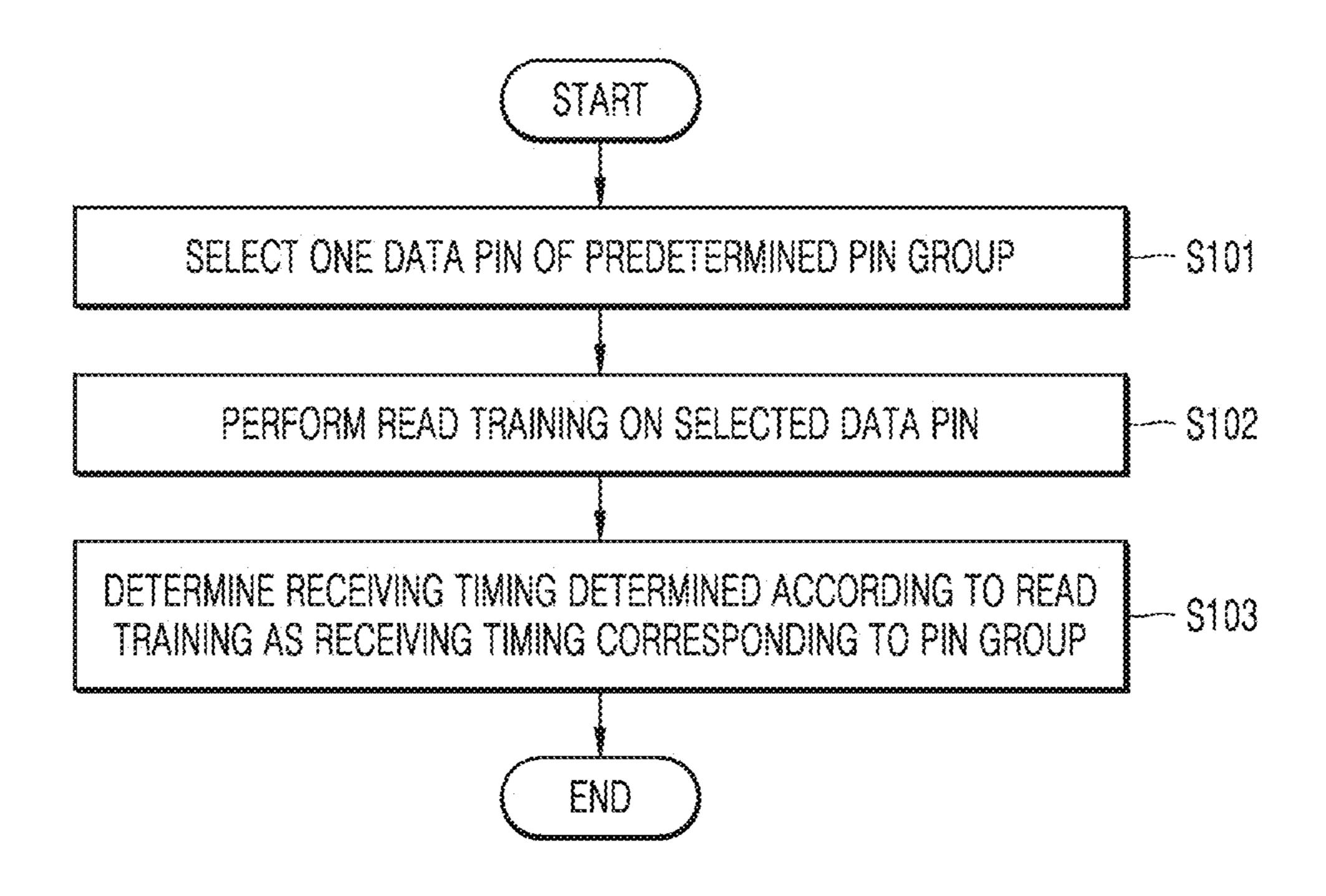

- FIG. 2 is a flowchart illustrating an example operation of the memory system of FIG. 1;

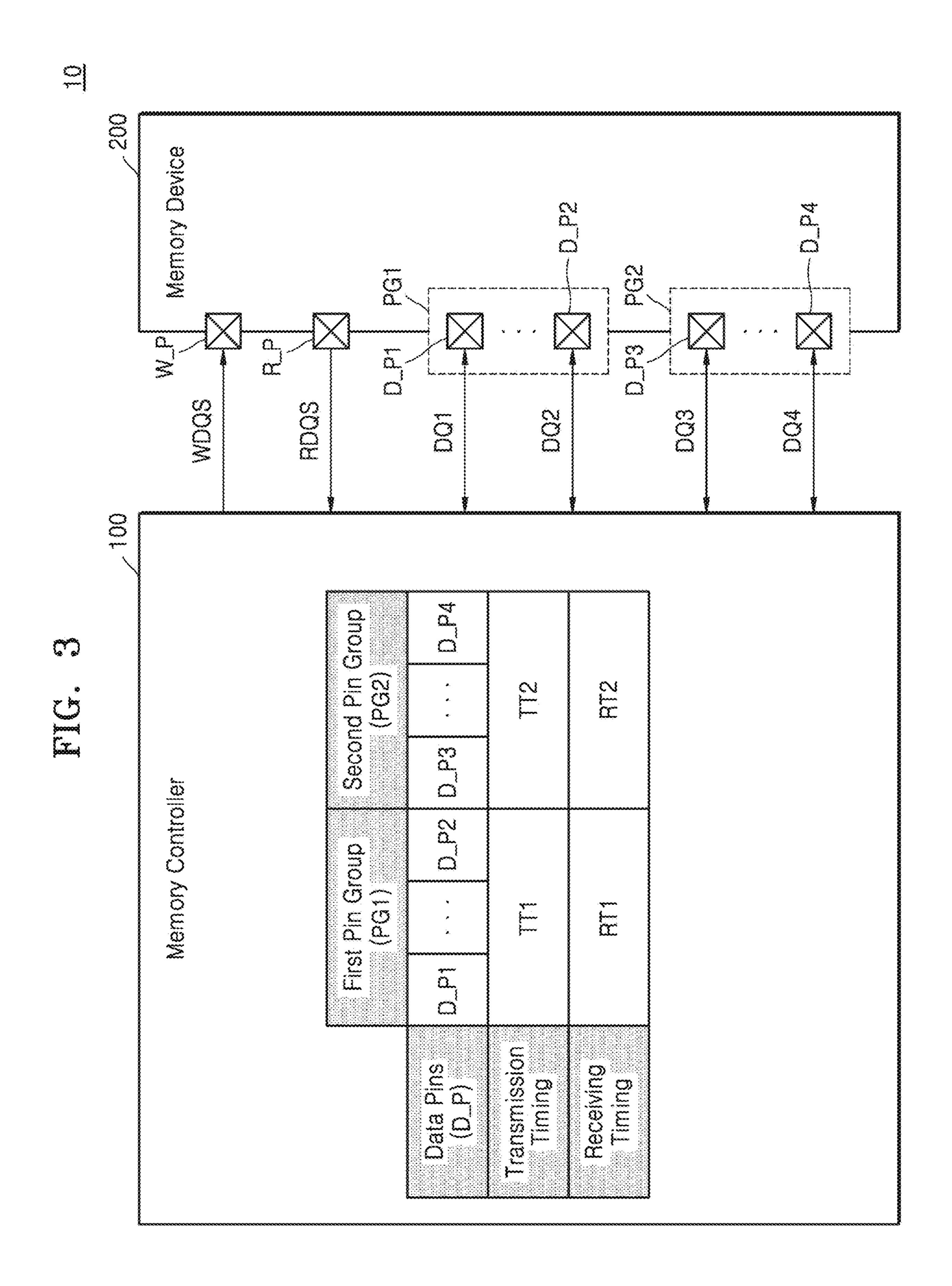

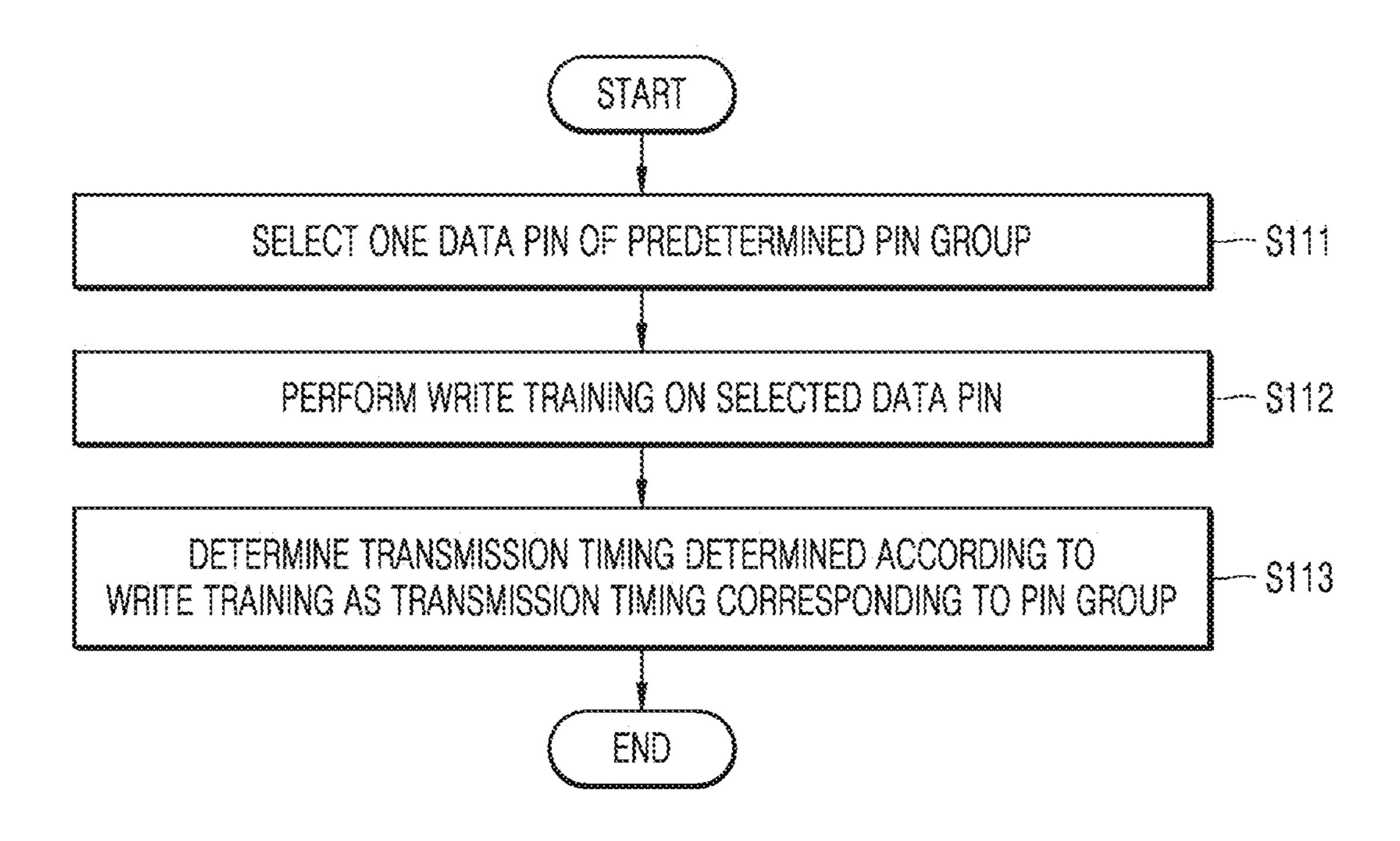

- FIG. 3 is a diagram illustrating an example of a read training operation and a write training operation of the memory system of FIG. 1;

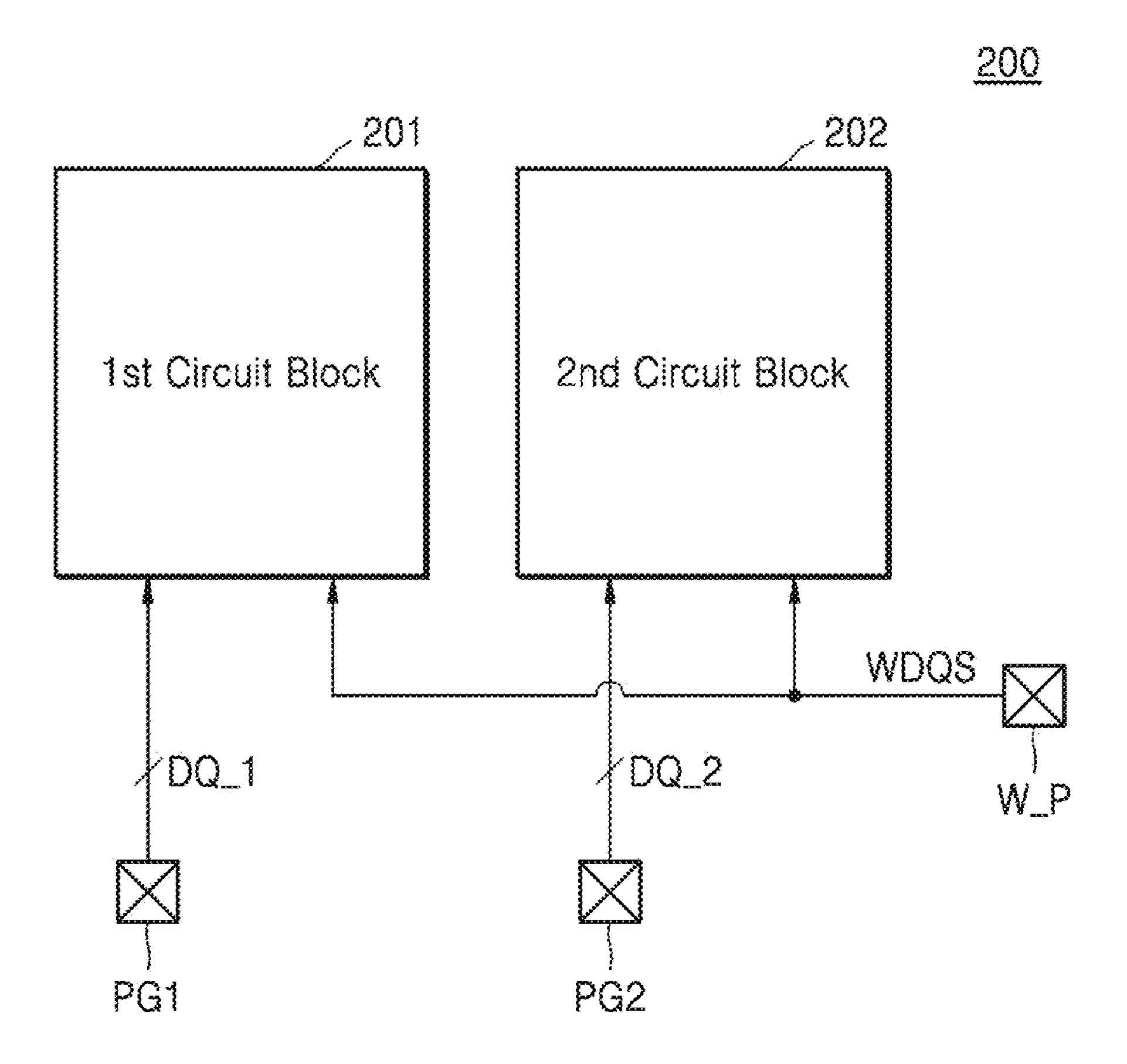

- FIG. 4 is a block diagram of the memory device of FIG. 3 according to an example embodiment;

- FIG. 5 is a flowchart illustrating an example of a read training operation of the memory controller of FIG. 3;

- FIG. 6 is a flowchart illustrating an example of a write training operation of the memory controller of FIG. 3;

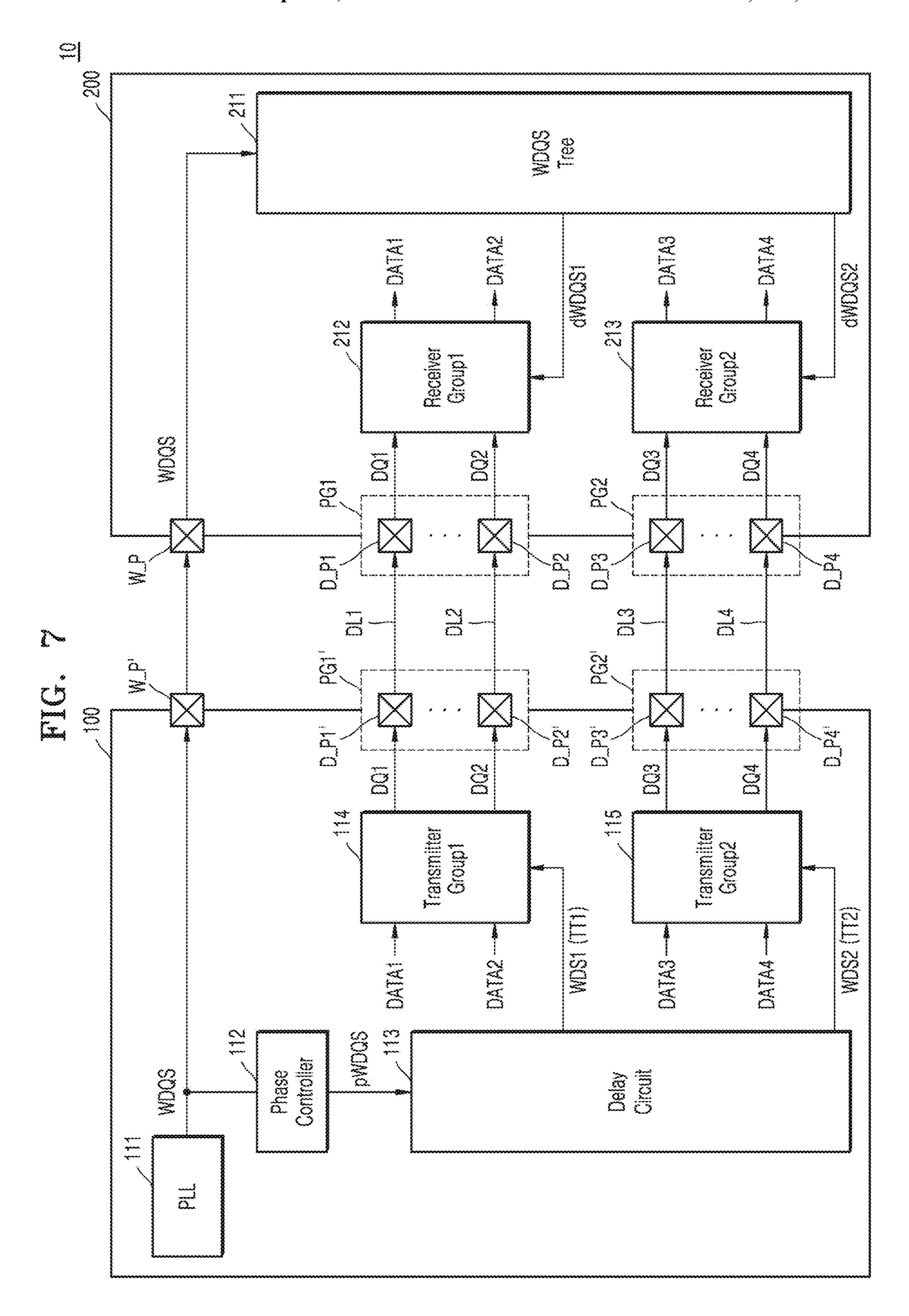

- FIG. 7 is a block diagram schematically illustrating the 50 memory system of FIG. 3 according to an example embodiment;

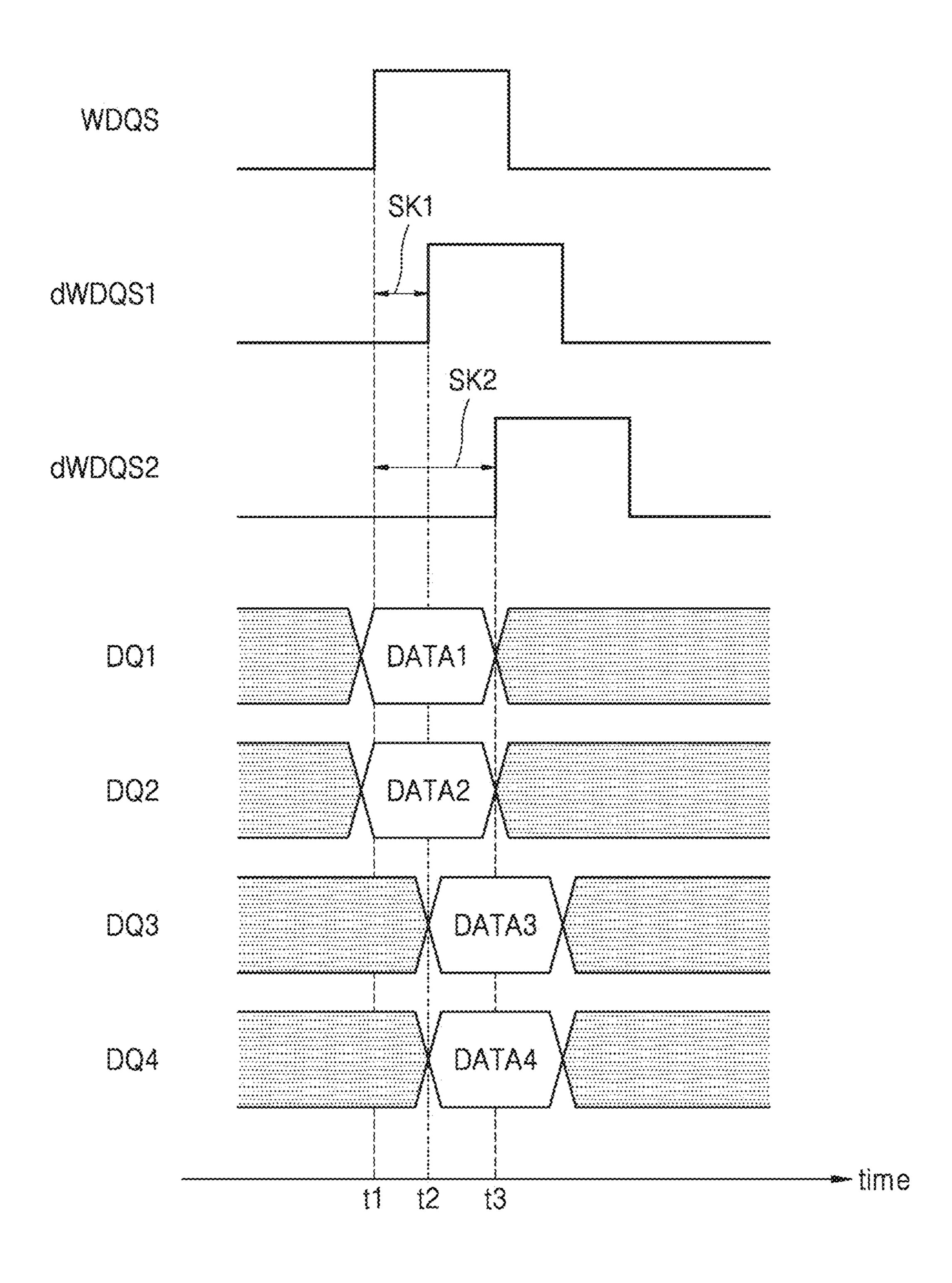

- FIG. 8 is a timing diagram illustrating an example in which the memory device of FIG. 7 samples data signals;

- FIG. 9 is a diagram illustrating an example configuration 55 of the memory device of FIG. 7;

- FIG. 10 is a block diagram schematically illustrating the memory system of FIG. 3 according to an example embodiment;

- FIG. 11 is a timing diagram illustrating an example in 60 may obtain data DATA from the data signals DQ. which the memory device of FIG. 10 transmits data signals; The training controller 120 may control training

- FIG. 12 is a diagram illustrating an example configuration of the memory device of FIG. 10;

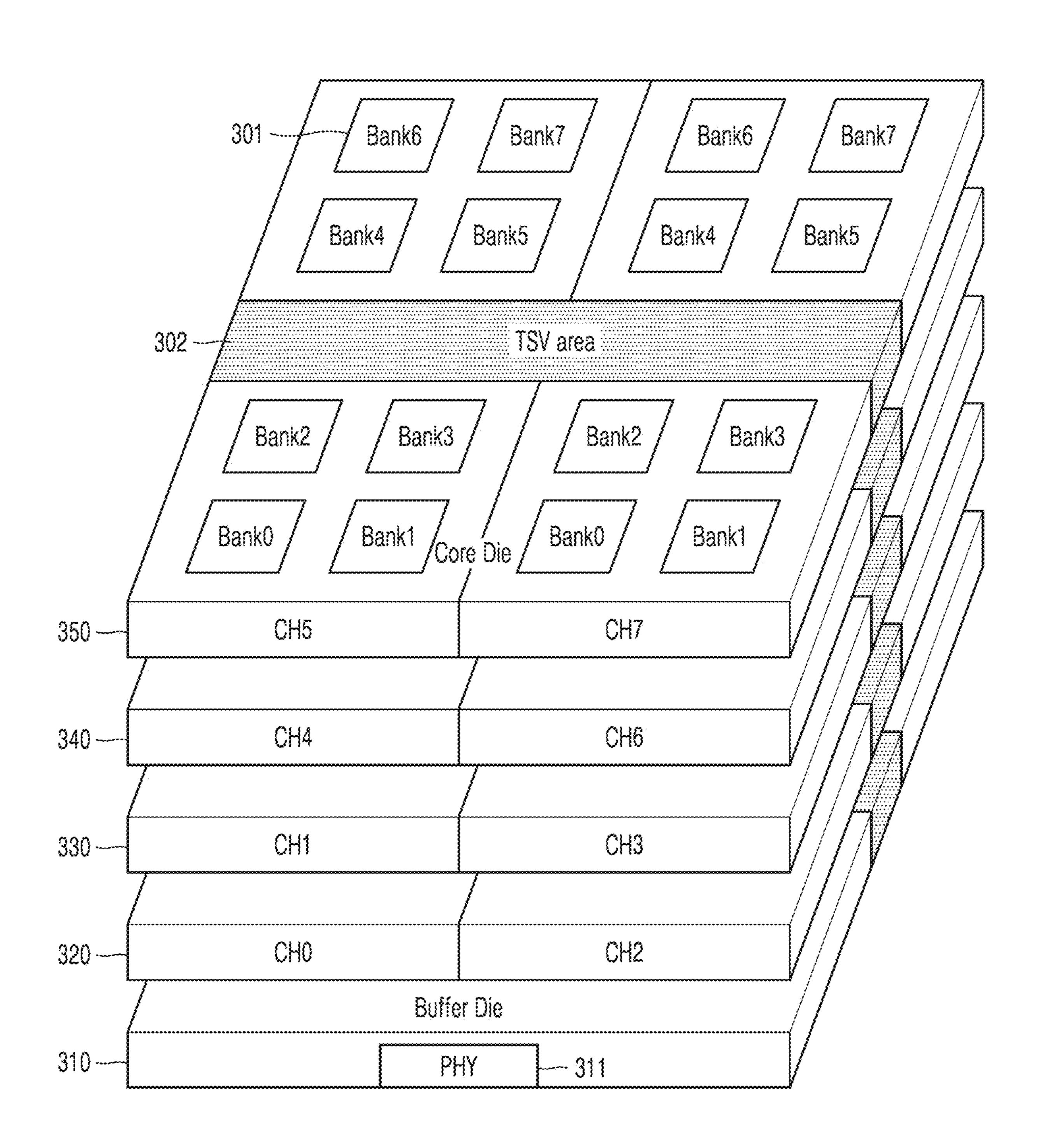

- FIG. 13 is a block diagram showing a stacked memory device according to an example embodiment;

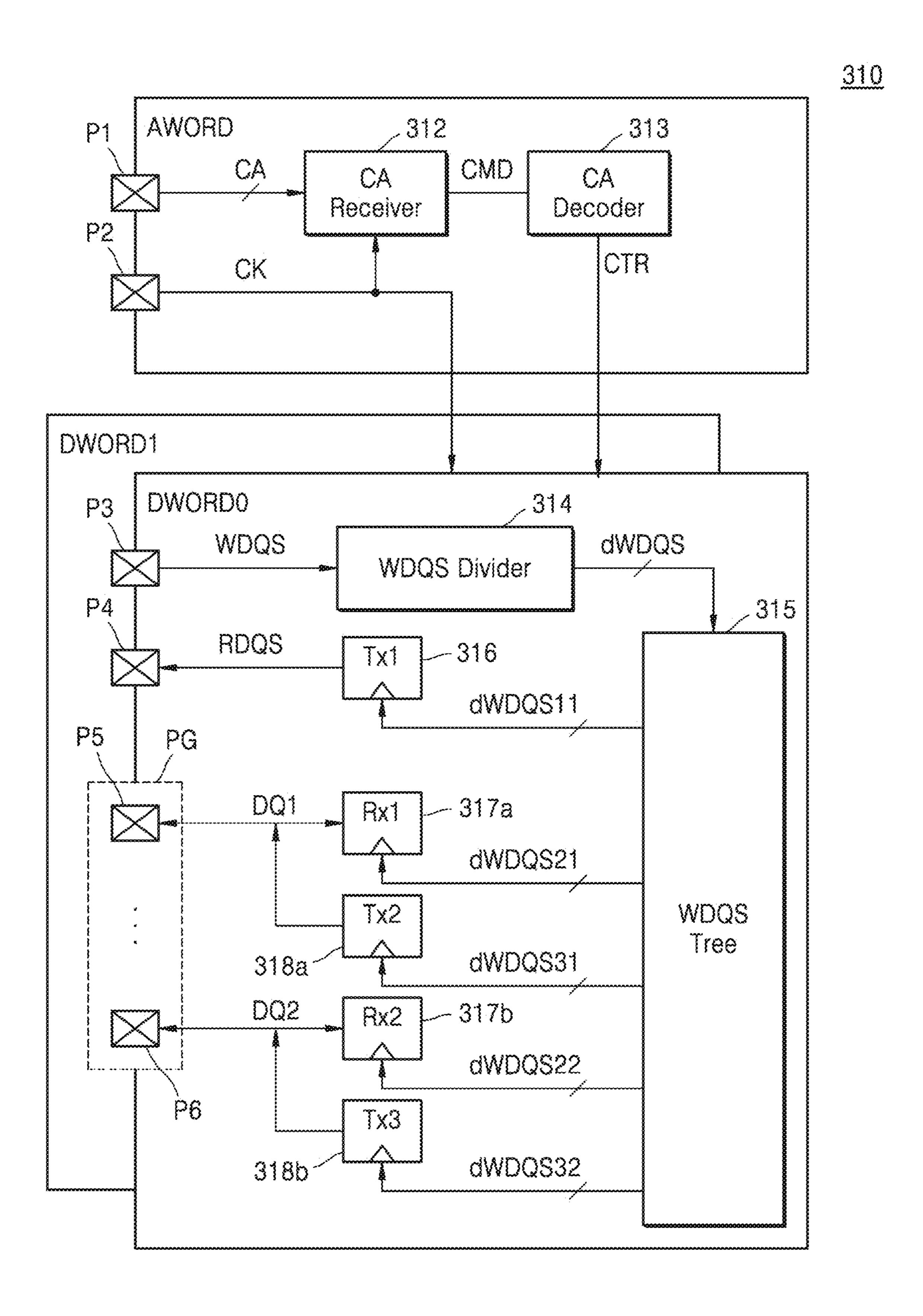

- FIG. 14 is a block diagram showing an example embodiment of the buffer die of FIG. 13;

4

- FIG. 15 shows an example pin map of pins included in the stacked memory device of FIG. 13;

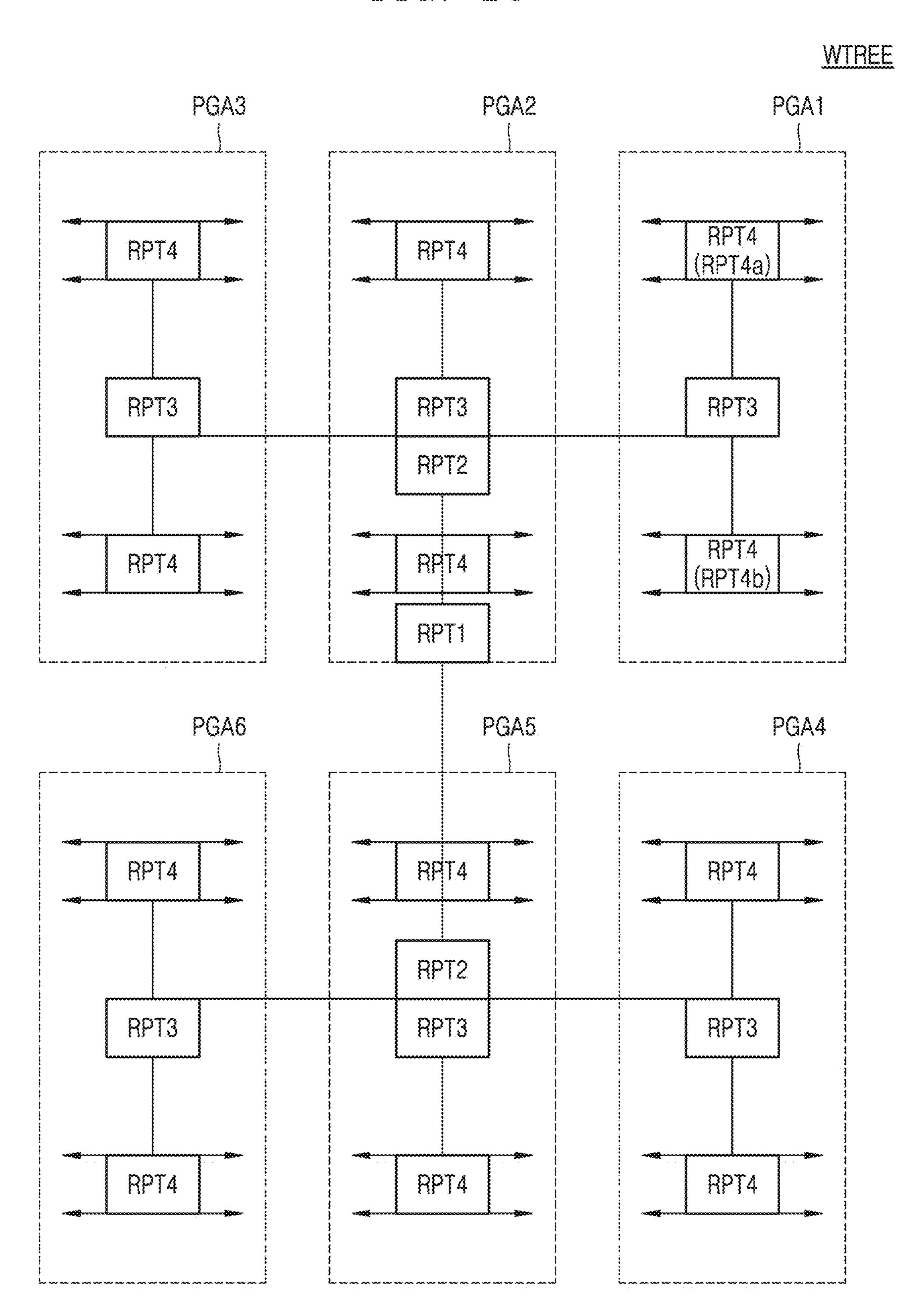

- FIG. 16 shows an example configuration of a WDQS tree corresponding to the pin map of FIG. 15;

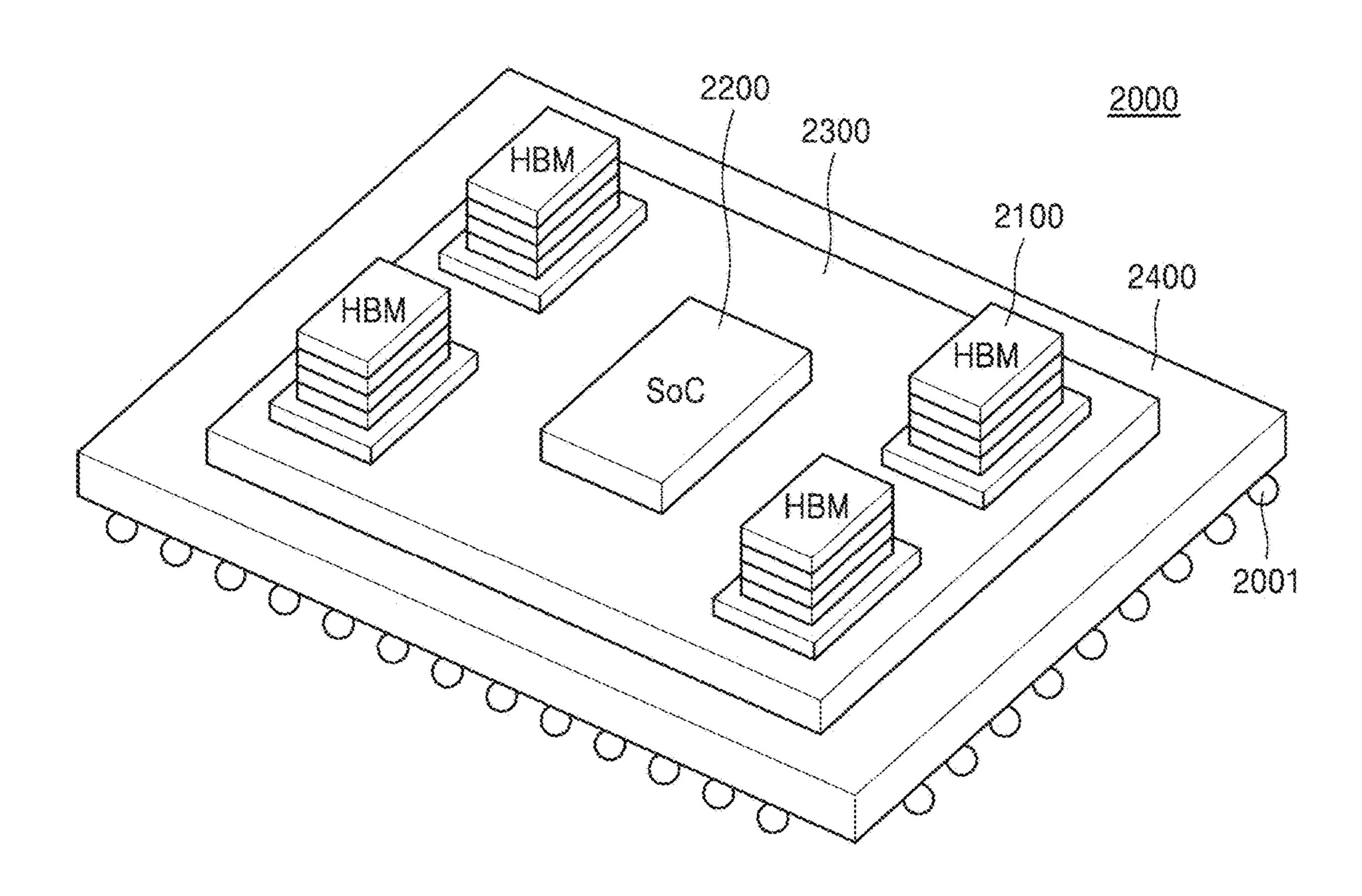

- FIG. 17 is a diagram illustrating a semiconductor package according to an example embodiment;

- FIG. 18 is a diagram illustrating a semiconductor package according to an example embodiment; and

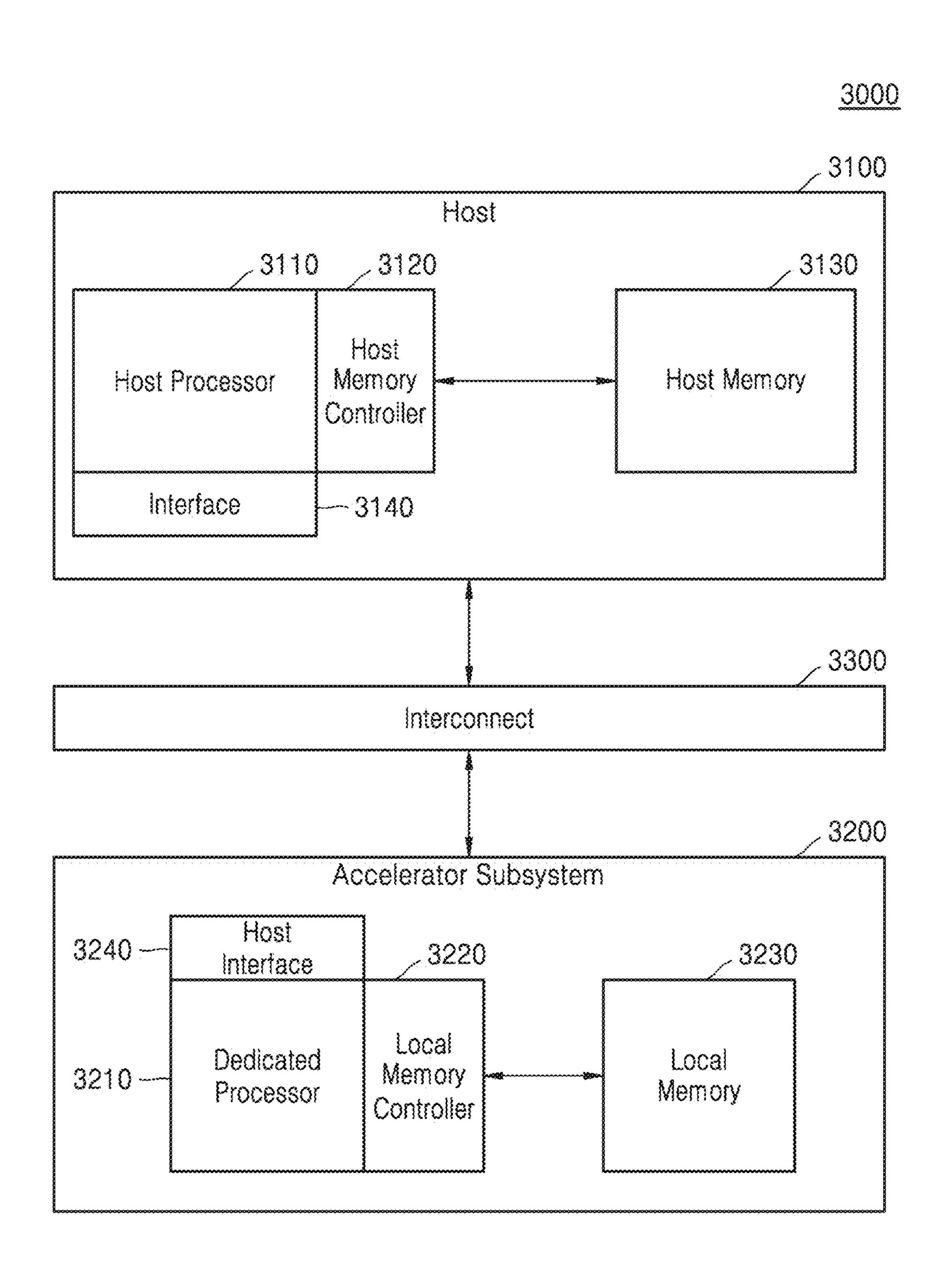

- FIG. **19** is a block diagram illustrating a computing system according to an example embodiment.

# DETAILED DESCRIPTION OF THE EMBODIMENTS

In the following, example embodiments illustrating the inventive concepts will be described in detail so that those skilled in the art easily carry out the inventive concepts.

FIG. 1 is a block diagram illustrating a memory system according to an example embodiment. Referring to FIG. 1, a memory system 10 may include a memory controller 100 and a memory device 200. The memory controller 100 may control the overall operation of the memory device 200. For example, the memory controller 100 may control the memory device 200 such that data is output from the memory device 200 and/or data is stored in the memory device 200. The memory controller 100 may be implemented as part of a system-on-chip (SoC), but example embodiments are not limited thereto.

The memory controller 100 may include a host interface circuit 110, a training controller 120, and a register 130. The host interface circuit 110 may generate a clock signal CK and transmit the clock signal CK to the memory device 200. The clock signal CK may be a signal that periodically toggles between a high level and a low level. The host interface circuit 110 may transmit command/address signals CA including a command CMD and/or an address ADD to the memory device 200 based on the toggle timing of the clock signal CK. The command/address signals CA may be transmitted to the memory device 200 through a plurality of signal lines.

The host interface circuit 110 may also generate a write data strobe signal WDQS and transmit the write data strobe signal WDQS to the memory device 200. The write data strobe signal WDQS may be or correspond to a signal that periodically toggles between a high level and a low level (See FIG. 8). The host interface circuit 110 may transmit data signals DQ including the data DATA to the memory device 200 based on the toggle timing of the write data strobe signal WDQS. The data signals DQ may be transmitted to the memory device 200 through a plurality of signal lines.

The host interface circuit 110 may receive a read data strobe signal RDQS from the memory device 200. The read data strobe signal RDQS may be or correspond to a signal that periodically toggles between a high level and a low level. The host interface circuit 110 may receive the data signals DQ from the memory device 200 and sample the data signals DQ based on the toggle timing of the read data strobe signal RDQS. Accordingly, the host interface circuit 110 may obtain data DATA from the data signals DQ.

The training controller 120 may control training operations for the memory device 200. The training controller 120 may determine a training value through training the memory device 200. Specifically, the training controller 120 determining the training value represents the training controller 120 determining the transmission timing of each of the data signals DQ transmitted from the host interface circuit 110,

and determining the receiving timing of each of the data signals DQ received by the host interface circuit 110. Accordingly, transmission timing information and receiving timing information on the data signals DQ may be generated. Here, the transmission timing corresponds to a timing for the host interface circuit 110 to transmit the data signals DQ including the data DATA to the memory device 200, and the specific time (or timing) at which the data DATA is transmitted to the memory device 200 may vary according to the transmission timing. The receiving timing corresponds to a timing for the host interface circuit 110 to sample the data signals DQ received from the memory device 200, and the specific time (or timing) at which each of the data signals DQ is sampled may vary according to the receiving timing.

The training controller 120 may be implemented with hardware including analog circuits and/or digital circuits, and/or may be implemented with software including a plurality of instructions executed by a central processing unit (CPU) inside the memory controller 100.

The register 130 may store training values generated from the training controller 120. For example, the register 130 may store transmission timing information and receiving timing information generated through training.

In some example embodiments, after the training, the host 25 interface circuit 110 may transmit data signals DQ based on the transmission timing information stored in the register 130, and may receive data signals DQ based on the receiving timing information stored in the register 130. The host interface circuit 110 may adjust the transmission and recep- 30 tion time of the data signals DQ according to the transmission timing information and the receiving timing information, respectively. For example, the host interface circuit 110 may delay the transmission time of each of the data signals DQ according to the transmission timing information on the 35 data signals DQ. In this case, a time at which data DATA included in the data signals DQ is transmitted to the memory device 200 may be delayed. The host interface circuit 110 may delay the reception time of the data signals DQ according to the receiving timing information. In this case, a time 40 at which the data DATA included in the data signals DQ is obtained from the memory controller 100 may be delayed.

The memory device 200 may operate under the control of the memory controller 100. For example, the memory device 200 may output stored data and/or may store data provided 45 from the memory controller 100 under the control of the memory controller 100.

The memory device 200 may include a memory interface circuit 210 and a memory bank 220. The memory interface circuit 210 may receive a clock signal CK from the memory 50 controller 100. The memory interface circuit 210 may receive command/address signals CA from the memory controller 100. The memory interface circuit 210 may sample the command/address signals CA based on the toggle timing (e.g., a rising edge and/or a falling edge) of the clock 55 signal CK. Accordingly, the memory interface circuit 210 may obtain a command CMD and/or an address ADD included in the command/address signals CA.

FIG. 1 shows that the command CMD and the address ADD are transmitted from the memory controller 100 to the 60 memory device 200 through the same channel (e.g., command/address signals CA) but the example embodiment is not limited to this. For example, the command CMD and the address ADD may be transmitted from the memory controller 100 to the memory device 200 using different channels. 65

The memory interface circuit 210 may receive a write data strobe signal WDQS and data signals DQ from the

6

memory controller 100. The memory interface circuit 210 may sample the data signals DQ based on the toggle timing (e.g., a rising edge and/or a falling edge) of the write data strobe signal WDQS. Accordingly, the memory interface circuit 210 may obtain data DATA from the data signals DQ based on the sampling.

The memory interface circuit 210 may generate a read data strobe signal RDQS and transmit the read data strobe signal RDQS to the memory controller 100. The read data strobe signal RDQS may correspond to a signal that periodically toggles between a high level and a low level. In some example embodiments, the memory interface circuit 210 may generate a read data strobe signal RDQS based on the write data strobe signal WDQS received from the 15 memory controller 100. The memory interface circuit 210 may transmit data signals DQ to the memory controller 100 based on toggle timing of the write data strobe signal WDQS. Accordingly, the data signals DQ may be aligned with edge timing of the read data strobe signal RDQS and 20 transmitted to the memory controller 100. However, example embodiments are not limited thereto, and the memory interface circuit 210 may generate a read data strobe signal RDQS based on the clock signal CK, and transmit data signals DQ to the memory controller 100 based on the read data strobe signal RDQS.

In some example embodiments, each of the write data strobe signal WDQS and the read data strobe signal RDQS may have a frequency which is two times greater than (double of) the frequency of the clock signal CK. For example, the frequency of the clock signal CK may be 1.6 GHz, and the frequency of each of the write data strobe signal WDQS and the read data strobe signal RDQS may be 3.2 GHz. However, example embodiments are not limited thereto, and the frequency of each of the write data strobe signal WDQS and the read data strobe signal RDQS may be N times (N is a natural number greater than or equal to two) the frequency of the clock signal CK.

The memory interface circuit **210** may generate a control signal iCTRL based on the command CMD and the address ADD received from the memory controller **100** and may provide the control signal iCTRL to the memory bank **220**. For example, the control signal iCTRL may include a row address and a column address. However, the example embodiments are not limited thereto.

The memory bank 220 may include a plurality of memory cells connected to word lines and bit lines. For example, each of the plurality of memory cells may be or correspond to a dynamic random access memory (DRAM) cell, e.g., a one-transistor/one capacitor DRAM cell. In this case, the host interface circuit 110 and the memory interface circuit 210 may communicate input/output signals based on one of standards such as Double Data Rate (DDR), Low Power Double Data Rate (LPDDR), Graphics Double Data Rate (GDDR), Wide I/O, High Bandwidth Memory (HBM), Hybrid Memory Cube (HMC), or the like. However, example embodiments are not limited thereto, and each of the plurality of memory cells may be various types of memory cells such as a resistive RAM (RRAM) cell.

The memory bank 220 may write data DATA to memory cells or read data DATA from memory cells in response to the control signal iCTRL. Although not shown in FIG. 1, the memory bank 220 may further include a row decoder, a column decoder, and a sense amplifier for write and/or read operations.

As described above, the memory controller 100 and the memory device 200 may transmit and receive data signals DQ based on the transmission timing and the receiving

timing determined through training. However, example embodiments are not limited thereto. The training controller 120 may determine transmission timing and/or receiving timing of various input/output signals transmitted or received based on the clock signal CK, the write data strobe 5 signal WDQS, and/or the read data strobe signal RDQS in addition to the data signals DQ through training. For example, the training controller 120 may determine transmission timing and/or receiving timing of the command/ address signals CA and various control signals (e.g., data bus 10 inversion (DBI), data parity (DPAR), and the like) transmitted and/or received between the memory controller 100 and the memory device 200. In the following, for convenience of description, some example embodiments will be described in detail based on the data signals DQ, but example embodi- 15 ments are not limited thereto, and example embodiments to be described below may be applied to various input/output signals including the command/address signals CA.

FIG. 2 is a flowchart illustrating an example operation of the memory system of FIG. 1. Referring to FIGS. 1 and 2, 20 in operation S11, the memory system 10 may perform initialization. When the memory system 10 is powered-up, the memory controller 100 and the memory device 200 may perform initialization according to a predetermined method. During the initialization, for example, the memory controller 25 100 may provide a power voltage to the memory device 200, perform various initial setting operations, and read necessary information from the memory device 200.

In operation S12, the memory system 10 may perform a read training operation. In order to optimize (or, improve) 30 the signal integrity or data-eye of the data DATA received from the memory device 200 to the memory controller 100, the memory controller 100 may determine receiving timing for the data signals DQ, and generate receiving timing information.

In operation S13, the memory system 10 may perform a write training operation. In order to optimize (or, improve) the signal integrity or data-eye of data DATA transmitted to the memory device 200 from the memory controller 100, the memory controller 100 may determine transmission timing 40 for the data signals DQ, and generate transmission timing information.

After the initialization and (read and write) training operation of operations S11 to S13 described above are performed, in operation S14, the memory system 10 may 45 perform a normal operation. For example, the memory controller 100 may obtain the data DATA by sampling the data signals DQ received from the memory device 200 based on the receiving timing determined according to the read training operation. The memory controller 100 may transmit 50 the data signals DQ to the memory device 200 based on the transmission timing determined according to the write training operation.

In some example embodiments, before operation S12, the memory system 10 may determine the transmission timing 55 of the command/address signal CA by performing training on the command/address signal CA. In some example embodiments, before operation S12, the memory system 10 performs training on the write data strobe signal WDQS so that the toggle timing of the clock signal CK and the toggle 60 timing of the write data strobe signal WDQS are aligned.

FIG. 3 is a diagram illustrating an example of a read training operation and a write training operation of the memory system of FIG. 1. Referring to FIG. 3, the memory device 200 may include a write data strobe pin W\_P, a read 65 data strobe pin R\_P, and data pins D\_P. The memory controller 100 may transmit a write data strobe signal

8

WDQS to the memory device **200** through a write data strobe pin W\_P, and receive a read data strobe signal RDQS from the memory device **200** through a read data strobe pin R\_P. The memory controller **100** may transmit data signals DQ to the memory device **200** through the data pins D\_P and/or may receive data signals DQ from the memory device **200**.

The data pins D\_P of the memory device 200 may be divided into a first pin group PG1 and a second pin group PG2. Each of the first pin group PG1 and the second pin group PG2 may include at least two data pins (e.g., at least or exactly eight data pins). For example, the first pin group PG1 may include a first data pin D\_P1 and a second data pin D\_P2, and the second pin group PG2 may include a third data pin D\_P3 and a fourth data pin D\_P4. For example, the first data pin D\_P1 and the second data pin D\_P2 may be positioned adjacent to each other, and the third data pin D\_P3 and the fourth data pin D\_P4 may be positioned to be adjacent to each other. The memory controller 100 may transmit the first to fourth data signals DQ1 to DQ4 to the memory device 200 through the first to fourth data pins D\_P1 to D\_P4, or receive the first to fourth data signals DQ1 to DQ4 from the memory device 200.

The memory controller 100 may store group information on pins of the memory device 200. For example, the memory controller 100 may store information on data pins D\_P included in the first pin group PG1 and the second pin group PG2. For example, group information on pins may be predetermined by standards. For example, group information on pins may be stored in the register 130 of FIG. 1.

The memory controller 100 may perform training for each pin group. The memory controller 100 may determine a first transmission timing TT1 corresponding to the first pin group PG1 by performing a write training operation on the first pin 35 group PG1, and determine a second transmission timing TT2 corresponding to the second pin group PG2 by performing a write training operation on the second pin group PG2. The determined transmission timing TT1 and TT2 may be stored in the register 130 corresponding to the first pin group PG1 and the second pin group PG2, respectively. Transmission timing of the data pins D\_P included in one pin group may be determined identically. For example, the transmission timing of the first data pin D\_P1 and the transmission timing of the second data pin D\_P2 may be determined by the same value (e.g. the first transmission timing TT1). The memory controller 100 may determine a first receiving timing RT1 corresponding to the first pin group PG1 by performing a read training operation on the first pin group PG1, and determine a second receiving timing RT2 corresponding to the second pin group PG2 by performing a read training operation on the second pin group PG2. The determined receiving timing RT1 and RT2 may be stored in the register 130 corresponding to the first pin group PG1 and the second pin group PG2, respectively. Receiving timing of the data pins D\_P included in one pin group may be determined identically. For example, the receiving timing of the first data pin D\_P1 and the receiving timing of the second data pin D\_P2 may be determined by the same value (e.g. the first receiving timing TT1). Accordingly, transmission timing and receiving timing may be determined for each pin group.

According to some example embodiments, training for a pin group may be performed by training for a specific pin among pins of the pin group. The training value (e.g. transmission timing or receiving timing) for the specific pin may be used for the pin group. The training operation for a specific pin of the memory device 200 refers to an operation of determining an optimal transmission timing of a signal

transmitted to a specific pin and/or refers to an operation of determining an optimal receiving timing of a signal received through a specific pin.

In the write operation after training, the memory controller 100 may transmit the first data signal DQ1 and the second 5 data signal DQ2 to the memory device 200 based on the first transmission timing TT1 and may transmit the third data signal DQ3 and the fourth data signal DQ4 to the memory device 200 based on the second transmission timing TT2. The memory device 200 may sample each of the first to 10 fourth data signals DQ1 to DQ4 based on the write data strobe signal WDQS.

In a read operation after training, the memory device 200 may transmit the first to fourth data signals DQ1 to DQ4 to the memory controller 100. The memory controller 100 may 15 sample the first data signal DQ1 and the second data signal DQ2 based on the first receiving timing RT1 using the read strobe signal RDQS, and may sample the third data signal DQ3 and the fourth data signal DQ4 based on the second receiving timing RT2.

FIG. 3 illustrates that the data pins D\_P are divided into two pin groups PG1 and PG2, but example embodiments are not limited thereto. For example, the data pins D\_P may be divided into three or more pin groups.

As described above, according to some example embodi- 25 ments of inventive concepts, training may be performed for each group of data pins D\_P. In this case, the memory controller 100 may store the transmission timing and receiving timing for each group, without having to store the transmission timing and receiving timing for each of the data 30 pin group PG2. pins D\_P. Therefore, when training is performed for each group on the data pins D\_P, the training speed may be improved compared to when training is performed, e.g. performed separately, for each pin for the data pins D\_P, transmission timing and the receiving timing may be reduced. Accordingly, resources used for training may be reduced.

FIG. 4 is an example block diagram of the memory device of FIG. 3. Referring to FIGS. 3 and 4, the memory device 40 200 may include a first pin group PG1, a second pin group PG2, and a write data strobe pin W\_P, and may also include a first circuit block 201 and a second circuit block 202. The first circuit block 201 may receive the first data signals DQ\_1 through the first pin group PG1 and may receive the 45 write data strobe signal WDQS through the write data strobe pin W\_P. The second circuit block 202 may receive the second data signals DQ\_2 through the second pin group PG2 and may receive the write data strobe signal WDQS through the write data strobe pin W\_P. For example, the first circuit 50 block 201 and the second circuit block 202 may operate based on one write data strobe signal WDQS.

The first circuit block 201 may sample the first data signals DQ\_1 based on the write data strobe signal WDQS. In this case, the first data signals DQ\_1 may be transmitted 55 from the memory controller 100 based on one training value (e.g., the first transmission timing TT1). The second circuit block 202 may sample the second data signals DQ\_2 based on the write data strobe signal WDQS. In this case, the second data signals DQ\_2 may be transmitted from the 60 memory controller 100 based on one training value (e.g., the second transmission timing TT2).

In some example embodiments, each of the first circuit block 201 and the second circuit block 202 may include a phase comparator. Each of the first circuit block **201** and the 65 second circuit block 202 may compare the phase of the write data strobe signal WDQS and the data signal received

**10**

through the data pin through a phase comparator in a training process for the data pin. For example, a phase comparison result may be generated by sampling the data signal based on the write data strobe signal WDQS through the phase comparator. The memory controller 100 may determine a training value for the data pin based on the result of the phase comparison. For example, the memory controller 100 may transmit a data signal to the memory device 200 by varying the phase (i.e. timing) of the data signal. The memory controller 100 may receive phase comparison results corresponding to various phases (i.e. timing) from the memory device 200. The memory controller 100 may determine a training value such that a timing window between the write data strobe signal WDQS and the data signal among the phase comparison results is maximized.

In some example embodiments, the first pin group PG1 and the first circuit block 201 and the second pin group PG2 and the second circuit block 202 may be disposed on a single silicon substrate. In some example embodiments, the first 20 pin group PG1 and the first circuit block 201 and the second pin group PG2 and the second circuit block 202 are shifted, and/or mirrored relationship.

FIG. 5 is a flowchart illustrating an example of a read training operation of the memory controller of FIG. 3. Referring to FIGS. 3 and 5, in operation S101, the memory controller 100 may select one data pin from a specific (or, predetermined) pin group. For example, the memory controller 100 may select a first data pin D\_P1 from the first pin group PG1 and select a third data pin D\_P3 from the second

In operation S102, the memory controller 100 may perform read training on the selected data pin. The memory controller 100 may perform read training to determine a receiving timing of a data signal received from the memory and/or the capacity of the register 130 for storing the 35 device 200 through the selected data pin. For example, the memory controller 100 may determine the receiving timing of the first data signal DQ1 as the first receiving timing RT1 by performing read training on the first data pin D\_P1.

In operation S103, the memory controller 100 may determine the receiving timing determined according to the read training as the receiving timing corresponding to the pin group. The memory controller 100 may store the determined receiving timing corresponding to the pin group. For example, the memory controller 100 may determine a first receiving timing RT1 determined according to read training on the first data pin D\_P1 as a receiving timing corresponding to the first pin group PG1. The memory controller 100 may set the first receiving timing RT1 corresponding to the first pin group PG1.

FIG. 6 is a flowchart illustrating an example of a write training operation of the memory controller of FIG. 3. Referring to FIGS. 3 and 6, in operation S111, the memory controller 100 may select one data pin from a specific (or, predetermined) pin group. For example, the memory controller 100 may select a first data pin D\_P1 from the first pin group PG1 and select a third data pin D\_P3 from the second pin group PG2; however, example embodiments are not limited thereto.

In operation S112, the memory controller 100 may perform write training on the selected data pin. The memory controller 100 may perform write training to determine a transmission timing of a data signal transmitted to the memory device 200 through the selected data pin. For example, the memory controller 100 may determine the transmission timing of the first data signal DQ1 as the first transmission timing TT1 by performing write training on the first data pin D\_P1. In this case, write training may be

performed so that a timing window between the write data strobe signal WDQS and the first data signal DQ1 is maximized.

In operation S113, the memory controller 100 may determine the transmission timing determined according to the 5 write training as the transmission timing corresponding to the pin group. The memory controller 100 may store the determined transmission timing corresponding to the pin group. For example, the memory controller 100 may determine a first transmission timing TT1 determined according to write training on the first data pin D\_P1 as a transmission timing corresponding to the first pin group PG1. The memory controller 100 may set the first transmission timing TT1 corresponding to the first pin group PG1.

In an example embodiment, unlike that shown in FIGS. 5 15 may be included in the host interface circuit 110 of FIG. 1. and 6, the memory controller 100 may perform training on each pin of one of the plurality of pin groups, and then determine a training value corresponding to the pin group based on training results for the pins. In an example embodiment, the training value determined corresponding to one 20 pin group may be used to determine a training value for another pin group. In this case, training for each pin of another pin group may be omitted.

As described above, After read training is performed for each group on the data pins D\_P, the memory controller 100 25 may sample each of the data signals received from the memory device 200 through one pin group at the same (e.g., substantially the same) time. In other words, sampling timing skew between sampling timing for the data signals may be minimized (or, reduced or removed). In this case, in 30 order to optimize (or, improve) the data bit error rate of the sampled data signals, each of the data signals transmitted from the memory device 200 through one pin group should or must be transmitted to the memory controller 100 at the same time. In other words, the data skew between data 35 signals inputted to the memory controller 100 should or must be minimized (or, reduced or removed).

As described above, after write training is performed for each group on the data pins D\_P, the memory controller 100 may transmit each of the data signals corresponding to one 40 pin group to the memory device 200 at the same time. In other words, the data skew between data signals outputted from the memory controller 100 may be minimized. In this case, memory device 200 may sample each of the data signals inputted to the memory device 200 at the same time. 45 In other words, sampling timing skew between sampling timing for the data signals inputted to the memory device 200 may be minimized. Since each of the data signals is transmitted from the memory controller 100 at the same time, when each of the data signals inputted to the memory 50 device 200 is sampled at the same time, the data bit error rate of the sampled data signals may be optimized.

In the following, in order to the data bit error rate of the data signals sampled by the memory controller 100 in read operation, the memory system 10 that minimizes data skew between the data signals inputted to the memory controller 100 through one pin group will be described in detail. And, in order to the data bit error rate of the data signals sampled by the memory device 200 in write operation, the memory system 10 that minimizes sampling timing skew between 60 sampling timing for the data signals inputted to the memory device 200 through one pin group will be described in detail.

FIG. 7 is a block diagram schematically illustrating the memory system of FIG. 3. For convenience of explanation, configurations of the memory system 10 for performing a 65 write operation according to the write training result (i.e., first and second transmission timing TT1 and TT2)

described with reference to FIG. 3 are described, but example embodiments are not limited thereto.

Referring to FIG. 7, the memory controller 100 may include a write data strobe pin W\_P', a first pin group PG1', and a second pin group PG2'. The write data strobe pin W\_P', the first pin group PG1', and the second pin group PG2' may correspond to the write data strobe pin W\_P, the first pin group PG1, and the second pin group PG2 of the memory device 200. The memory controller 100 may include a phase locked loop 111, a phase controller 112, a delay circuit 113, a first transmitter group 114, and a second transmitter group 115. For example, the phase locked loop 111, the phase controller 112, the delay circuit 113, the first transmitter group 114, and the second transmitter group 115

The phase locked loop 111 may generate a write data strobe signal WDQS that toggles with a specific (or, predetermined) phase. The write data strobe signal WDQS may be provided to the phase controller 112 and may be transmitted to the memory device 200 through the write data strobe pin W\_P'. In an example embodiment, although not shown in FIG. 7, the write data strobe signal WDQS may be transmitted to the memory device 200 through a separate transmitter (or buffer) positioned between the phase locked loop 111 and the write data strobe pin W\_P'.

The phase controller 112 may generate a write data strobe signal pWDQS whose phase is adjusted by adjusting a phase of the write data strobe signal WDQS. For example, the phase controller 112 may adjust the phase of the write data strobe signal WDQS so that the phase difference between the write data strobe signal WDQS and the phase-adjusted write data strobe signal pWDQS is 90 degrees.

The delay circuit 113 may delay the write data strobe signal pWDQS whose phase is adjusted according to the write training result. The delay circuit 113 may delay the write data strobe signal pWDQS whose phase is adjusted according to the first transmission timing TT1 corresponding to the first pin group PG1 to generate the first write delay signal WDS1. The delay circuit 113 may delay the write data strobe signal pWDQS whose phase is adjusted according to the second transmission timing TT2 corresponding to the second pin group PG2 to generate the second write delay signal WDS2. The first write delay signal WDS1 may be provided to the first transmitter group 114, and the second write delay signal WDS2 may be provided to the second transmitter group 115. In this case, the first write delay signal WDS1 may have a toggle timing corresponding to the first transmission timing TT1, and the second write delay signal WDS2 may have a toggle timing corresponding to the second transmission timing TT2.

The first transmitter group 114 may transmit data signals including data to the memory device 200 through the first pin group PG1' based on the toggle timing of the first write delay signal WDS1. For example, the first transmitter group 114 may transmit the first data signal DQ1 including the first data DATA1 to the memory device 200 through the first data pin D\_P1' based on the toggle timing of the first write delay signal WDS1. The first transmitter group 114 may transmit the second data signal DQ2 including the second data DATA2 to the memory device 200 through the second data pin D\_P2' based on the toggle timing of the first write delay signal WDS1. Accordingly, the first transmitter group 114 may transmit each of the data signals to the memory device 200 at the same transmission timing (i.e., the first transmission timing TT1).

The second transmitter group 115 may transmit data signals including data to the memory device 200 through the

second pin group PG2' based on the toggle timing of the second write delay signal WDS2. For example, the second transmitter group 115 may transmit the third data signal DQ3 including the third data DATA3 to the memory device 200 through the third data pin D\_P3' based on the toggle timing of the second write delay signal WDS2. The second transmitter group 115 may transmit the fourth data signal DQ4 including the fourth data DATA4 to the memory device 200 through the fourth data pin D\_P4' based on the toggle timing of the second write delay signal WDS2. Accordingly, the second transmitter group 115 may transmit each of the data signals to the memory device 200 at the same transmission timing (i.e., the second transmission timing TT2).

Data signals outputted through the first pin group PG1' may be transmitted to the first pin group PG1 through 15 corresponding signal lines. In this case, signal lines may be configured to maintain minimized data skew between data signals transmitted to the first pin group PG1. For example, lengths and/or resistances of signal lines connecting the data pins of the first pin group PG1' and the data pins of the first 20 pin group PG1 may be the same or substantially the same. As described above, since the data skew between the data signals outputted through the first pin group PG1' can be minimized, when the lengths of signal lines through which data signals are transmitted are the same (assuming that the 25 physical properties of the signal lines are also the same), minimized data skew between data signals may be maintained until data signals reach the first pin group PG1. For example, when the length of the first signal line DL1 through which the first data signal DQ1 is transmitted and the length 30 of the second signal line DL2 through which the second data signal DQ2 is transmitted are the same, data skew between the first and second data signals DQ1 and DQ2 inputted to the memory device 200 through the first and second data pins D\_P1 and D\_P2 may be kept minimized. Accordingly, 35 each of the data signals transmitted from the first transmitter group 114 may be inputted to the memory device 200 at the same time.

Likewise, signal lines may be configured to maintain minimized data skew between data signals transmitted to the 40 second pin group PG2. For example, lengths and/or resistances of signal lines connecting the data pins of the second pin group PG2' and the data pins of the second pin group PG2 may be the same. For example, when the length of the third signal line DL3 through which the third data signal 45 DQ3 is transmitted and the length of the fourth signal line DL4 through which the fourth data signal DQ4 is transmitted are the same, data skew between the third and fourth data signals DQ3 and DQ4 received by the memory device 200 through the third and fourth data pins D\_P3 and D\_P4 may 50 be minimized. Accordingly, each of the data signals transmitted from the second transmitter group 115 may be inputted to the memory device 200 at the same time.

The memory device 200 may include a write data strobe signal (WDQS) tree 211, a first receiver group 212, and a second receiver group 213. For example, the write data strobe signal (WDQS) tree 211, the first receiver group 212, and the second receiver group 213 may be included in the memory interface circuit 210 of FIG. 1. For example, the write data strobe signal (WDQS) tree 211, the first receiver 60 group 212, and the second receiver group 213 may correspond to the first circuit block 201 and the second circuit block 202 of FIG. 4. The WDQS tree 211 may transmit to the first receiver group 212 the first internal write data strobe signal dWDQS1 toggling based on the write data strobe 65 signal WDQS received through the write data strobe pin W\_P and transmit the toggled second internal write data

**14**

strobe signal dWDQS2 to the second receiver group 213. In an example embodiment, the WDQS tree 211 may include a plurality of repeaters, and may transmit the first internal write data strobe signal dWDQS1 and the second internal write data strobe signal dWDQS2 through the repeaters.

In an example embodiment, the first internal write data strobe signal dWDQS1 and the second internal write data strobe signal dWDQS2 may be/correspond to signals generated by delaying the write data strobe signal WDQS through the WDQS tree 211. In this case, toggle timing of the write data strobe signal WDQS and the first internal write data strobe signal dWDQS1 may be different from each other, and toggle timing of the write data strobe signal WDQS and the second internal write data strobe signal dWDQS2 may be different from each other. The toggle timing skew between the write data strobe signal WDQS and internal write data strobe signal (e.g. dWDQS1 or dWDQS2) may be generated by the WDQS tree 211. In this case, the transmission timing determined through training in the memory controller 100 may compensate for the toggle timing skew by the WDQS tree **211**. Accordingly, a skew between the write data strobe signal WDQS and the first internal write data strobe signal dWDQS1 may be compensated by the first transmission timing TT1, and a skew between the write data strobe signal WDQS and the second internal write data strobe signal dWDQS2 may be compensated by the second transmission timing TT2.

FIG. 7 illustrates an example in which the first and second internal write data strobe signals dWDQS1 and dWDQS2 are generated by delaying the write data strobe signal WDQS through the WDQS tree 211, but example embodiments are limited thereto. In some example embodiments, the first internal write data strobe signal dWDQS1 and the second internal write data strobe signal dWDQS2 may be signals generated by delaying the divided write data strobe signal through the WDQS tree 211. In this case, a write data strobe signal divided from the write data strobe signal WDQS may be generated through a divider located between the write data strobe pin W\_P and the WDQS tree 211.

The first receiver group 212 may sample each of the data signals received through the first pin group PG1 based on the toggle timing of the first internal write data strobe signal dWDQS1. Accordingly, the first receiver group 212 may obtain data from data signals received through the first pin group PG1. For example, the first receiver group 212 may sample the first data signal DQ1 received through the first data pin D\_P1 to obtain the first data DATA1 based on the toggle timing of the first internal write data strobe signal dWDQS1 and obtain the second data DATA2 by sampling the second data signal DQ2 received through the second data pin D\_P2.

The second receiver group 213 may sample each of the data signals received through the second pin group PG2 based on the toggle timing of the second internal write data strobe signal dWDQS2. Accordingly, the second receiver group 213 may obtain data from data signals received through the second pin group PG2. For example, the second receiver group 213 may obtain the third data DATA3 by sampling the third data signal DQ3 received through the third data pin D\_P3 based on the toggle timing of the second internal write data strobe signal dWDQS2 and obtain the fourth data DATA4 by sampling the fourth data signal DQ4 received through the fourth data pin D\_P4.

In such a manner, when each of the data signals received through one pin group is sampled based on the same toggle timing (e.g., the toggle timing of the first internal write data strobe signal dWDQS1 or the toggle timing of the second

internal write data strobe signal dWDQS2), sampling timing skew for data signals can be minimized.

As described above, in relation to the memory system 10 according to some example embodiments of inventive concepts, the memory controller 100 may transmit each of the 5 data signals to the memory device 200 through one pin group at the same transmission time. The memory device 200 may sample each of the data signals inputted through one pin group at the same sampling time. Accordingly, even if the write training is performed for each pin group, the data 10 bit error rate of data signals transmitted from the memory controller 100 to the memory device 200 in the write operation can be optimized.

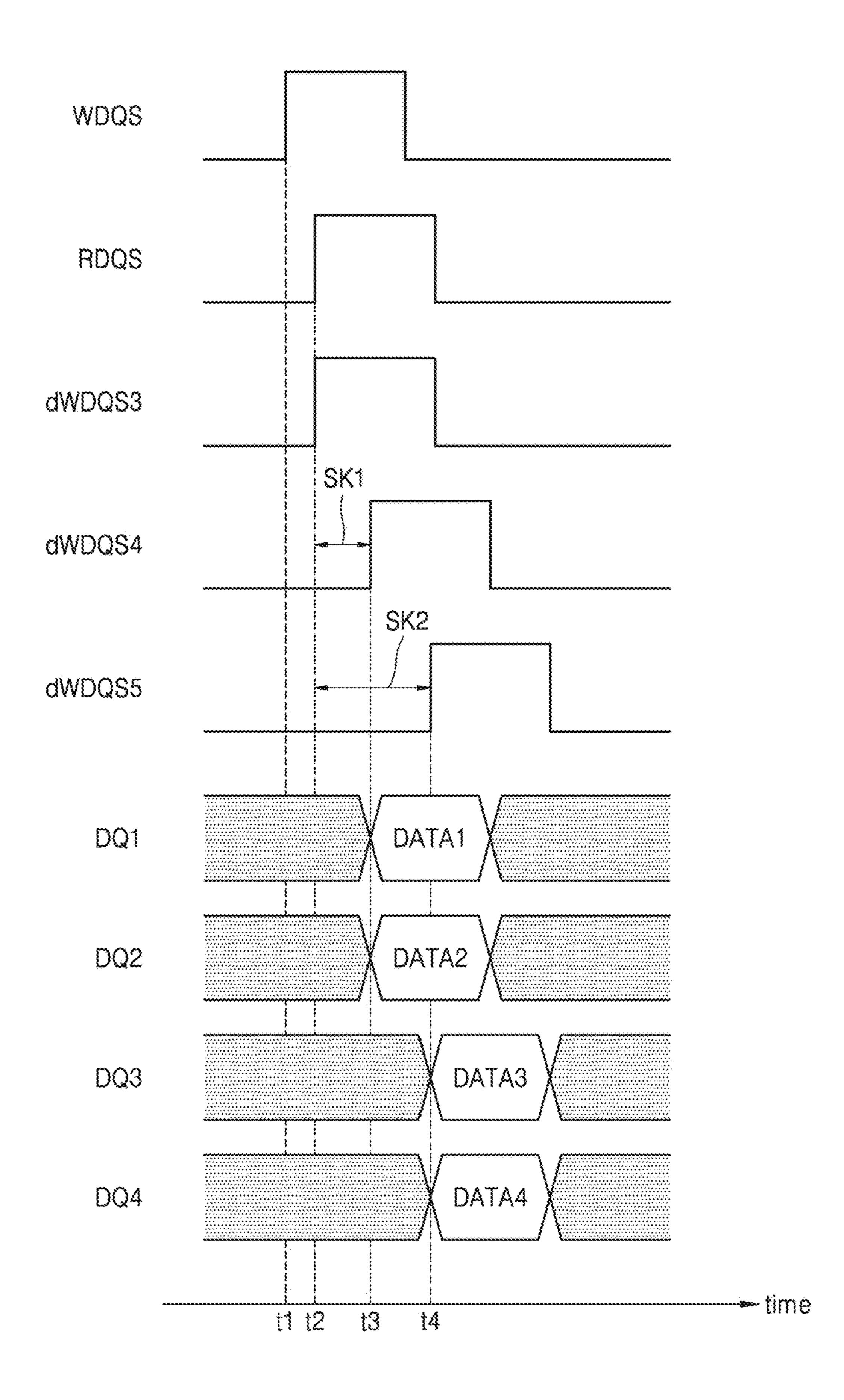

FIG. 8 is a timing diagram illustrating an example in which the memory device of FIG. 7 samples data signals. 15 Referring to FIGS. 7 and 8, a write data strobe signal WDQS received by the memory device 200 through a write data strobe pin W\_P may have a toggle timing at a first time point t1. The first internal write data strobe signal dWDQS1 transmitted to the first receiver group 212 by the WDQS tree 20 211 has a toggle timing at the second time point t2, and the second internal write data strobe signal dWDQS2 transmitted to the second receiver group 213 by the WDQS tree 211 may have a toggle timing at a third time point t3. Accordingly, a first skew SK1 between the first internal write data 25 strobe signal dWDQS1 and the write data strobe signal WDQS may be generated, and a second skew SK2 between the second internal write data strobe signal dWDQS2 and the write data strobe signal WDQS may be generated. For example, the first skew SK1 is different from the second 30 skew SK2.

The first data signal DQ1 including the first data DATA1 and the second data signal DQ2 including the second data DATA2 may be transmitted to the first receiver group 212 according to the first transmission timing TT1 for compensating for the first skew SK1. The first data signal DQ1 and the second data signal DQ2 transmitted to the first receiver group 212 may be sampled based on the toggle timing of the first internal write data strobe signal dWDQS1. In this case, a sampling margin for the first data DATA1 and the second 40 data DATA2 is secured (or, improved), so that a data bit error rate can be optimized.

The third data signal DQ3 including the third data DATA3 and the fourth data signal DQ4 including the fourth data DATA4 may be transmitted to the second receiver group 213 45 according to the second transmission timing TT2 for compensating for the second skew SK2. The third data signal DQ3 and the fourth data signal DQ4 delivered to the second receiver group 213 may be sampled based on the toggle timing of the second internal write data strobe signal 50 dWDQS2. In this case, a sampling margin for the third data DATA3 and the fourth data DATA4 is secured (or, improved), so that the data bit error rate can be optimized.

As described above, the sampling timing skew for data signals transmitted through one pin group of the memory 55 device 200 may be minimized. For example, the sampling timing for the first data signal DQ1 and the sampling timing for the second data signal DQ2 are the same. Hereinafter, a detailed configuration of a memory device for minimizing sampling timing skew for data signals transmitted through 60 one pin group will be described with reference to FIG. 9.

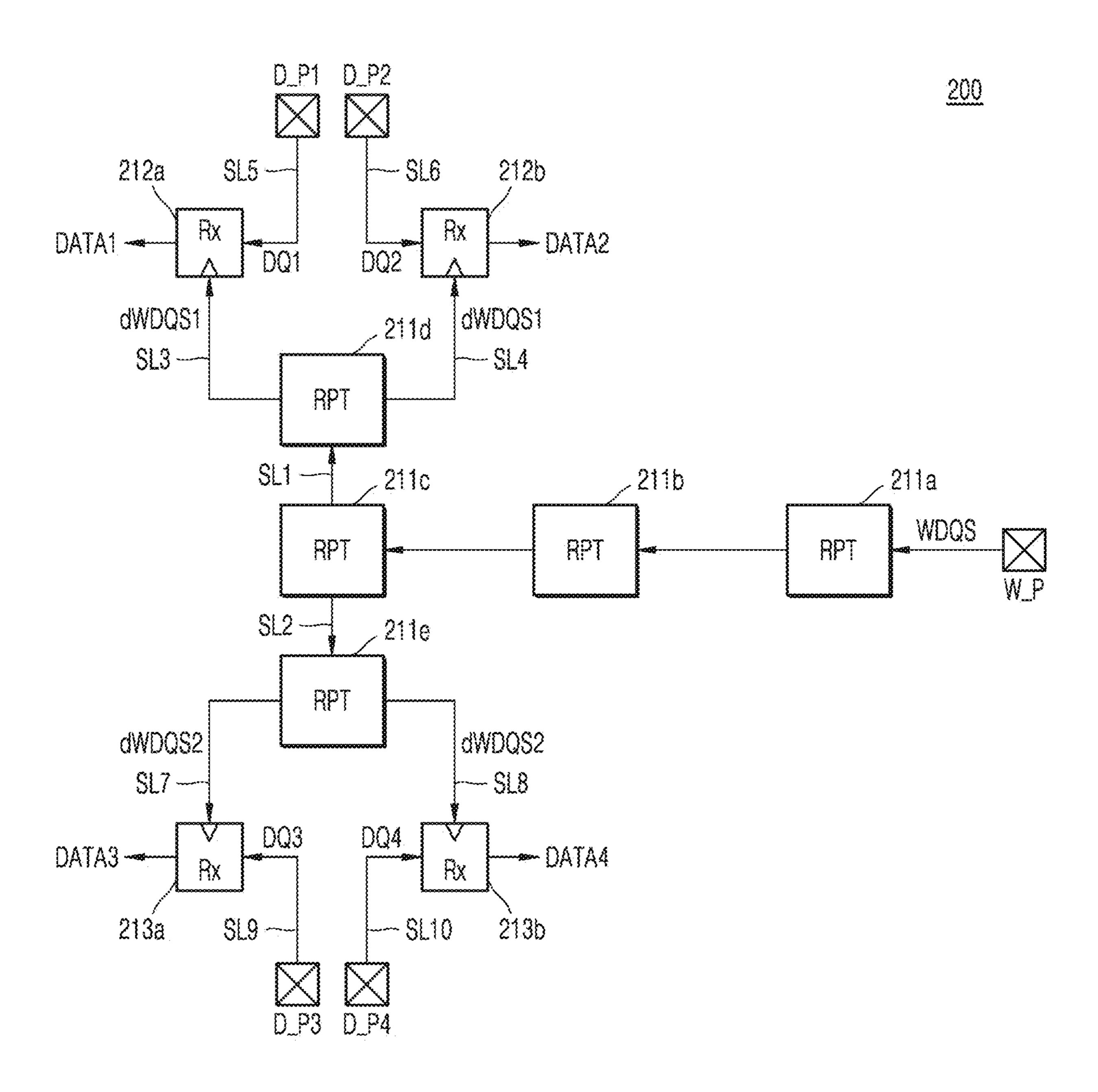

FIG. 9 is a diagram illustrating an example configuration of the memory device of FIG. 7. Referring to FIGS. 7 and 9, the memory device 200 may include a plurality of repeaters 211a to 211e and a plurality of receivers 212a, 65 212b, 213a, and 213b. The repeaters 211a to 211e may be included in the WDQS tree 211. The receivers 212a and

**16**

212b may be included in the first receiver group 212, and the receivers 213a and 213b may be included in the second receiver group 213.

The write data strobe signal WDQS received through the write data strobe pin W\_P may be transmitted to the receivers 212a and 212b, respectively, as the first internal write data strobe signal dWDQS1, through the repeaters 211a, **211**b, **211**c, and **211**d on the first path. The write data strobe signal WDQS may be transmitted to the receivers 213a and 213b as a second internal write data strobe signal dWDQS2 through the repeaters 211a, 211b, 211c, and 211e on the second path. For example, when the length of and/or resistance of the first signal line SL1 connecting the repeater 211cand the repeater 211d on the first path is different from the length of/resistance of the second signal line SL2 connecting the repeater 211c and the repeater 211e on the second path, as described with reference to FIG. 8, the toggle timing of the first internal write data strobe signal dWDQS1 and the toggle timing of the second internal write data strobe signal dWDQS2 may be different. For example, each of the repeaters 211a to 211e may be implemented with at least one buffer or at least one inverter.

The receiver 212a may sample the first data signal DQ1 received through the first data pin D\_P1 based on the toggle timing of the first internal write data strobe signal dWDQS1 and output the first data DATA1. The receiver 212b may sample the second data signal DQ2 received through the second data pin D\_P2 based on the toggle timing of the first internal write data strobe signal dWDQS1 and output the second data DATA2. In some example embodiments, in order for the receivers 212a and 212b to sample the data signals DQ1 and DQ2 at the same toggle timing (i.e., in order for the first internal write data strobe signal dWDQS1 to reach the same timing with the receivers 212a and 212b), the receivers 212a and 212b may be disposed at the same distance from the repeater 211d. In some example embodiments, in order for the receivers 212a and 212b to sample the data signals DQ1 and DQ2 at the same toggle timing, the length of the third signal line SL3 for transmitting the first internal write data strobe signal dWDQS1 from the repeater 211d to the receiver 212a and the length of the fourth signal line SL4 for transmitting the first internal write data strobe signal dWDQS1 from the repeater 211d to the receiver 212b may be the same.

The receiver 212a may receive the first data signal DQ1 from the first data pin D\_P1 through the fifth signal line SL5, and the receiver 212b may receive the second data signal DQ2 from the second data pin D\_P2 through the sixth signal line SL6. In some example embodiments, in order for the data signals DQ1 and DQ2 to be transmitted from the first and second data pins D\_P1 and D\_P2 to the receivers 212a and 212b at the same timing, the length of the fifth signal line SL5 and the length of the sixth signal line SL6 may be the same.

The receiver 213a may sample the third data signal DQ3 received through the third data pin D\_P3 based on the toggle timing of the second internal write data strobe signal dWDQS2 and output the third data DATA3. The receiver 213b may sample the fourth data signal DQ4 received through the fourth data pin D\_P4 based on the toggle timing of the second internal write data strobe signal dWDQS2 and output the fourth data DATA4. In some example embodiments, in order for the receivers 213a and 213b to sample the data signals DQ3 and DQ4 at the same toggle timing (e.g., in order for the second internal write data strobe signal dWDQS2 to reach the same timing with the receivers 213a and 213b), the receivers 213a and 213b may be arranged to

have the same distance from the repeater 211e. As an example, the length of the seventh signal line SL7 for transmitting the second internal write data strobe signal dWDQS2 from the repeater 211e to the receiver 213a and the length of the eighth signal line SL8 for transmitting the second internal write data strobe signal dWDQS2 from the repeater 211e to the receiver 213b may be the same.

The receiver 213a may receive the third data signal DQ3 from the third data pin D\_P3 through the ninth signal line SL9, and the receiver 213b may receive the fourth data signal DQ4 from the fourth data pin D\_P4 through the tenth signal line SL10. In an example embodiment, in order for the data signals DQ3 and DQ4 to be transmitted from the third and fourth data pins D\_P3 and D\_P4 to the receivers 213a and 213b at the same timing, the length of the ninth signal line SL9 and the length of the tenth signal line SL10 may be the same.

When the memory device 200 is configured as described above, the internal write data strobe signal may be trans- 20 mitted to each of the receivers corresponding to one pin group at the same time. Accordingly, the sampling timing skew for data signals received through one pin group can be minimized. For example, the sampling timing skew may be compensated by adding dummy loads such as regulating 25 length and/or resistance of signal lines.

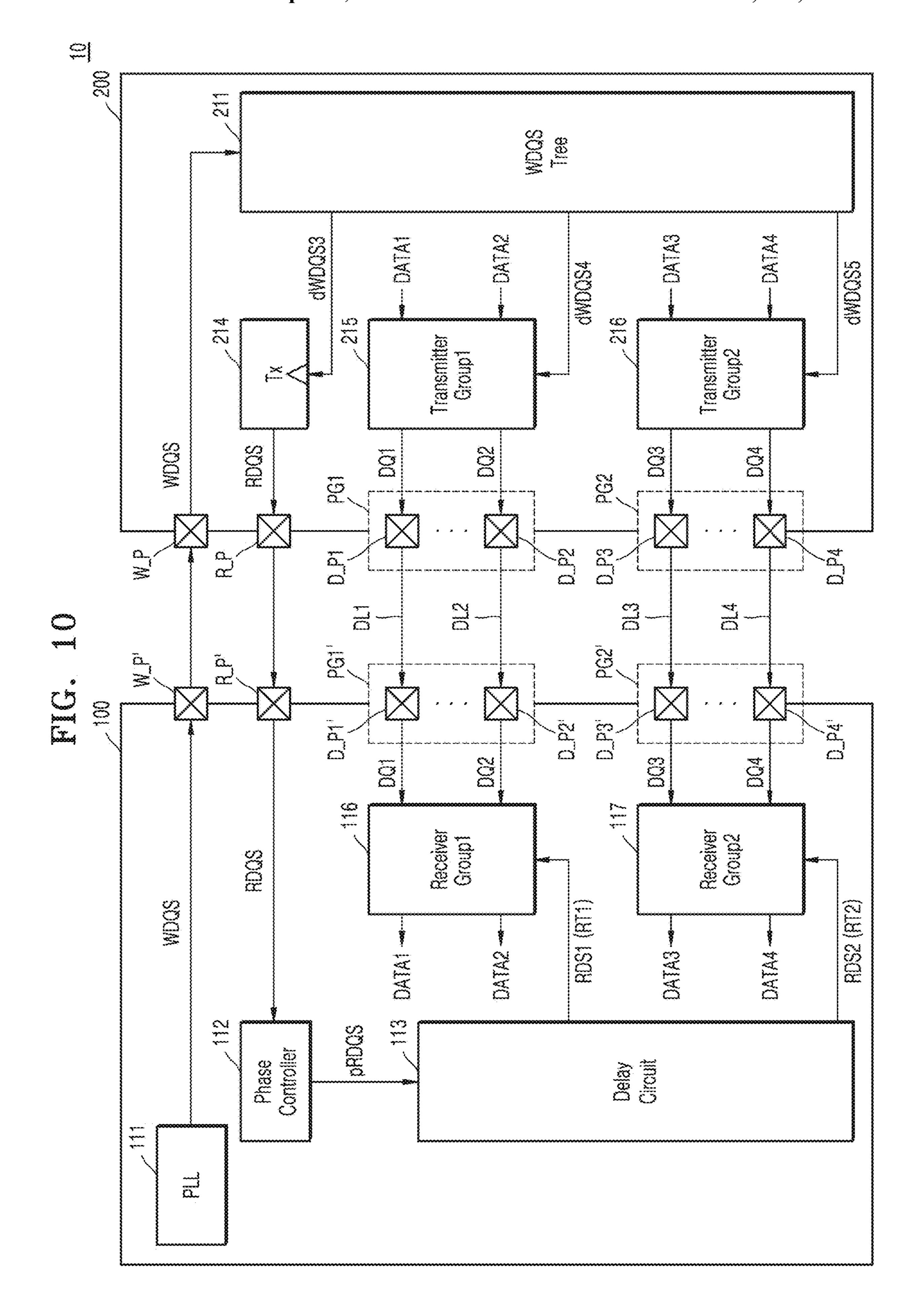

FIG. 10 is a block diagram schematically illustrating the memory system of FIG. 3. For convenience of explanation, configurations of the memory system 10 for performing a read operation according to the read training result (e.g., first 30 and second receiving timing RT1 and RT2) described with reference to FIG. 3 are described, but the example embodiment is not limited thereto.

Referring to FIG. 10, the memory controller 100 may R\_P', a first pin group PG1', and a second pin group PG2'. The write data strobe pin W\_P', the read data strobe pin R\_P', the first pin group PG1', and the second pin group PG2' may correspond to the write data strobe pin W\_P, the read data strobe pin R\_P, the first pin group PG1, and the second 40 pin group PG2 of the memory device 200.

The memory device 200 may include a WDQS tree 211, a transmitter 214, a first transmitter group 215, and a second transmitter group 216. For example, WDQS tree 211, a transmitter 214, a first transmitter group 215, and a second 45 transmitter group 216 may be included in the host interface circuit 210 of FIG. 1. The WDQS tree 211 may transmit to the transmitter **214** a third internal write data strobe signal dWDQS3 toggling based on the write data strobe signal WDQS received through the write data strobe pin W\_P. The 50 WDQS tree 211 may transmit the fourth internal write data strobe signal dWDQS4 toggling based on the write data strobe signal WDQS to the first transmitter group 215, and transmit the toggled fifth internal write data strobe signal dWDQS5 to the second transmitter group 216. For example, 55 the toggle timing of the fourth internal write data strobe signal dWDQS4 may be the same as the toggle timing of the first internal write data strobe signal dWDQS1 of FIG. 7, and the toggle timing of the fifth internal write data strobe signal dWDQS5 may be the same as the second internal write data 60 strobe signal dWDQS2 of FIG. 7. In some example embodiments, the WDQS tree 211 may include a plurality of repeaters, and may transmit the third to fifth internal write data strobe signals dWDQS3 to dWDQS5 through the repeaters.

The transmitter 214 may transmit the read data strobe signal RDQS to the memory controller 100 through the read

**18**

data strobe pin R\_P based on the toggle timing of the third internal write data strobe signal dWDQS3.

In some example embodiments, the third to fifth internal write data strobe signals dWDQS3 to dWDQS5 may be signals generated by delaying the write data strobe signal WDQS through the WDQS tree 211. In this case, toggle timing of the read data strobe signal RDQS generated based on the third internal write data strobe signal dWDQS3 and the fourth internal write data strobe signal dWDQS4 may be different from each other, and toggle timing of the read data strobe signal RDQS and the fifth internal write data strobe signal dWDQS5 may be different from each other. Accordingly, the toggle timing skew may be generated by the WDQS tree 211. The receiving timing determined through 15 training in the memory controller 100 may compensate for the toggle timing skew by the WDQS tree 211. Accordingly, a skew between the read data strobe signal RDQS and the fourth internal write data strobe signal dWDQS4 may be compensated by the first receiving timing RT1, and a skew between the read data strobe signal RDQS and the fifth internal write data strobe signal dWDQS5 may be compensated by the second receiving timing RT2.

The first transmitter group 215 may transmit data signals including data to the memory controller 100 through the first pin group PG1 based on the toggle timing of the fourth internal write data strobe signal dWDQS4. For example, the first transmitter group 215 may transmit the first data signal DQ1 including the first data DATA1 to the memory controller 100 through the first data pin D\_P1 based on the toggle timing of the fourth internal write data strobe signal dWDQS4. The first transmitter group 215 may transmit the second data signal DQ2 including the second data DATA2 to the memory controller 100 through the second data pin D\_P2 based on the toggle timing of the fourth internal write include a write data strobe pin W\_P', a read data strobe pin 35 data strobe signal dWDQS4. Accordingly, the first transmitter group 215 may transmit each of the data signals to the memory controller 100 at the same time.

> The second transmitter group 216 may transmit data signals including data to the memory controller 100 through the second pin group PG2 based on the toggle timing of the fifth internal write data strobe signal dWDQS5. For example, the second transmitter group 216 may transmit the third data signal DQ3 including the third data DATA3 to the memory controller 100 through the third data pin D\_P3 based on the toggle timing of the fifth internal write data strobe signal dWDQS5. The second transmitter group 216 may transmit the fourth data signal DQ4 including the fourth data DATA4 to the memory controller 100 through the fourth data pin D\_P4 based on the toggle timing of the fifth internal write data strobe signal dWDQS5. Accordingly, the second transmitter group 216 may transmit each of the data signals to the memory controller 100 at the same time.

> In this way, when each of the data signals is outputted at the same timing through one pin group, the data skew between the output data signals can be minimized.

As described with reference to FIG. 7, the lengths of signal lines connecting the first pin group PG1' and the first pin group PG1 may be the same, and the lengths of signal lines connecting the second pin group PG2' and the second pin group PG2 may be the same. As described above, since data skew between data signals outputted through one pin group can be minimized, when the lengths of signal lines through which data signals are transmitted are the same, data skew may be kept minimized until data signals are trans-65 mitted to the memory controller 100. Accordingly, each of the data signals transmitted from the first transmitter group 215 may be inputted to the memory controller 100 at the

same time, and each of the data signals transmitted from the second transmitter group 216 may be inputted to the memory controller 100 at the same time.

The memory controller 100 may include a phase locked loop 111, a phase controller 112, a delay circuit 113, a first 5 receiver group 116, and a second receiver group 117. For example, the phase locked loop 111, the phase controller 112, the delay circuit 113, the first receiver group 116, and the second receiver group 117 may be included in the host interface circuit 110 of FIG. 1.

The phase locked loop 111 may generate a write data strobe signal WDQS that toggles with a predetermined phase. The write data strobe signal WDQS may be transmitted to the memory device 200 through the write data strobe pin W\_P'.

The phase controller 112 may receive the read data strobe signal RDQS transmitted from the memory device 200 through the read data strobe pin R\_P'. The phase controller 112 may generate a read data strobe signal pRDQS whose phase is adjusted by adjusting a phase of the read data strobe 20 signal RDQS. For example, the phase controller 112 may adjust the phase of the read data strobe signal RDQS so that a phase difference between the read data strobe signal RDQS and the phase adjusted read data strobe signal pRDQS is 90 degrees.

The delay circuit 113 may delay the read data strobe signal pRDQS whose phase is adjusted according to the read training result. The delay circuit 113 delays the read data strobe signal pRDQS whose phase is adjusted according to the first receiving timing RT1 corresponding to the first pin 30 group PG1 to generate the first read delay signal RDS1. The delay circuit 113 delays the read data strobe signal pRDQS whose phase is adjusted according to the second receiving timing RT2 corresponding to the second pin group PG2 to generate the second read delay signal RDS2. The first read 35 delay signal RDS1 may be provided to the first receiver group 116, and the second read delay signal RDS2 may be provided to the second receiver group 117. In this case, the first read delay signal RDS1 may have a toggle timing corresponding to the first receiving timing RT1, and the 40 second read delay signal RDS2 may have a toggle timing corresponding to the second receiving timing RT2.

The first receiver group 116 may obtain data by sampling each of the data signals received through the first pin group PG1' based on the toggle timing of the first read delay signal 45 RDS1. For example, the first receiver group 116 may obtain the first data DATA1 by sampling the first data signal DQ1 based on the toggle timing of the first read delay signal RDS1. The first receiver group 116 may obtain the second data DATA2 by sampling the second data signal DQ2 based 50 on the toggle timing of the first read delay signal RDS1. Accordingly, the first receiver group 116 may sample each of the data signals according to the same receiving timing (e.g., the first receiving timing RT1).

The second receiver group 117 may obtain data by sampling each of the data signals received through the second pin group PG2' based on the toggle timing of the second read delay signal RDS2. For example, the second receiver group 117 may obtain the third data DATA3 by sampling the third data signal DQ3 based on the toggle 60 timing of the second read delay signal RDS2. The second receiver group 117 may obtain the fourth data DATA4 by sampling the fourth data signal DQ4 based on the toggle timing of the second read delay signal RDS2. Accordingly, the second receiver group 117 may sample each of the data 65 signals according to the same receiving timing (e.g., the second receiving timing RT2).

**20**

As described above, in relation to the memory system 10 according to some example embodiments of inventive concepts, the memory device 200 may transmit each of the data signals to the memory controller 100 through one pin group at the same time. The memory controller 100 may sample each of the data signals received through one pin group at the same time. Accordingly, even if the read training is performed for each pin group, a data bit error rate of data signals transmitted from the memory device 200 to the memory controller 100 in the read operation may be optimized.

FIG. 11 is a timing diagram illustrating an example in which the memory device of FIG. 10 transmits data signals. Referring to FIGS. 10 and 11, a write data strobe signal 15 WDQS received through a write data strobe pin W\_P may have a toggle timing at a first time point t1. The third internal write data strobe signal dWDQS3 transmitted to the transmitter 214 by the WDQS tree 211 and the read data strobe signal RDQS may have a toggle timing at the second time point t2. The fourth internal write data strobe signal dWDQS4 transmitted to the first transmitter group 215 may have a toggle timing at a third time point t3, and the fifth internal write data strobe signal dWDQS5 transmitted to the second transmitter group 216 by the WDQS tree 211 may 25 have a toggle timing at a fourth time point t4. Accordingly, a first skew SK1 between the fourth internal write data strobe signal dWDQS4 and the read data strobe signal RDQS may be generated, and a second skew SK2 between the fifth internal write data strobe signal dWDQS5 and the read data strobe signal RDQS may be generated.

The first data signal DQ1 including the first data DATA1 and the second data signal DQ2 including the second data DATA2 may be transmitted to the memory controller 100 at a toggle timing of the fourth internal write data strobe signal dWDQS4. Accordingly, the first data DATA1 and the second data DATA2 may be transmitted to the memory controller 100 at the same timing. The first data signal DQ1 and the second data signal DQ2 transmitted to the first receiver group 116 may be sampled based on a first receiving timing RT1 for compensating for the first skew SK1. In this case, a sampling margin for the first data DATA1 and the second data DATA2 is secured, so that the data bit error rate can be optimized.

The third data signal DQ3 including the third data DATA3 and the fourth data signal DQ4 including the fourth data DATA4 may be transmitted to the memory controller 100 at a toggle timing of the fifth internal write data strobe signal dWDQS5. Accordingly, the third data DATA3 and the fourth data DATA4 may be transmitted to the memory controller 100 at the same timing. The third data signal DQ3 and the fourth data signal DQ4 transmitted to the second receiver group 117 may be sampled based on the second receiving timing RT2 for compensating for the second skew SK2. In this case, a sampling margin for the third data DATA3 and the fourth data DATA4 is secured, so that the data bit error rate can be optimized.

As described above, data skew between data signals outputted from one pin group of the memory device 200 may be minimized. For example, the first data DATA1 and the second data DATA2 are transmitted at the same time (e.g. the fourth time point t4). Hereinafter, a detailed configuration of a memory device that minimizes data skew between data signals outputted from one pin group will be described with reference to FIG. 12.

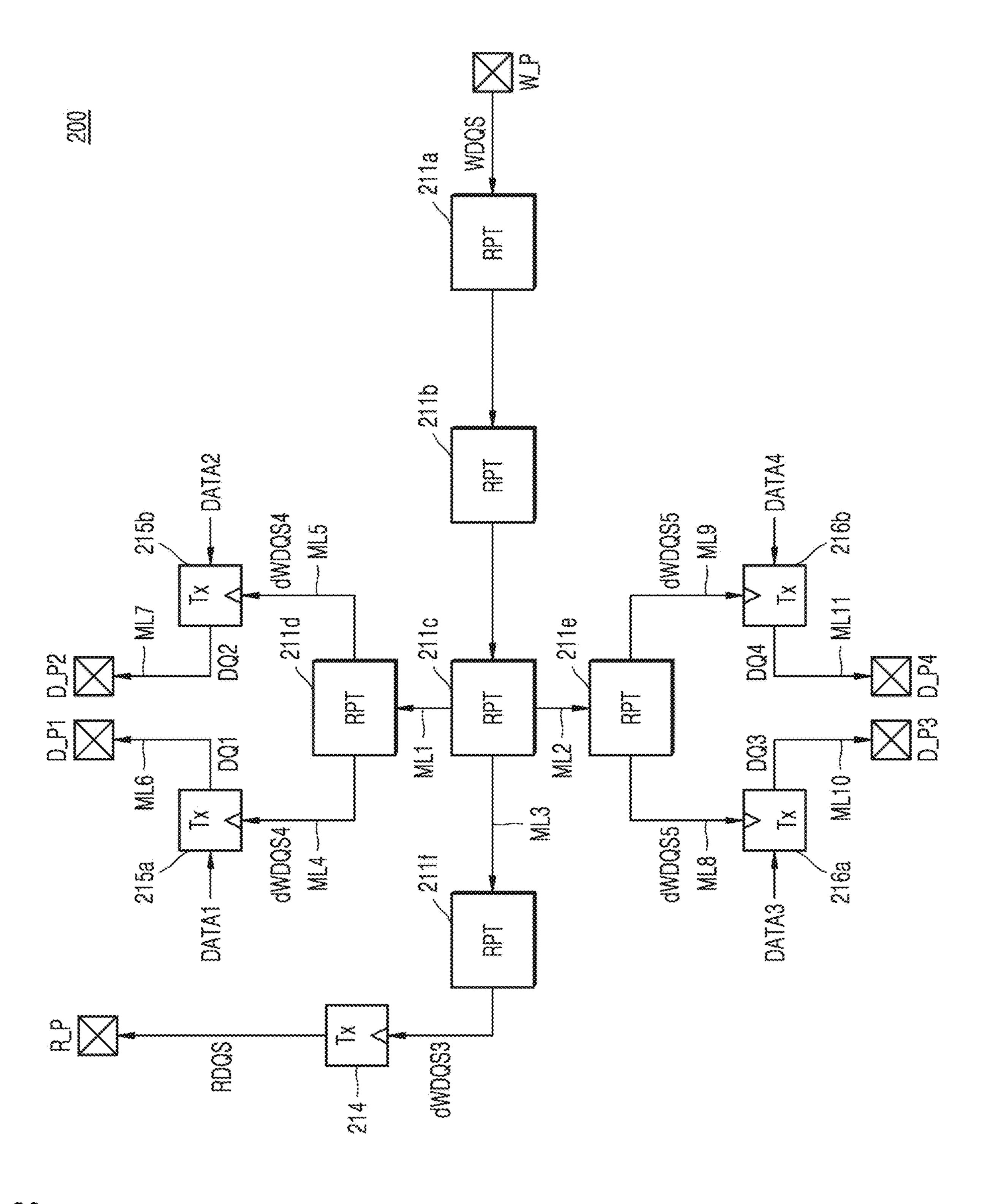

FIG. 12 is a diagram illustrating an example configuration of the memory device of FIG. 10. Referring to FIGS. 10 and 12, the memory device 200 may include a plurality of

repeaters 211a to 211f and a plurality of transmitters 214, 215a, 215b, 216a and 216b. The repeaters 211a to 211f may be included in the WDQS tree 211. The transmitters 215a and 215b may be included in the first transmitter group 215, and the transmitters 216a and 216b may be included in the 5 second transmitter group 216.

The write data strobe signal WDQS received through the write data strobe pin W\_P may be transmitted to the transmitters 215a and 215b, respectively, as the fourth internal write data strobe signal dWDQS4 through the repeaters 10 211a, 211b, 211c, and 211d on the first path. The write data strobe signal WDQS may be transmitted to the transmitters **216***a* and **216***b* as a fifth internal write data strobe signal dWDQS5 through the repeaters 211a, 211b, 211c, and 211e on the second path. The write data strobe signal WDQS may 15 be transmitted to the transmitter **214** as a third internal write data strobe signal dWDQS3 through the repeaters 211a, 211b, 211c, and 211f on the third path. For example, when the length of the first signal line ML1 connecting the repeater 211c and the repeater 211d on the first path, the 20 length of the second signal line ML2 connecting the repeater 211c and the repeater 211e on the second path, and the length of the third signal line ML3 connecting the repeater 211c and the repeater 211f on the third path are different from each other, as described with reference to FIG. 11, toggle timing 25 of the third to fifth internal write data strobe signals dWDQS3 to dWDQS5 may be different from each other.