#### US011269396B2

## (12) United States Patent

### Ananthakrishnan et al.

# (54) PER-CORE OPERATING VOLTAGE AND/OR OPERATING FREQUENCY DETERMINATION BASED ON EFFECTIVE CORE UTILIZATION

(71) Applicant: **Intel Corporation**, Santa Clara, CA (US)

(72) Inventors: Avinash Ananthakrishnan, Portland,

OR (US); Stephen Gunther, Beaverton, OR (US); Amr Muhammad Lotfy El-Sayed, Hillsboro, OR (US); Akshay Parnami, Portland, OR (US)

(73) Assignee: Intel Corporation, Santa Clara, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 87 days.

(21) Appl. No.: 16/147,285

(22) Filed: Sep. 28, 2018

#### (65) Prior Publication Data

US 2019/0041962 A1 Feb. 7, 2019

(51) Int. Cl.

G06F 1/3234 (2019.01)

G06F 1/3296 (2019.01)

G06F 1/3228 (2019.01)

G06F 1/324 (2019.01)

(52) **U.S. Cl.** CPC ...... *G06F 1/3243* (2013.01); *G06F 1/324* (2013.01); *G06F 1/3228* (2013.01); *G06F*

(58) Field of Classification Search

CPC ..... G06F 1/3243; G06F 1/3228; G06F 1/324; G06F 1/3296

*1/3296* (2013.01)

See application file for complete search history.

## (10) Patent No.: US 11,269,396 B2

(45) **Date of Patent:** Mar. 8, 2022

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,711,447<br>8,943,334 |     | 3/2004<br>1/2015 | Saeed<br>Kumar et al. |  |  |

|------------------------|-----|------------------|-----------------------|--|--|

| 2008/0148027           |     |                  | Fenger et al.         |  |  |

| 2008/0162868           | A1* |                  | Glew G06F 12/1027     |  |  |

|                        |     |                  | 711/203               |  |  |

| 2009/0089792           | A1* | 4/2009           | Johnson               |  |  |

|                        |     |                  | 718/105               |  |  |

| 2010/0332856           | A1  | 12/2010          | Song                  |  |  |

| (Continued)            |     |                  |                       |  |  |

#### FOREIGN PATENT DOCUMENTS

WO 2012040052 3/2012

#### OTHER PUBLICATIONS

Intel 64 and IA-32 Architectures Software Developer's Manual, Sep. 2016, Intel Corporation, vol. 3B: System Programming Guide, Part 2. (Year: 2016).\*

(Continued)

Primary Examiner — Jaweed A Abbaszadeh

Assistant Examiner — Hyun Soo Kim

(74) Attorney, Agent, or Firm — Schwabe, Williamson & Wyatt, P.C.

#### (57) ABSTRACT

An apparatus is provided, where the apparatus includes a plurality of processing cores to execute a plurality of processes, a register to store an indicator that is to indicate a preference for either performance or energy efficiency, a first circuitry to determine an effective utilization of a first processing core, based on the indicator, and a second circuitry to select at least one of an operating voltage or an operating frequency of the first processing core, based at least in part on the effective utilization of the first processing core.

### 18 Claims, 11 Drawing Sheets

#### **References Cited** (56)

#### U.S. PATENT DOCUMENTS

| 2011/0113220 A1* | 5/2011  | Morishita G06F 9/3009           |

|------------------|---------|---------------------------------|

| 2011/0202206 41* | 11/2011 | 712/30<br>Wu G06F 1/329         |

| 2011/0283280 A1  | 11/2011 | 718/103                         |

| 2014/0053009 A1* | 2/2014  | Semin G06F 9/30083              |

| 2014/0068284 A1* | 3/2014  | 713/322<br>Bhandaru G06F 1/3296 |

|                  |         | 713/300                         |

| 2015/0355800 A1* | 12/2015 | Cronin                          |

| 2010/00/0122 11% | 2/2010  | 715/835                         |

| 2018/0060123 A1* |         | Weissmann G06F 9/5027           |

| 2018/0120920 A1* | 5/2018  | Iyigun G06F 1/3243              |

| 2018/0129534 A1* |         | Iyigun G06F 9/4881              |

| 2019/0004585 A1* |         | Halverson G06F 1/3206           |

| 2019/0041962 A1  | 2/2019  | Ananthakrishnan et al.          |

#### OTHER PUBLICATIONS

International Search Report and Written Opinion from PCT/US2019/ 039342 notified Oct. 18, 2019, 14 pgs.

<sup>\*</sup> cited by examiner

Mar. 8, 2022

```

<u>600</u>

```

```

hat we want to track

<u>_</u>

discard it and replace it with a new process

== Oldest

oldest_tsc = sorted(LRU_process.values())[-1] #Get the process with the oldest TSC

C0 residency for that thread

process_id_to_remove = [key for key, value in LRU_process.iteritems() If value #Remove the oldest process_id from history to make way for a new process_id

add it to the

delta

= 8 # Let's say we want to keep stats for upto 8 unique process

_remove])

# New process_ID from the OS. Check to see if we want to If (len(LRU_process) < MAX_PROCESS_COYNT):

process_C0_residency[process_id] = C0_residency_

# check to see the process_id that's the oldest

#Add the new process_id's data to our history

<_THREAD_COUNT = 8 # 8 threads for example

thread in range (0, MAXTHREAD_COUNT) :

thread_hwp_req = readlo(IA32_HWP_REQUEST[_thread])</pre>

process_C0_residency.keys():

_C0_residency[process_id] += C0_residency_delta

process_id = thread_hwp_req.Logical_Process_Identifier

c0_residency_current = readIO(C0_RESIDENCY_MSR) #

delete(process_C0_residency[process_id_to_

c0_residency_delta = C0_residency - C0_residency_last C0_residence_last = C0_residency_current

LRU_process[process_id] = current_tsc

delta

thread_C0_residency[_thread] += C0_residency_

process_c0_residency = {}

thread_c0_residency = {}

pkg_C0_residency = { }

else:

process

If (process_id in

MAX_THREAD

Process_count

LRU_process

Else:

```

C0\_residence += C0\_residency\_delta

Mar. 8, 2022

700

For each core

("Performance or energy efficiency bias indicator 120" == Performance):

process\_utilization of a process being executed Effective\_utilization[core] =

Else

Effective\_utilization[core] = Core\_utilization[core\_id]

Fig. 7

r each core:

If ("Performance or energy efficiency bias indicator 120"

Effective\_utilization[core] = package utilization

Elco.

Effective\_utilization[core] = Core\_utilization[core\_

**IIG. 7B**

# PER-CORE OPERATING VOLTAGE AND/OR OPERATING FREQUENCY DETERMINATION BASED ON EFFECTIVE CORE UTILIZATION

#### BACKGROUND

A trend in modern computing is to integrate an increasing number of processing cores, to deliver more throughput performance. As more and more cores get integrated, e.g., to increase overall performance and efficiency, it may be useful and/or possible to run each of the cores on corresponding independent voltage and/frequency domains. Different algorithms have been developed over the years on how to pick a frequency and/or a voltage (e.g., a power state, such as a P-state) for individual cores to operate. These algorithms have looked at various factors, e.g., to select a frequency to run the cores.

A thread in computer science is short for a thread of execution. Threads are a way for a program or process to 20 divide or split itself into two or more simultaneously (or pseudo-simultaneously) running tasks. In an example, workloads of computing devices are threaded, and there may be multiple processes concurrently running on a processing core. A duration for which a process gets scheduled on a core 25 has material impact on performance of the process and/or the core. It may be desirable to develop ways to select voltage and/or frequency (e.g., select a power state, such as a P-state that is in accordance with the ACPI (Advanced Configuration and Power Interface) specification) for a core 30 to operate, e.g., based on the threads being executed on the core.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The material described herein is illustrated by way of example and not by way of limitation in the accompanying figures. For simplicity and clarity of illustration, elements illustrated in the figures are not necessarily drawn to scale. For example, the dimensions of some elements may be 40 exaggerated relative to other elements for clarity. Further, where considered appropriate, reference labels have been repeated among the figures to indicate corresponding or analogous elements. In the figures:

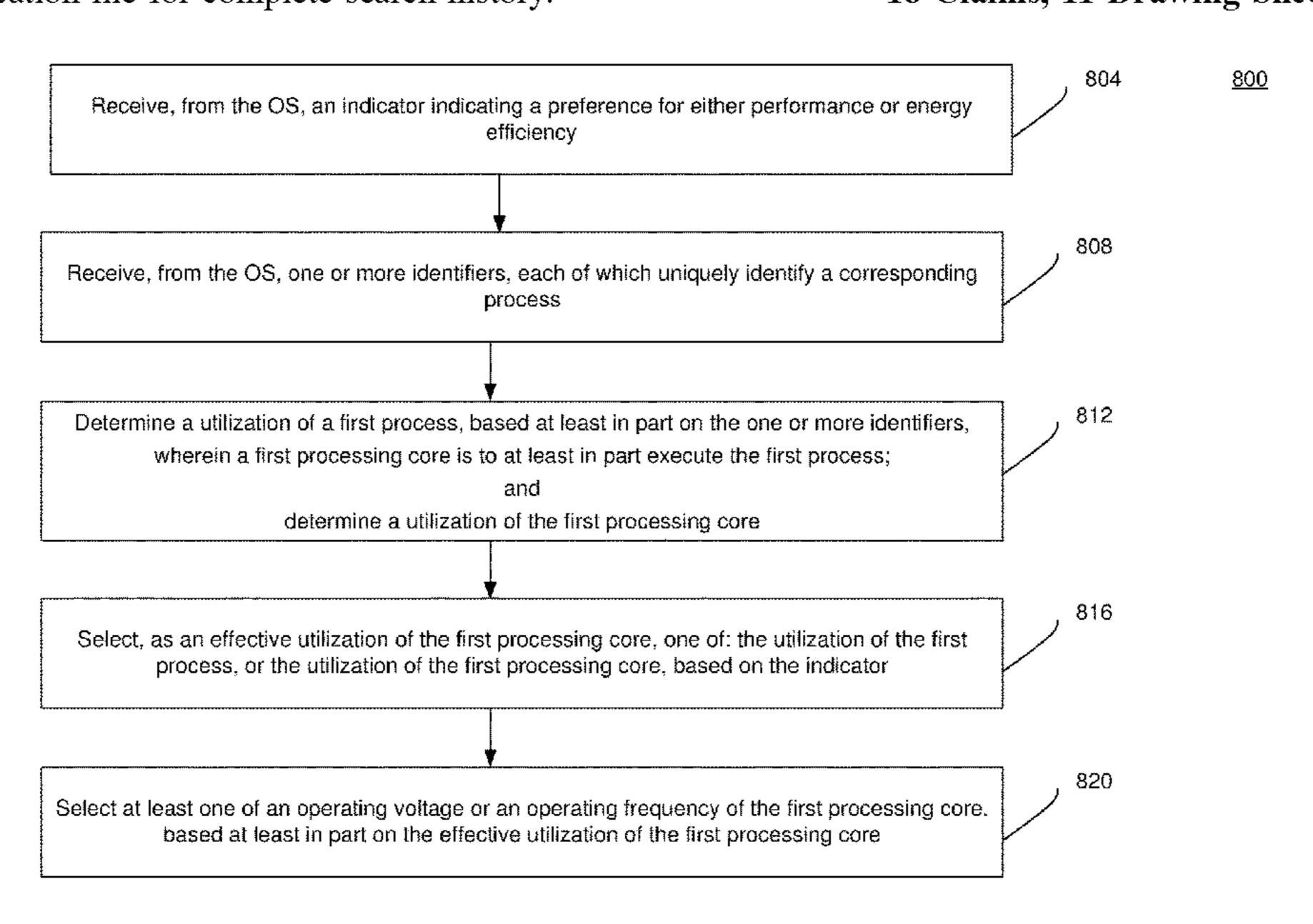

- FIG. 1A schematically illustrates a computing device that 45 determines operating states of processing cores, based on a "performance or energy efficiency bias indicator" and an "effective core utilization", according to some embodiments.

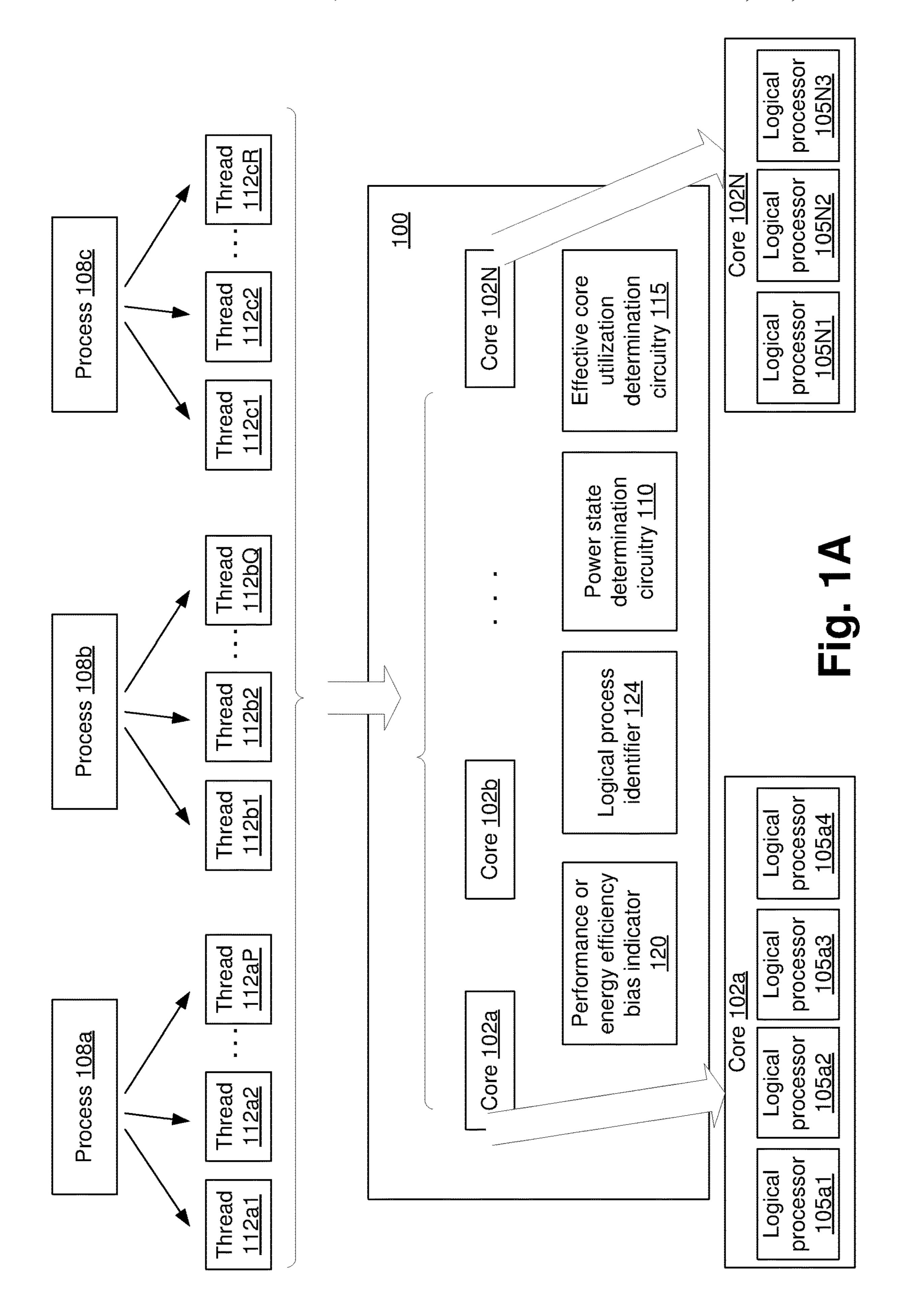

- FIG. 1B illustrates an example system including a power 50 management unit (PMU) that implements a power state determination circuitry and an effective core utilization determination circuitry, according to some embodiments.

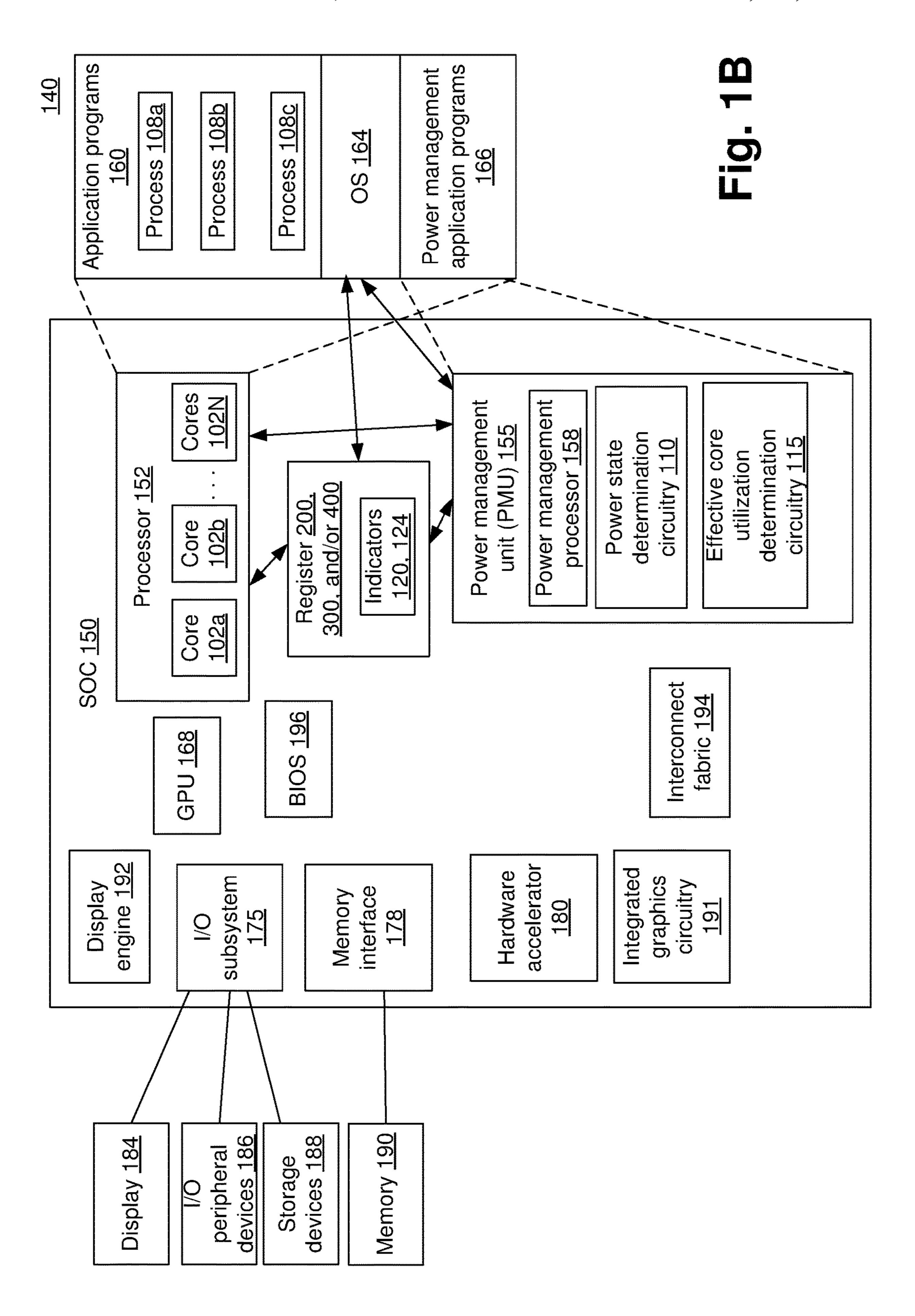

- FIG. 2 illustrates an example register that stores the performance or energy efficiency bias indicator, according to 55 some embodiments.

- FIG. 3 illustrates another example register that stores the performance or energy efficiency bias indicator, according to some embodiments.

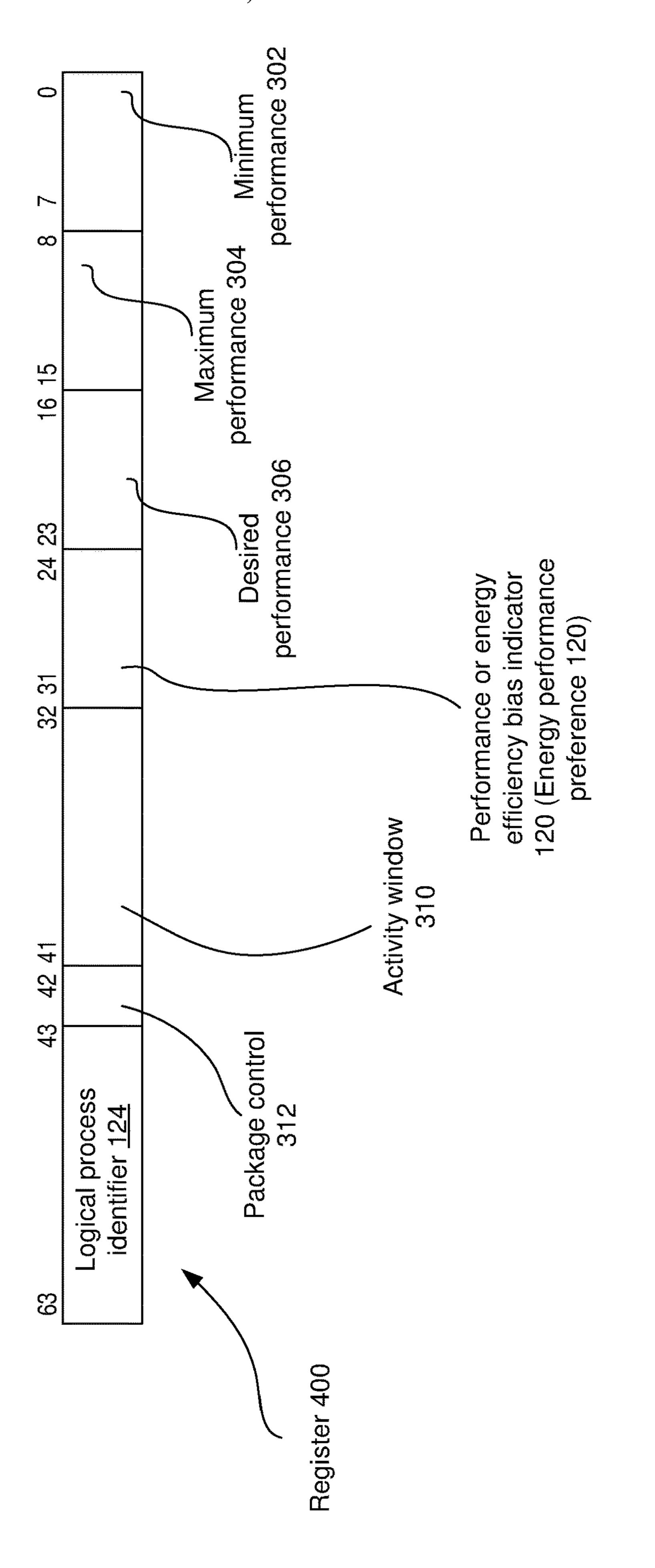

- FIG. 4 illustrates an example register including a logical 60 process identifier, according to some embodiments.

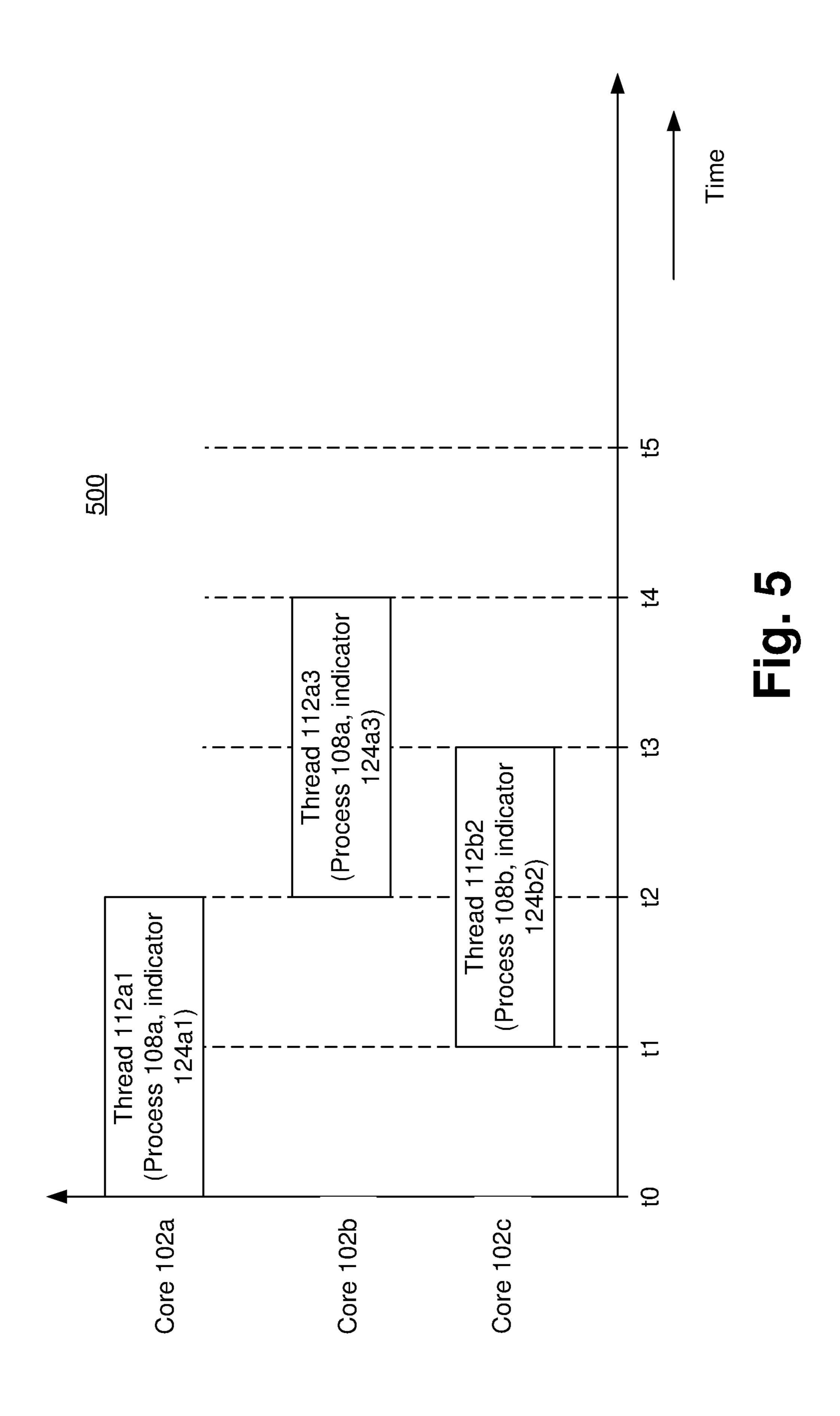

- FIG. 5 illustrates a graph illustrates example processing cores executing various threads, according to some embodiments.

- FIG. 6 illustrates an example pseudo-code for determin- 65 ing a process\_CO\_residency, a thread\_CO\_residency, and a package\_CO\_residency, according to some embodiments.

2

- FIG. 7A illustrates an example pseudo-code for determining an effective core utilization of a core, based on the "Performance or energy efficiency bias indicator" of FIG. 1A, according to some embodiments.

- FIG. 7B illustrates another example pseudo-code for determining an effective core utilization of a core, based on the "Performance or energy efficiency bias indicator" of FIG. 1A, according to some embodiments.

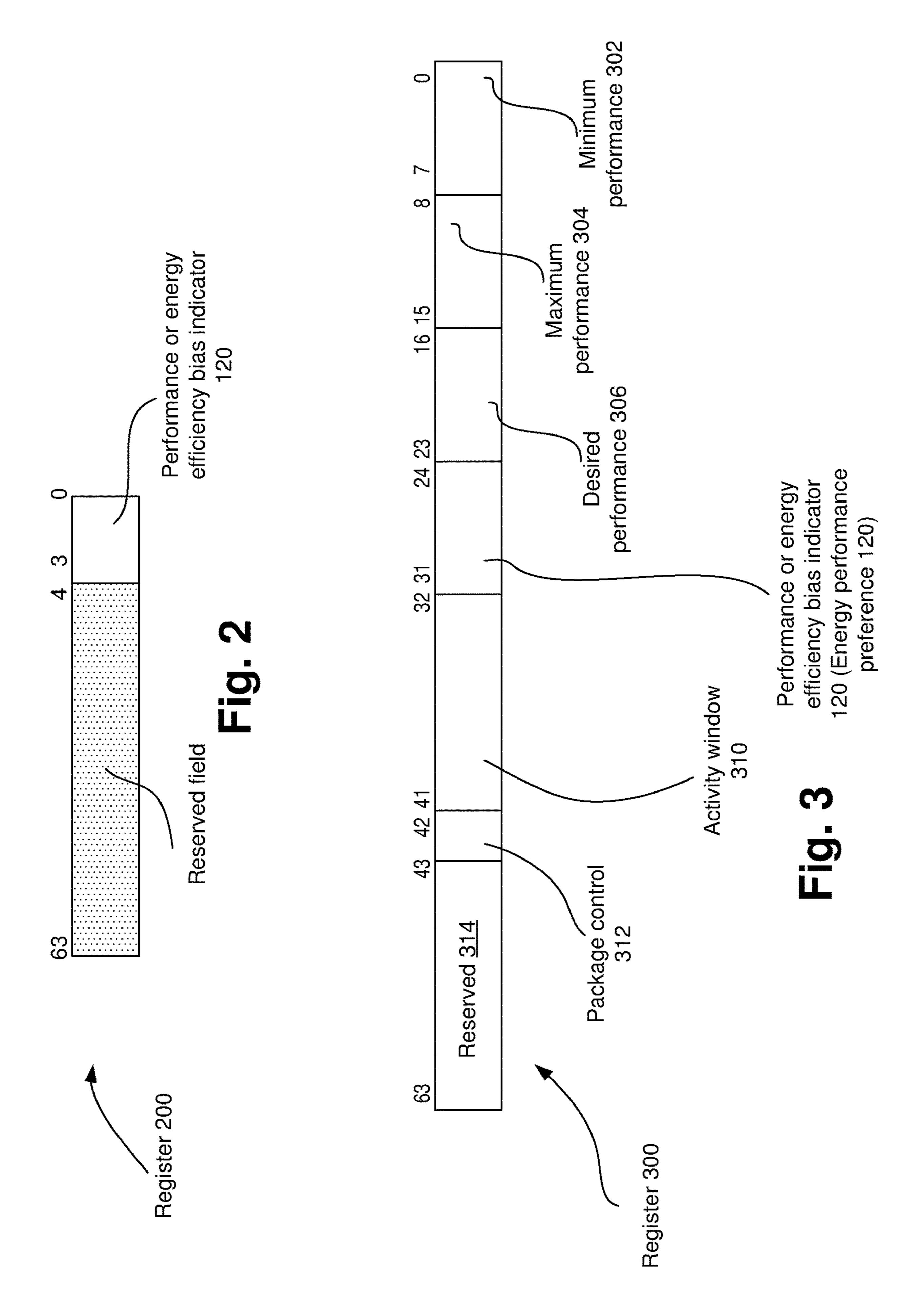

- FIG. 8 illustrates a flowchart depicting a method for assigning operating voltage and/or operating frequency to individual cores of the system of FIG. 1A, according to some embodiments.

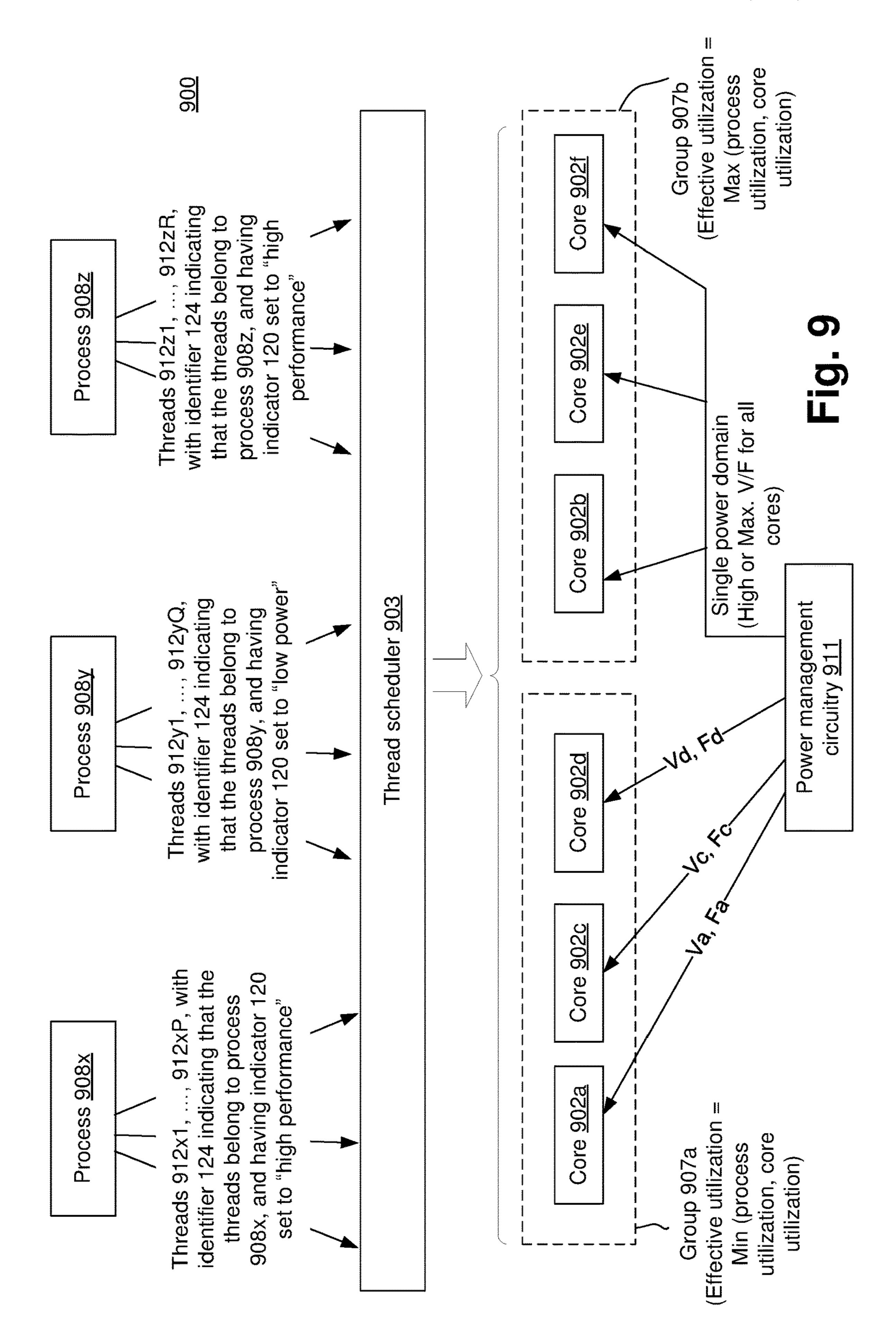

- FIG. 9 schematically illustrates a computing device that determines operating states of processing cores, based on an effective utilization of the processing cores, according to some embodiments.

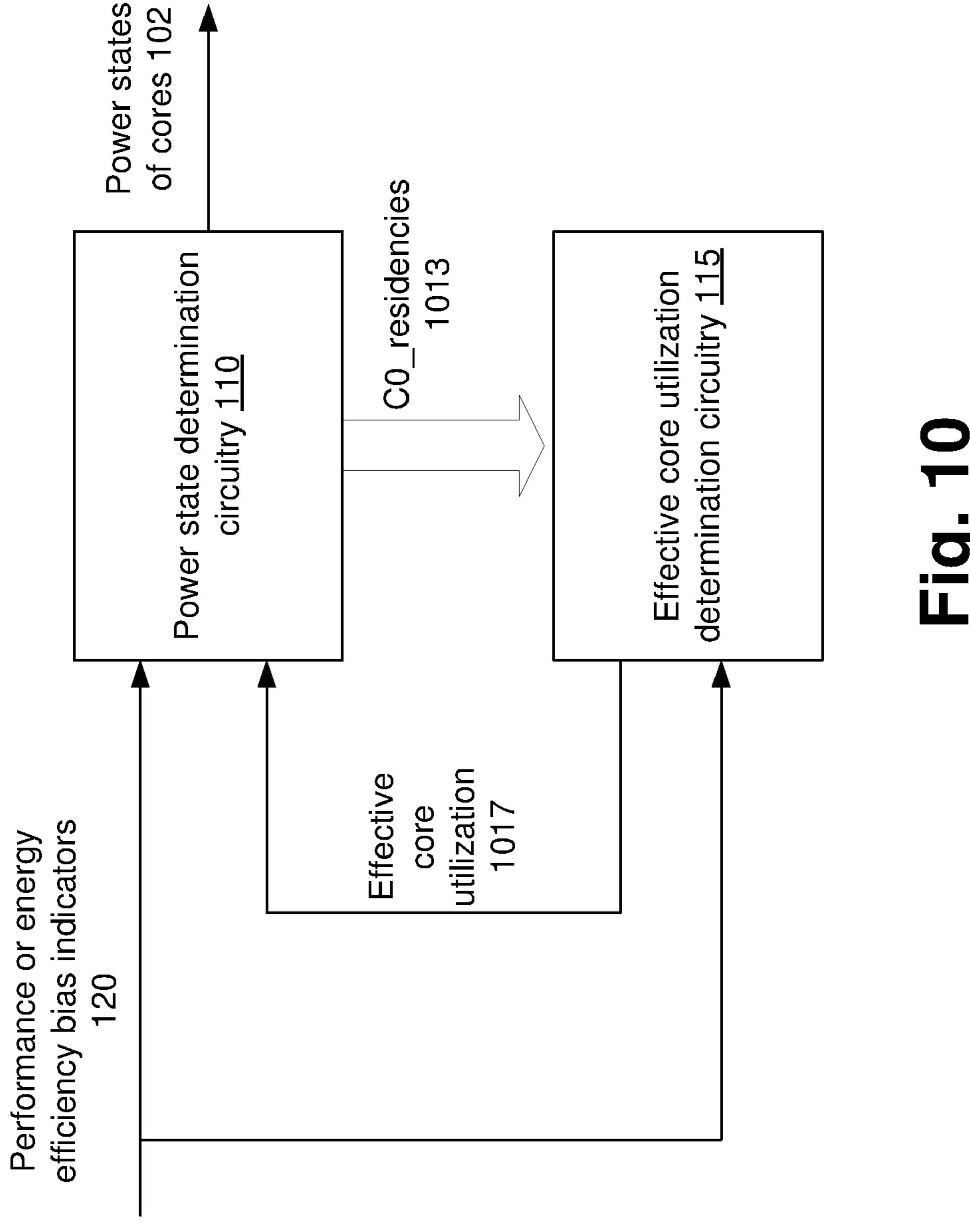

- FIG. 10 illustrates a power state determination circuitry and an effective core utilization determination circuitry, according to some embodiments.

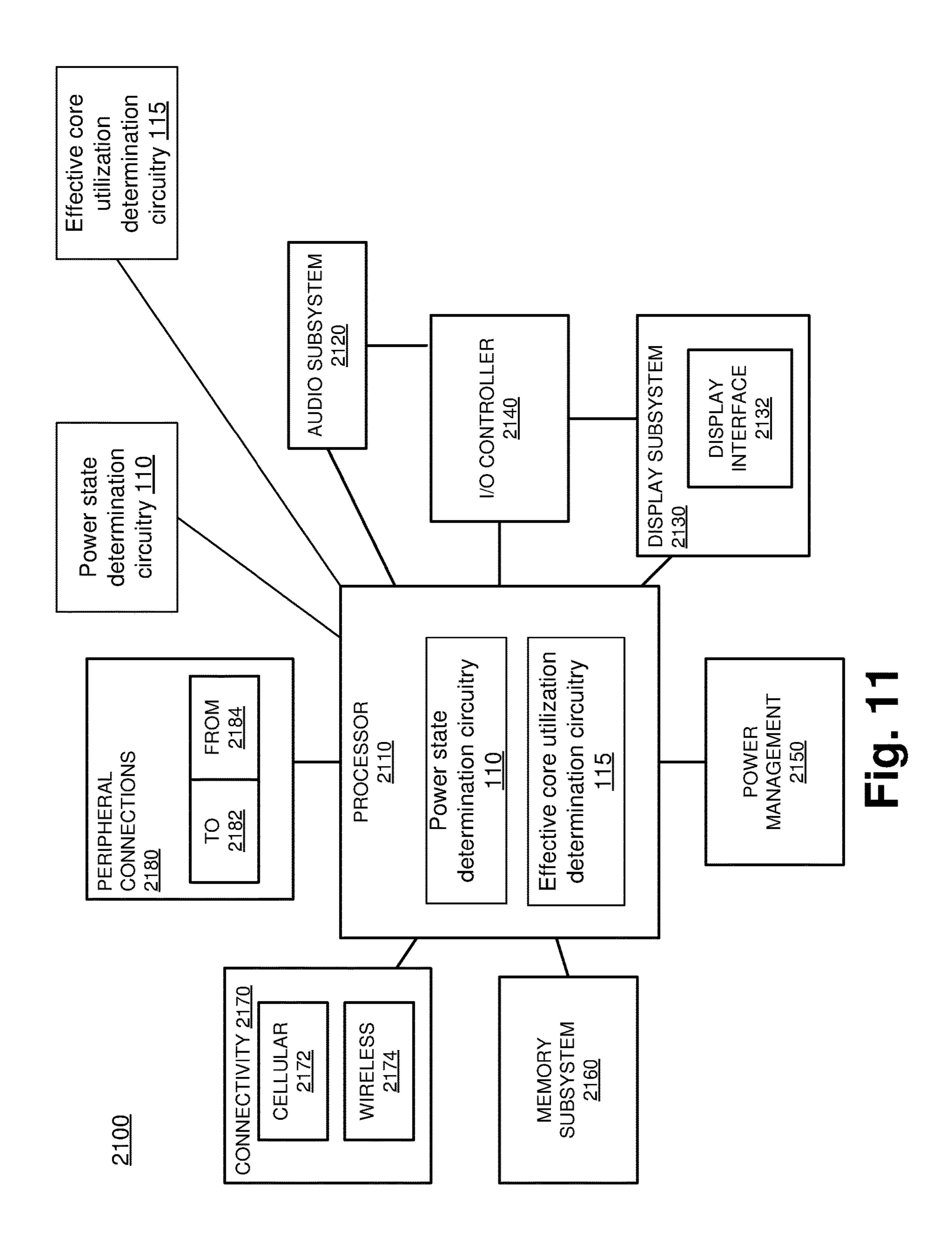

- FIG. 11 illustrates a computer system, a computing device or a SoC (System-on-Chip), where operating states of processing cores are determined based on a "performance or energy efficiency bias indicator" and an "effective core utilization," according to some embodiments.

#### DETAILED DESCRIPTION

In a computing device, power state selection circuitries usually take into account a utilization of a processing core (e.g., residence of the processing core at active state or C0 state, also referred to as core utilization), and implement a controller (e.g., a proportional controller, a Proportional-Integral-Derivative (PID) controller, etc.) that selects a power state (e.g., a frequency and/or a voltage, where P-state is an example of a power state) as a function of the core utilization. For example, the higher the core utilization, the more work that needs to be done by the core, and hence higher the selection of the operating frequency of the core. For example, the PID controller takes historical core utilization into account (e.g., the integral component of PID), and also modulate the frequency recommendation based on the rate of change of the core utilization (e.g., derivative component of PID).

In modern computing devices, a process may spawn or generate multiple logical processes or threads, and multiple threads may be executed in parallel in multiple processing cores. Thread migration refers to migration of a thread (or a process) from one processing core to another during execution. A process utilization refers to a utilization or active C0 residency time of a process, e.g., over the multiple threads the process generates.

With thread migration, as the workload moves from core to core, the core utilization of a specific core may be less than the process utilization. Merely as a simple example, a process may spend 50% time on a first core and 50% time on a second core—in such an example, the core utilization of each of the first and second cores is 50%, but the process utilization is 100%. In a conventional P-state selection that is done at a per core granularity based on core utilization, for this example, the P-state selection is done assuming merely a 50% core utilization, thereby leading to a selection of a relatively lower value of operational frequency for each of the processing cores.

However, if the process were to run solely on the first core, then the core utilization would have been 100%—this would have resulted in a selection of a relatively high value of operational frequency for the first core.

Thus, power state selection based solely on core utilization may not take into account migration of threads over multiple cores, may result in sub-optimal performance.

In some embodiments and as will be discussed in further details herein, an "effective core utilization" (e.g., an "effective utilization" of a processing core) is taken into account while selecting a power state (such as a P-state having a specific voltage and/or frequency) for a processing core. The effective core utilization can be either the actual core utilization, or the process utilization.

It is to be noted that some examples and embodiments discussed in this disclosure refers specifically to P-state, where a P-state may be in accordance with the ACPI (Advanced Configuration and Power Interface) standard. However, the scope of this disclosure is not limited by 15 merely P-state determination in accordance with the ACPI standard. For example, the principles of this disclosure may generally be applied to determining operating voltage and/or operating frequency, which may, or may not, be in accordance with P-states. Thus, any reference to P-states are for 20 merely example purposes and for not limiting the scope of this disclosure. Any specific reference to a P-state determination for a core may also generally apply to determination of an operating voltage and/or frequency for the core.

In an example, an indicator associated with a process (or associated with individual threads of a process) may indicate either a preference for higher performance, or a preference for energy savings (e.g., a preference for low power). If the indicator indicates a preference for higher performance, the effective core utilization is equal to the process utilization. 30 However, if the indicator indicates a preference for energy savings, the effective core utilization is equal to the core utilization.

The power state selection algorithm is then executed based on the effective core utilization, e.g., instead of being 35 based on the actual core utilization. Thus, for example, if a process is migrating between two cores and assuming that the indicator indicates a preference for higher performance, the effective core utilization for the process is based on the total or overall utilization of the process over the two cores. 40 This results in a frequency selection that is based on the process utilization, and not on the core utilization. On the other hand, if energy savings is a concern, the frequency selection is based on the core utilization (e.g., as in such a case, the effective core utilization would be equal to the 45 actual core utilization). Thus, the embodiments result in better selection of frequency, thereby resulting in enhanced performance or enhanced energy savings, as desired. Other technical effects will be evident from the various embodiments and figures.

One or more embodiments are described with reference to the enclosed figures. While specific configurations and arrangements are depicted and discussed in detail, it should be understood that this is done for illustrative purposes only. Persons skilled in the relevant art will recognize that other 55 configurations and arrangements are possible without departing from the spirit and scope of the description. It will be apparent to those skilled in the relevant art that techniques and/or arrangements described herein may be employed in a variety of other systems and applications other than what is 60 described in detail herein.

Reference is made in the following detailed description to the accompanying drawings, which form a part hereof and illustrate exemplary embodiments. Further, it is to be understood that other embodiments may be utilized and structural 65 and/or logical changes may be made without departing from the scope of claimed subject matter. It should also be noted 4

that directions and references, for example, up, down, top, bottom, and so on, may be used merely to facilitate the description of features in the drawings. Therefore, the following detailed description is not to be taken in a limiting sense and the scope of claimed subject matter is defined solely by the appended claims and their equivalents.

In the following description, numerous details are set forth. However, it will be apparent to one skilled in the art, that the present invention may be practiced without these specific details. In some instances, well-known methods and devices are shown in block diagram form, rather than in detail, to avoid obscuring the present invention. Reference throughout this specification to "an embodiment" or "one embodiment" or "some embodiments" means that a particular feature, structure, function, or characteristic described in connection with the embodiment is included in at least one embodiment of the invention. Thus, the appearances of the phrase "in an embodiment" or "in one embodiment" or "some embodiments" in various places throughout this specification are not necessarily referring to the same embodiment of the invention. Furthermore, the particular features, structures, functions, or characteristics may be combined in any suitable manner in one or more embodiments. For example, a first embodiment may be combined with a second embodiment anywhere the particular features, structures, functions, or characteristics associated with the two embodiments are not mutually exclusive.

As used in the description and the appended claims, the singular forms "a", "an" and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will also be understood that the term "and/or" as used herein refers to and encompasses any and all possible combinations of one or more of the associated listed items.

The terms "coupled" and "connected," along with their derivatives, may be used herein to describe functional or structural relationships between components. It should be understood that these terms are not intended as synonyms for each other. Rather, in particular embodiments, "connected" may be used to indicate that two or more elements are in direct physical, optical, or electrical contact with each other. "Coupled" may be used to indicated that two or more elements are in either direct or indirect (with other intervening elements between them) physical or electrical contact with each other, and/or that the two or more elements co-operate or interact with each other (e.g., as in a cause an effect relationship).

The terms "substantially," "close," "approximately," "near," and "about," generally refer to being within +/-10% of a target value. For example, unless otherwise specified in the explicit context of their use, the terms "substantially equal," "about equal" and "approximately equal" mean that there is no more than incidental variation between among things so described. In the art, such variation is typically no more than +/-10% of a predetermined target value.

The term "scaling" generally refers to converting a design (schematic and layout) from one process technology to another process technology and subsequently being reduced in layout area. The term "scaling" generally also refers to downsizing layout and devices within the same technology node. The term "scaling" may also refer to adjusting (e.g., slowing down or speeding up—i.e. scaling down, or scaling up respectively) of a signal frequency relative to another parameter, for example, power supply level.

As used throughout this description, and in the claims, a list of items joined by the term "at least one of" or "one or more of" can mean any combination of the listed terms. For

example, the phrase "at least one of A, B or C" can mean A; B; C; A and B; A and C; B and C; or A, B and C.

The terms "left," "right," "front," "back," "top," "bottom," "over," "under," and the like in the description and in the claims, if any, are used for descriptive purposes and not 5 necessarily for describing permanent relative positions. For example, the terms "over," "under," "front side," "back side," "top," "bottom," "over," "under," and "on" as used herein refer to a relative position of one component, structure, or material with respect to other referenced compo- 10 nents, structures or materials within a device, where such physical relationships are noteworthy. These terms are employed herein for descriptive purposes only and predominantly within the context of a device z-axis and therefore may be relative to an orientation of a device. Hence, a first 15 material "over" a second material in the context of a figure provided herein may also be "under" the second material if the device is oriented upside-down relative to the context of the figure provided. In the context of materials, one material disposed over or under another may be directly in contact or 20 may have one or more intervening materials. Moreover, one material disposed between two materials may be directly in contact with the two layers or may have one or more intervening layers. In contrast, a first material "on" a second material is in direct contact with that second material. 25 Similar distinctions are to be made in the context of component assemblies.

The term "between" may be employed in the context of the z-axis, x-axis or y-axis of a device. A material that is between two other materials may be in contact with one or 30 both of those materials, or it may be separated from both of the other two materials by one or more intervening materials. A material "between" two other materials may therefore be in contact with either of the other two materials, or it may be coupled to the other two materials through an intervening 35 material. A device that is between two other devices may be directly connected to one or both of those devices, or it may be separated from both of the other two devices by one or more intervening devices.

It is pointed out that those elements of the figures having 40 the same reference numbers (or names) as the elements of any other figure can operate or function in any manner similar to that described, but are not limited to such.

FIG. 1A schematically illustrates a computing device 100 (also referred to as device 100) that determines operating 45 states of processing cores, based on a "performance or energy efficiency bias indicator 120" (also referred to as indicator 120) and an "effective core utilization" (e.g., as determined by an "Effective core utilization determination circuitry 115"), according to some embodiments. The device 50 100 comprises processing cores (also referred to as cores) 102a, 102b, . . . , 102N. Thus, there may be N number of cores, where N may be an appropriate integer. As will be discussed in further details herein later, the device 100 comprises a logical process identifier 124 and a power state 55 determination circuitry 110.

Elements referred to herein with a common reference label followed by a particular number or alphabet may be collectively referred to by the reference label alone. For example, cores 102a, 102b, . . . , 102N may be collectively 60 and generally referred to as cores 102 in plural, and core 102 in singular.

Illustrated in FIG. 1A are various examples processes 108a, 108b, 108c executed by the cores 102. Although merely three processes 108 are illustrated, any other appropriate number of processes may be executed by the cores 102. Individual process of the processes 108a, 108b, 108c

6

may represent any appropriate process or program (e.g., a Microsoft Word® program) being executed in the device 100.

In an example, individual processes may spawn or generate multiple threads. Threads are a way for a process to divide or split itself into two or more simultaneously (or pseudo-simultaneously) running tasks. For example, the process 108a may spawn threads 112a1, 112a2, . . . , 112aP, e.g., P number of threads, where P is an appropriate integer. The process 108b may spawn threads 112b1, 112b2, . . . , 112bQ, e.g., Q number of threads, where Q is an appropriate integer. The process 108c may spawn threads 112c1, 112c2, . . . , 112cR, e.g., R number of threads, where R is an appropriate integer.

In an example, a physical processing core 102 (e.g., which is a physical processing core of the device 100) may implement one or more logical processors 105. Merely as an example, the core 102a is illustrated to execute logical processors 105a1, 105a2, 105a3, 105a4, and the core 102N is illustrated to execute logical processors 105N1, 105N2, 105N3. A number of logical processors being formed by a corresponding physical core 102 (e.g., four logical processors being formed by core 102a), as illustrated in FIG. 1A, is merely an example, and do not limit the scope of this disclosure. Although not illustrated, other cores (e.g., core 102b) may also form one or more logical processors.

Threads 112 of a specific process 108 may be executed by a core 102, or by more than one core. A logical processor 105 may execute a thread 112. A logical process refers to a thread 112 scheduled on a logical processor 105. The terms logical process and thread may be used interchangeably in this disclosure.

Thread migration refers to a scenario where a thread (or process) being executed in a core moves to another core. For example, the thread 112a1 may initially be executed by logical processor 105a1 of the core 102a, and then by the logical processor 105N1 of the core 102N. The migration of the thread 112a1 (or the parent process 108a) from the core 102a to the core 102N is referred to as thread migration.

FIG. 1B illustrates an example system 140 including a power management unit (PMU) 155 that implements the Power state determination circuitry 110 and the effective core utilization determination circuitry 115, according to some embodiments. The system 100 comprises a System on a Chip (SoC) 150. In the example of FIG. 1B, the SoC 150 includes a processor 152 (e.g., a central processing unit (CPU)) comprising the plurality of processing cores 102a, 102b, . . . , 102N of FIG. 1A.

The system **140** comprises the PMU **155**. In an example, the PMU **155** may include a dedicated power management processor **158**, although in another example a section of the processor **152** (e.g., one or more cores **102**) may be used to for the power management processor **158**. Although shown to be included within the SOC **150** in FIG. **1B**, the PMU **155** may be external to the SOC **150** as well (e.g., as a separate power management integrated circuit chip (PMIC)).

In some embodiments, the power management processor 158 may be used at least in part to implement the power state determination circuitry 110 and the effective core utilization determination circuitry 115. In some other embodiments, the power state determination circuitry 110 and/or the effective core utilization determination circuitry 115 may be separate from the power management processor 158.

Various application programs 160, the OS 164, one or more power management application programs 166, etc. execute on the processor 152 and/or the power management processor 158. For example, the application programs 160

and the OS 164 may execute on the processor 152 (symbolically illustrated using dotted line), and the one or more power management application programs 166 may execute on the power management processor 158 (symbolically illustrated using dotted line). In some embodiments, the 5 application programs 160 includes the processes 108a, 108b, 108c of FIG. 1A.

The system 140 includes a software interface through which the OS 164 communicates with the PMU 155 (e.g., through which the OS 164 communicates with the power 10 state determination circuitry 110 and/or the effective core utilization determination circuitry 115 of the PMU 155). For example, as will be discussed herein later with respect to FIGS. 2, 3, and 4, the OS 164 communicates the indicator **120** and the identifiers **124** to the power state determination 15 circuitry 110 and/or the effective core utilization determination circuitry 115 through such a software interface. In an example, an OS driver (not illustrated in FIG. 1B) of the OS 164 may be a part of the software interface between the OS **164** and the PMU **155**. The OS driver may transmit the 20 indicators 120, identifiers 124 from the OS 164 to the PMU 155, e.g., directly or via registers 200, 300, and/or 400 (these registers are discussed in further details with respect to FIGS. **2-4**).

Merely as an example, an interface through which the OS 164 communicates with the PMU 155 may include one or more of the registers 200, 300, or 400. For example, the OS 164 may write data in one or more of the registers 200, 300, or 400 (e.g., write the indicators 120 and/or the identifiers 124), and the PMU 155 (e.g., the power state determination circuitry 110 and the effective core utilization determination circuitry 115) may fetch the written data from the registers. In another example, the OS 164 communicates with the PMU 155 directly (e.g., by bypassing the registers), which is illustrated as a direct line between the processor 150 and 35 the PMU 155, and a direct line between the OS 164 and the PMU 155.

In some embodiments, the SOC 150 comprises a graphics processing unit (GPU) 168, an integrated graphics circuitry 191, a hardware accelerator 180 (e.g., which performs 40 functions more efficiently than is possible in software running on the more general-purpose processor 152), a memory interface 178 (e.g., to interface with a memory 190), a display engine 192 (e.g., to render images on a display 184), BIOS 196, etc.

The SOC 150 further comprises an I/O subsystem 175, e.g., for interfacing with one or more input/output devices, such as the display 184, one or more I/O peripheral devices 186, one or more storage devices 188, etc.

Referring again to FIG. 1A, in some embodiments, the 50 device 100 stores the performance or energy efficiency bias indicator 120 (also referred to as indicator 120). The indicator 120 is also referred to herein as "Energy Policy" Preference Hint" 120, as "Energy Performance Preference **120**," or as "Energy Performance Priority (EPP) **120**." FIG. 55 2 illustrates an example register 200 that stores the performance or energy efficiency bias indicator 120, according to some embodiments. The register 200, merely as an example, may also be referred to as an IA32\_Energy\_Preference\_Bias register 200, or an Energy\_Preference\_Bias register 200. 60 The indicator 120 may be, merely as an example and as illustrated in FIG. 2, may be a 4-bit field in the register 200. The indicator 120 may provide guidance as to whether favor increasing dynamic performance or conserve energy consumption.

The 4-bit indicator **120** can have a value from any of 0 to 15. The values represent a sliding scale, where a value of 0

8

(e.g., which may be the default reset value) may correspond to a hint preference for highest performance, and a value of 15 may correspond to a maximum energy savings. A value of, for example, 7 may roughly translate into a hint to balance performance with energy consumption. The bits 0 to 3 of the register 200 may be used for the indicator 120, and the bits 4 to 63 may be reserved for future use. Merely as an example, a value of the indicator 120 being lower than a threshold value may indicate a preference for performance, and a value of the indicator 120 being equal to or higher than the threshold value may indicate a preference for energy savings (e.g., preference for low power).

The Operating System (OS) may dynamically change the indicator 120, based on a variety of factors, such as user input, default configuration, power availability, type of processes being executed, a desired Quality of Service (QoS) of a process, etc. Merely as an example, if battery power of the device 100 is low and/or no Alternating Current (AC) power from an adapter is available, the OS may favor energy savings (e.g., a high value of the indicator 120). In another example, if power availability is sufficient, the OS may prefer performance (e.g., a low value of the indicator 120).

In an example, indicator 120 may be per logical process (e.g., per individual thread 112). Thus, each of the logical processes or threads 112 in the device 100 may be programmed with a different value of the indicator 120. The thread 112a1 may have a first value of the indicator 120, the thread 112a2 may have a second value of the indicator 120, and so on. Put differently, the device 100 may include different instances of the indicator 120, one for a corresponding logical process or thread 112. This may be useful in virtualization scenarios or any other appropriate scenario, where the performance and/or energy requirements of one logical process may differ from the other. The register 200 storing the indicator 120 may be an example of an interface through which the OS indicates whether the OS wants the cores 102 to bias towards performance or energy. For example, the register 200 (e.g., the IA32\_Energy Preference\_Bias register 200, or the Energy\_Preference\_Bias register 200) acts as an interface (e.g., a software interface) for the OS to prescribe a performance vs. energy efficiency preference.

FIG. 3 illustrates another example register 300 that stores the performance or energy efficiency bias indicator 120, according to some embodiments. The register 300, merely as an example, may also be referred to as an IA32\_HWP\_Request register 300, or as an HWP\_Request register 300.

The register 300 includes a minimum performance field 302 comprising bits 7:0. The field 302 may convey a hint to HWP (Hardware Controlled Performance States) hardware. The OS programs the minimum performance hint to achieve a required quality of service (QOS) or to meet a service level agreement (SLA) as needed.

The register 300 includes a maximum performance field 304 comprising bits 15:8, which conveys a hint to the HWP hardware. The OS programs this field to limit the maximum performance that is expected to be supplied by the HWP hardware. Excursions above the limit requested by OS are possible due to hardware coordination between the processor cores and other components in the package.

The register 300 includes a desired performance field 306 comprising bits 23:16, which conveys a hint to the HWP hardware. When set to zero, hardware autonomous selection determines the performance target. When set to a non-zero value, the field 306 conveys an explicit performance request hint to the hardware, effectively disabling HW Autonomous

selection. The Desired\_Performance input is non-constraining in terms of Performance and Energy Efficiency optimizations, which are independently controlled. A default value of this field is 0.

The register 300 includes the performance or energy efficiency bias indicator 120, where the indicator 120 is also referred to as Energy\_Performance\_Preference field (or referred to as Energy Performance Priority (EPP) field), comprising bits 31:24. This field conveys a hint to the HWP hardware. The OS may write a range of values from 0 (performance preference) to 0FFH (energy efficiency preference) to influence the rate of performance increase/decrease and the result of the hardware's energy efficiency and performance optimizations. The default value of this field is 80H. In an example, if this field is not supported, the HWP uses the value of the indicator 120 from the register 200 to determine the energy efficiency/performance preference.

The register 300 includes an activity\_Window field 310 comprising bits 41:32, which conveys a hint to the HWP 20 hardware specifying a moving workload history observation window for performance/frequency optimizations. If 0, the hardware may determine the appropriate window size. When writing a non-zero value to this field, this field may be encoded in the format of bits 38:32 as a 7-bit mantissa and 25 bits 41:39 as a 3-bit exponent value in powers of 10. The resultant value may be in microseconds. Thus, the minimal/maximum activity window size is 1 microsecond/1270 seconds. In an example, the Activity\_Window 310 influences the rate of performance increase and/or decrease. This 30 non-zero hint merely has meaning when the desired performance field 306 is set to 0.

The register 300 includes a package control field 312 comprising bit 42. When set, the field 312 causes a logical processor's IA32\_HWP\_REQUEST control inputs to be 35 derived from a register IA32\_HWP\_REQUEST\_PKG. The register 300 includes reserved field 314 comprising bits 63:43, which are reserved and set to zero.

Thus, referring to FIGS. 1A-3, the OS may communicate a bias towards performance or energy efficiency through the indicator 120, which may be included in any one or both the registers 200 or 300.

Thus, the register **200** (e.g., which may be the IA32\_Energy\_Preference\_Bias register) and/or the register **300** (e.g., which may be the IA32\_HWP\_Request register), 45 any of which may store the indicator **120**, may be examples of the interface through which the OS indicates whether the OS wants the cores **102** to bias towards performance or energy. For example, the registers **200** and/or **300** acts as an interface (e.g., a software interface) for the OS to prescribe 50 a performance vs. energy efficiency preference.

Referring again to FIG. 1A, in some embodiments, the device 100 stores a logical process identifier 124 (also referred to as identifier 124). Individual logical processes or threads 112 may have a corresponding instance of the 55 identifier 124. As an example, an identifier 124a1 may be associated with a logical process or thread 112a1, an identifier 124a2 may be associated with a logical process or thread 112a2, an identifier 124b1 may be associated with a logical process or thread 112b1, and so on. The identifier 124for a specific logical process or thread 112 may be a meta data tag indicating the uniqueness of the corresponding logical process or thread. A value of the identifier 124 may uniquely identify the corresponding thread. For example, the OS may tag a thread 112a1 with a corresponding unique 65 attribute using the identifier 124a1, the OS may tag a thread 112b1 with a corresponding unique attribute using the

10

identifier 124b1, and so on (it may be noted that merely a single instance of the identifier, labelled as identifier 124, is illustrated in FIG. 1A).

FIG. 4 illustrates an example register 400 including the logical process identifier 124, according to some embodiments. The register 400 may be at least in part similar to the register 300 of FIG. 3. The reserved bits 63:43 of the register may be used to store the logical process identifier 124. As discussed with respect to FIG. 3, the register 400 may be the IA32\_HWP\_Request register (or HWP\_Request register), in an example. In another example, the logical process identifier 124 may be included in another appropriate register.

Various fields of the register 400 (e.g., which may be the IA32\_HWP\_Request register (or HWP\_Request register)) are also shown in Table 1 below.

TABLE 1

| · | Bits  | Field                         |

|---|-------|-------------------------------|

| , | 0:7   | Minimum_Performance           |

|   | 8:15  | Maximum_Performance           |

|   | 23:16 | Desired_Performance           |

|   | 31:24 | Energy_Performance_Preference |

|   | 41:32 | Activity Window               |

|   | 42    | Package_Control               |

|   | 63:43 | Logical_Process_Identifier    |

Table 1 will be evident based on FIGS. 3-4 and associated discussion. As discussed with respect to FIG. 4 and also shown in Table 1, the register 400 includes the logical process identifier 124 (referred to as "Logical\_Process Identifier" in Table 1).

Referring to FIG. 4 and Table 1, in an example, the register 400 provides an interface with the OS that enables the OS to tag co-operative processes 108. For example, the device 100 may support per logical process instances of the register 400. Thus, the OS may request a level of performance and energy and/or performance priority (e.g., using the indicator 120) on a per logical process basis. An extension to this interface (e.g., the register 400) is to have the OS add the meta data tag (e.g., the identifier 124) indicating the uniqueness of this logical process. Thus, the register 400 can be used as a software interface by the OS to identify co-operative processes 108 using a unique attribute, e.g., using the identifier 124 (e.g., the Logical Process Identifier field 124) of the register 300.

The unique attribute or identifier 124 may be used to denote all the logical processes belong to the same parent process. For example, the referring to FIG. 1A, individual ones of the threads 112a1, 112a2, . . . , 112aP may be assigned corresponding instances of the identifier 124 (e.g., the threads 112a1, 112a2, . . . , 112aP may be respectively assigned identifiers 124a1, 124a2, . . . , 124aP). The identifiers 124a1, 124a2, . . . , 124aP may be used to identify the parent process 108 to which the threads 112a1, 112a2, . . . , 112aP belong. Put differently, the identifiers 124a1 and 124a2 may not only uniquely identify the threads 112a1 and 112a2, respectively, but also identify that these threads belong to the same parent process 108a.

In an example, the identifier 124 also identifies a logical processor 105 in which the corresponding thread 112 is being executed. For example, if the thread 112a1 is being executed in the logical processor 105a2, the identifier 124a1 may identify the logical processor 105a2.

FIG. 5 illustrates a graph 500 illustrates example processing cores 102a, 102b, 102c executing various threads, according to some embodiments. The X axis represents

time, and the Y axis represents the cores 102a, 102b, 102c. For example, between time t0 and t2, the thread 112a1 (e.g., which is identified using the indicator 124a1) of the process 108a is being executed at core 102a. At time t2, the process 108a migrates to core 102b, and the thread 112a3 of the process 108a is being executed at core 102b from time t2 to time t4. Between time t1 and t3, the thread 112b2 (e.g., which is identified using the indicator 124b2) of the process 108b is being executed at core 102b. The identifiers 124a1 and 124a3 respectively indicates that the process 108a is being executed in the core 102a from time t0 to t2, and is being executed in the core 102b from time t2 to t4, and

It is assumed that the time interval between time t0 and t1 is same as time interval between time t1 and t2, same as the time interval between time t2 and t3, and so on. The graph 500 is merely an example, is a simplistic representation of thread execution at various cores, and does not limit the scope of this disclosure.

A utilization is referred to as a ratio of: a duration of a C0 <sub>20</sub> state (e.g., an operating or active state) during a time period, and the time period. Thus, a utilization tracks a C0 residence over a specific duration of time. The utilization is also referred to herein as C0\_residency.

For example, referred to FIG. 5, a utilization of the core 25 **102***a* from time t**0** to t**5** is <sup>2</sup>/<sub>5</sub>, or 40% (e.g., for 40% of the time between t**0** and t**5**, the core **102***a* is executing threads). The utilization of each of the cores **102***b*, **102***c* is also 40%. The utilization of a core is also referred to herein as core utilization, core\_C0\_utilization, core\_C0\_residency, or the 30 like. Thus, the core utilization for each of the cores **102***a*, **102***b*, **102***c* from time t**0** to t**5** is 40%.

The utilization of the process 108a (e.g., note that the threads 112a1 and 112a3 are spawned by the same parent process 108a) is  $\frac{4}{5}$ , or 80% (e.g., for 80% of the time 35 between t0 and t5, one or more threads of the process 108a are being executed). The utilization of the process 108b(e.g., note that the threads 112b2 is spawned by the process 108b) is  $\frac{2}{5}$ , or 40%. The utilization of a process is also referred utilization, 40 herein process as process\_C0\_utilization, process\_C0\_residency, or the like. Thus, the process utilization for the processes 108a and 108bfrom time to to to are 80% and 40%, respectively. For example, if a process spawns multiple logical processes or threads (e.g., if the identifiers 124 of multiple threads 45 indicate that the threads belong to the same parent process), the process utilization would be a union or sum of C0 residence of these threads.

The utilization of the combination of all the cores of the device **100** from time **t0** to **t5** is 4/5, or 80%. The utilization 50 of the combination of all the cores is also referred to herein as device utilization, package utilization, package\_C0\_utilization, package\_C0\_residency, or the like, which is 80% in the example graph **500**.

The utilization of the thread 112a1 from time t0 to t5 is ½5, 55 or 40%. The utilization of each of the threads 112a3 and 112b2 from time t0 to t5 is also ½5, or 40%. The utilization of a thread is also referred to herein as thread utilization, thread\_C0\_utilization, thread\_C0\_residency, or the like.

FIG. 6 illustrates an example pseudo-code 600 for determining a process\_CO\_residency, a thread\_CO\_residency, and a package\_CO\_residency, according to some embodiments. For example, as discussed with respect to FIG. 5, these CO residencies may be determined based on tracking execution of individual threads using the identifiers 124. The 65 IA32\_HWP\_Request referred to in the pseudo-code 600 refers to the register 400, which outputs the identifier 124 for

12

a given thread. The principle of operation of the pseudocode 600 has been discussed with respect to FIG. 5.

Thus, FIG. 6 outputs the process\_C0\_residency for each of one or more of the processes 108a, 108b, ..., 108c. FIG. 6 outputs the thread\_C0\_residency for each of one or more of the threads 112a1, ..., 112aP, 112b1, ..., 112bQ, 112c1, ..., 112cR. FIG. 6 outputs the package\_C0\_residency (also referred to as pkg\_C0\_residency in FIG. 6) for the combination of all the cores 102a, ..., 102N.

Although not illustrated in FIG. 6, a core\_C0\_residency may also be determined for each of one or more of the cores 102a, . . . , 102N. For example, a core\_C0\_residency of a core 102 may be a union of the thread\_C0\_residency of all the threads being executed in the core 102.

FIG. 7A illustrates an example pseudo-code 700 for determining an "effective core utilization" of a core, based on the "Performance or energy efficiency bias indicator 120" of FIG. 1A, according to some embodiments. For example, as discussed with respect to FIGS. 1A-3, the indicator 120 (e.g., which may be the Energy Policy Preference Hint) provides an indication on whether the OS favors performance or energy efficiency.

If the indicator 120 has a relatively low value (e.g., lower than a threshold), this implies that the OS favors performance over energy efficiency. As illustrated in FIG. 7A, if the OS favors performance over energy efficiency (e.g., as indicated by the indicator 120), the effective utilization of the core may be based on (e.g., may be equal to) utilization of a process being executed in the core. On the other hand, if the OS favors energy efficiency over performance (e.g., the "Else" clause in FIG. 7A), the effective utilization of the core may be based on (e.g., may be equal to) an actual utilization of the core. This process may be repeated for all cores  $102a, \ldots, 102N$  of the device 100.

Thus, put differently, if the OS wants to bias towards performance, the effective utilization of a core over a time window is determined based on cumulative utilization of the process running on various cores. For example, referring to FIG. 5, for core 102a, if the OS wants to bias towards performance, the effective utilization of the core 102a is a union or cumulation of the utilization of the process 108a running on various cores (e.g., cores 102a, 102b). Thus, the effective utilization of the core 102a for this example is 80%. For example, if a process (or underlying threads) is migrating between two cores, the effective utilization for the process may be calculated based on the total utilization of the process over the two cores.

On the other hand, if the OS wants to bias towards energy efficiency, the effective utilization of the core over the time window for that core is determined based on the C0 residency of that specific core. For example, referring to FIG. 5, for core 102a, if the OS wants to bias towards energy efficiency, the effective utilization of the core 102a is the utilization of the core 102a, which is 40%.

Referring to FIGS. 1A and 7A, the device 100 includes an "effective core utilization determination circuitry 115" (also referred to as circuitry 115). In an example, the circuitry 115 determines the effective utilization of various cores, e.g., as discussed with respect to FIG. 7A.

FIG. 7B illustrates an example pseudo-code 750 for determining an effective core utilization of a core, based on the "Performance or energy efficiency bias indicator 120" of FIG. 1A, according to some embodiments. The pseudo-codes 700 and 750 are at least in part similar. However, in the code 750, if the OS favors performance over energy efficiency (e.g., as indicated by the indicator 120), the effective utilization of the core may be based on (e.g., may

be equal to) the package utilization (e.g., instead of being based on a utilization of a process being executed in the core).

In an example, the pseudo-code 750 may be used (e.g., instead of the pseudo-code 700) in situations where, for 5 example, is may not be possible or desirable to determine the process utilization. Such a scenario may arise when the logical process identifier 124 may not be available.

For example, the logical process identifier 124 is used to determine the process utilization (e.g., the logical process 10 identifier 124 is used to identify a parent process of a thread, and hence, is used to track the process utilization). When the logical process identifier 124 is not available, the process utilization may not be effectively tracked, and the pseudocode 750 may be used (e.g., instead of the pseudo-code 700). 15

In some embodiments, the device 100 includes the power state determination circuitry 110, e.g., for determining a power state (e.g., where a power state refers to a corresponding operating voltage and/or a corresponding operating frequency, such as a specific P-state in accordance with 20 ACPI standards) for individual cores (illustrated in FIG. 1A). For example, once an effective utilization of a core 102 is determined (e.g., as discussed with respect to FIGS. 7A-7B), an appropriate power state of a core may be selected based on the effective utilization of the core. The 25 power state, such as the P-state of the core in an example, is an ACPI state, which may specify a frequency, voltage, and/or other operating parameters for the core. For example, a power state, such as a P-state, may be selected from a P1 state, a P2 state, a P3 state, etc. Each of the P1, P2, P3 states 30 may be associated with corresponding frequency, voltage, and/or other operating parameters for the core. Thus, selecting a power state, such as a P-state, may be akin to selecting an operating frequency, voltage, and/or other operating parameters for the core. As discussed herein above, the 35 of FIG. 1A) are executed by the device 900. selection of the power state (or the selection of operating voltage, frequency, etc.) for a core 102 (e.g., core 102a) may be based on the effective utilization of the core 102 (e.g., core **102***a*).

For example, if the core 102a has a relatively higher 40 effective utilization, the core 102a may be operated at relatively high voltage and/or frequency. On the other hand, if the core 102a has a relatively lower effective utilization, the core 102a may be operated at relatively low voltage and/or frequency. Any appropriate type of controller (e.g., a 45 proportional controller, a PID controller, etc.) may be used to determine a power state (e.g., a P-state) for a core, based on the effective utilization of the core.

FIG. 8 illustrates a flowchart depicting a method 840 for assigning operating voltage and/or operating frequency to 50 individual cores 102 of the system 100 of FIG. 1A, according to some embodiments. Although the blocks in the flowchart with reference to FIG. 8 are shown in a particular order, the order of the actions can be modified. Thus, the illustrated embodiments can be performed in a different 55 order, and some actions/blocks may be performed in parallel. Some of the blocks and/or operations listed in FIG. 8 may be optional in accordance with certain embodiments. The numbering of the blocks presented is for the sake of clarity and is not intended to prescribe an order of operations 60 in which the various blocks must occur.

At 804 of the method 800, an indicator (e.g., indicator 120), which indicates a preference for either performance or energy efficiency, may be received from the OS (e.g., OS **164** of FIG. **1B**). For example, the effective core utilization 65 determination circuitry 115 may receive the indicator 120 via any of the registers 200, 300, and/or 400.

14

At 808, one or more identifiers (e.g., identifiers 124), each of which uniquely identify a corresponding process, may be received from the OS (e.g., OS 164 of FIG. 1B). For example, the effective core utilization determination circuitry 115 may receive the identifiers via any of the register **400**.

At **812**, a utilization of a first process may be determined (e.g., by the effective core utilization determination circuitry 115), based at least in part on the identifiers 124, e.g., as discussed with respect to FIGS. 5, 6, and 7A. In an example, a first processing core (e.g., core 102a) is to at least in part execute the first process. Also at **812**, a utilization of the first processing core may be determined (e.g., by the effective core utilization determination circuitry 115), e.g., as discussed with respect to FIGS. 5, 6, and 7A.

At **816**, one of the utilization of the first process or the utilization of the first processing core may be selected (e.g., by the effective core utilization determination circuitry 115) as an effective utilization of the first processing core, based on the indicator **120**, e.g., as discussed with respect to FIG. 7A.

At **820**, at least one of an operating voltage or an operating frequency of the first processing core may be selected (e.g., by the power state determination circuitry 110), based at least in part on the effective utilization of the first processing core, e.g., as discussed herein above in further details.

FIG. 9 schematically illustrates a computing device 900 (also referred to as device 900) that determines operating states (e.g., power states, voltages, frequencies, etc.) of processing cores, based on an effective utilization of the processing cores, according to some embodiments. The device 900 comprises cores  $902a, \ldots, 902f$  (e.g., which may be similar to the cores 102 of FIG. 1A). Processes 908x, 908y, 908z (e.g., which may be similar to the processes 108

The process 908x generates threads 912x1, . . . , 912xP, each of which have corresponding identifiers 124 (e.g., identifiers  $124x1, \ldots, 124xP$ , respectively). The identifiers 124x of the threads 912x identify the process 908x as the parent process. It is assumed, merely as an example, that the indicators 120 associated with the threads  $912x1, \dots, 912xP$ indicate a preference for high performance.

The process 908y generates threads 912y1, . . . , 912yQ, each of which have corresponding identifiers 124 (e.g., identifiers 124y1, . . . , 124yQ, respectively). The identifiers 124y of the threads 912y identify the process 908y as the parent process. It is assumed that the indicators 120 associated with the threads 912y1, 912yQ indicate a preference for low power (e.g., energy conservation).

The process 908z generates threads 912z1, . . . , 912zR, each of which have corresponding identifiers 124 (e.g., identifiers 124z1, . . . , 124zR, respectively). The identifiers 124z of the threads 912z identify the process 908z as the parent process. It is assumed that the indicators 120 associated with the threads 912z1, . . , 912zR indicate a preference for high performance.

Thus, the processes 908x and 908z have a preference for high performance, while the process 908 has a preference for low power or energy conservation. In some embodiments, a thread scheduler 903 schedules the threads 912 for execution in various cores  $902a, \ldots, 902f$ .

In some embodiments, the power state of the cores 902 may be determined based on effective utilization of the cores 902. In the example of FIG. 9, the effective utilization of first one or more cores is maximum of process utilization or core utilization (e.g., Effective utilization=Max (process utilization, core utilization)). The effective utilization of second

one or more cores is minimum of process utilization or core utilization (e.g., Effective utilization=Min (process utilization, core utilization)).

For example, as illustrated in FIG. 9, the effective utilization of the core 902a is minimum of (process utilization, 5) core utilization), where the process utilization and the core utilization are discussed with respect to FIG. 7A-7B. Also, the effective utilization of the core 902b is maximum of (process utilization, core utilization).

Thus, in FIG. 9, the threads 912 are dynamically divided 10 into two main groups: high performance threads (e.g., threads 912x, 912z), and low power threads (e.g., threads 912y). The cores 902 are also dynamically grouped into two groups: group 907a, 907b.

handles high performance threads. Cores 902b, 902e, 902f of the group 907b, accordingly, have effective utilization=Max (process utilization, core utilization). The cores 902*b*, 902*e*, 902*f* of the group 907*b* may be set on a single power domain (SPD), and are to handle the high- 20 performance threads (e.g., threads 912x, 912z). Accordingly, in some embodiments, the cores of the group 907b may be set for the single power domain having a high value of frequency and/or a high value of voltage (e.g., maximum frequency and/or maximum voltage).

The group 907a includes cores 902a, 902c, 902d, which handle low power threads (e.g., thread having preference for low power, such as threads 912y). Cores 902a, 902c, 902dof the group 907a, accordingly, have effective utilization=Min (process utilization, core utilization). In 30 some embodiments, a voltage and/or a frequency of the cores of this group 907a are determined dynamically by a power management circuitry 911 (also referred to as circuitry 911). For example, the circuitry 911 sets voltage Va, frequency Fa for the core 902a; sets voltage Vc, frequency 35 Fc for the core 902c; and so on. The cores of the group 907aare on a per core p-state (PCPS) set, as the power state of the cores of this group is determined on an individual core basis.

The thread scheduler 903 (e.g., which may be operated by the OS) may allow high performance threads to migrate and 40 execute primarily (e.g., only) among the cores of the group 907b, and may allow low power threads to migrate and execute primarily (e.g., only) among the cores of the group 907a. The core groups may be pre-allocated in advance and communicated to the OS, and/or allocated dynamically 45 based on the OS needs. Thus, the high-performance threads 912x, 912z may be executed by the cores of the group 907b; and the low power threads 912y may be executed by the cores of the group 907a,

Running some of the cores (e.g., cores of the group 907b) 50 on a single power domain (e.g., selecting relatively high, such as maximum, voltage and/or frequency for these cores) provides high performance, and prevents from using unnecessary power for the other cores (e.g., cores of the group 907a) that may not require much performance. Per core 55 power state (e.g., for the group 907a) may optimize the power consumption by running each core on a corresponding voltage and/or frequency based on its power and/or performance requirements.

In a conventional system, performance may be impacted 60 due to thread migration between different cores. For example, performance hit may occur when a thread migrates from one core running at high power state to another operating at a low power state. However, in the example of FIG. 9, the thread scheduler 903 allows high performance 65 threads to migrate and execute primarily (e.g., only) among the cores of the group 907b, and allows low power threads

**16**

to migrate and execute primarily (e.g., only) among the cores of the group 907a. This prevents from the above discussed performance impact due to thread migration, thereby improving the performance of the device 900.

In some embodiments, the circuitry 911 monitors the indicator 120 of the threads being scheduled on a core. If the indicator 120 is lower than a threshold value (e.g., which indicates bias towards performance), the circuitry 911 runs the core on the single power domain (e.g., groups the core in group 907b). On the other hand, if the indicator 120 of the threads scheduled for a core is higher than the threshold value (e.g., which indicates bias towards low power), the circuitry 911 runs the core on a per core power state (e.g., groups the core in group 907a). This prevents any perfor-The group 907b includes cores 902b, 902e, 902f, which 15 mance issues due to threads migration, as well as provide low power optimization for the low power threads.

> FIG. 10 illustrates a power state determination circuitry 110 and an effective core utilization determination circuitry 115, according to some embodiments. For example, as discussed with respect to FIG. 1A, the device 100 of FIG. 1A (and also the device 900 of FIG. 9) may include the circuitries 110, 115. The power state determination circuitry 110 receives the performance or energy efficiency bias indicators 120 for various threads, and also receives effec-25 tive core utilization 1017 (e.g., from the effective core utilization determination circuitry 115). The effective core utilization determination circuitry 115 determines the effective core utilization 1017 using the pseudo-codes 700 and/or **750** of FIG. **7A** and/or **7B**.

The power state determination circuitry 110 determines the power states of the various cores 102, e.g., based on the indicators 120 and the effective core utilization 1017. Determination of the power state involves determining an operating voltage and/or operating frequency of individual cores that are active (e.g., that are in C0 operating state). Any appropriate type of controller (e.g., a proportional controller, a PID controller, etc.) may be used in the power state determination circuitry 110.

The power state determination circuitry 110 may also determine various C0 residencies 1013, such as core\_C0\_residency, package\_C0\_residency, thread\_C0\_residency, process\_C0\_residency, e.g., as discussed with respect to FIG. 6. The effective core utilization determination circuitry 115 receives the various C0 residency 1013, and determines the effective core utilization 1017 using, for example, the pseudo-codes 700 and/or 750 of FIG. 7A and/or 7B. In an example, the effective core utilization determination circuitry 115 receives the indicators 120, and determines the effective core utilization 1017 based on the indicators 120.

It is to be noted that any reference to circuitry (e.g., circuitry 110, 115) are not for restricting merely to circuitries. For example, individual ones of the circuitries 110, 115 may be use any circuit elements, hardware, software, firmware, logic, etc., for operation.

FIG. 11 illustrates a computer system, a computing device or a SoC (System-on-Chip) 2100, where operating states (e.g., power states, frequencies, voltages, etc.) of processing cores are determined based on a "performance or energy efficiency bias indicator" and an "effective core utilization," according to some embodiments. It is pointed out that those elements of FIG. 11 having the same reference numbers (or names) as the elements of any other figure can operate or function in any manner similar to that described, but are not limited to such.

In some embodiments, computing device 2100 represents an appropriate computing device, such as a computing

tablet, a mobile phone or smart-phone, a laptop, a desktop, an IOT device, a server, a set-top box, a wireless-enabled e-reader, or the like. It will be understood that certain components are shown generally, and not all components of such a device are shown in computing device **2100**.

In some embodiments, computing device 2100 includes a first processor 2110. The various embodiments of the present disclosure may also comprise a network interface within 2170 such as a wireless interface so that a system embodiment may be incorporated into a wireless device, for 10 example, cell phone or personal digital assistant.

In one embodiment, processor 2110 can include one or more physical devices, such as microprocessors, application processors, microcontrollers, programmable logic devices, or other processing means. The processing operations performed by processor 2110 include the execution of an operating platform or operating system on which applications and/or device functions are executed. The processing operations include operations related to I/O with a human user or with other devices, operations related to power 20 management, and/or operations related to connecting the computing device 2100 to another device. The processing operations may also include operations related to audio I/O and/or display I/O.

In one embodiment, computing device 2100 includes 25 audio subsystem 2120, which represents hardware (e.g., audio hardware and audio circuits) and software (e.g., drivers, codecs) components associated with providing audio functions to the computing device. Audio functions can include speaker and/or headphone output, as well as microphone input. Devices for such functions can be integrated into computing device 2100, or connected to the computing device 2100. In one embodiment, a user interacts with the computing device 2100 by providing audio commands that are received and processed by processor 2110.

Display subsystem 2130 represents hardware (e.g., display devices) and software (e.g., drivers) components that provide a visual and/or tactile display for a user to interact with the computing device 2100. Display subsystem 2130 includes display interface 2132, which includes the particular screen or hardware device used to provide a display to a user. In one embodiment, display interface 2132 includes logic separate from processor 2110 to perform at least some processing related to the display. In one embodiment, display subsystem 2130 includes a touch screen (or touch pad) 45 device that provides both output and input to a user.

I/O controller 2140 represents hardware devices and software components related to interaction with a user. I/O controller 2140 is operable to manage hardware that is part of audio subsystem 2120 and/or display subsystem 2130. 50 Additionally, I/O controller 2140 illustrates a connection point for additional devices that connect to computing device 2100 through which a user might interact with the system. For example, devices that can be attached to the computing device 2100 might include microphone devices, 55 speaker or stereo systems, video systems or other display devices, keyboard or keypad devices, or other I/O devices for use with specific applications such as card readers or other devices.

As mentioned above, I/O controller 2140 can interact with 60 audio subsystem 2120 and/or display subsystem 2130. For example, input through a microphone or other audio device can provide input or commands for one or more applications or functions of the computing device 2100. Additionally, audio output can be provided instead of, or in addition to 65 display output. In another example, if display subsystem 2130 includes a touch screen, the display device also acts as

**18**

an input device, which can be at least partially managed by I/O controller 2140. There can also be additional buttons or switches on the computing device 2100 to provide I/O functions managed by I/O controller 2140.

In one embodiment, I/O controller 2140 manages devices such as accelerometers, cameras, light sensors or other environmental sensors, or other hardware that can be included in the computing device 2100. The input can be part of direct user interaction, as well as providing environmental input to the system to influence its operations (such as filtering for noise, adjusting displays for brightness detection, applying a flash for a camera, or other features).

In one embodiment, computing device 2100 includes power management 2150 that manages battery power usage, charging of the battery, and features related to power saving operation. Memory subsystem 2160 includes memory devices for storing information in computing device 2100. Memory can include nonvolatile (state does not change if power to the memory device is interrupted) and/or volatile (state is indeterminate if power to the memory device is interrupted) memory devices. Memory subsystem 2160 can store application data, user data, music, photos, documents, or other data, as well as system data (whether long-term or temporary) related to the execution of the applications and functions of the computing device 2100. In one embodiment, computing device 2100 includes a clock generation subsystem 2152 to generate a clock signal.

Elements of embodiments are also provided as a machine-readable medium (e.g., memory 2160) for storing the computer-executable instructions (e.g., instructions to implement any other processes discussed herein). The machine-readable medium (e.g., memory 2160) may include, but is not limited to, flash memory, optical disks, CD-ROMs, DVD ROMs, RAMs, EPROMs, EEPROMs, magnetic or optical cards, phase change memory (PCM), or other types of machine-readable media suitable for storing electronic or computer-executable instructions. For example, embodiments of the disclosure may be downloaded as a computer program (e.g., BIOS) which may be transferred from a remote computer (e.g., a server) to a requesting computer (e.g., a client) by way of data signals via a communication link (e.g., a modem or network connection).

Connectivity 2170 includes hardware devices (e.g., wireless and/or wired connectors and communication hardware) and software components (e.g., drivers, protocol stacks) to enable the computing device 2100 to communicate with external devices. The computing device 2100 could be separate devices, such as other computing devices, wireless access points or base stations, as well as peripherals such as headsets, printers, or other devices.

Connectivity 2170 can include multiple different types of connectivity. To generalize, the computing device 2100 is illustrated with cellular connectivity 2172 and wireless connectivity 2174. Cellular connectivity 2172 refers generally to cellular network connectivity provided by wireless carriers, such as provided via GSM (global system for mobile communications) or variations or derivatives, CDMA (code division multiple access) or variations or derivatives, TDM (time division multiplexing) or variations or derivatives, or other cellular service standards. Wireless connectivity (or wireless interface) 2174 refers to wireless connectivity that is not cellular, and can include personal area networks (such as Bluetooth, Near Field, etc.), local area networks (such as Wi-Fi), and/or wide area networks (such as Wi-Fi).

Peripheral connections 2180 include hardware interfaces and connectors, as well as software components (e.g., driv-

ers, protocol stacks) to make peripheral connections. It will be understood that the computing device 2100 could both be a peripheral device ("to" 2182) to other computing devices, as well as have peripheral devices ("from" 2184) connected to it. The computing device 2100 commonly has a "docking" 5 connector to connect to other computing devices for purposes such as managing (e.g., downloading and/or uploading, changing, synchronizing) content on computing device 2100. Additionally, a docking connector can allow computing device 2100 to connect to certain peripherals that allow 10 the computing device 2100 to control content output, for example, to audiovisual or other systems.

In addition to a proprietary docking connector or other proprietary connection hardware, the computing device **2100** can make peripheral connections **2180** via common or 15 standards-based connectors. Common types can include a Universal Serial Bus (USB) connector (which can include any of a number of different hardware interfaces), Display-Port including MiniDisplayPort (MDP), High Definition Multimedia Interface (HDMI), Firewire, or other types.

In some embodiments, the computing device 2100 may comprise the power state determination circuitry 110, effective core utilization determination circuitry 115, etc., as discussed with respect to FIGS. 1A-10. FIG. 11 illustrates various example locations of the power state determination 25 circuitry 110 and the effective core utilization determination circuitry 115. The power state determination circuitry 110 and/or the effective core utilization determination circuitry 115 may be included in the processor 2110, in an example. The power state determination circuitry 110 and/or the 30 effective core utilization determination circuitry 115 may be coupled to the processor 2110, in another example. The power state determination circuitry 110 and/or the effective core utilization determination circuitry 115 may be included in a PMU, or a PMIC, e.g., as discussed with respect to FIG. 35 1B, in another example. For example, operating states (e.g., power states, frequencies, voltages, etc.) of various processing cores (e.g., which are included in the processors 2110) are determined based on a "performance or energy efficiency bias indicator" and an "effective core utilization," as dis- 40 cussed with respect to FIGS. 1A-10.

Reference in the specification to "an embodiment," "one embodiment," "some embodiments," or "other embodiments' means that a particular feature, structure, or characteristic described in connection with the embodiments is 45 included in at least some embodiments, but not necessarily all embodiments. The various appearances of "an embodiment," "one embodiment," or "some embodiments" are not necessarily all referring to the same embodiments. If the specification states a component, feature, structure, or char- 50 acteristic "may," "might," or "could" be included, that particular component, feature, structure, or characteristic is not required to be included. If the specification or claim refers to "a" or "an" element, that does not mean there is only one of the elements. If the specification or claims refer 55 to "an additional" element, that does not preclude there being more than one of the additional element.

Furthermore, the particular features, structures, functions, or characteristics may be combined in any suitable manner in one or more embodiments. For example, a first embodi- 60 ment may be combined with a second embodiment anywhere the particular features, structures, functions, or characteristics associated with the two embodiments are not mutually exclusive

While the disclosure has been described in conjunction 65 with specific embodiments thereof, many alternatives, modifications and variations of such embodiments will be appar-

**20**

ent to those of ordinary skill in the art in light of the foregoing description. The embodiments of the disclosure are intended to embrace all such alternatives, modifications, and variations as to fall within the broad scope of the appended claims.

In addition, well known power/ground connections to integrated circuit (IC) chips and other components may or may not be shown within the presented figures, for simplicity of illustration and discussion, and so as not to obscure the disclosure. Further, arrangements may be shown in block diagram form in order to avoid obscuring the disclosure, and also in view of the fact that specifics with respect to implementation of such block diagram arrangements are highly dependent upon the platform within which the present disclosure is to be implemented (i.e., such specifics should be well within purview of one skilled in the art). Where specific details (e.g., circuits) are set forth in order to describe example embodiments of the disclosure, it should be apparent to one skilled in the art that the disclosure can 20 be practiced without, or with variation of, these specific details. The description is thus to be regarded as illustrative instead of limiting.

The following examples pertain to further embodiments. Specifics in the example may be used anywhere in one or more embodiments. All optional features of the apparatus described herein may also be implemented with respect to a method or process.