#### US011250611B1

# (12) United States Patent

# Ruud et al.

# (10) Patent No.: US 11,250,611 B1

# (45) **Date of Patent:** Feb. 15, 2022

## (54) GRAPHICS PROCESSING

(71) Applicant: **Arm Limited**, Cambridge (GB)

(72) Inventors: Ole Magnus Ruud, Oslo (NO); Rafal

Stepuch, Cambridge (GB); Toni Viki

Brkic, Staffanstorp (SE)

(73) Assignee: Arm Limited, Cambridge (GB)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 17/163,281

(22) Filed: Jan. 29, 2021

(51) Int. Cl. *G06T 15/00*

(2011.01) (2011.01)

G06T 15/80 (52) U.S. Cl.

CPC ...... *G06T 15/005* (2013.01); *G06T 15/80*

(2013.01)

## (58) Field of Classification Search

None

See application file for complete search history.

## (56) References Cited

## U.S. PATENT DOCUMENTS

| 2015/0178983 A1 | * 6/2015        | Akenine-Moller | G06T 15/80 |

|-----------------|-----------------|----------------|------------|

|                 |                 |                | 345/426    |

| 2017/0263046 A1 | <b>*</b> 9/2017 | Patney         | G06F 3/013 |

| 2017/0293995 A1* | 10/2017 | Saleh G06T 15/005       |

|------------------|---------|-------------------------|

| 2017/0323475 A1* | 11/2017 | Moreton G06T 15/30      |

| 2018/0047203 A1* | 2/2018  | Grossman G06T 15/005    |

| 2018/0232936 A1* | 8/2018  | Nevraev G06T 11/40      |

| 2018/0240268 A1* | 8/2018  | Nevraev G06T 15/005     |

| 2018/0284872 A1* | 10/2018 | Schluessler G06F 9/5083 |

| 2019/0005712 A1* | 1/2019  | Nevraev G06T 11/40      |

| 2019/0005713 A1* | 1/2019  | Nevraev G06T 17/10      |

| 2019/0005714 A1* | 1/2019  | Fuller G06T 1/20        |

| 2020/0051290 A1* | 2/2020  | Yang G06T 13/20         |

#### OTHER PUBLICATIONS

DirectX Developer Blog, "Variable Rate Shading: a scalpel in a world of sledgehammers", Mar. 18, 2019, Microsoft, website, retrieved from: https://devblogs.microsoft.com/directx/variable-rate-shading-a-scalpel-in-a-world-of-sledgehammers/ on Dec. 3, 2021.\*

## \* cited by examiner

Primary Examiner — Robert Bader (74) Attorney, Agent, or Firm — Vierra Magen Marcus LLP

# (57) ABSTRACT

A method of operating a graphics processor that executes a graphics processing pipeline that can generate a render output using different shading rates is disclosed. First and second input shading rates are combined prior to rasterisation, and a combined shading rate may be propagated through the pipeline instead of the first and second input shading rates. The combined shading rate may then be combined with a third input shading rate at or after the rasterisation stage. This can reduce bandwidth, hardware and energy requirements.

# 19 Claims, 5 Drawing Sheets

# **GRAPHICS PROCESSING**

## BACKGROUND

The technology described herein relates to the processing 5 of computer graphics, and in particular to a method of operating a graphics processor.

Graphics processing is normally carried out by first splitting a scene (e.g. a 3-D model) to be displayed into a number of similar basic components or "primitives", which primi- 10 tives are then subjected to the desired graphics processing operations. The graphics "primitives" are usually in the form of simple polygons, such as triangles or quadrilaterals, or points or lines.

The graphics primitives are usually generated by the 15 applications program interface (API) for the graphics processing system, using the graphics drawing instructions (requests) received from the application (e.g. game) that requires the graphics processing (render) output.

Each primitive is at this stage defined by and represented 20 as a set of vertices. Each vertex for a primitive has associated with it a set of data (such as position, colour, texture and other attributes data) representing the vertex. This "vertex data" is then used, e.g., when rasterising and rendering the primitive(s) to which the vertex relates in order to generate 25 the desired render output of the graphics processing system.

For a given output, e.g. frame to be displayed, to be generated by the graphics processing system, there will typically be a set of vertices defined for the output in question. The primitives to be processed for the output will 30 then be indicated as comprising given vertices in the set of vertices for the graphics processing output being generated. Typically, the overall output, e.g. frame to be generated, will be divided into smaller units of processing, referred to as "draw calls". Each draw call will have a respective set of 35 different overlapping primitives, at a given location may vertices defined for it and a set of primitives that use those vertices.

Once primitives and their vertices have been generated and defined, they can be processed by the graphics processing system, in order to generate the desired graphics pro- 40 cessing output (render output), such as a frame for display.

This basically involves determining which sampling points of an array of sampling points associated with the render output area to be processed are covered by a primitive, and then determining the appearance each sampling 45 point should have (e.g. in terms of its colour, etc.) to represent the primitive at that sampling point. These processes are commonly referred to as rasterising and rendering, respectively.

The rasterising process determines the sample positions 50 that should be used for a primitive (i.e. the (x, y) positions of the sample points to be used to represent the primitive in the output, e.g. scene to be displayed). This is typically done using the positions of the vertices of a primitive.

The rendering process then derives (samples) the data, 55 such as red, green and blue (RGB) colour values and an "Alpha" (transparency) value, necessary to represent the primitive at the sample points (i.e. "shades" each sample point). This can involve, for example, applying textures, blending sample point data values, etc.

(The term "rasterisation" is sometimes used to mean both primitive conversion to sample positions and rendering. However, herein "rasterisation" will be used to refer to converting primitive data to sampling point addresses only.)

These processes are typically carried out by testing sets of 65 one, or of more than one, sampling point, and then generating for each set of sampling points found to include a

sample point that is inside (covered by) the primitive in question (being tested), a discrete graphical entity usually referred to as a "fragment" on which the graphics processing operations (such as rendering) are carried out. Covered sampling points are thus, in effect, processed as fragments that will be used to render the primitive at the sampling points in question. The "fragments" are the graphical entities that pass through the rendering process (the rendering pipeline). Each fragment that is generated and processed may, e.g., represent a single sampling point or a set of plural sampling points, depending upon how the graphics processing system is configured.

Each fragment will typically have "fragment data", such as colour, depth and/or transparency data, associated with it, with the fragment data for a given fragment typically being derived from primitive data associated with (the vertices of) the primitive to which the fragment relates.

A "fragment" is therefore effectively (has associated with it) a set of primitive data as interpolated to a given output space sample point or points of a primitive. It may also include per-primitive and other state data that is required to shade the primitive at the sample point (fragment position) in question. Each graphics fragment may typically be the same size and location as a "pixel" of the output (e.g. output frame) (since as the pixels are the singularities in the final display, there may be a one-to-one mapping between the "fragments" the graphics processor operates on (renders) and the pixels of a display). However, it can be the case that there is not a one-to-one correspondence between a fragment and a display pixel, for example where particular forms of post-processing are carried out on the rendered image prior to displaying the final image.

It is also the case that as multiple fragments, e.g. from affect each other (e.g. due to transparency and/or blending), the final pixel output may depend upon plural or all fragments at that pixel location.

Correspondingly, there may be a one-to-one correspondence between the sampling points and the pixels of a display, but more typically there may not be a one-to-one correspondence between sampling points and display pixels, as downsampling may be carried out on the rendered sample values to generate the output pixel values for displaying the final image. Similarly, where multiple sampling point values, e.g. from different overlapping primitives, at a given location affect each other (e.g. due to transparency and/or blending), the final pixel output will also depend upon plural overlapping sample values at that pixel location.

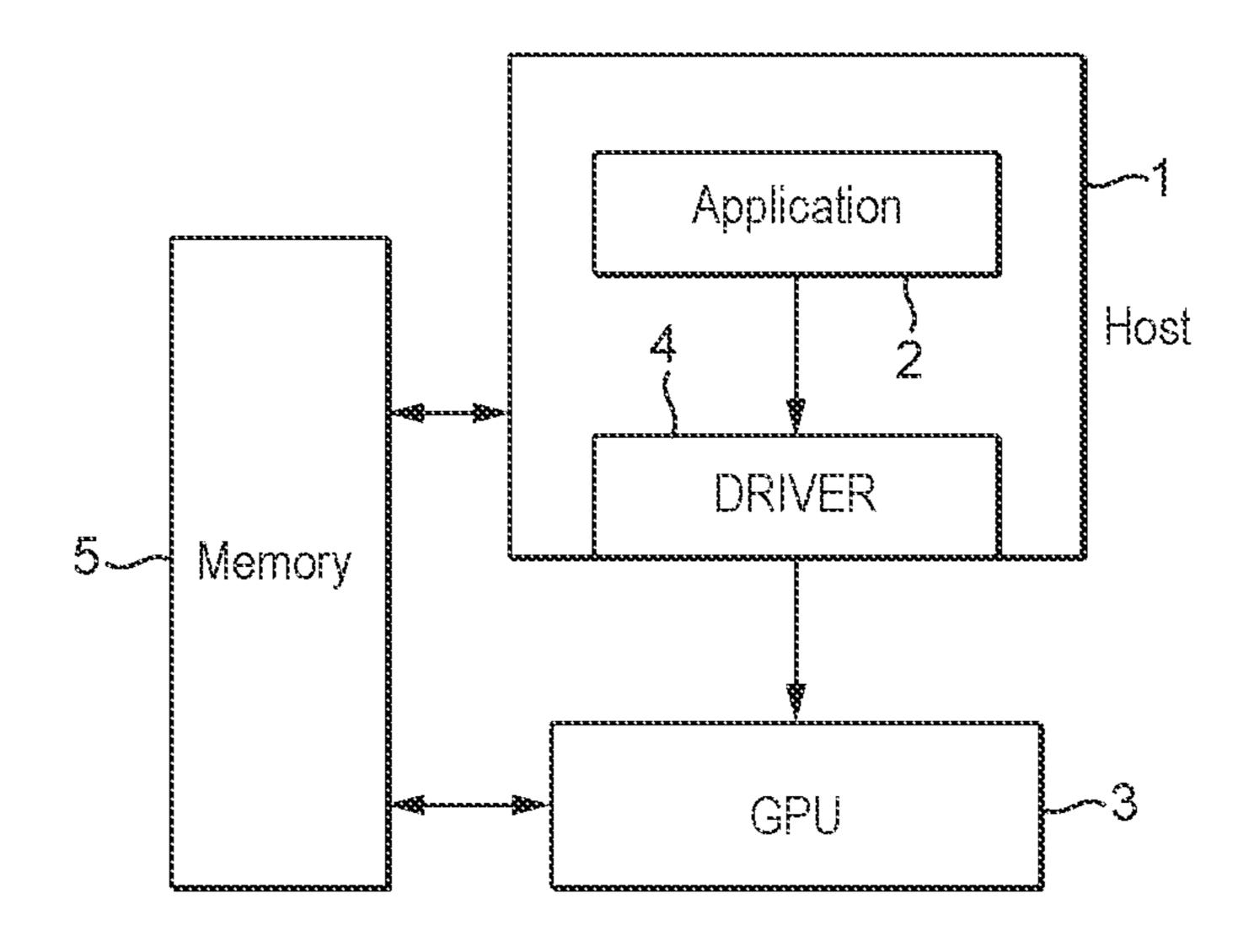

FIG. 1 shows a typical computer graphics processing system, comprising a host processor (CPU) 1, a graphics processing unit (GPU) 3, and a memory 5 for storing data required by and/or generated by the host processor 1 and graphics processor 3.

When an application 2 that is executing on the host processor 1 requires graphics processing from the graphics processor 3, such as a frame to be displayed, the application 2 will send appropriate commands and data to a driver 4 for the graphics processor 3 that is running on the host processor 1. The driver 4 will then send appropriate commands and data to the graphics processor 3 to cause it to generate the render output required by the application 2. The driver 4 sends commands and data to the graphics processor 3 by writing to the memory 5.

The commands and data provided by the driver 4 will include commands to render primitives for the render output to be generated by the graphics processor 3, together with

associated vertex data representing the vertices to be used for the primitives for the render output.

The commands sent to the graphics processor 3 cause the graphics processor 3 to read the vertex data from the memory 5, and process the read vertex data to generate the render output. The graphics processor 3 will typically use the vertex data for a primitive to rasterise the primitive to one or more fragments each (potentially) applying to a region (area) of the render output. The fragments will then be rendered.

The completed render output (e.g. frame) may be written in a frame buffer in the memory 5, from where it may be provided for display on a display device, such as a screen or printer.

When rendering a render output, e.g. frame for display, there is typically a balance between image quality and processing effort. For example, "supersampling" arrangements attempt to increase image quality by increasing the number of colours that are sampled (rendered), but this typically involves a greater processing effort. Conversely, decreasing the number of colours that are sampled (rendered) will usually reduce processing requirements, but at the expense of reduced image quality.

"Variable rate shading" (VRS) is a technique that allows this balance between image quality and processing effort to be varied across a render output, e.g. frame for display. In <sup>25</sup> particular, "variable rate shading" (VRS) allows the area of a render output, e.g. frame, that a single colour is sampled (rendered) for, i.e. the "shading rate", to vary within the render output.

Thus, in "variable rate shading" (VRS), different shading rates can be used to render a render output such that, for example, in some places in the output a single sampled (rendered) colour is used for a single output pixel, whereas elsewhere in the output, the same single sampled (rendered) colour is used for each of plural output pixels in a block of plural output pixels, thereby reducing the processing effort for those pixels.

The Applicants believe that there remains scope for improvements to graphics processors and to graphics processing.

## BRIEF DESCRIPTION OF THE DRAWINGS

Various embodiments of the technology described herein will now be described by way of example only and with 45 reference to the accompanying drawings, in which:

- FIG. 1 shows an exemplary graphics processing system;

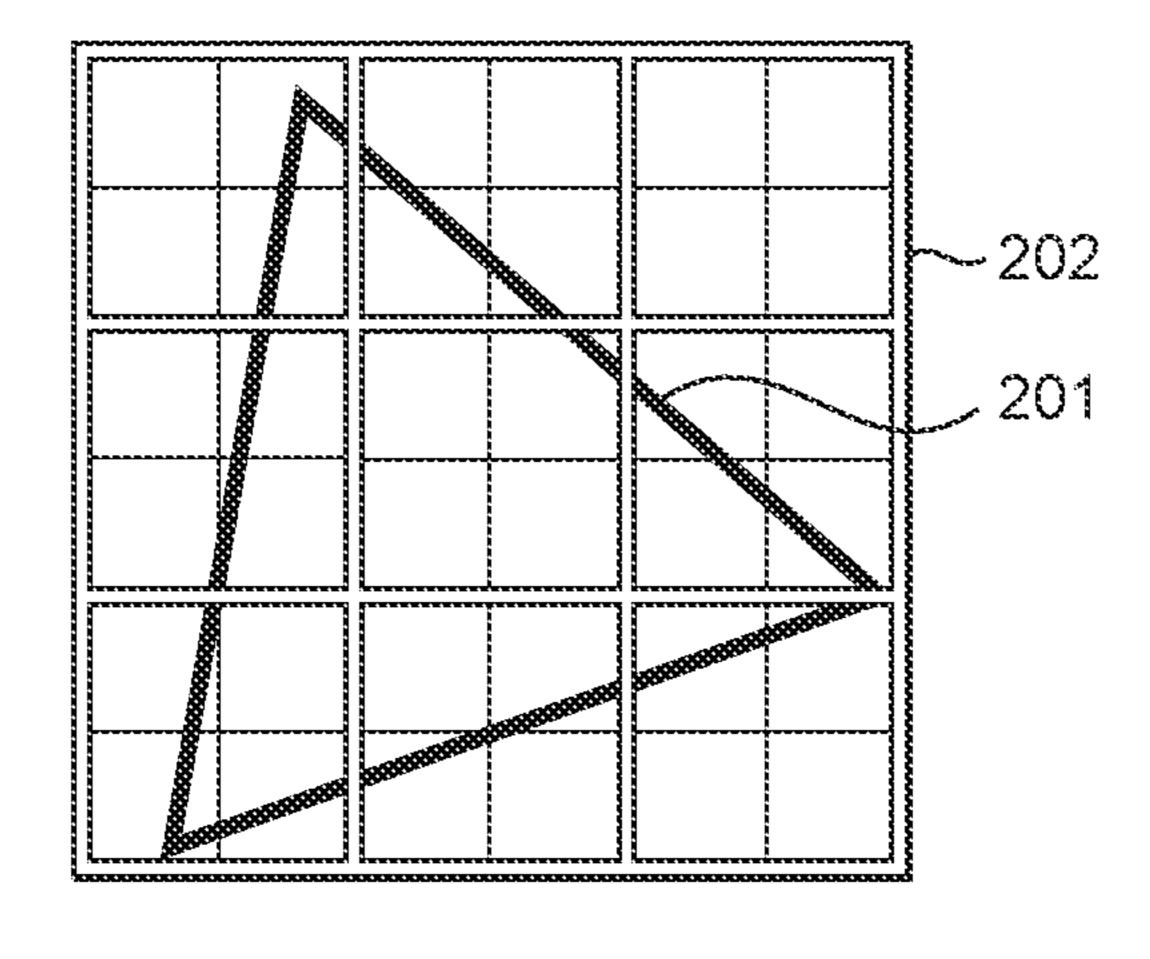

- FIG. 2 illustrates an exemplary primitive being rendered according to different shading rates;

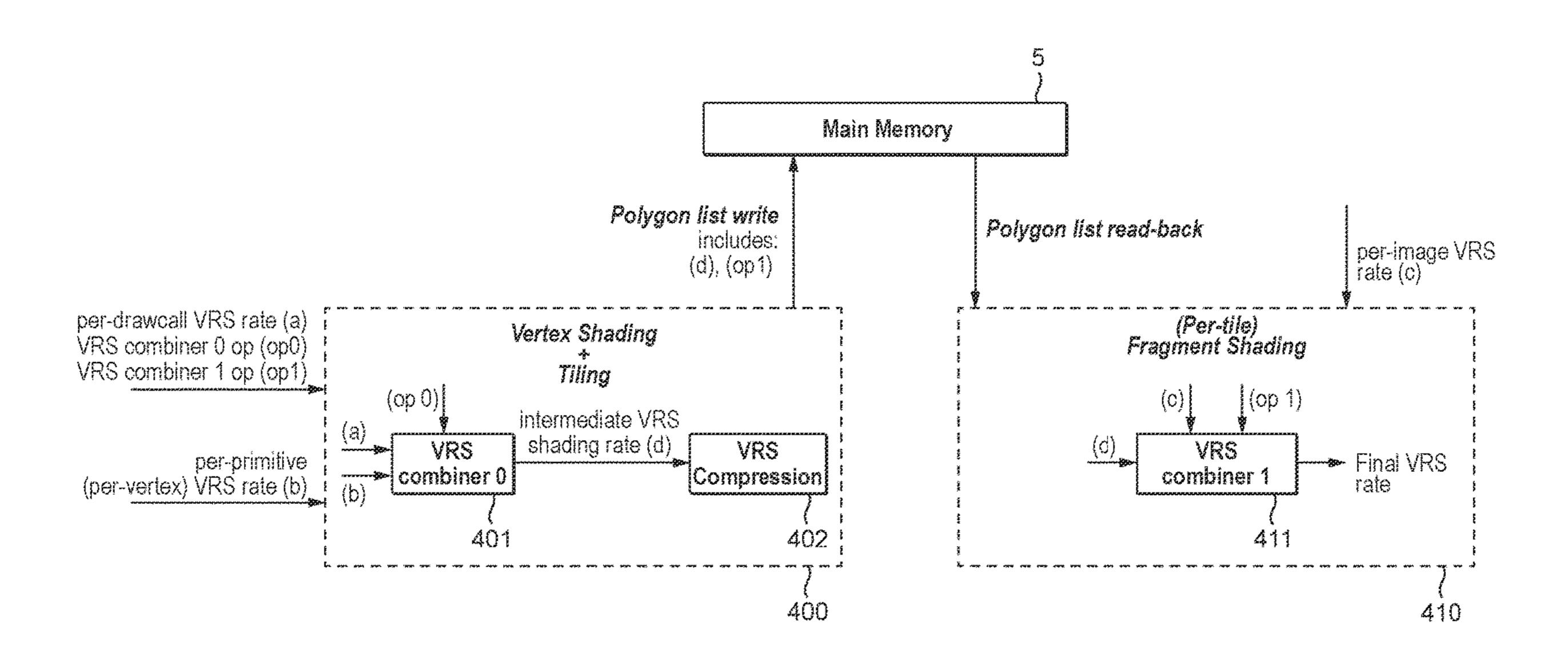

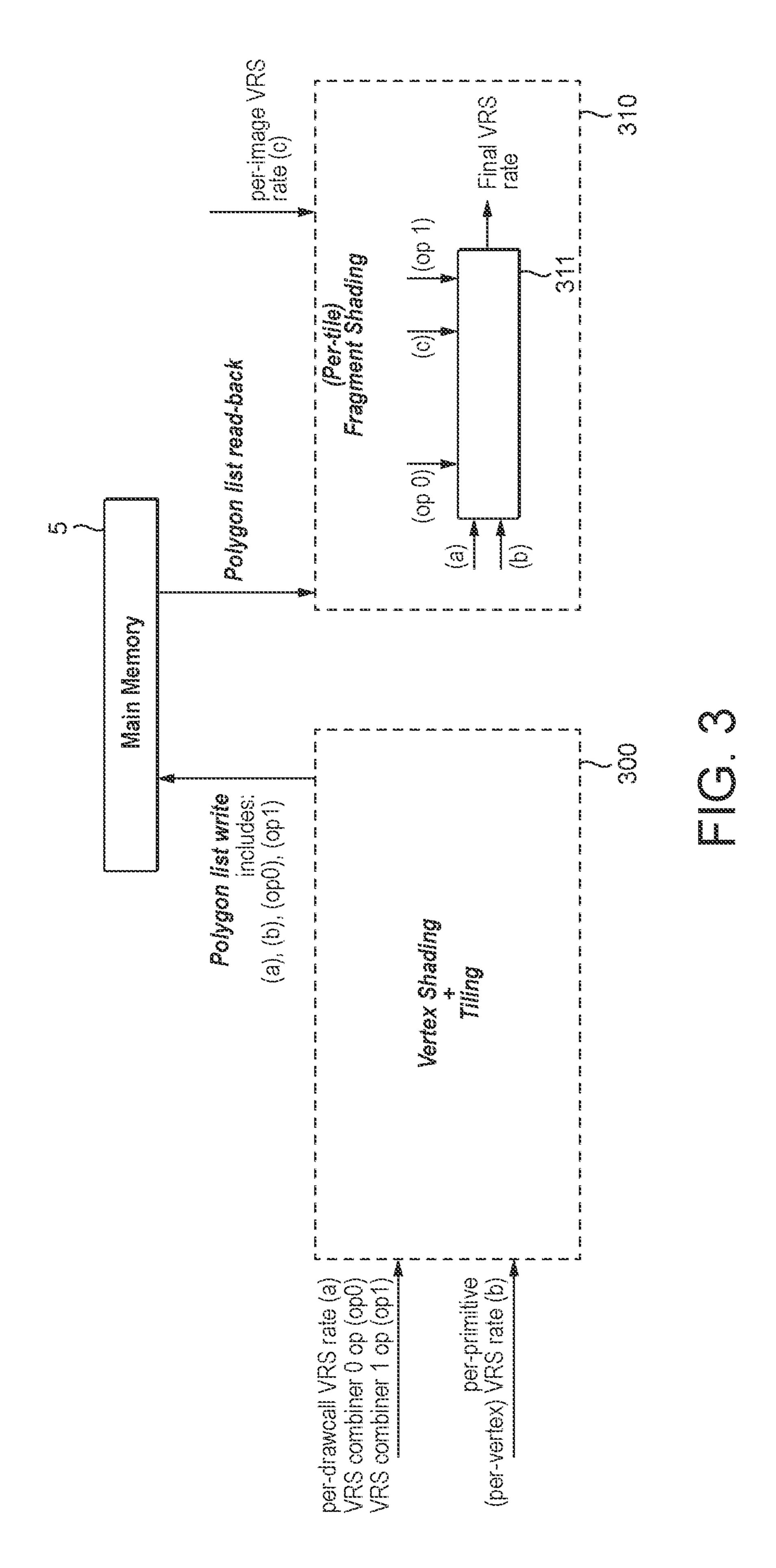

- FIG. 3 shows a graphics processing pipeline arrangement 50 that is not in accordance with the technology described herein;

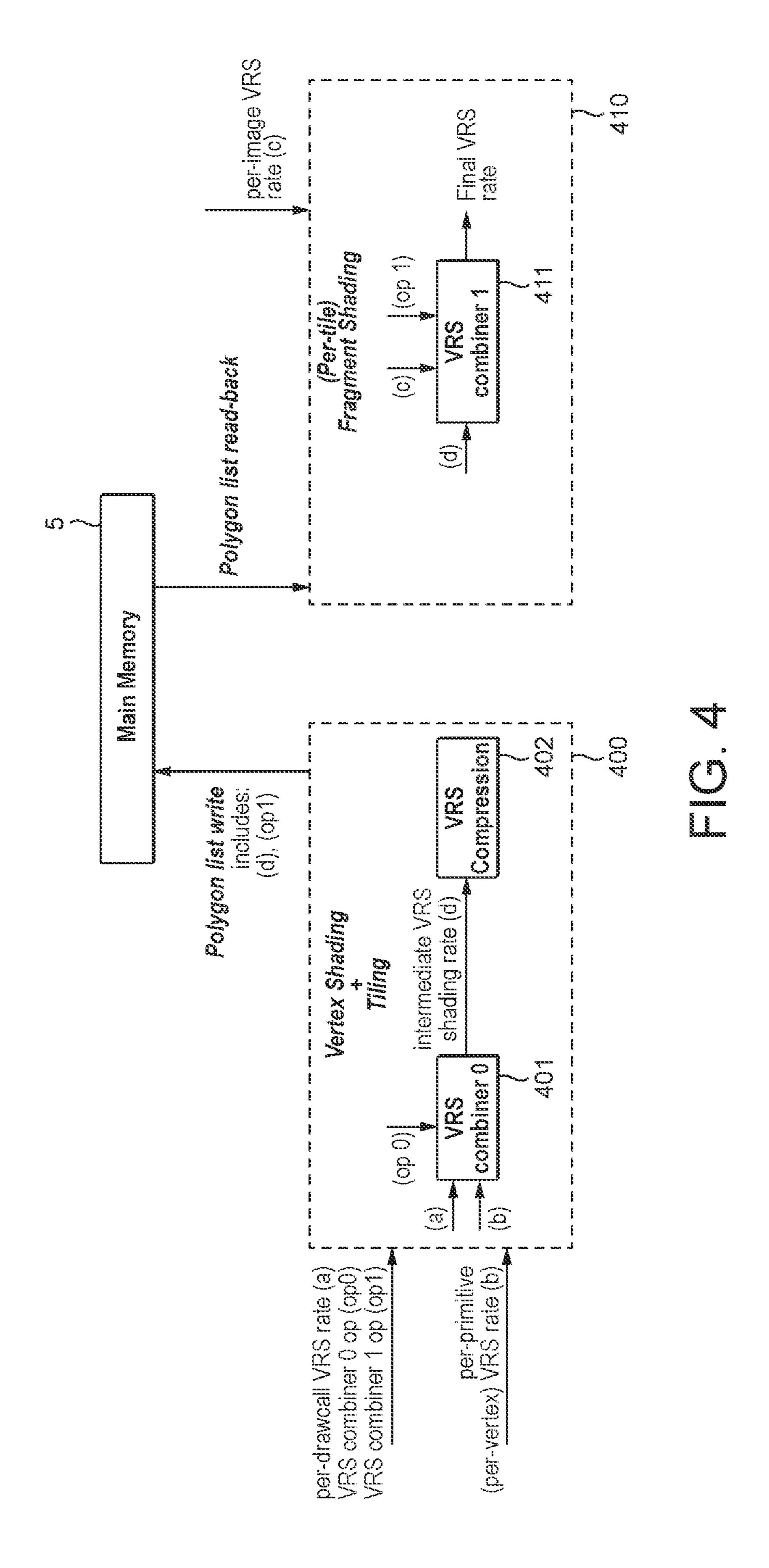

- FIG. 4 shows a graphics processing pipeline in accordance with an embodiment of the technology described herein;

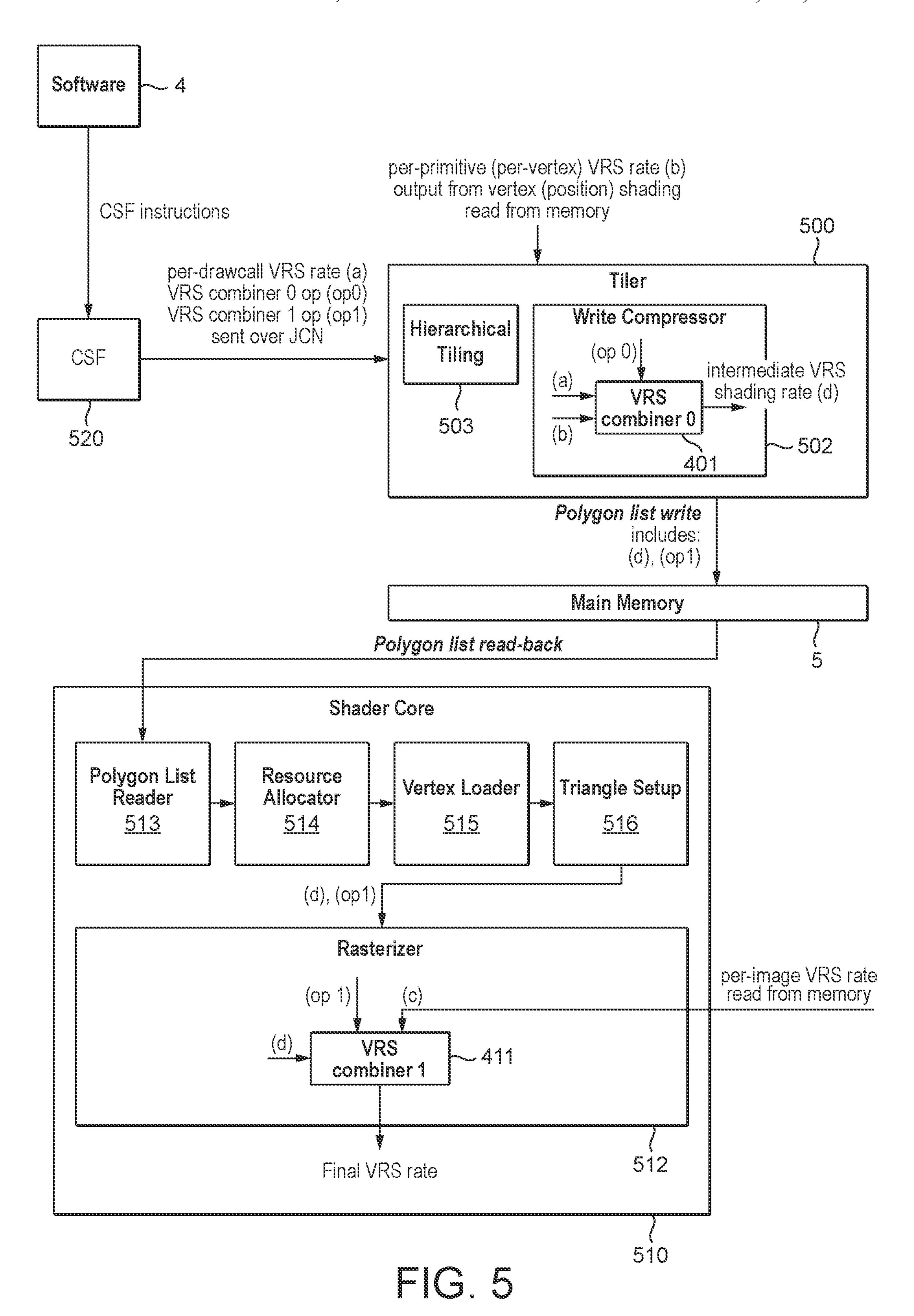

- FIG. 5 shows a graphics processing pipeline in accordance with an embodiment of the technology described herein; and

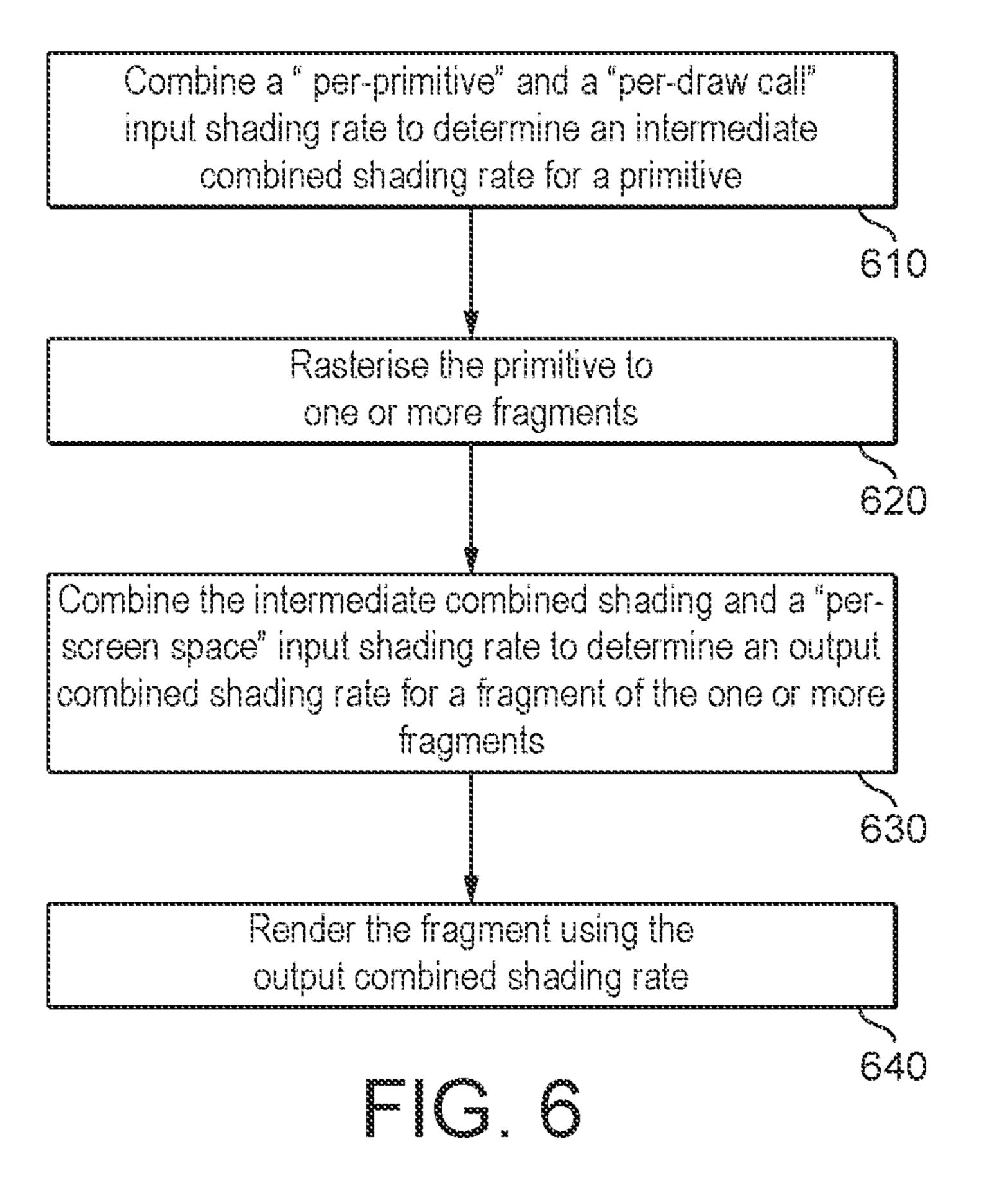

- FIG. 6 shows a process in accordance with an embodiment of the technology described herein.

Like reference numerals are used for like components where appropriate in the drawings.

# DETAILED DESCRIPTION

A first embodiment of the technology described herein comprises a method of operating a graphics processor that is

4

operable to execute a graphics processing pipeline that can generate a render output using different shading rates, wherein the graphics processing pipeline comprises one or more earlier processing stages followed by later processing stages, wherein the later processing stages comprise at least a rasteriser, and a renderer that is operable to render a render output using one or more output shading rates, wherein an output shading rate used by the renderer to render a render output may be determined using plural input shading rates defined for the render output;

the method comprising, when generating a render output for which a plurality of input shading rates have been defined:

combining at least a first input shading rate defined for the render output and a second input shading rate defined for the render output to determine a combined shading rate for the render output prior to the rasteriser stage of the graphics processing pipeline, and providing the determined combined shading rate to one or more of the later processing stages of the graphics processing pipeline;

using the determined combined shading rate when determining an output shading rate to be used by the renderer to render the render output; and

the renderer rendering at least some of the render output using the determined output shading rate.

A second embodiment of the technology described herein comprises a graphics processor that is operable to execute a graphics processing pipeline that can generate a render output using different shading rates, wherein the graphics processing pipeline comprises one or more earlier processing stages followed by later processing stages, wherein the later processing stages comprise at least a rasteriser, and a renderer that is operable to render a render output using one or more output shading rates, wherein an output shading rate used by the renderer to render a render output may be determined using plural input shading rates defined for the render output;

wherein the graphics processor comprises a combining circuit prior to the rasteriser stage of the graphics processing pipeline that is configured to combine at least a first input shading rate defined for a render output and a second input shading rate defined for the render output to determine a combined shading rate for the render output, and to cause the determined combined shading rate to be provided to one or more of the later processing stages of the graphics processing pipeline; and

wherein the renderer is operable to render at least some of a render output using an output shading rate determined using a combined shading rate determined by the combining circuit.

The technology described herein is concerned with arrangements in which a render output can be generated (rendered) using one or more of plural different possible ("output") shading rates, such as in the case of "variable rate shading" (VRS). That is, the technology described herein is concerned with arrangements in which the area of the render output for which a single colour is rendered (sampled) by the renderer can be one of plural different possibilities.

For example, and in an embodiment, when a relatively fine output shading rate is used, a single colour may be sampled by the renderer for an area of the render output corresponding to only a single pixel. When a coarser output shading rate is used, however, a single colour may be sampled by the renderer for an area of the render output corresponding to a block of plural pixels.

In the technology described herein, an "output" shading rate that the renderer uses, e.g. when rendering a primitive

for the render output, is based on a combination of plural "input" shading rates. For example, and as will be discussed in more detail below, the input shading rates for a particular primitive may (and in an embodiment do) include at least an input shading rate defined for the primitive itself (e.g. based on a provoking vertex that the primitive is associated with) (a "per-primitive" input shading rate), an input shading rate defined for (based on) a draw call that the primitive belongs to (a "per-draw call" input shading rate), and an input shading rate defined for (based on) a region of the render output within which the primitive falls (a "per-screen space" input shading rate). The input shading rates are combined to determine a single "final" combined output shading rate that is actually used by the renderer, e.g. when rendering the primitive in question.

In the technology described herein, at least some of the (at least first and second) input shading rates are combined into a single, combined shading rate prior to the rasteriser (and renderer) (i.e. prior to rasterisation).

The Applicants have recognised that while it may typically be the case that one or more input shading rates for a primitive (such as a "per-screen space" shading rate) are determined after (or during) rasterisation of that primitive, such that all of the input shading rates that are to be combined to determine a "final", output shading rate for the primitive can only be guaranteed to be available following rasterisation of the primitive, other input shading rates for the primitive (such as a "per-primitive" shading rate and a "per-draw call" shading rate) may be available prior to rasterisation of the primitive.

This means that it is possible to combine at least some of the input shading rates into a single, e.g. "intermediate" combined shading rate prior to rasterisation. This (e.g. "intermediate") combined shading rate can then be, and is, provided to later processing stages of the graphics processing pipeline (e.g. the rasteriser and/or the renderer), e.g. and in an embodiment, instead of the individual input shading rates that were combined to determine the (e.g. "intermediate") combined shading rate.

As will be discussed in more detail below, any other input 40 shading rates that are determined after (or during) rasterisation, such as a "per-screen space" shading rate, can then be, and in an embodiment are, combined with the "intermediate" combined shading rate following (or during) rasterisation to determine the output shading rate to be used by the 45 renderer.

The Applicants have recognised that combining at least some input shading rates into a single, (e.g. "intermediate") combined shading rate prior to rasterisation, and then propagating the single (e.g. "intermediate") combined shading 50 rate through the graphics processing pipeline in this manner can reduce bandwidth, hardware and energy requirements, e.g. as compared to propagating each of the individual input shading rates through the pipeline and, e.g. only combining them once all of the input shading rates can be guaranteed 55 to be available, i.e. after rasterisation.

The technology described herein can thus provide a graphics processor having reduced bandwidth and hardware requirements and energy consumption. This is generally advantageous, but may be particularly advantageous in 60 block of 2×2 fine pixels. The set of plural possi devices, e.g. mobile phones and tablets.

It will be appreciated, therefore, that the technology described herein provides an improved graphics processor.

The render output generated by the graphics processing 65 sible. pipeline of the technology described herein may comprise any suitable render output, such as frame for display, or rate render output.

6

render-to-texture output, etc. In an embodiment, the render output is an output frame in a sequence of plural output frames that the graphics processing pipeline generates. In this case, each output frame is in an embodiment generated in the manner of the technology described herein.

The render output will typically comprise an array of data elements (sampling points) (e.g. pixels), for each of which appropriate render output data (e.g. a set of colour value data) is generated. The data may comprise, for example, a set of red, green and blue, RGB values and a transparency (alpha, a) value.

The render output may be generated for display on a display device having a display or output comprising a plurality of pixels, such as a computer monitor or a printer.

The render output may accordingly include, for each output pixel of the display device, a set of one or more corresponding data elements (sampling points). Each such set of data element (sampling points) may include only a single data element (sampling point). Alternatively, each set of data elements may include plural data elements (sampling points). In this latter case, each sampling point may effectively correspond to a part of a pixel (e.g. a sub-pixel) of the display device, and the render output may be subjected to an appropriate downsampling operation to generate the output pixel values for displaying the final image on the display device.

The render output should be, and in an embodiment is, rendered by the renderer (circuit) using one or more of plural possible different "output" shading rates. Thus, there is in an embodiment a set of plural possible shading rates that the graphics processor supports and can use.

Correspondingly, there should be, and in an embodiment is, a set of plural possible different sized render output areas for which a single set of colour value data (a single colour) can be sampled (rendered) by the renderer. Accordingly, the renderer rendering at least some of the render output in an embodiment comprises the renderer sampling one or more sets of colour value data (colours), wherein the area of the render output for which each set of colour value data (colour) is sampled has a size in accordance with the respective output shading rate used.

The smallest render output area in the set of plural possible render output areas may be referred to as a "fine pixel", and the other, larger render output areas may be referred to as "coarse pixels". Each "fine pixel" may be the same size and location as a pixel of the output display device. Alternatively, each "fine pixel" may correspond to less than one pixel of the output display device, for example where downsampling is to be applied.

The area of each possible "coarse pixel" in an embodiment corresponds to a block of plural "fine pixels".

The different possible shading rates may be referred to in terms of the number of fine pixels that the shading rate corresponds to. For example, a 1×1 shading rate may signify the finest possible shading mode in which a single set of colour value data is sampled for an area of the render output corresponding to a single fine pixel, whereas a 2×2 shading rate may signify that a single set of colour value data is sampled for an area of the render output corresponding to a block of 2×2 fine pixels.

The set of plural possible shading rates can include any suitable shading rates. In an embodiment, the set of plural possible shading rates includes 1×1, 1×2, 2×1, 2×2, 2×4, 4×2 and 4×4 shading rates. Other shading rates would be possible.

It will be appreciated here that the same output shading rate may be used by the renderer to render all of a render

output, or different output shading rates may be used by the renderer to render different regions of a render output.

The render output should be, and in an embodiment is, generated by the graphics processing pipeline processing a set of primitives for the render output. To do this, the 5 rasteriser (circuit) should, and in an embodiment does, rasterise primitives of the set of primitives (to fragments), and the renderer (circuit) should, and in an embodiment does, render (samples colour values for) (fragments generated from) primitives of the set of primitives.

Thus, the first input shading rate, second input shading rate and combined shading rate are in an embodiment shading rates associated with (for) a particular primitive, and the renderer rendering at least some of the render output in an embodiment comprises the renderer rendering (sampling one or more sets of colour value data (colours) for) (one or more fragments generate from) that primitive. In an embodiment, a respective combined shading rate is determined (by the combining circuit) for each of one or more (fragments generated from) primitives of the set of primitives, and the renderer renders such a (fragment generated from a) primitive using a respective output shading rate determined using the respective combined shading rate.

As discussed above, an "output" shading rate that is used by the renderer when rendering the render output should be, 25 and in an embodiment is, based on a combination of a set of "input" shading rates that includes at least a (the) first input shading rate and a (the) second input shading rate. An output shading rate that is used by the renderer may be the same as, or different to, any of the input shading rates that are 30 combined to determine that output shading rate.

An input shading rate can be any suitable shading rate that can be combined with other input shading rate(s) to determine an output shading rate to be used by the renderer (for a particular primitive or fragment). In an embodiment, an 35 input shading rate is a shading rate that is specified by an application that the render output is being generated for, and in an embodiment that the graphics processor (pipeline) can determine directly (i.e. without combining shading rates) from commands and data issued to it (e.g. by a driver for the 40 graphics processor).

The arrangement is in an embodiment such that plural input shading rates are specified (by the application) based on different factors, such that plural input shading rates apply to the same primitive (or fragment), and so are 45 combined (by the graphics processor (pipeline)) to determine a single output shading rate for use by the renderer when rendering that primitive (or fragment). Thus the input shading rates that are combined (including the first and second input shading rates) to determine a combined shading rate should be, and in an embodiment are, shading rates that are based on different factors, but which all apply to the same primitive (or fragment).

In an embodiment, an input shading rate is specified (by the application) for each of one or more vertices, with each 55 such input shading rate applying to any primitives that are associated with (comprise) the respective vertex. Thus, the set of input shading rates in an embodiment includes a "per-primitive" shading rate.

In an embodiment, an input shading rate is (additionally or alternatively) specified (by the application) for each of one or more draw calls, with each such input shading rate applying to any primitives that belong to the respective draw call. Thus, the set of input shading rates in an embodiment includes a "per-draw call" shading rate.

In an embodiment, an input shading rate is (additionally or alternatively) specified (by the application) for each of

8

one or more regions of the render output, with each such input shading rate applying to any primitives (or fragments) that appear within the respective render output region. Thus, the set of input shading rates in an embodiment includes a "per-screen space" shading rate.

Thus, in an embodiment, the graphics processor (pipeline) determines an output shading rate that the renderer uses when rendering a (each) primitive (or fragment) by combining (from) a "per-primitive" shading rate, a "per-draw call" shading rate and a "per-screen space" shading rate that apply to the (respective) primitive (or fragment).

However, other input shading rates would be possible. For example, a "per-depth" shading rate could (additionally or alternatively) be specified for each of one or more Z depth ranges, with each such input shading rate applying to any primitives (or fragments) having a Z depth within the respective Z depth range, e.g. as described in U.S. patent application Ser. No. 16/897,160, the entire contents of which is hereby incorporated by reference.

In the technology described herein, at least first and second input shading rates are combined prior to the raster-iser stage to determine a combined shading rate. These input shading rates (i.e. at least the first and second input shading rates) should thus be, and in an embodiment are, input shading rates that can be determined (directly) for a primitive prior to the primitive being rasterised.

In this regard, as mentioned above, the Applicants have recognised that some "input" shading rates may be available (determinable) prior to rasterisation, whereas the graphics processor (pipeline) may determine other "input" shading rates based on information determined by the rasterisation process, such that these latter "input" shading rates may not be available prior to rasterisation.

For example, in the case of a set of "per-screen space" input shading rates being specified, with each such "per-screen space" input shading rate applying to any primitives (or fragments) that appear within a corresponding region of the render output, the "per-screen space" input shading rate that applies to a particular primitive will depend on the position in the render output at which the primitive appears, and the position in the render output at which the primitive appears will be determined by rasterising the primitive. Thus, a "per-screen space" input shading rate will typically not be available prior to rasterisation. Similarly, a "per-depth" input shading rate may typically not be available prior to rasterisation.

In contrast, "per-primitive" and "per-draw call" input shading rates will typically not depend on information determined by the rasterisation process, and thus will typically be available (determinable) prior to rasterisation.

Thus, in an embodiment, the first input shading rate is a "per-primitive" shading rate, and the second input shading rate is a "per-draw call" shading rate.

Where the set of input shading rates includes only shading rates that are available prior to rasterisation (such as only the first and second input shading rates), then all of the input shading rates may be, and in an embodiment are, combined prior to rasterisation (by the combining circuit). Thus, in an embodiment, the combined shading rate that is determined by (the combining circuit) combining at least the first and second input shading rates is the output shading rate that is used by the renderer. Thus, using the determined combined shading rate when determining an output shading rate to be used by the renderer to render the render output in an embodiment comprises using the determined combined shading rate as the output shading rate.

However, as mentioned above, where the set of input shading rates includes one or more input shading rates that are not available prior to rasterisation, then those one or more input shading rates may be, and in an embodiment are, combined with the other input shading rates after (or during) rasterisation.

In one such embodiment, the arrangement is such that all input shading rates that are available prior to rasterisation are combined to determine an "intermediate" combined shading rate prior to rasterisation (in an embodiment by the 10 (first) combining circuit), and then all of the input shading rates that are not available prior to rasterisation are combined with this "intermediate" combined shading rate after (or during) rasterisation (in an embodiment by a second combining circuit) to determine the "final" combined output 15 shading rate that is actually used by the renderer.

In this regard, the Applicants have recognised that since it is possible to combine first, second and third input shading rates to determine an output shading rate by performing a first "partial" combining operation that combines the first 20 and second input shading rates into an "intermediate" combined shading rate, and then performing a second "partial" combining operation that combines the "intermediate" combined shading rate with the third (or more) input shading rate to determine the "final" combined output shading rate, it is 25 possible to perform the first and second "partial" combining operations at different processing stages of the graphics processing pipeline. Embodiments of the technology described herein exploit this by performing the first "partial" combining operation prior to the rasteriser stage, and the 30 second "partial" combining operation at or after the rasteriser stage.

Thus, in an embodiment, the combined shading rate that is determined by (the (first) combining circuit) combining at least the first and second input shading rates represents an 35 "intermediate" combined shading rate, which "intermediate" combined shading rate is then combined with at least a third input shading rate after (or during) rasterisation to determine a second combined shading rate that is in an embodiment the "final" output shading rate that is actually 40 used by the renderer.

Thus, using the determined combined shading rate when determining an output shading rate to be used by the renderer to render the render output in an embodiment comprises combining at least the determined combined 45 shading rate and a third input shading rate defined for the render output to determine the output shading rate at or after the rasteriser stage of the graphics processing pipeline.

In an embodiment, the third input shading rate is a "per-screen space" shading rate.

It is believed that the idea of combining at least first, second and third shading rates by performing first and second "partial" combining operations at different processing stages of the graphics processing pipeline in this manner may be novel and inventive in its own right.

Thus, another embodiment of the technology described herein comprises a method of operating a graphics processor that is operable to execute a graphics processing pipeline that can generate a render output using different shading rates, wherein the graphics processing pipeline comprises one or more earlier processing stages followed by one or more later processing stages, wherein the one or more later processing stages comprise at least a renderer that is operable to render a render output using one or more output shading rates, wherein an output shading rate used by the 65 renderer to render a render output may be determined using plural input shading rates defined for the render output;

10

the method comprising, when generating a render output for which a plurality of input shading rates have been defined:

combining at least a first input shading rate defined for the render output and a second input shading rate defined for the render output to determine an intermediate combined shading rate for the render output prior to the one or more later processing stages of the graphics processing pipeline, and providing the determined intermediate combined shading rate to one or more of the one or more later processing stages of the graphics processing pipeline;

combining at least the determined intermediate combined shading rate and a third input shading rate defined for the render output to determine an output shading rate for the render output at or after a processing stage of the one or more later processing stages of the graphics processing pipeline; and

the renderer rendering at least some of the render output using the determined output shading rate.

Another embodiment of the technology described herein comprises a graphics processor that is operable to execute a graphics processing pipeline that can generate a render output using different shading rates, wherein the graphics processing pipeline comprises one or more earlier processing stages followed by one or more later processing stages, wherein the one or more later processing stages comprise at least a renderer that is operable to render a render output using one or more output shading rates, wherein an output shading rate used by the renderer to render a render output may be determined using plural input shading rates defined for the render output;

wherein the graphics processor comprises:

a first combining circuit prior to the one or more later processing stages of the graphics processing pipeline that is configured to combine at least a first input shading rate defined for a render output and a second input shading rate defined for the render output to determine an intermediate combined shading rate for the render output, and to cause the determined intermediate combined shading rate to be provided to one or more of the one or more later processing stages of the graphics processing pipeline; and

a second combining circuit at or after a processing stage of the one or more later processing stages of the graphics processing pipeline that is configured to combine at least an intermediate combined shading rate determined by the first combining circuit for a render output and a third input shading rate defined for the render output to determine an output shading rate for the render output;

wherein the renderer is operable to render at least some of a render output using an output shading rate determined by the second combining circuit.

These embodiments can include, as appropriate, any one or more or all of the optional features described herein. For example, the first input shading rate may be a "per-primitive" shading rate, the second input shading rate may be a "per-draw call" shading rate, and the third input shading rate may be a "per-screen space" shading rate. Moreover, the later processing stages may comprise a rasteriser. However, a graphics processing pipeline that does not necessarily include a rasteriser, such as a ray tracing graphics processing pipeline, is also contemplated.

In an embodiment, shading rates are combined into a single combined shading rate according to one or more combining functions that are in an embodiment specified by the application that the render output is being generated for. A combining function may combine different shading rates by, for example, selecting one of the shading rates, such as

the finest or coarsest shading rate, or by determining an average shading rate. In an embodiment, an input and/or an output of a combining function is "sanitized", i.e. mapped to a, e.g. the nearest, shading rate supported by the graphics processor.

Thus, in an embodiment, the at least the first input shading rate and the second input shading rate are combined to determine the single (e.g. "intermediate") combined shading rate according to a (defined) combining function.

In an embodiment, a first combining function is specified 10 (by the application) for (and used when) combining the at least the first and second input shading rates to determine the "intermediate" combined shading rate, and a second combining function is specified (by the application) for (and used when) combining the at least the "intermediate" com- 15 bined shading rate and the third input shading rate to determine the output combined shading rate.

Once an (e.g. "intermediate") combined shading rate has been determined (prior to rasterisation) (by the combining circuit), the determined combined shading rate is provided 20 to one or more of the later processing stages (e.g. the rasteriser and/or renderer). It will be appreciated here that this means that the individual input shading rates that were combined to determine the (e.g. "intermediate") combined shading rate do not need to be provided to the later processing stage(s). Thus, the individual (including first and second) input shading rates that were combined to determine the (e.g. "intermediate") combined shading rate are in an embodiment not provided (other than provided) to the later processing stage(s).

Similarly, in an embodiment, the second combining function is in an embodiment provided to the later processing stage(s) (e.g. the rasteriser and/or renderer), but the first combining function is in an embodiment not provided (other provide a reduction in terms of bandwidth, hardware, and energy requirements.

The graphics processing pipeline that the graphics processor executes can include any suitable and desired processing stages for generating a (the) render output (e.g. 40) frame). Thus, the graphics processing pipeline can include, and in an embodiment does include, in addition to the rasteriser (stage) and/or renderer (stage), any one or one or more, and in an embodiment all, of the other processing stages that graphics processing pipelines normally include.

In an embodiment, the graphics processing pipeline comprises one or more vertex processing stages (circuits) that are operable to receive and process raw vertex data to generate transformed vertex data. In an embodiment, the graphics processing pipeline comprises, in an embodiment 50 (logically) after the one or more vertex processing stages, one or more primitive setup stages (circuits) that are operable to use transformed vertex data generated by the one or more vertex processing stages to setup primitives for rasterisation.

The rasteriser (circuit) is then in an embodiment (logically) after the one or more primitive setup stages (and the one or more vertex processing stages) in the graphics processing pipeline, and rasterises primitive setup for rasterisation by the one or more primitive setup stages to 60 generate fragments. Each fragment that is generated by the rasteriser should, and in an embodiment does, have associated with it a set of data elements (sampling points) of the render output, and may be used by the renderer to generate render output data for one or more of the data elements 65 (sampling points) of the set of data elements (sampling points) associated with the fragment.

The renderer (circuit) is thus in an embodiment (logically) after the rasteriser (and the one or more vertex processing stages and the one or more primitive setup stages) in the graphics processing pipeline, and renders fragments generated by the rasteriser. To do this, the renderer in an embodiment comprises one or more fragment processing stages.

The graphics processor (and pipeline) may be an immediate mode graphics processor (and pipeline). However, in an embodiment, the graphics processor (and pipeline) is a tile-based graphics processor (and pipeline). The graphics processor (and pipeline) thus in an embodiment generates the render output on a tile-by-tile basis. The render output (area) may thus be divided into plural rendering tiles for rendering purposes.

The tiles that the render output is divided into for rendering purposes can be any suitable and desired such tiles. The size and shape of the rendering tiles may normally be dictated by the tile configuration that the graphics processor is configured to use and handle.

The rendering tiles are in an embodiment all the same size and shape (i.e. regularly-sized and shaped tiles are in an embodiment used), although this is not essential. The tiles are in an embodiment rectangular, and in an embodiment square. The size and number of tiles can be selected as desired. In an embodiment, each tile is 16×16, or 32×32 data elements (e.g. fragments or pixels) in size (with the render output then being divided into however many such tiles as are required for the render output size and shape that is being used).

To facilitate tile-based graphics processing, the graphics processor in an embodiment comprises one or more tile buffers that store rendered data for a rendering tile being rendered by the graphics processing pipeline, until the graphics processing pipeline completes the rendering of the than provided) to the later processing stage(s). This can 35 rendering tile. The tile buffer should be, and in an embodiment is, provided local to (i.e. on the same chip as) the graphics processor, for example, and in an embodiment, as part of RAM that is located on (local to) the graphics processor (chip). The tile buffer may accordingly have a fixed storage capacity, for example corresponding to the data (e.g. for an array or arrays of sample values) that the graphics processor needs to store for (only) a single rendering tile until the rendering of that tile is completed.

> Moreover, in an embodiment, the graphics processing pipeline comprises a primitive list preparing stage (circuit) (a "tiler") that prepares primitive lists for respective regions of the render output. The regions of the render output that the primitive list preparing stage (circuit) ("tiler") can prepare primitive lists for may correspond e.g. to single rendering tiles, or to sets of plural rendering tiles (e.g. in the case of "hierarchical tiling" arrangements).

In this case, the primitive list preparing stage in an embodiment receives transformed vertex data generated by the one or more vertex processing stages of the graphics 55 processing pipeline, and uses the transformed vertex data to prepare primitive lists.

In an embodiment, the primitive list preparing stage (circuit) is followed by a primitive list reading stage (circuit) in the graphics processing pipeline that reads primitives listed for a rendering tile by the primitive list preparing stage (circuit) ("tiler"), and passes those read primitives to subsequent stages of the graphics processing pipeline for processing, which subsequent stages of the graphics processing pipeline in an embodiment comprise the one or more primitive setup stages.

Thus, the primitive list preparing stage (circuit) and primitive list reading stage (circuit) are in an embodiment

(logically) between the one of more vertex processing stages (circuits) and the one or more primitive setup stages (circuits) in the graphics processing pipeline, and primitives read by the primitive list reading stage are in an embodiment setup up for rasterisation by the one or more primitive setup stages, and are then rasterised to fragments by the rasteriser, etc.

Thus, the one or more earlier processing stages of the graphics processing pipeline (that are prior to the rasteriser stage) in an embodiment comprise one or more, and in an embodiment all, of: one or more vertex processing stages; a primitive list preparing stage; a primitive list reading stage; and one or more primitive setup stages. The later processing comprise the rasteriser and the renderer, which in an embodiment comprises one or more fragment processing stages.

It will be appreciated here that a later processing stage refers to a processing stage of the graphics processing 20 pipeline that may perform its respective processing operation(s) (in respect of a primitive) after an earlier processing stage, and thus may use a processing result generated by an earlier processing stage.

As discussed above, in the technology described herein at 25 least first and second input shading rates are combined to determine a combined shading rate (prior to the rasteriser stage of the graphics processing pipeline). This (first) combining operation may be performed by any suitable and desired stage or component of the graphics pipeline or 30 processor.

For example, the one or more earlier processing stages of the graphics processing pipeline (that are prior to the rasteriser stage) may comprise a "standalone" (first) combining stage (circuit) that performs the (first) combining operation 35 (prior to the rasteriser stage). Alternatively, one of the earlier processing stages of the graphics processing pipeline (prior to the rasteriser stage) may perform the (first) combining operation, e.g. in addition to the other processing operation(s) that the processing stage is operable to perform. 40 For example, a vertex processing stage or primitive setup stage of the graphics processing pipeline may combine the first and second input shading rates to determine a combined shading rate (prior to the rasteriser stage).

In an embodiment (where the graphics processing pipe- 45) line is tile-based), the primitive list preparing stage (circuit) (the "tiler") combines at least the first input shading rate and the second input shading rate to determine the (e.g. "intermediate") combined shading rate. In an embodiment, the primitive list preparing stage (circuit) comprises a (first) 50 combining circuit for this purpose.

In this regard, the Applicants have recognised that a primitive list preparing stage ("tiler") of a tile-based graphics processing pipeline may typically be the earliest processing stage of the pipeline where e.g. "per-primitive" and 55 "per-draw call" input shading rates for a primitive are available. As such, combining these input shading rates in the primitive list preparing stage ("tiler") can minimise the propagation of individual e.g. "per-primitive" and "per-draw call" shading rates through the pipeline, and thus minimise 60 bandwidth, hardware and energy requirements.

As also discussed above, in embodiments of the technology described herein at least a combined shading rate (determined prior to the rasterisation stage) and a third shading rate are combined to determine an output shading 65 rate (at or after the rasteriser stage of the graphics processing pipeline). This (second) combining operation may be per14

formed by any suitable and desired stage or component of the graphics pipeline or processor.

For example, the later processing stages of the graphics processing pipeline may comprise a "standalone" second combining stage (circuit) that performs the (second) combining operation (at or after the rasteriser stage). Alternatively, one of the later processing stages of the graphics processing pipeline may perform the (second) combining operation, e.g. in addition to the other processing operation(s) that the processing stage is operable to perform. For example, a fragment processing stage of the renderer may combine the determined combined shading rate and third input shading rate to determine an output shading rate.

In an embodiment, the rasteriser (circuit) combines at stages of the graphics processing pipeline in an embodiment 15 least a combined shading rate (determined prior to the rasterisation stage) and a third input shading rate to determine the output (combined) shading rate. In an embodiment, the rasteriser (circuit) comprises a second combining circuit for this purpose (and the combining circuit that combines the first and second input shading rates (prior to the rasteriser stage) is in an embodiment a (in an embodiment different) first combining circuit).

> In this regard, the Applicants have recognised that a rasteriser of a graphics processing pipeline may typically be the earliest processing stage of the pipeline where e.g. "per-screen space" input shading rates are available. As such, combining a e.g. "per-screen space" input shading rate in the rasteriser can minimise the propagation of individual e.g. "per-screen space" shading rates through the pipeline, and thus minimise bandwidth, hardware and energy requirements.

> As also discussed above, in the technology described herein a combined shading rate (determined (by an earlier processing stage) prior to the rasterisation stage) is provided to a later processing stage. Where the determined combined shading rate is used as the output shading rate, the determined combined shading rate should be, and in an embodiment is, provided to the renderer so that the renderer can then use that output shading rate when rendering the render output.

> Where the determined combined shading rate is combined with at least a third input shading rate to determine the output shading rate, the determined combined shading rate should be, and in an embodiment is, provided to the later processing stage that performs the (second) combining operation. Thus, the combined shading rate (determined prior to the rasteriser stage) is in an embodiment provided to the (second combining circuit of the) rasteriser. In this case, the output combined shading rate determined by the (second combining circuit of the) rasteriser should be, and in an embodiment is, provided to the renderer so that the renderer can then use that output shading rate when rendering the render output.

> As also discussed above, a second combing function may also be, and is in an embodiment, provided to the later processing stage (in an embodiment the (second combining circuit of the) rasteriser) that performs the (second) combining operation (at or after the rasterisation stage).

> A (combined) shading rate and/or a (second) combining function can be provided to a later processing stage in any suitable and desired manner. In an embodiment, shading rate information propagates from the earlier "originating" processing stage to the later "receiving" processing stage through any "intermediate" processing stages that are (logically) between the originating and receiving processing stages in the graphics processing pipeline. This may involve, for example, shading rate information propagating from a

processing stage to the next by the processing stage writing shading rate information to storage (such as to one or more registers) that the next processing stage can access, and the next processing stage reading that shading rate information (and writing the shading rate information to storage), and so on.

In an embodiment, any such "intermediate" processing stage will, as well as propagate shading rate information for a primitive to the next processing stage, perform a respective processing operation in respect of the primitive, which processing operation in an embodiment does not use the shading rate information.

Thus, in an embodiment, the graphics processing pipeline comprises, (logically) between the (first) combining circuit (e.g. earlier processing stage, in an embodiment the primitive list preparing stage) that determines the ("intermediate") combined shading rate and the (later) second combining circuit (e.g. later processing stage, in an embodiment the rasteriser) that determines the output combined shading rate, 20 one or more, and in an embodiment plural, intermediate processing stages that are each operable to perform a respective processing operation which does not use the ("intermediate") combined shading rate information, and in an embodiment to propagate the ("intermediate") combined 25 shading rate information to the next processing stage.

In embodiments where the combined shading rate is determined by (the "originating" processing stage is) the primitive list preparing stage (circuit), providing the determined combined shading rate (and optionally the second 30 combining function) in an embodiment involves the primitive list preparing stage (the "tiler") writing information indicative of the (e.g. "intermediate") combined shading rate (and optionally the second combining function) to one or reading stage then reads this information when reading primitive lists, and the information propagates to subsequent processing stages (including the rasteriser and/or renderer), e.g. as discussed above.

The primitive list preparing stage (circuit) (the "tiler") 40 could write shading rate indicative information for each and every primitive listed in the primitive lists. However, in an embodiment, the primitive list preparing stage (circuit) (the "tiler") writes shading rate indicative information for a primitive to a primitive list only when the shading rate for 45 that primitive is different to the shading rate for a previous primitive written to that primitive list. That is, in an embodiment, the primitive list preparing stage ("tiler") only writes information indicative of the shading rate to a primitive list when there is a change of shading rate.

Thus, the primitive list preparing stage (circuit) (the "tiler") in an embodiment comprises a primitive list writing circuit that is configured to determine whether a shading rate for a current primitive to be written to a primitive list is different to a shading rate for a previous primitive written to 55 the primitive list, and to, when it is determined that a shading rate for a current primitive to be written to a primitive list is different to a shading rate for a previous primitive written to the primitive list, write information indicative of the shading rate for the current primitive to the primitive list.

In an embodiment, the primitive list writing circuit is configured to, when it is not determined that a shading rate for a current primitive to be written to a primitive list is different to a shading rate for a previous primitive written to the primitive list (when it is determined that the shading rate 65 for the current primitive is the same as the shading rate for the previous primitive), not write (omit writing) information

**16**

indicative of the shading rate for the current primitive to the primitive list. This can further reduce energy, hardware and bandwidth requirements.

The shading rate indicative information that the primitive list preparing stage (circuit) (the "tiler") writes to one or more primitive lists could comprise the actual determined (e.g. "intermediate") combined shading rate (and optionally the second combining function). However, in an embodiment, the shading rate indicative information comprises a 10 compressed representation of a determined (e.g. "intermediate") combined shading rate (and optionally a second combining function). This can further reduce bandwidth, hardware and energy requirements.

Thus, in an embodiment, a compressed representation of 15 the (e.g. "intermediate") combined shading rate (and optionally the second combining function) is determined (prior to the rasterisation stage), and the compressed representation of the (e.g. "intermediate") combined shading rate (and optionally the second combining function) is provided to the later processing stage(s) (in an embodiment instead of the actual "uncompressed" combined shading rate).

To facilitate this, the graphics processor in an embodiment comprises a shading rate compressing circuit that is configured to compress a (combined) shading rate (and optionally a combining function) to determine a compressed representation of the (combined) shading rate (and optionally the combining function) (prior to the rasteriser stage of the graphics processing pipeline), and in an embodiment to provide the compressed representation of the (combined) shading rate to the later processing stage(s). In an embodiment, the shading rate compressing circuit compresses a combined shading rate determined by the (first) combining circuit. In an embodiment, the primitive list preparing stage (circuit) (the "tiler") comprises the shading rate compressing more primitive lists. In an embodiment, the primitive list 35 circuit, in an embodiment as well as the (first) combining circuit.

> Correspondingly, the graphics processor in an embodiment comprises a shading rate decompressing circuit that is configured to decompress a compressed representation of a (combined) shading rate (and optionally a second combining function) to determine the (combined) shading rate (and optionally the combining function) (at or after the rasteriser stage of the graphics processing pipeline). In an embodiment, the rasteriser (circuit) or (a fragment processing stage of the) renderer (circuit) comprises the shading rate decompressing circuit, in an embodiment as well as the second combining circuit.

A compressed representation of a (combined) shading rate can be provided in any suitable form. In an embodiment, each shading rate of the set of plural possible shading rates that the graphics processor supports is encoded as a respective bit pattern of a set of bits. A further bit pattern of the set of bits may be used to encode the case where "variable rate shading" (VRS) is disabled.

Similarly, a compressed representation of a (second) combing function can be provided in any suitable form. In an embodiment, each possible combing function is encoded as a respective bit pattern of a set of bits. In an embodiment, a further bit pattern of the set of bits that encodes a (second) 60 combing function is used to encode the case where "variable rate shading" (VRS) is disabled.

Thus, in an embodiment, shading rate indicative information written by the primitive list preparing stage (circuit) can indicate that "variable rate shading" (VRS) is disabled. In this case, the primitive list preparing stage (circuit) is in an embodiment configured to, when "variable rate shading" (VRS) is disabled, not write (omit writing) information

indicative of individual shading rates (and (only) write information that indicates that "variable rate shading" (VRS) is disabled), and the primitive list reading stage (circuit) is in an embodiment configured to, in response to reading shading rate indicative information that indicates that "variable rate shading" (VRS) is disabled, provide information to subsequent processing stages of the graphics processing pipeline that indicates that the finest possible shading rate (1×1) should be used (as an "output" shading rate). This arrangement can reduce the amount of information that is 10 written and read, and thus bandwidth requirements and energy consumption, when "variable rate shading" (VRS) is disabled.

Once an "output" shading rate has been determined (from plural "input" shading rates), the renderer should, and in an 15 embodiment does, use that output shading rate when rendering a primitive for the render output. This should, and in an embodiment does, have the effect that a greater number of colours are sampled by the renderer when a finer output shading rate is determined, as compared to when a coarser 20 output shading rate is determined. This can be achieved in any suitable and desired manner.

For example, the rasteriser could rasterise primitives into fragments based on shading rate, such that the area of the render output that a fragment generated by the rasteriser 25 corresponds to varies according to shading rate. Thus, in an embodiment, the rasteriser rasterises a primitive according to the output shading rate. For example, the rasteriser could generate fragments that correspond to larger areas of the render output when a coarser output shading rate is used, and 30 generate fragments that correspond to smaller areas of the render output when a finer output shading rate is used. The renderer may then sample a single set of colour value data (a single colour) for each so-generated fragment. This will then have the effect that a greater number of fragments are 35 generated, and so colours are sampled, when a finer shading rate is used, as compared to when a coarser shading rate is used.

In an embodiment, the rasteriser is operable to generate fragments in the "normal" manner. That is, in an embodi- 40 ment, the rasteriser (always) operates to generate fragments that each correspond to the same sized area of the render output, e.g. corresponding to one pixel or sub-pixel (a "fine pixel") irrespective of the output shading rate used. Fragments generated in this way are then in an embodiment 45 "combined" according to the output shading rate into sets of one or more fragments, and a single set of colour value data (a single colour) is sampled for each such set of one or more fragments. For example, and in an embodiment, a greater number of fragments are included in a set of fragments when 50 a coarser output shading rate is used, as compared to when a finer output shading rate is used. This will then have the effect that a greater number of colours are sampled when a finer shading rate is used, as compared to when a coarser shading rate is used.

Once a colour (set of colour value data) has been sampled by the renderer (circuit), the colour should be, and in an embodiment is, "broadcast" to each (e.g. covered) sampling position in the render output that the colour applies to. This should, and in an embodiment does, have the effect that a 60 single colour will be used for more sampling positions in the render output when a coarser output shading rate is used, as compared to when a finer output shading rate is used.

In an embodiment, render output data is "broadcast" to each corresponding sampling position in an output buffer, 65 e.g. the tile buffer. This may comprise writing render output data produced by the renderer (directly) to the output (e.g.

**18**

tile) buffer based on the output shading rate. Alternatively, where blending is required, a blender stage of the graphics processing pipeline may appropriately blend render output data newly generated by the renderer with render output data already stored in the output (e.g. tile) buffer based on the output shading rate.

The graphics processor may execute any suitable and desired graphics processing pipeline, and may and in an embodiment does, include any suitable and desired processing circuits, processing logic, components and elements for that purpose.

A (and each) processing stage (circuit) of the graphics processing pipeline (processor) can be implemented as desired, e.g. as a fixed function hardware unit (circuit) (i.e. a circuit that is dedicated to one or more functions that cannot be changed) or as a programmable processing circuit (that is programmed to perform the desired operation).

For example, the primitive list preparing stage (the "tiler") may be a fixed function tiling unit (circuit), and vertex and fragment processing stages may be executed by one or more programmable execution units (shader cores) of the graphics processor.

Thus, in an embodiment, the graphics processor comprises one or more programmable execution units (shader cores), which can, and in an embodiment do, each execute one or more of the processing stages of the graphics processing pipeline. Where the graphics processor comprises plural programmable execution units (shader cores), then different programmable execution units may execute the same or different processing stages of the graphics processing pipeline independently and at the same time (in parallel). Thus, plural instances of the graphics processing pipeline may be executed in parallel.

As will be appreciated by those skilled in the art, the graphics processor of the technology described herein may be part of an overall graphics processing system that includes, e.g., and in an embodiment, a host processor that, e.g., executes applications that require processing by the graphics processor. The host processor will send appropriate commands and data to the graphics processor to control it to perform graphics processing operations and to produce graphics processing output required by applications executing on the host processor. To facilitate this, the host processor should, and in an embodiment does, also execute a driver for the graphics processor and optionally a compiler or compilers for compiling (e.g. shader) programs to be executed by (e.g. a programmable execution unit of) the graphics processor.

The graphics processor may also comprise, and/or be in communication with, one or more memories and/or memory devices that store the data described herein, and/or the output data generated by the graphics processor, and/or store software (e.g. (shader) program) for performing the processes described herein. The graphics processor may also be in communication with a host microprocessor, and/or with a display for displaying images based on the data generated by the graphics processor.

The technology described herein can be used for all forms of output that a graphics processor (and processing pipeline) may be used to generate. For example, the graphics processing pipeline may generate frames for display, render-to-texture outputs, etc. The output data values from the processing are in an embodiment exported to external, e.g. main, memory, for storage and use, such as to a frame buffer for a display.

The technology described herein is applicable to any suitable form or configuration of graphics processor and

graphics processing system. It is particularly applicable to tile-based graphics processors and graphics processing systems. Thus in an embodiment, the graphics processor is a tile-based graphics processor (and pipeline).

In an embodiment, the various functions of the technology described herein are carried out on a single graphics processing platform that generates and outputs data (such as rendered fragment data that is, e.g., written to the frame buffer), for example for a display device.

The technology described herein can be implemented in any suitable system, such as a suitably configured microprocessor based system. In an embodiment, the technology described herein is implemented in a computer and/or micro-processor based system.

The technology described herein is in an embodiment implemented in a portable device, such as, and in an embodiment, a mobile phone or tablet.

The various functions of the technology described herein can be carried out in any desired and suitable manner. For 20 example, the functions of the technology described herein can be implemented in hardware or software, as desired. Thus, for example, the various functional elements, stages, and "means" of the technology described herein may comprise a suitable processor or processors, controller or con- 25 trollers, functional units, circuitry, circuit(s), processing logic, microprocessor arrangements, etc., that are operable to perform the various functions, etc., such as appropriately dedicated hardware elements (processing circuit(s)) and/or programmable hardware elements (processing circuit(s)) 30 that can be programmed to operate in the desired manner.

It should also be noted here that, as will be appreciated by those skilled in the art, the various functions, etc., of the technology described herein may be duplicated and/or carried out in parallel on a given processor. Equally, the various 35 processing stages may share processing circuit(s), etc., if desired.

It will also be appreciated by those skilled in the art that all of the described embodiments of the technology described herein can include, as appropriate, any one or 40 now be described with reference to the Figures. more or all of the optional features described herein.

The methods in accordance with the technology described herein may be implemented at least partially using software e.g. computer programs. It will thus be seen that when viewed from further embodiments the technology described 45 herein provides computer software specifically adapted to carry out the methods herein described when installed on a data processor, a computer program element comprising computer software code portions for performing the methods herein described when the program element is run on a 50 data processor, and a computer program comprising code adapted to perform all the steps of a method or of the methods herein described when the program is run on a data processing system. The data processing system may be a microprocessor, a programmable FPGA (Field Program- 55 mable Gate Array), etc.

The technology described herein also extends to a computer software carrier comprising such software which when used to operate a graphics processor, renderer or other system comprising a data processor causes in conjunction 60 with said data processor said processor, renderer or system to carry out the steps of the methods of the technology described herein. Such a computer software carrier could be a physical storage medium such as a ROM chip, CD ROM, RAM, flash memory, or disk, or could be a signal such as an 65 electronic signal over wires, an optical signal or a radio signal such as to a satellite or the like.

It will further be appreciated that not all steps of the methods of the technology described herein need be carried out by computer software and thus from a further broad embodiment the technology described herein provides computer software and such software installed on a computer software carrier for carrying out at least one of the steps of the methods set out herein.

The technology described herein may accordingly suitably be embodied as a computer program product for use with a computer system. Such an implementation may comprise a series of computer readable instructions fixed on a tangible, non-transitory medium, such as a computer readable medium, for example, diskette, CD ROM, ROM, RAM, flash memory, or hard disk. It could also comprise a 15 series of computer readable instructions transmittable to a computer system, via a modem or other interface device, over either a tangible medium, including but not limited to optical or analogue communications lines, or intangibly using wireless techniques, including but not limited to microwave, infrared or other transmission techniques. The series of computer readable instructions embodies all or part of the functionality previously described herein.

Those skilled in the art will appreciate that such computer readable instructions can be written in a number of programming languages for use with many computer architectures or operating systems. Further, such instructions may be stored using any memory technology, present or future, including but not limited to, semiconductor, magnetic, or optical, or transmitted using any communications technology, present or future, including but not limited to optical, infrared, or microwave. It is contemplated that such a computer program product may be distributed as a removable medium with accompanying printed or electronic documentation, for example, shrink wrapped software, preloaded with a computer system, for example, on a system ROM or fixed disk, or distributed from a server or electronic bulletin board over a network, for example, the Internet or World Wide Web.

An embodiment of the technology described herein will

When a computer graphics image is to be displayed, it is usually first defined as a series of primitives (polygons), which primitives are then rasterised into graphics fragments for graphics rendering in turn. These fragments are the processing entities that pass through the rendering process (the renderer). During a normal graphics rendering operation, the renderer typically samples a single colour (e.g. a set of red, green and blue, RGB values and a transparency (alpha, a) value) for each fragment so that the fragments can be displayed correctly. Once the fragments have fully traversed the renderer, then their associated colour values are stored in memory, ready for output, e.g. for display on a display device.

Each graphics fragment will typically be the same size and location as a "pixel" of the output display device. Alternatively, each graphics fragment may effectively correspond to less than one pixel of the output display device, for example where downsampling is to be applied.

Thus, the rendering process may typically produce a render output comprising an array of sampling points, for each of which appropriate data (e.g. a set of colour value data) is generated. For each output pixel, there is typically a set of one or more corresponding sampling points in the render output. Each such set of sampling points may include only one sampling point, or where downsampling is used, each set of sampling points may include plural sampling points.

As discussed above, "variable rate shading" (VRS) is a technique that allows different shading rates to be used to render a render output, i.e. such that a single colour (set of colour value data) can be sampled (rendered) for one of plural possible different sized areas in a render output. For 5 example, a single colour may be sampled for an area of the render output corresponding to only a single pixel, or a single colour may be sampled for an area of the render output corresponding to each pixel in a block of plural pixels.

Sampling (rendering) a single colour and applying it to plural sampling points (e.g. pixels) will reduce the processing effort required for those sampling points, as compared to sampling an individual colour for each sampling point, but will usually come at the expense of reduced image quality. 15

In "variable rate shading" (VRS), there will typically be a set of plural possible shading rates that a graphics processor supports and is able to use. That is, there will typically be a set of plural possible different sized render output areas that a single colour (set of colour value data) can be sampled 20 for. The smallest possible of these render output areas may be referred to as a "fine pixel", and the other, larger render output areas may be referred to as "coarse pixels".

Each "fine pixel" will typically be the same size and location as a pixel of the output display device. However, it 25 is also possible for each "fine pixel" to effectively correspond to less than one pixel of the output display device, for example where downsampling is to be applied.

The area of each possible "coarse pixel" typically corresponds to a block of plural "fine pixels". The different 30 possible shading rates are then referred to in terms of the number of fine pixels that the shading rate corresponds to. For example, a 1×1 shading rate will signify the finest possible shading mode in which a single colour should be sampled for a single fine pixel, whereas a 2×2 shading rate 35 will signify that a single colour should be sampled for an area corresponding to a block of 2×2 fine pixels. A graphics processor may typically support 1×1, 1×2, 2×1, 2×2, 2×4, 4×2 and 4×4 shading rates, for example.