### US010998391B2

# (12) United States Patent Bae et al.

## (54) DISPLAY APPARATUS WITH A CRACK DETECTION LINE

- (71) Applicant: LG Display Co., Ltd., Seoul (KR)

- (72) Inventors: **Jeong Min Bae**, Bucheon-si (KR); **JinHwan Kim**, Bucheon-si (KR)

- (73) Assignee: LG DISPLAY CO., LTD., Seoul (KR)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 16/168,237

- (22) Filed: Oct. 23, 2018

- (65) **Prior Publication Data**US 2019/0165312 A1 May 30, 2019

### (30) Foreign Application Priority Data

Nov. 30, 2017 (KR) ...... 10-2017-0163671

(51) Int. Cl.

H01L 27/32 (2006.01)

H01L 51/52 (2006.01)

H01L 51/56 (2006.01)

H01L 51/50 (2006.01)

G09G 3/3225 (2016.01)

(52) **U.S. Cl.**

C ...... H01L 27/3258 (2013.01); G09G 3/3225 (2013.01); H01L 27/3246 (2013.01); H01L 27/3276 (2013.01); H01L 51/5246 (2013.01); H01L 51/5253 (2013.01); H01L 51/56 (2013.01); G09G 2310/0264 (2013.01); H01L 27/322 (2013.01); H01L 27/3211 (2013.01); H01L 51/5056 (2013.01); H01L 51/5072 (2013.01); H01L 51/5092 (2013.01)

### (10) Patent No.: US 10,998,391 B2

(45) **Date of Patent:** May 4, 2021

### (58) Field of Classification Search

CPC . H01L 51/5253; H01L 51/5246; H01L 51/56; H01L 27/3246; H01L 27/3276; H01L 51/5056; H01L 51/5072; H01L 51/5092; H01L 27/3211; H01L 27/322; H01L 27/3225; H01L 27/3258; G09G 3/3225; G09G 2310/0264; G09G 2300/0426; G09G 3/20

See application file for complete search history.

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 2016/0307971 | A1* | 10/2016 | Jeon | H01L 51/5246 |

|--------------|-----|---------|------|--------------|

| 2018/0124933 | A1* | 5/2018  | Park | H01L 27/32   |

<sup>\*</sup> cited by examiner

Primary Examiner — Laura M Menz Assistant Examiner — Candice Chan (74) Attorney, Agent, or Firm — Birch, Stewart, Kolasch & Birch LLP

### (57) ABSTRACT

A display apparatus includes a substrate including a display area where a plurality of pixels are provided and a non-display area surrounding the display area, an encapsulation layer including an inorganic layer and an organic layer and covering the display area, a dam disposed in the non-display area to surround the display area and to block a flow of the organic layer, a pad disposed in one edge of the non-display area and spaced apart from the dam in the non-display area, an auxiliary buffer layer spaced apart from the dam and disposed in the non-display area to overlap an end of the inorganic layer, a power auxiliary line disposed between the dam and the auxiliary buffer layer and electrically connected to the pad to receive a voltage from the pad, and a crack detection line spaced apart from the power auxiliary line and electrically connected to the pad.

### 14 Claims, 32 Drawing Sheets

FIG. 1 RELATED ART

FIG. 2 RELATED ART

FIG. 3

RELATED ART

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26A

FIG. 26B

FIG. 26C

FIG. 26D

FIG. 26E

FIG. 26F

FIG. 26G

FIG. 26H

FIG. 27

FIG. 28A

FIG. 28B

FIG. 28C

FIG. 28D

FIG. 28E

FIG. 28F

FIG. 28G

## FIG. 28H

FIG. 28I

FIG. 28J

FIG. 28K

FIG. 28L

FIG. 29

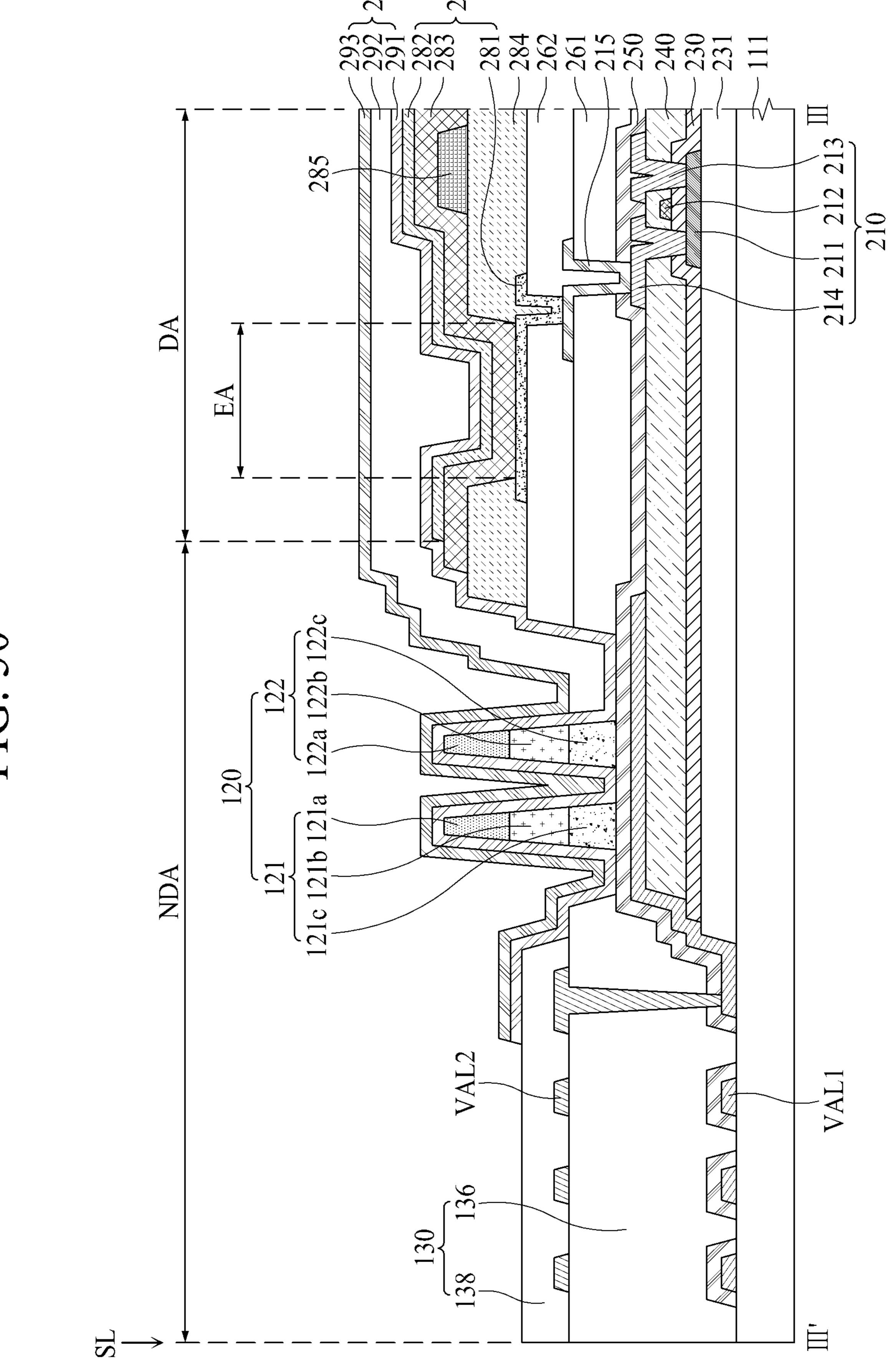

FIG. 30

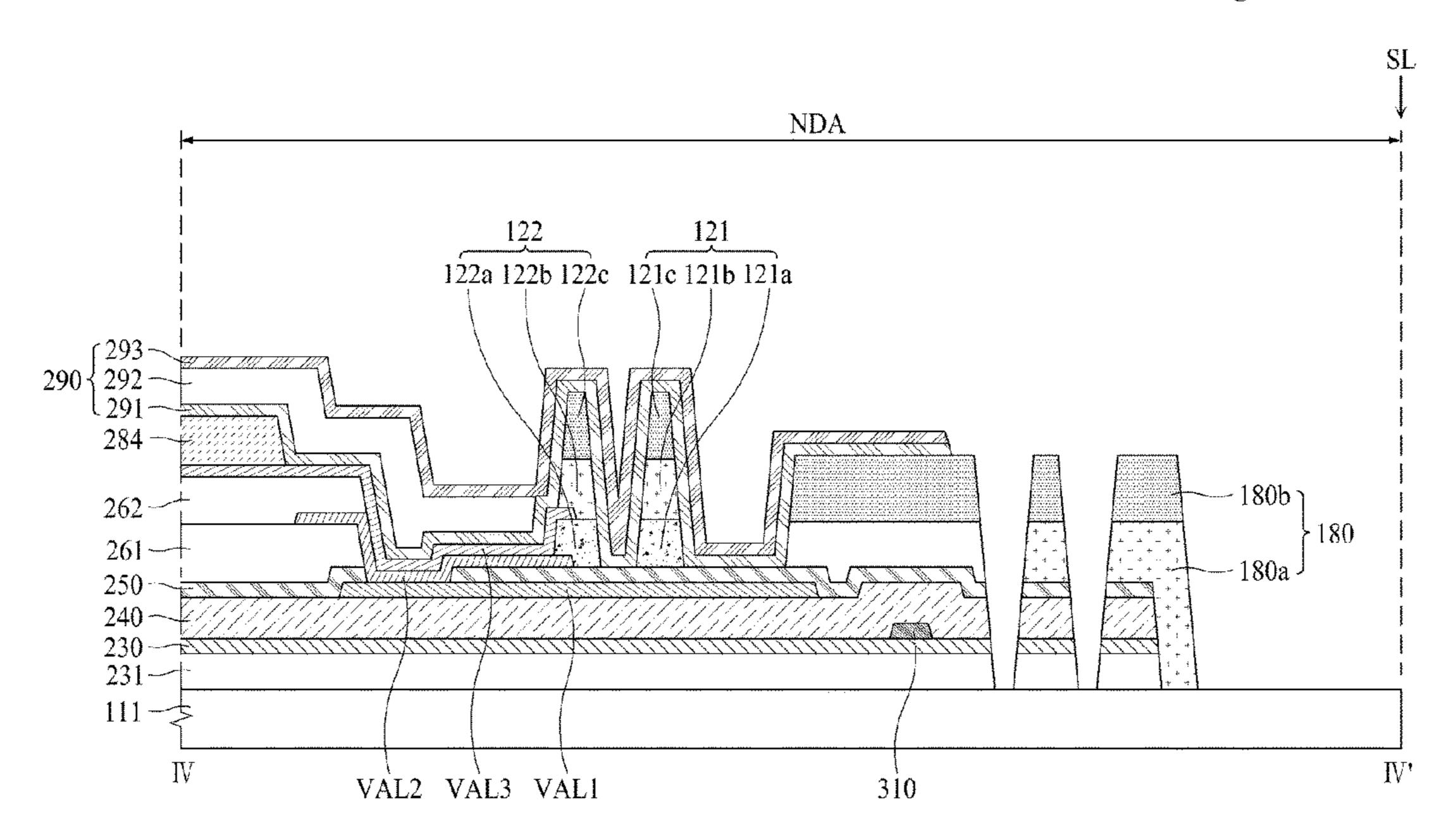

SI

290 \{ 292 \\ 291 \\ 284 \.

262 261 261 270 230 231 231 111

FIG. 32

SI

$\prod$

290 \{ 292 \\ 291 \\ 284 \.

262 261 261 270 230 231 231 111 1

## DISPLAY APPARATUS WITH A CRACK DETECTION LINE

## CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims the priority benefit of the Korean Patent Application No. 10-2017-0163671 filed on Nov. 30, 2017 in the Republic of Korea, which is hereby incorporated by reference for all purposes as if fully set forth herein.

### **BACKGROUND**

#### Field of the Invention

The present disclosure relates to a display apparatus.

### Discussion of the Related Art

With the advancement of information-oriented society, 20 various requirements for display apparatuses for displaying an image are increasing. Therefore, various display apparatuses such as liquid crystal display (LCD) apparatuses, organic light emitting display apparatuses, quantum dot light emitting display apparatuses, and electroluminescence display apparatuses are being used recently.

As a type of display apparatus, organic light emitting display apparatuses and quantum dot light emitting display apparatuses are self-emitting display apparatuses and are better in viewing angle and contrast ratio than LCD apparatuses. Also, since the organic light emitting display apparatuses do not need a separate backlight, it is possible to lighten and thin the organic light emitting display apparatuses, and the organic light emitting display apparatuses are excellent in power consumption. Furthermore, the organic 35 light emitting display apparatuses are driven with a low direct current (DC) voltage, have a fast response time, and are low in manufacturing cost.

Organic light emitting display apparatuses each include a plurality of pixels each including an organic light emitting 40 device and a bank which divides the pixels for defining the pixels. The bank can act as a pixel defining layer. The organic light emitting device includes an anode electrode, a hole transporting layer, an organic light emitting layer, an electron transporting layer, and a cathode electrode. When a 45 high-level voltage is applied to the anode electrode and a low-level voltage is applied to the cathode electrode, a hole and an electron respectively move to the organic light emitting layer through the hole transporting layer and the electron transporting layer and are combined with each other 50 in the organic light emitting layer to emit light.

However, light emitting devices are easily deteriorated by external factors such as external moisture and oxygen. In order to prevent the deterioration, organic light emitting display apparatuses each include an encapsulation layer for 55 preventing external moisture or oxygen from penetrating into the light emitting devices.

Quantum dot light emitting display apparatuses each include a light emitting structure. The light emitting structure includes an anode electrode, a cathode electrode facing 60 the anode electrode, and a light emitting device disposed between the anode electrode and the cathode electrode. The light emitting device includes a hole transporting layer, a light emitting layer, and an electron transporting layer. The light emitting layer includes a quantum dot material.

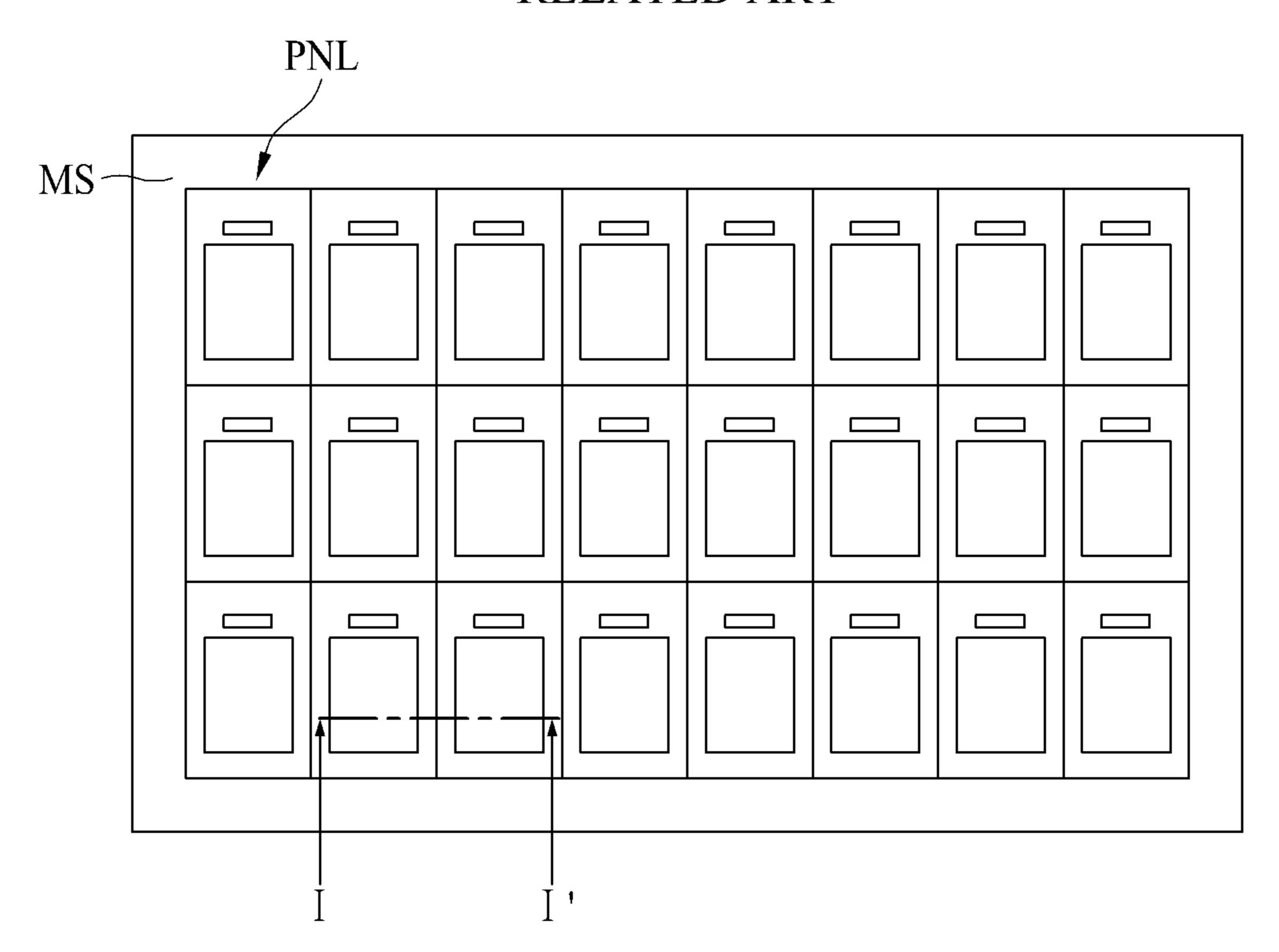

FIG. 1 is a diagram illustrating a mother substrate on which a plurality of display panels are provided according to

2

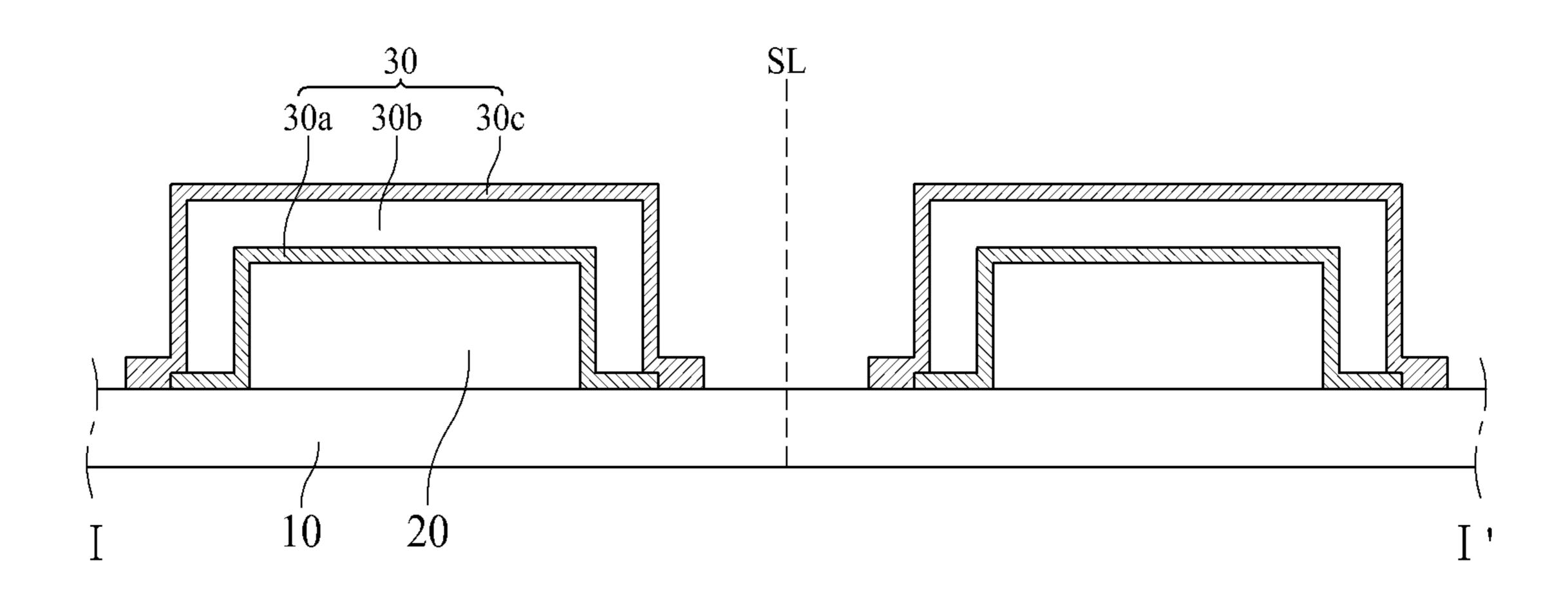

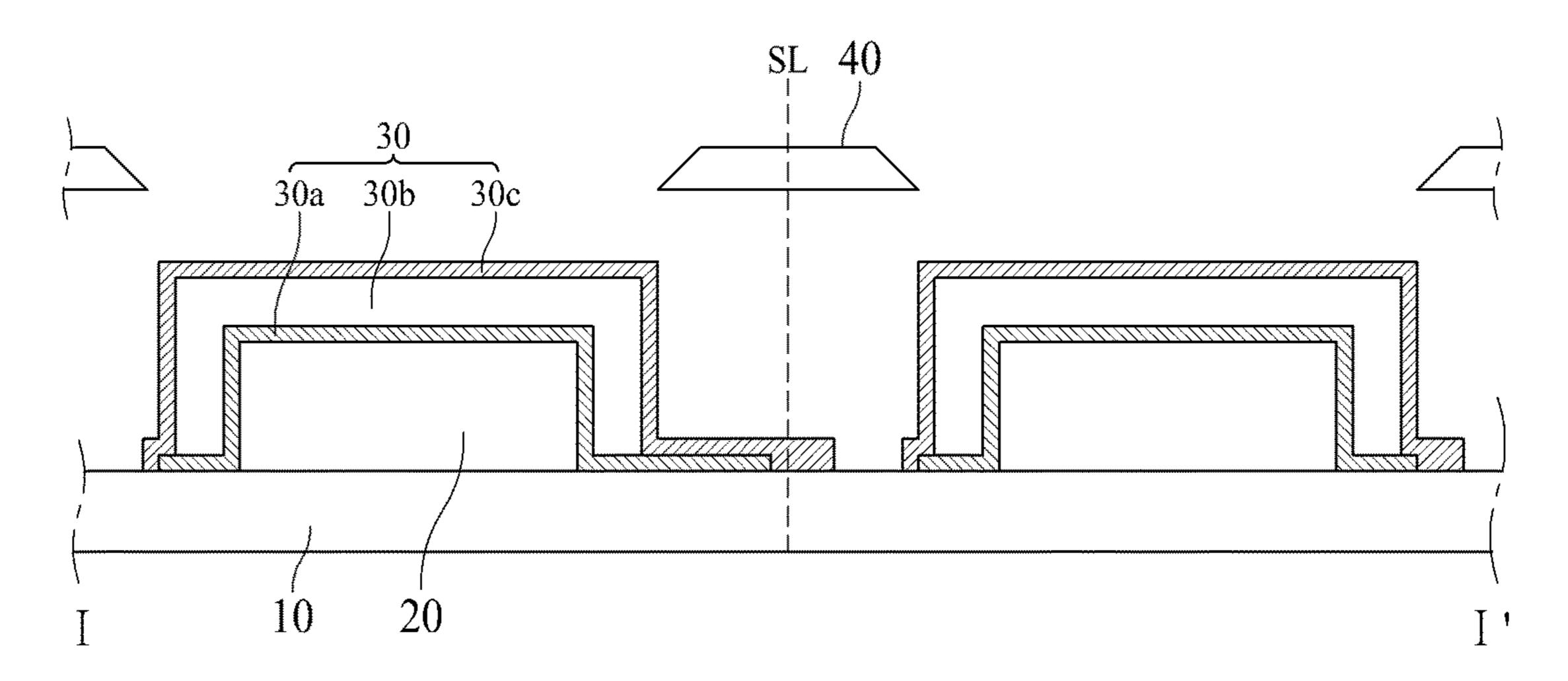

a related art. FIG. 2 is a cross-sectional view taken along line I-I' illustrated in FIG. 1 and is a cross-sectional view schematically illustrating a display apparatus. FIG. 3 is a cross-sectional view for describing a method of forming an inorganic layer of a display apparatus according to a related art.

Referring to FIGS. 1 to 3, a mother substrate MS is a substrate for simultaneously manufacturing a plurality of display panels PNL, for convenience of a process. The display panels PNL are individually separated from one another and each act as a display apparatus. A plurality of mother substrates MS are simultaneously formed, and then, are separated from one another through a cutting process or a scribing process.

In the display apparatus, an encapsulation layer 30 is formed on a substrate 10 on which an organic light emitting device 20 is provided. In this case, the encapsulation layer 30 includes a first inorganic layer 30a, an organic layer 30b, and a second inorganic layer 30c and prevents oxygen or water from penetrating into a light emitting layer.

The first inorganic layer 30a and the second inorganic layer 30c are deposited on the substrate 10 through a chemical vapor deposition (CVD) process. The CVD process, as illustrated in FIG. 3, disposes a mask 40 on the substrate 10 and supplies a gas, including a chemical element constituting the first inorganic layer 30a or the second inorganic layer 30c, to the substrate 10. The supplied gas performs a chemical reaction on a surface, disposed in an area where the mask 40 is not provided, of the substrate 10. Therefore, the first inorganic layer 30a or the second inorganic layer 30c is formed on the surface, disposed in the area where the mask 40 is not provided, of the substrate 10.

However, in the CVD process, since the mask 40 is spaced apart from the substrate 10 by a certain interval, the gas penetrates into a space between the mask 40 and the substrate 10 and performs a chemical reaction on a surface, disposed in an area where the mask 40 is provided, of the substrate 10, and for this reason, the first inorganic layer 30a or the second inorganic layer 30c can be formed on the surface, disposed in the area where the mask 40 is provided, of the substrate 10.

As described above, if the first inorganic layer 30a or the second inorganic layer 30c is formed on the surface (for example, a scribing line SL), disposed in the area where the mask 40 is provided, of the substrate 10, a crack can occur in the first inorganic layer 30a or the second inorganic layer 30c when performing a cutting process (i.e., a laser cutting process or a mechanical scribing process) of separating the display panels PNL. The crack can be propagated to the inside along an inorganic layer due to an external impact, and water and oxygen which flow in along the propagated crack cause a black spot and a dark line smear.

In order to overcome a limitation where a step coverage of the CVD process is low, technology for depositing the first inorganic layer 30a and the second inorganic layer 30b on the substrate 10 through an atomic layer deposition (ALD) process is attracting much attention recently. The ALD process is a method which disposes the mask 40 on the substrate 10 and forms a thin layer by alternating a raw material including an ALD metal and a reactant gas. The ALD process is better in adsorbing force than the CVD process, is high in step coverage, and adjusts a thickness of a thin layer. Accordingly, the ALD process is easy to form a very thin layer.

However, since the ALD process has an excellent absorbing force as described above, the first inorganic layer 30a or the second inorganic layer 30c can be long formed up to the

3

inside of a region, where the mask 40 is disposed, of the substrate 10, and for this reason, in comparison with the CVD process, the ALD process has a high possibility that the first inorganic layer 30a or the second inorganic layer 30c is formed up to the scribing line SL.

In order to solve the above-described problem, it can be considered to develop a method which disposes the mask 40 at a position close to the light emitting device 20 to reduce a separation distance to the substrate 10 and prevents the first inorganic layer 30a or the second inorganic layer 30c from penetrating into a region where the mask 40 is disposed. However, the method has a problem where the organic light emitting device 20 is damaged or deformed by disposing the mask 40, causing a black spot.

Moreover, a plurality of metal lines are disposed on the substrate 10, and for example, metal lines disposed in a non-display area are covered by a thin passivation layer in the CVD process. When a high voltage is instantaneously applied in the CVD process, the passivation layer for protecting the metal lines is torn by the high voltage, and static electricity occurs between the metal lines disposed in the non-display area and the mask 40. Due to the static electricity, the metal lines are damaged which causes the display panel not to normally operate, and it is unable to reuse the mask 40.

Moreover, if a crack occurs in an outer region of the display panel of the display apparatus according to the related art, power applied to the display panel is short-circuited or cut off, and due to this, a screen is abnormally displayed, or a driving power is not normally supplied.

### **SUMMARY**

Accordingly, the present disclosure is directed to provide a display apparatus that substantially obviates one or more 35 problems due to limitations and disadvantages of the related art.

An aspect of the present disclosure is directed to provide a display apparatus which detects a crack occurring in an outer region of a display panel to decrease an error rate.

Another aspect of the present disclosure is directed to provide a display apparatus in which an organic layer is provided to overlap a crack detection line provided in an outer region of a display panel, thereby reducing the damage of the crack detection line caused by static electricity which 45 occurs in a process of depositing an encapsulation layer.

Additional advantages and features of the disclosure will be set forth in part in the description which follows and in part will become apparent to those having ordinary skill in the art upon examination of the following or can be learned 50 from practice of the disclosure. The objectives and other advantages of the disclosure can be realized and attained by the structure particularly pointed out in the written description and claims hereof as well as the appended drawings.

To achieve these and other advantages and in accordance with the purpose of the disclosure, as embodied and broadly described herein, there is provided a display apparatus including a substrate including a display area where a plurality of pixels are provided and a non-display area surrounding the display area, an encapsulation layer including an inorganic layer and an organic layer and covering the display area, and display area and to block a flow of the organic layer, a pad disposed in one edge of the non-display area and spaced apart from the dam in the non-display area, an espaced apart from the dam and disposed in the non-display area, an encapsulation layer including a present disclosure; FIG. 12 is a cross FIG. 13; is a plantaged apart from the dam and display area and spaced apart from the dam and disposed in the non-display area and of the FIG. 13;

4

inorganic layer, a power auxiliary line disposed between the dam and the auxiliary buffer layer and electrically connected to the pad to receive a voltage from the pad, and a crack detection line spaced apart from the power auxiliary line and electrically connected to the pad.

In another aspect of the present disclosure, there is provided a display apparatus including a substrate including a display area where a plurality of pixels are provided and a non-display area adjacent to the display area, a pad disposed in one edge of the non-display area, a dam disposed in the non-display area to surround the display area and disposed between the display area and the pad in the non-display area where the pad is disposed, an auxiliary buffer layer disposed in the non-display area and spaced apart from the dam, a power auxiliary line disposed between the display area and the auxiliary buffer layer and electrically connected to the pad, and a crack detection line provided to overlap a bottom of the auxiliary buffer layer and electrically connected to the pad.

It is to be understood that both the foregoing general description and the following detailed description of the present disclosure are exemplary and explanatory and are intended to provide further explanation of the disclosure as claimed.

### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, which are included to provide a further understanding of the disclosure and are incorporated in and constitute a part of this application, illustrate embodiments of the disclosure and together with the description serve to explain the principle of the disclosure. In the drawings:

FIG. 1 is a diagram illustrating a mother substrate on which a plurality of display panels are provided according to a related art;

FIG. 2 is a cross-sectional view taken along line I-I' illustrated in FIG. 1;

FIG. 3 is a cross-sectional view for describing a method of forming an inorganic layer of a display apparatus according to a related art;

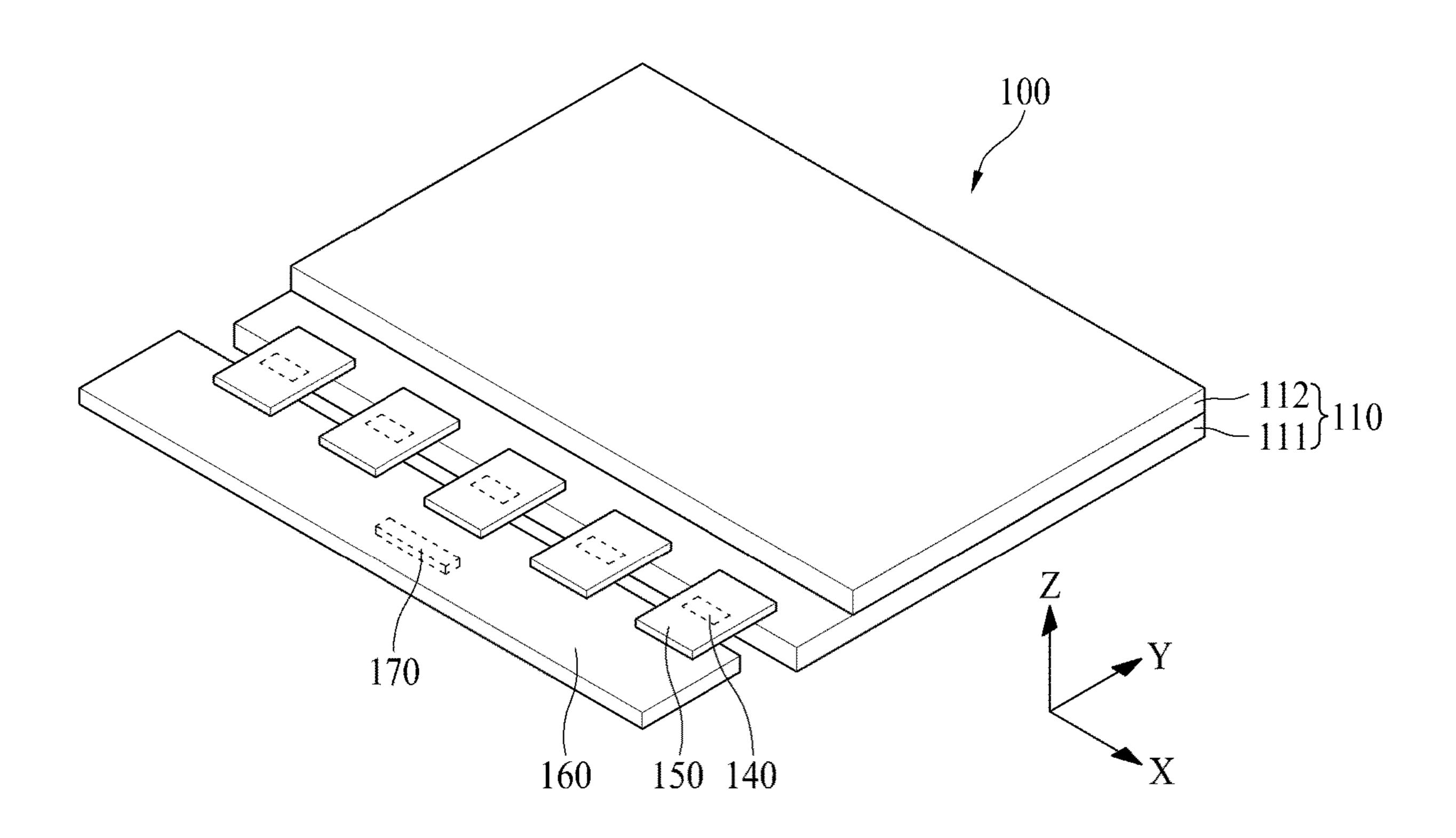

FIG. 4 is a perspective view illustrating a display apparatus according to an embodiment of the present disclosure;

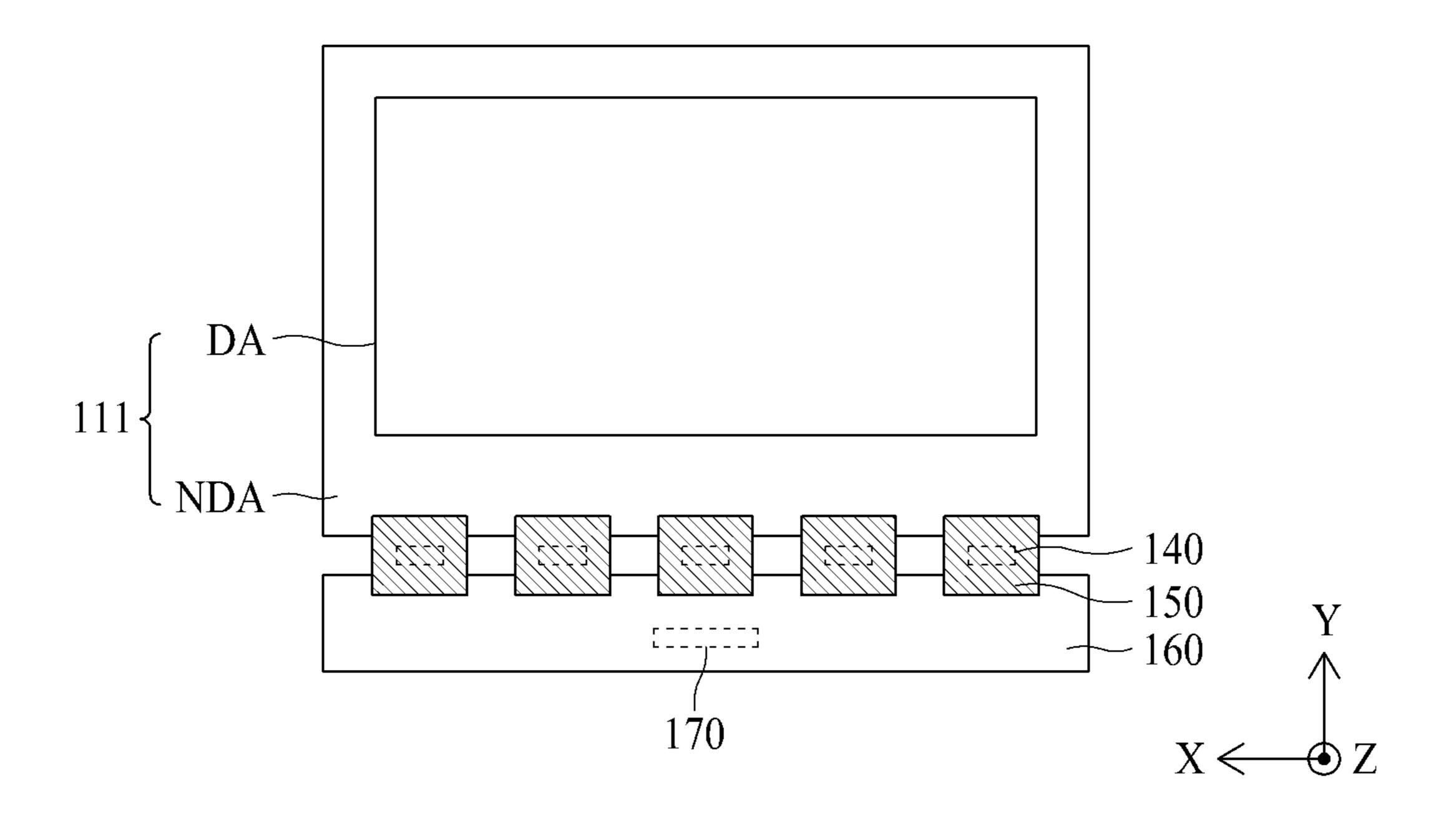

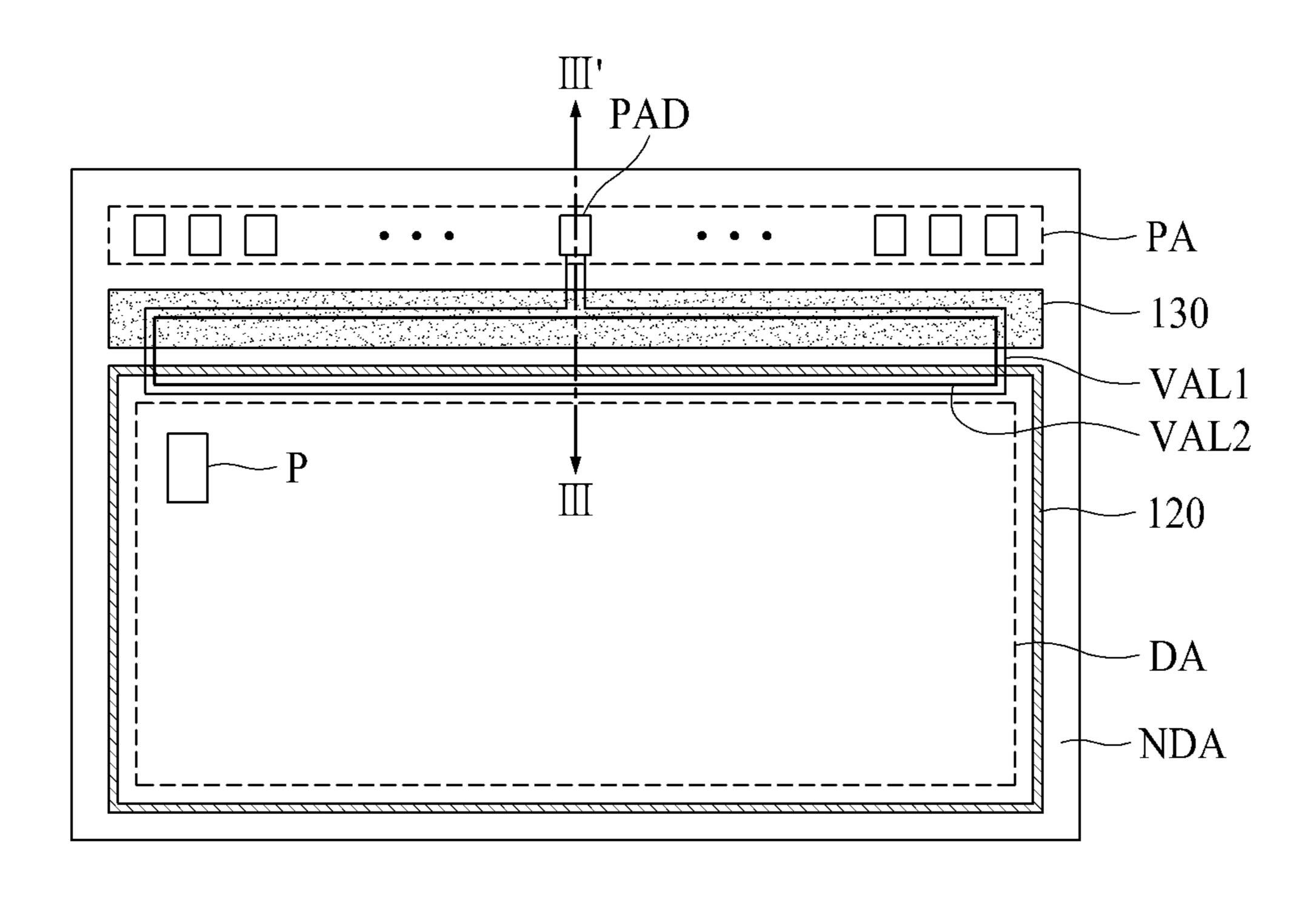

FIG. 5 is a plan view illustrating a first substrate, a source drive integrated circuit (IC), a flexible film, a circuit board, and a timing controller illustrated in FIG. 4;

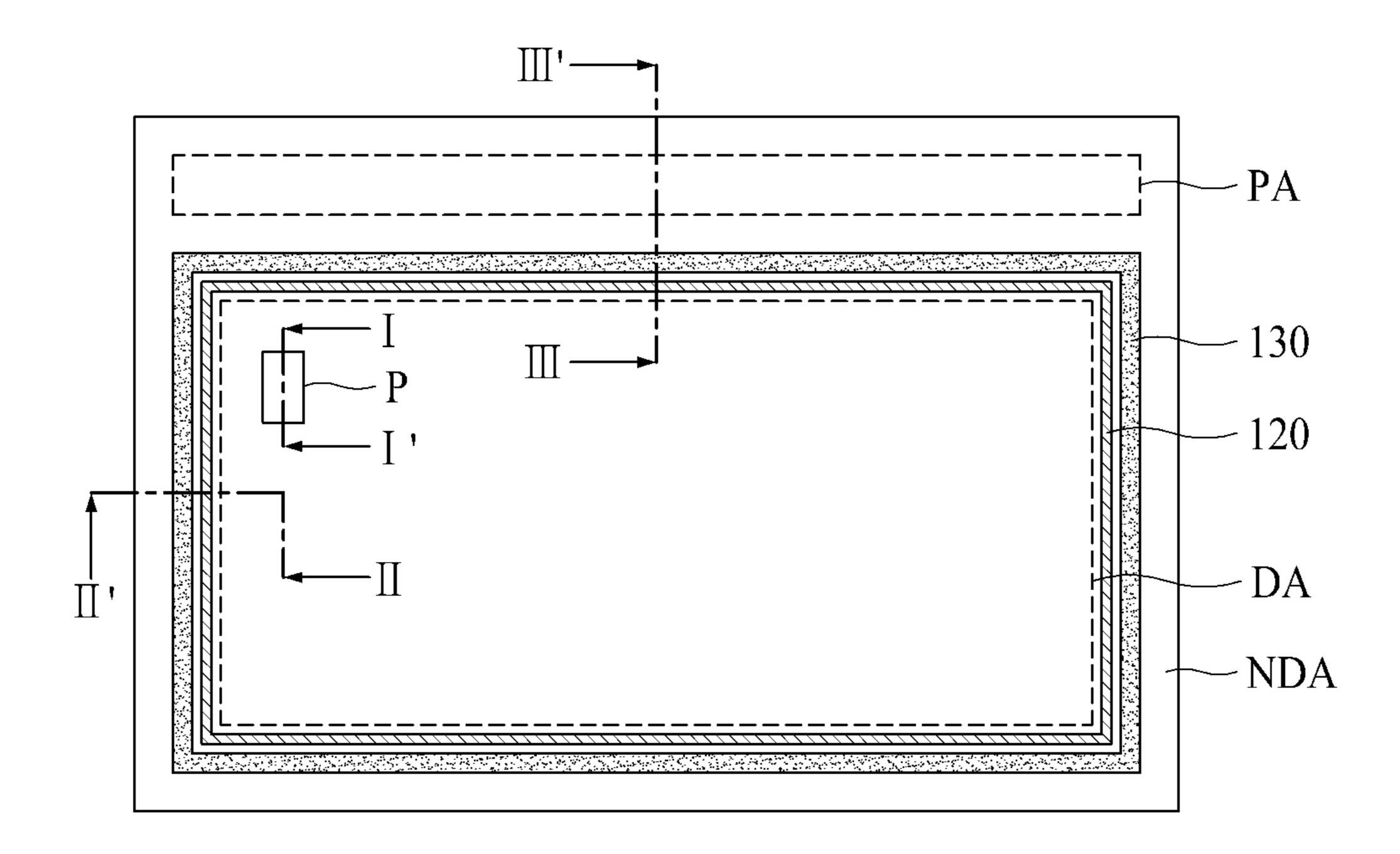

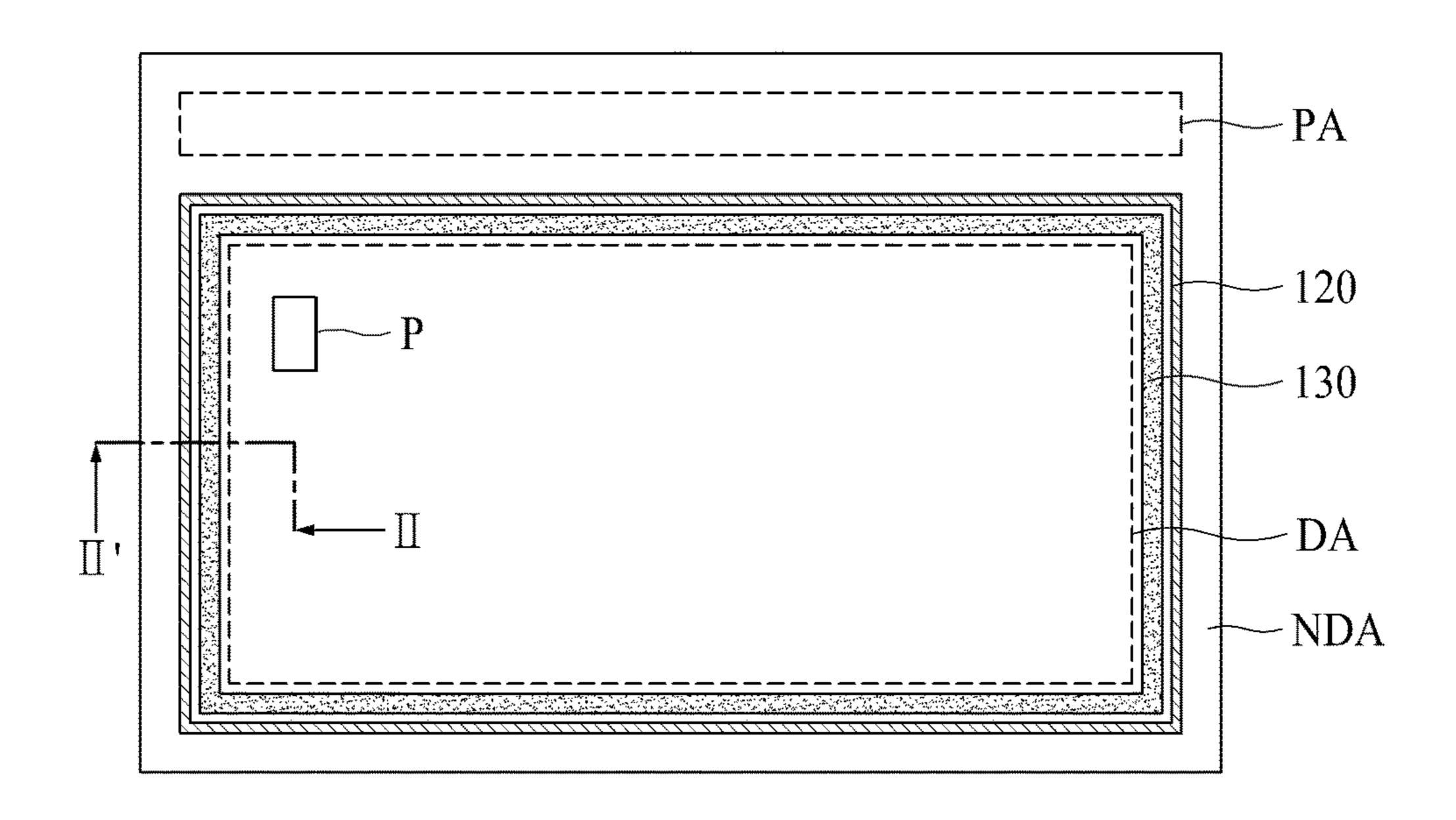

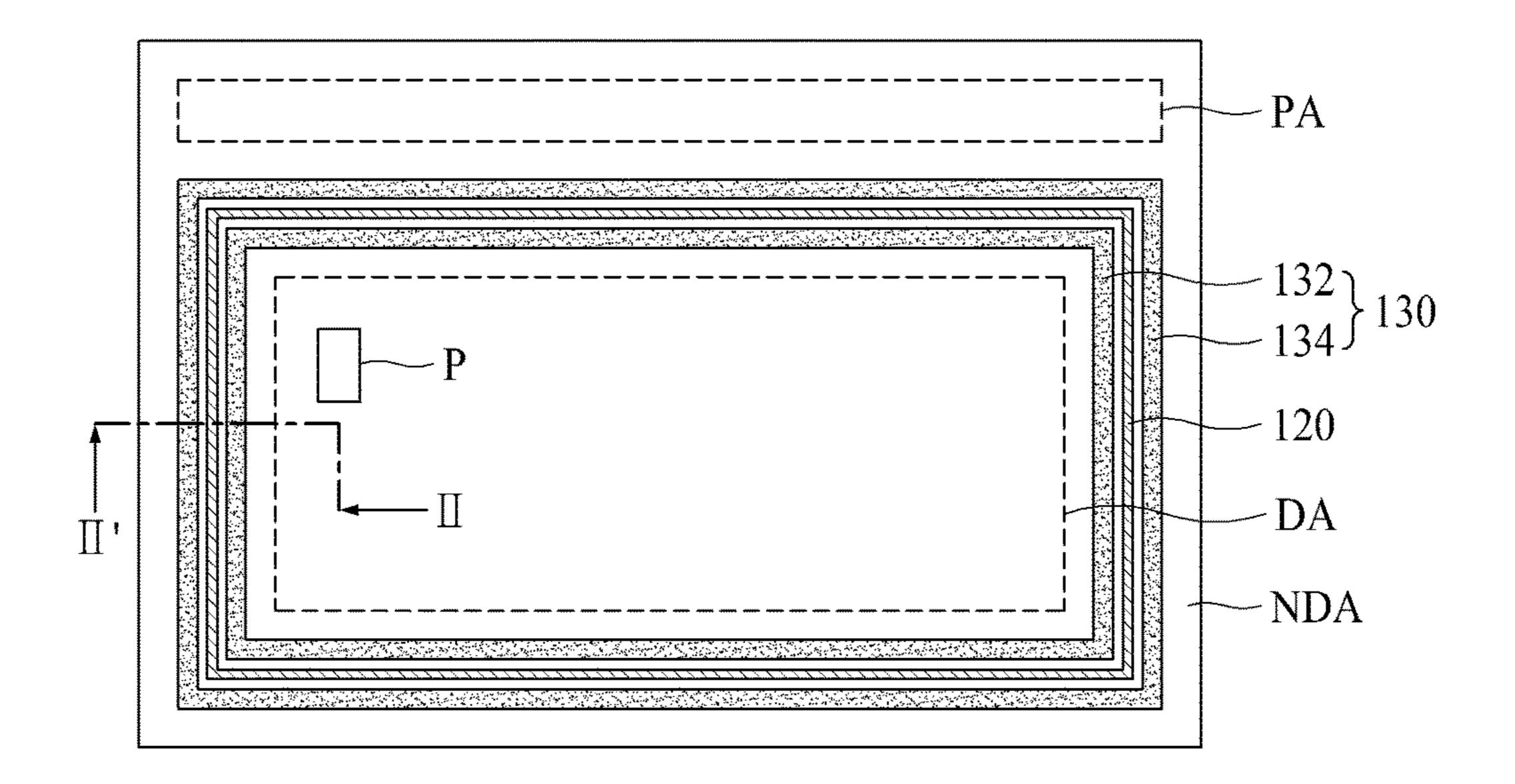

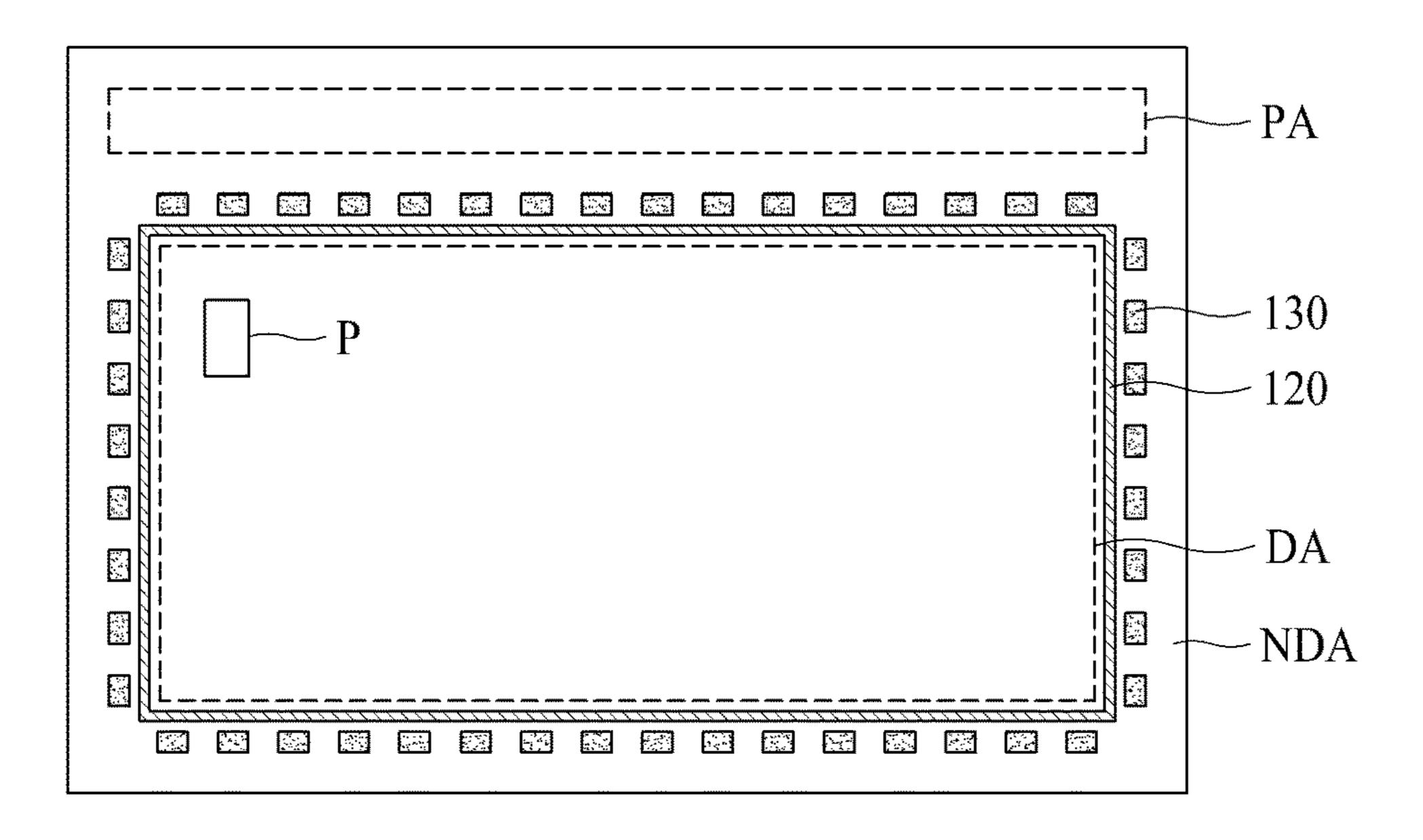

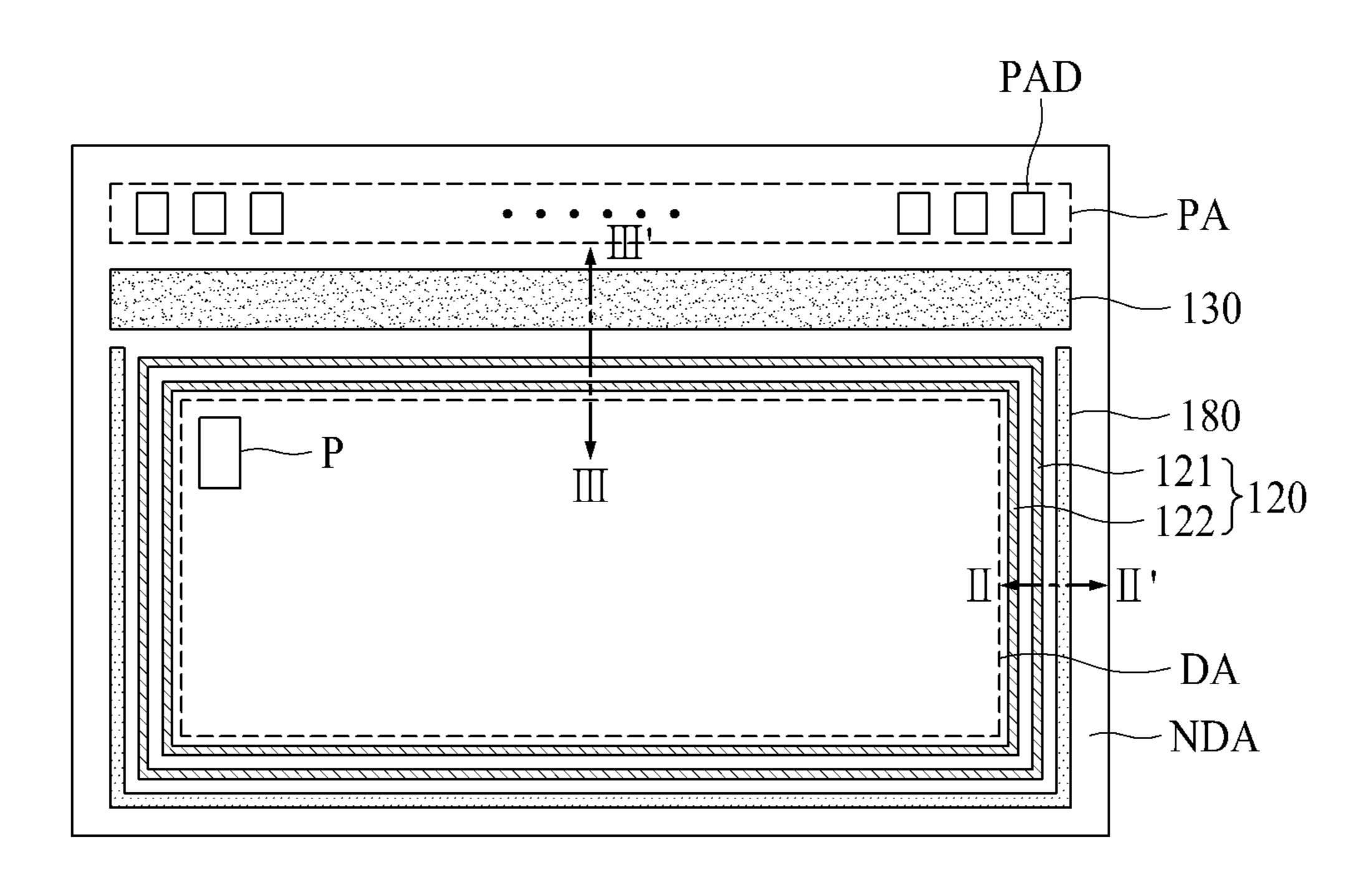

FIG. 6 is a plan view illustrating a first substrate of a display apparatus according to a first embodiment of the present disclosure;

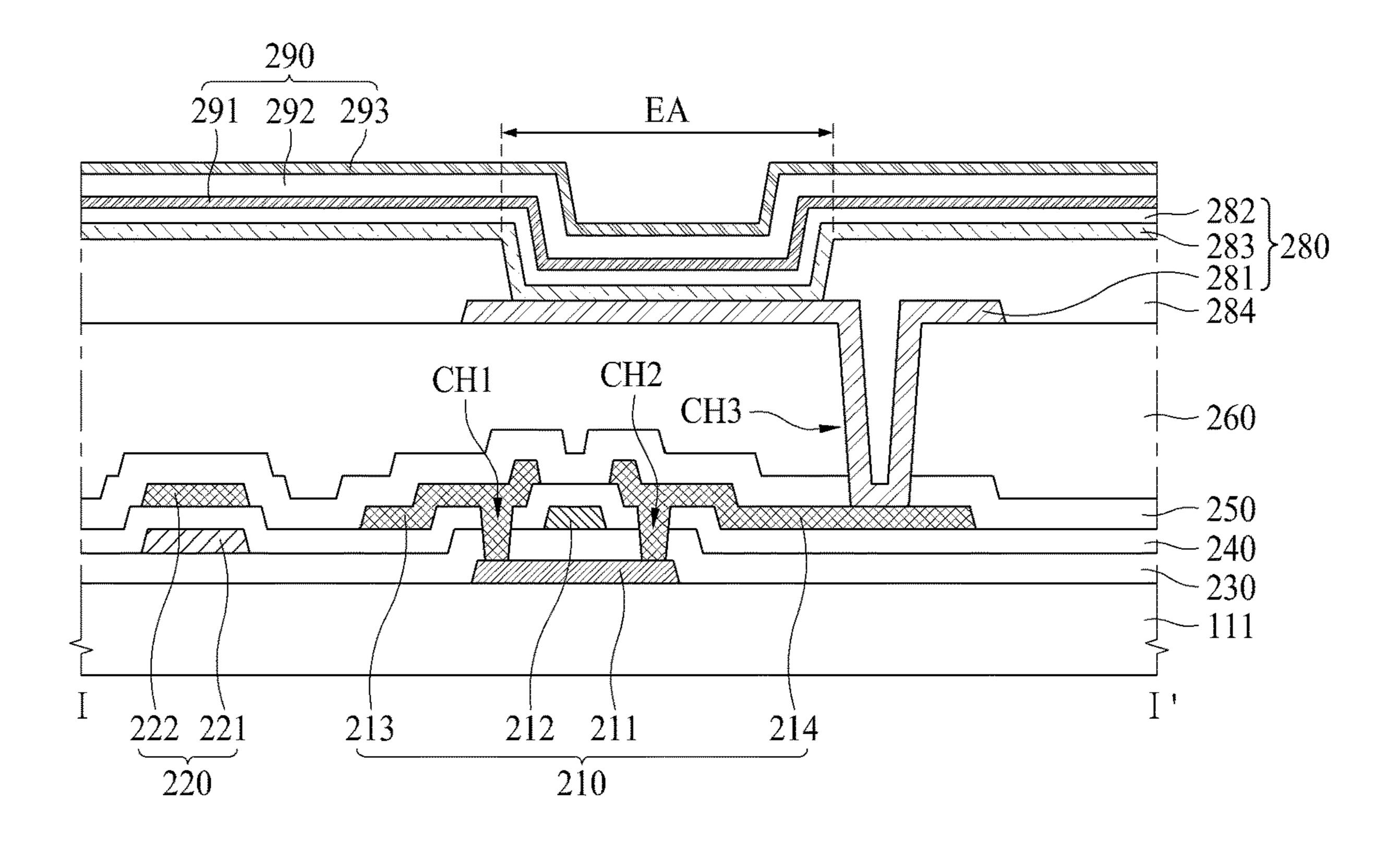

FIG. 7 is a cross-sectional view taken along line I-I' of FIG. 6;

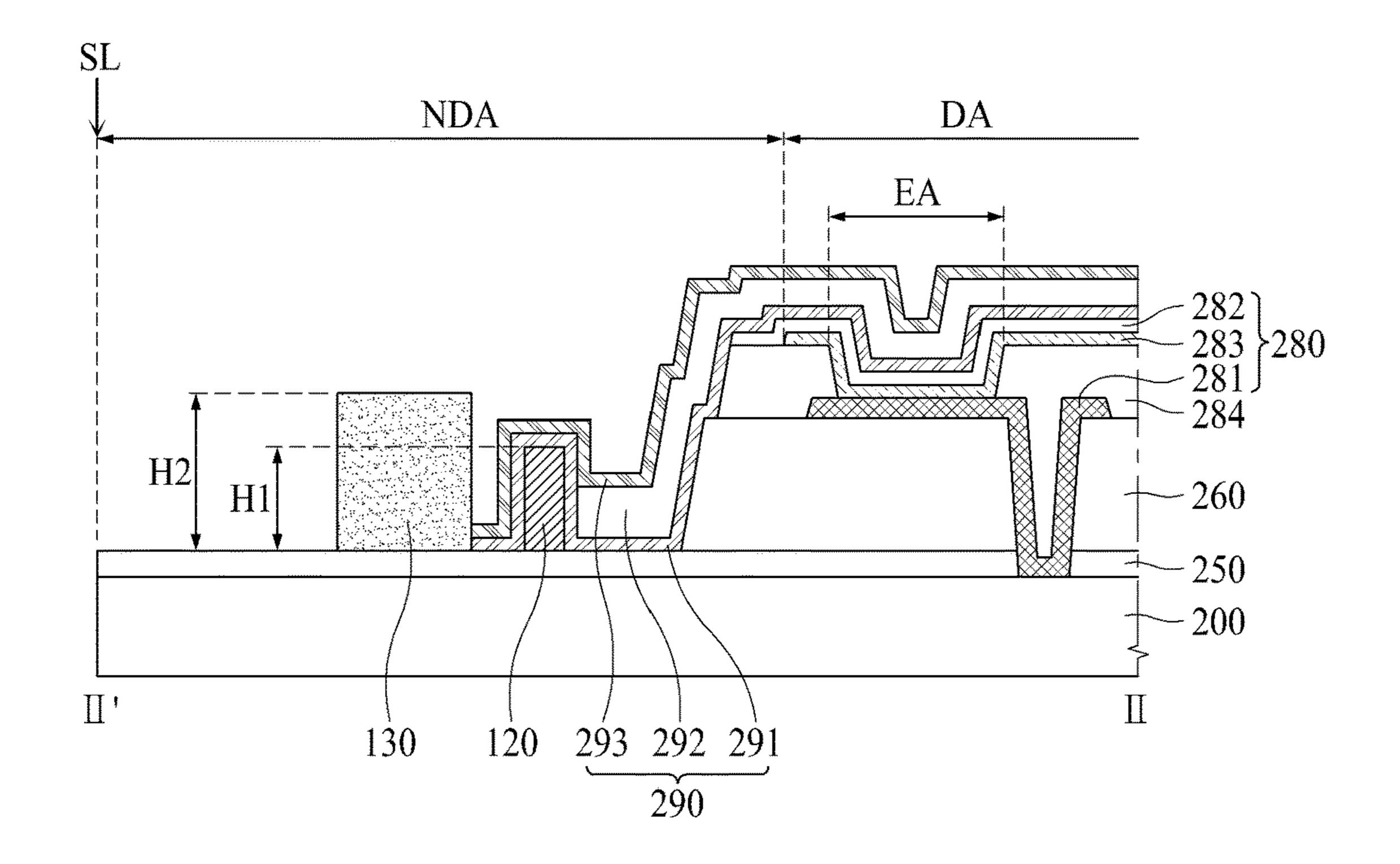

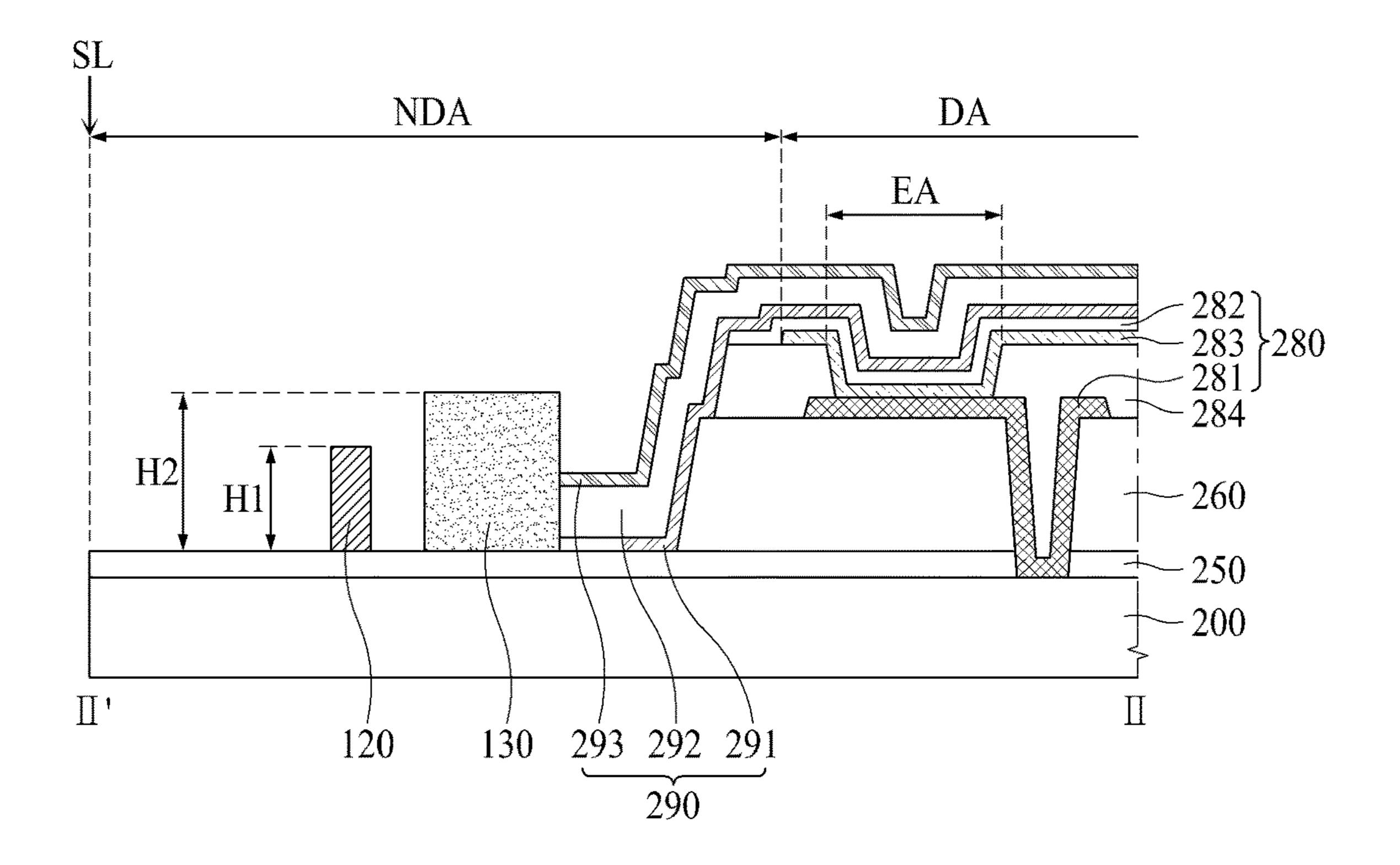

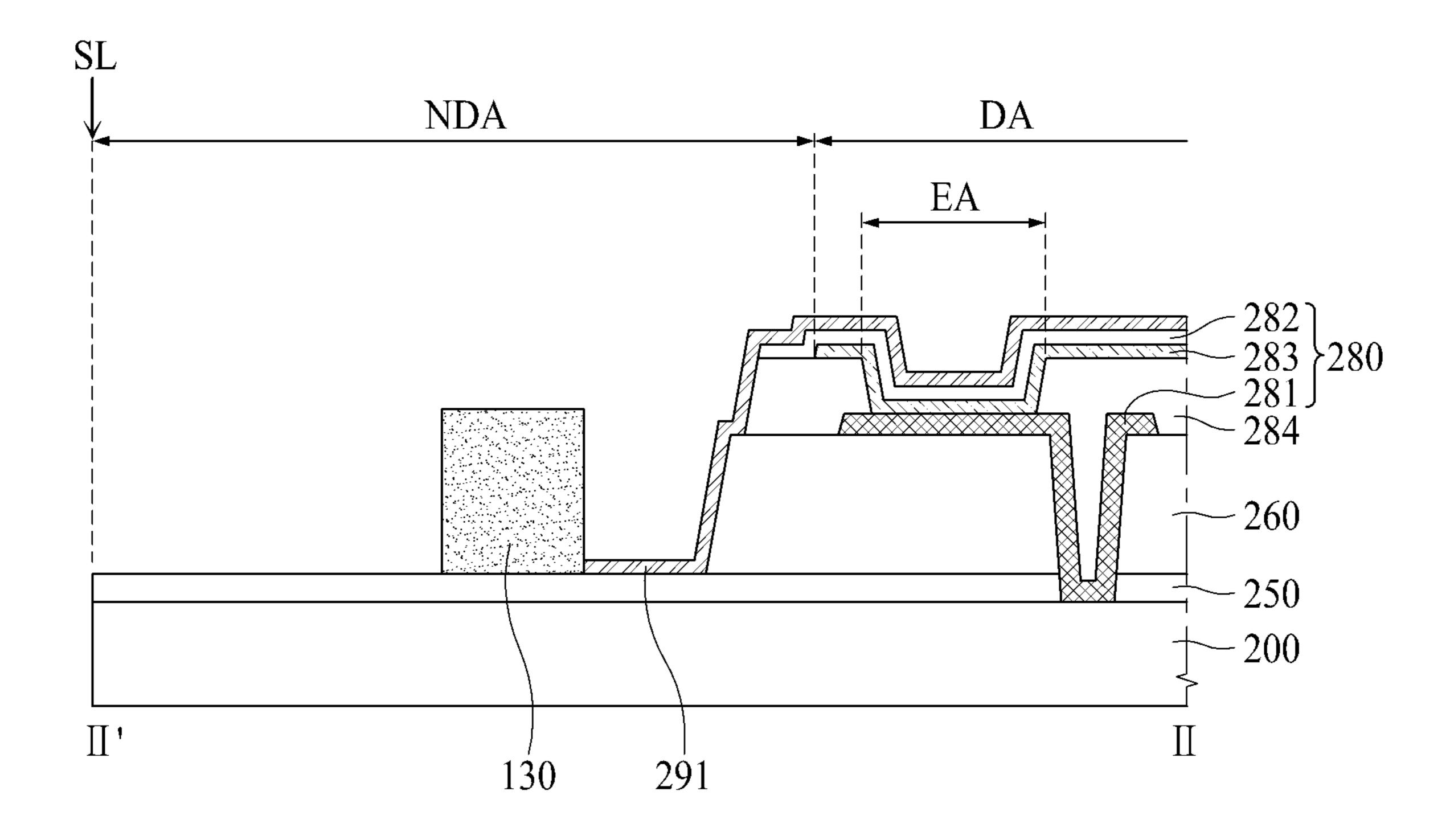

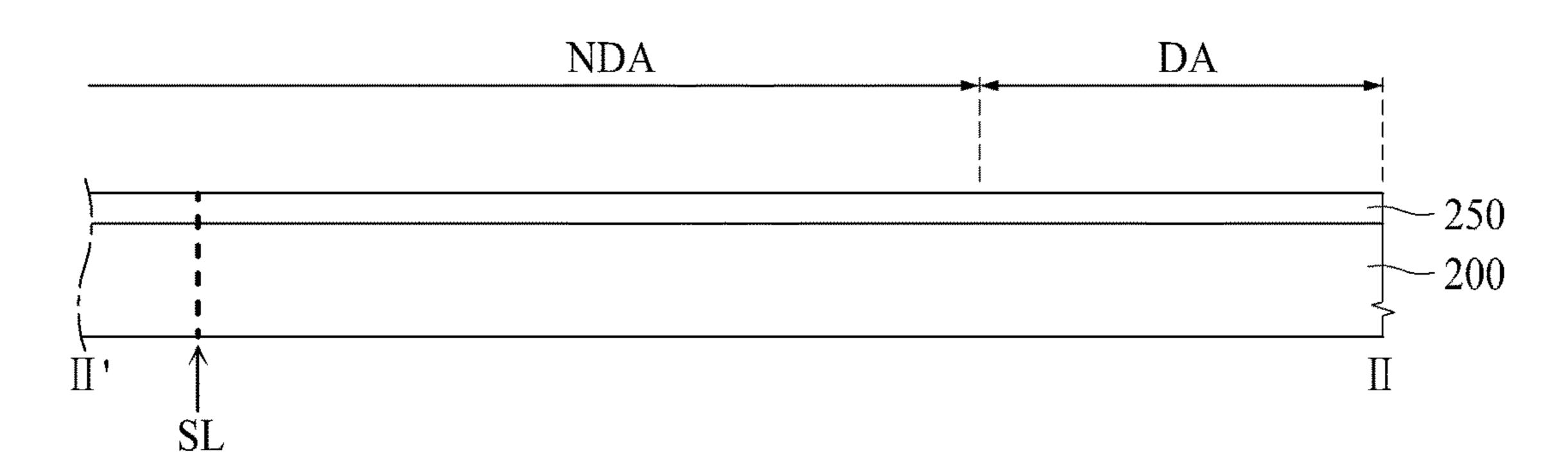

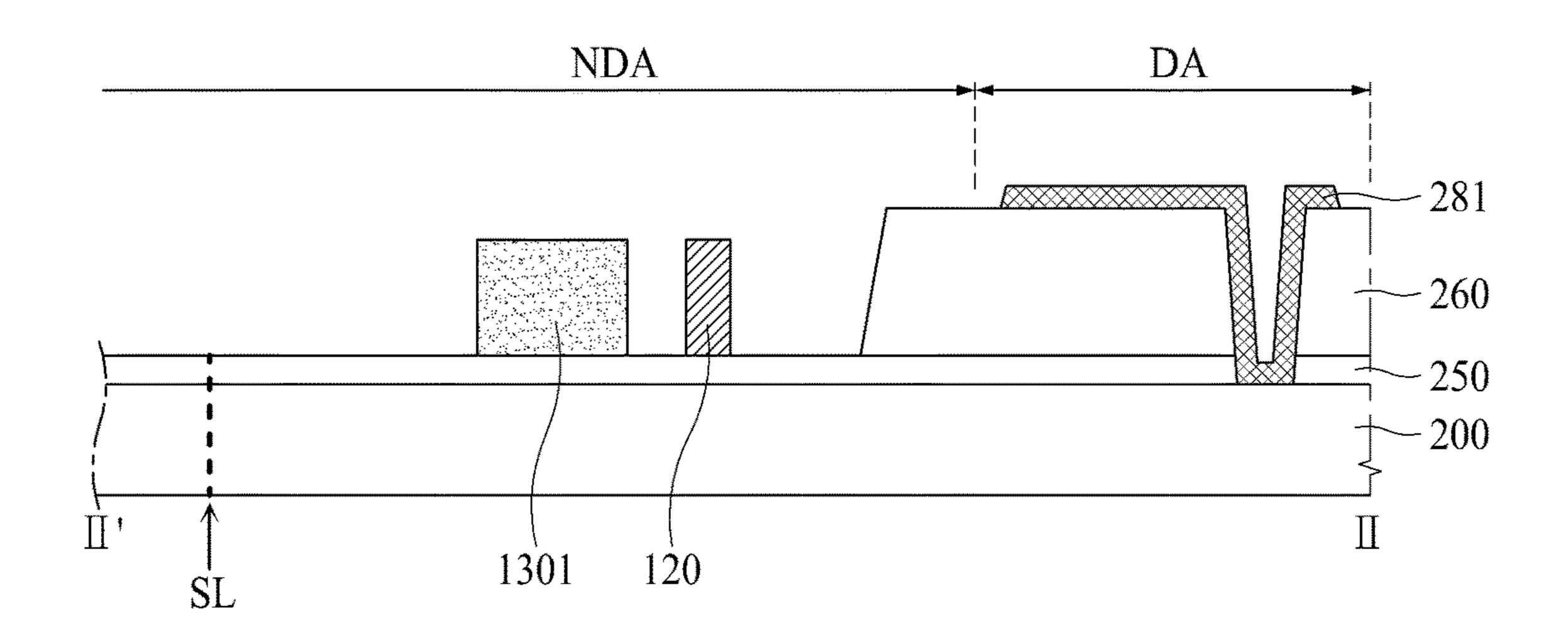

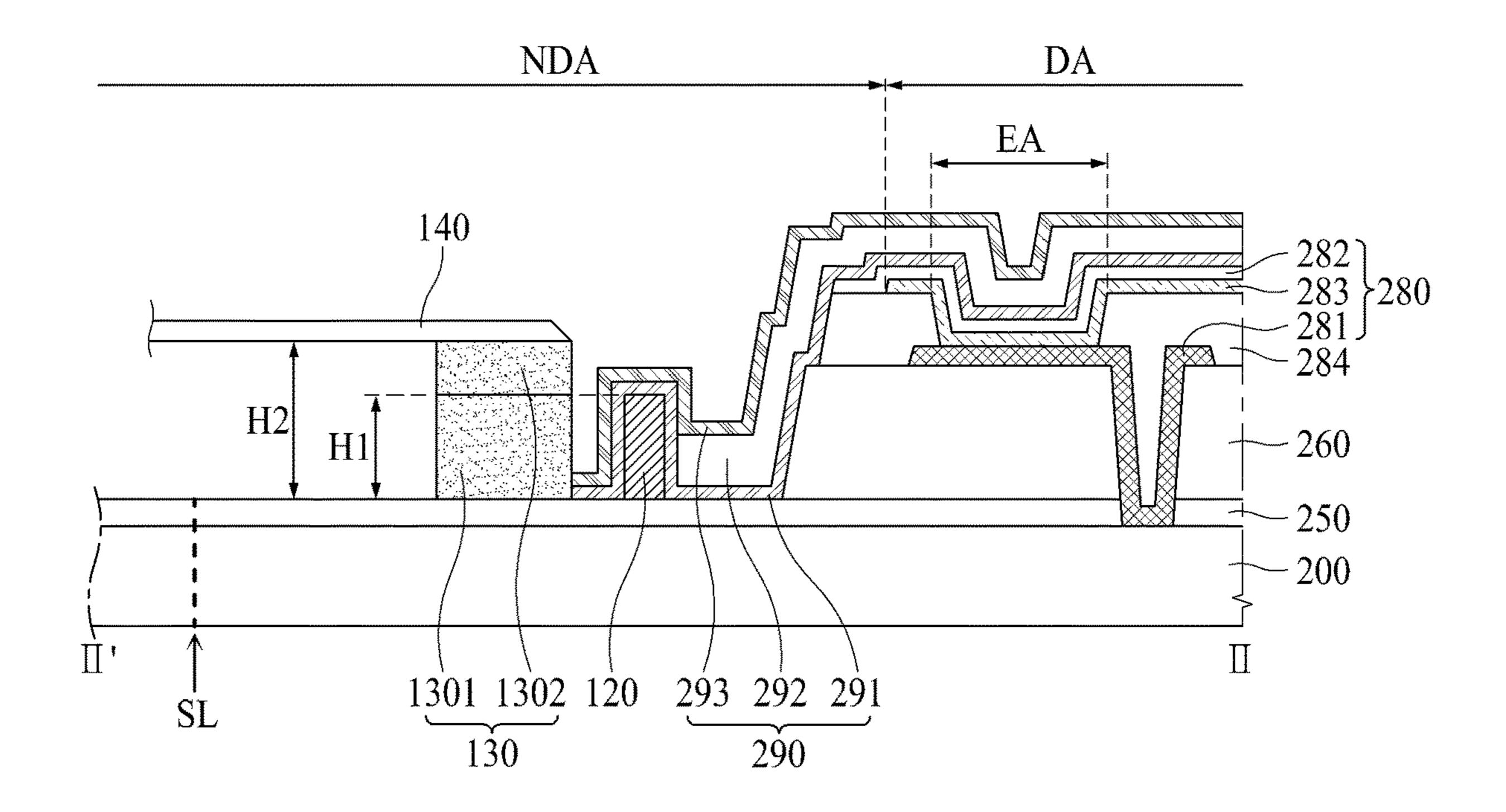

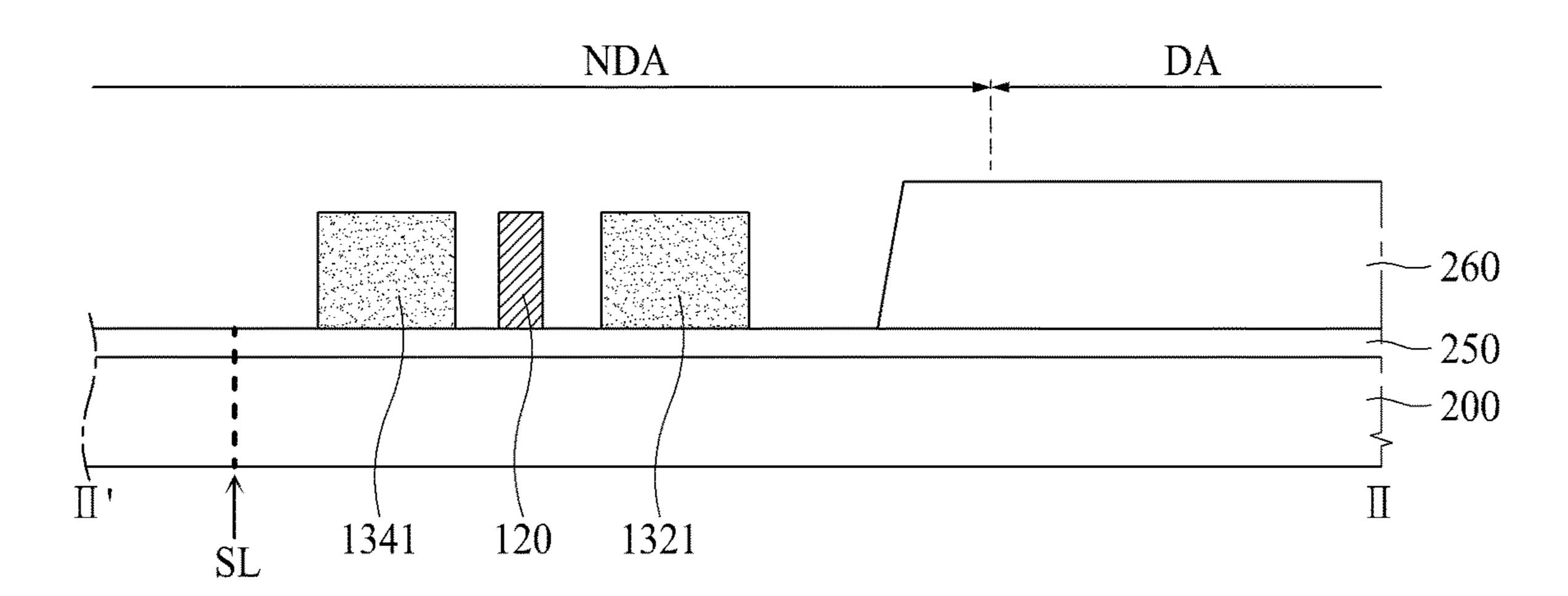

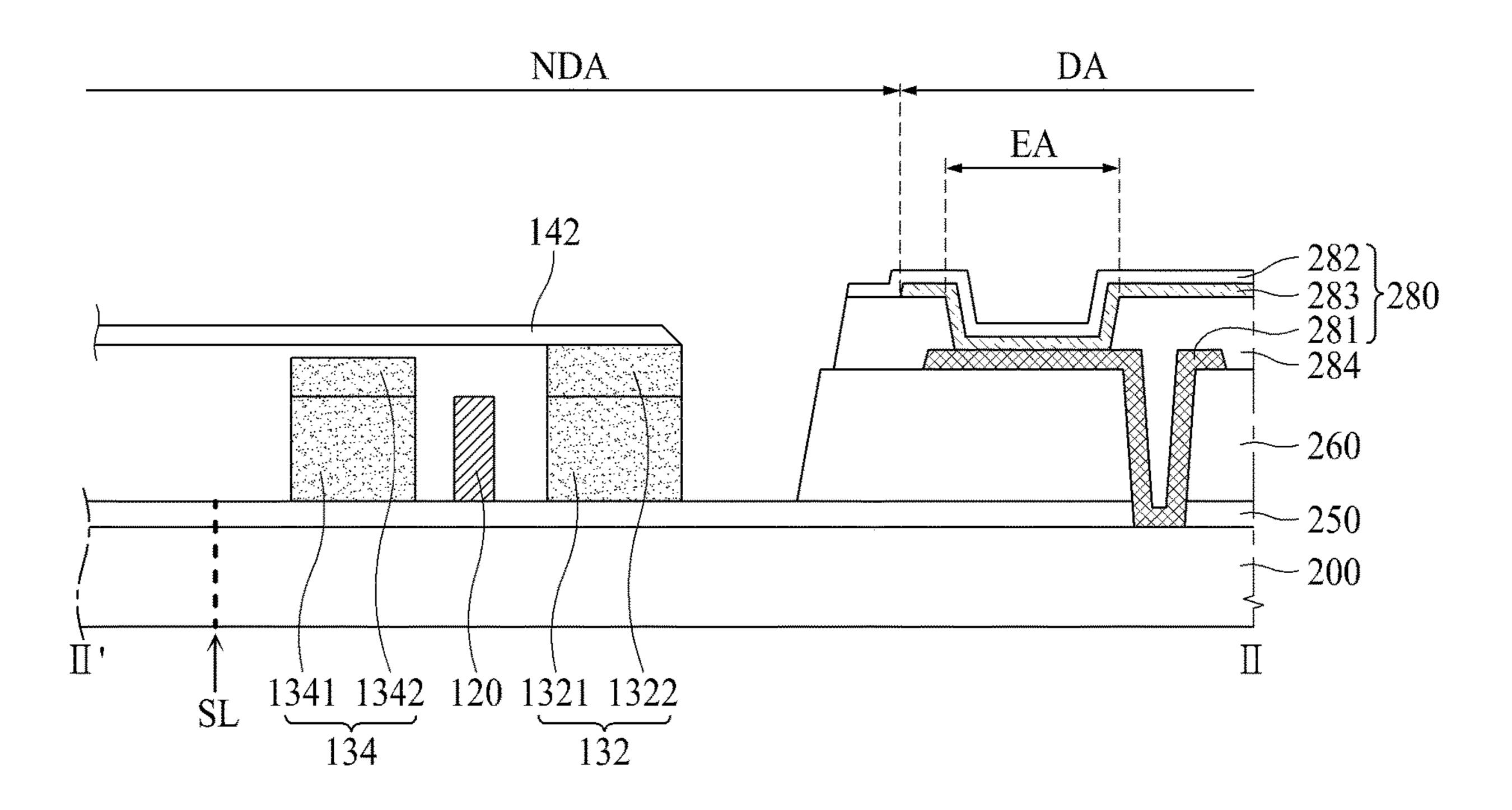

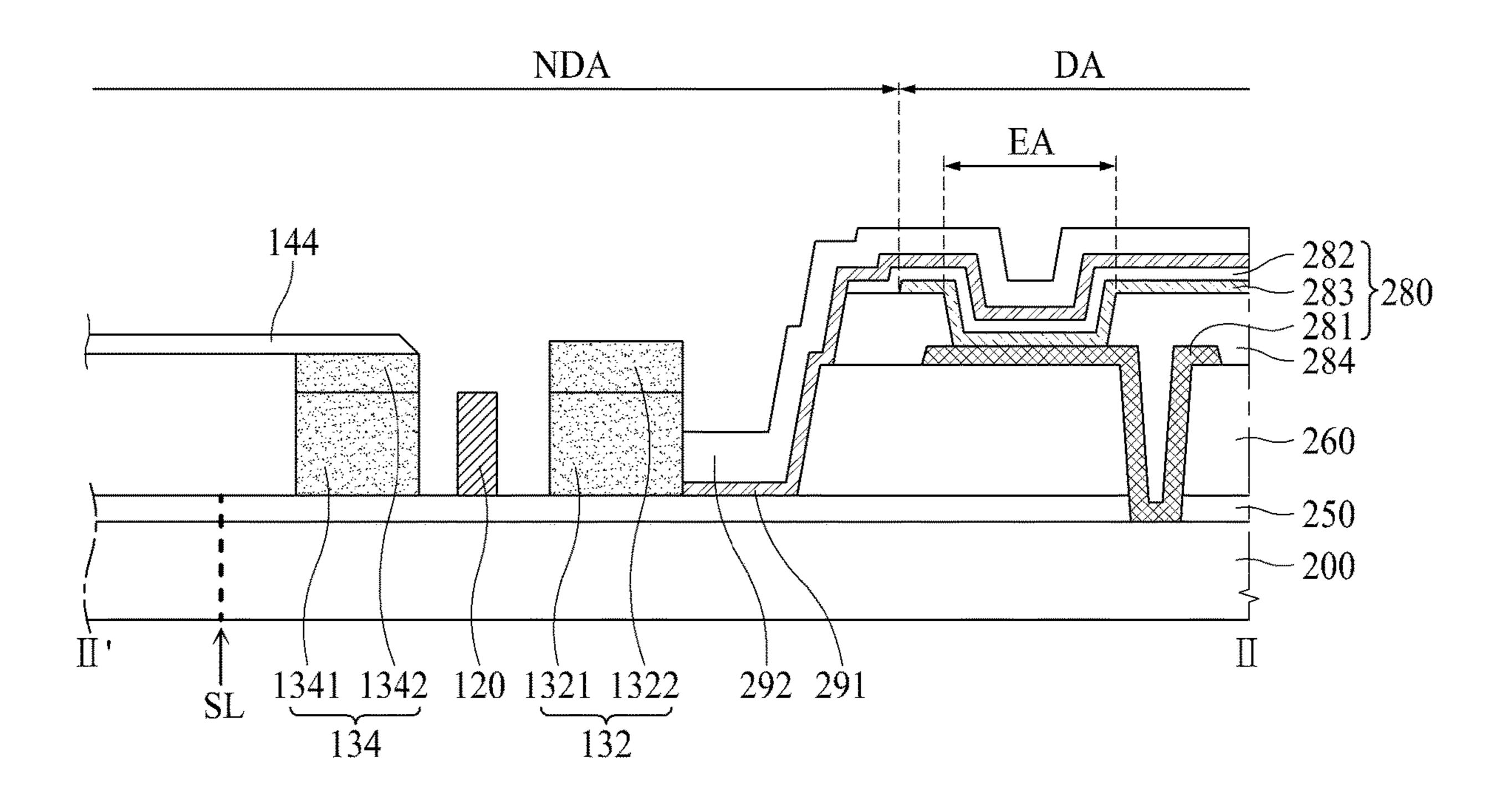

FIG. 8 is a cross-sectional view taken along line II-II' of FIG. 6;

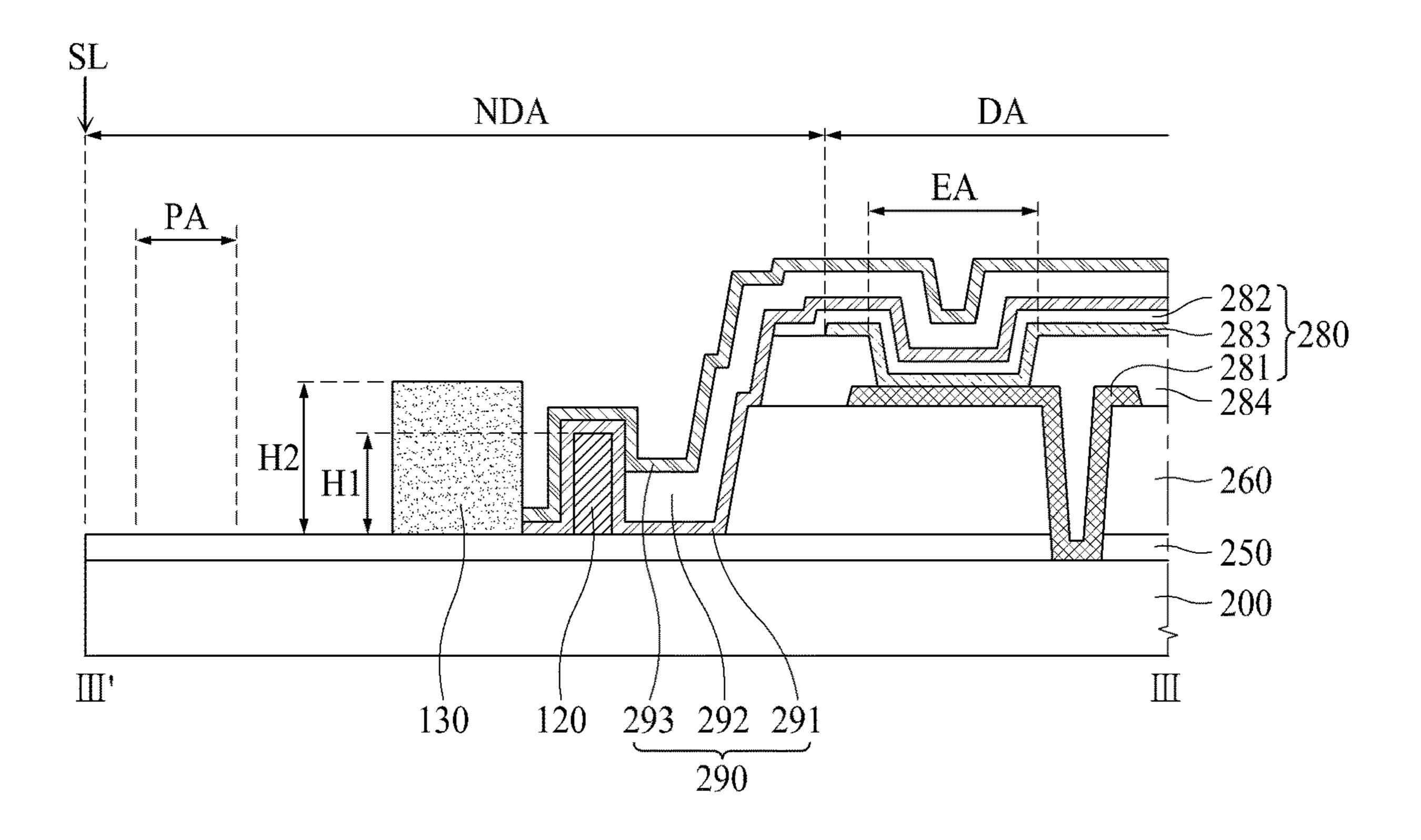

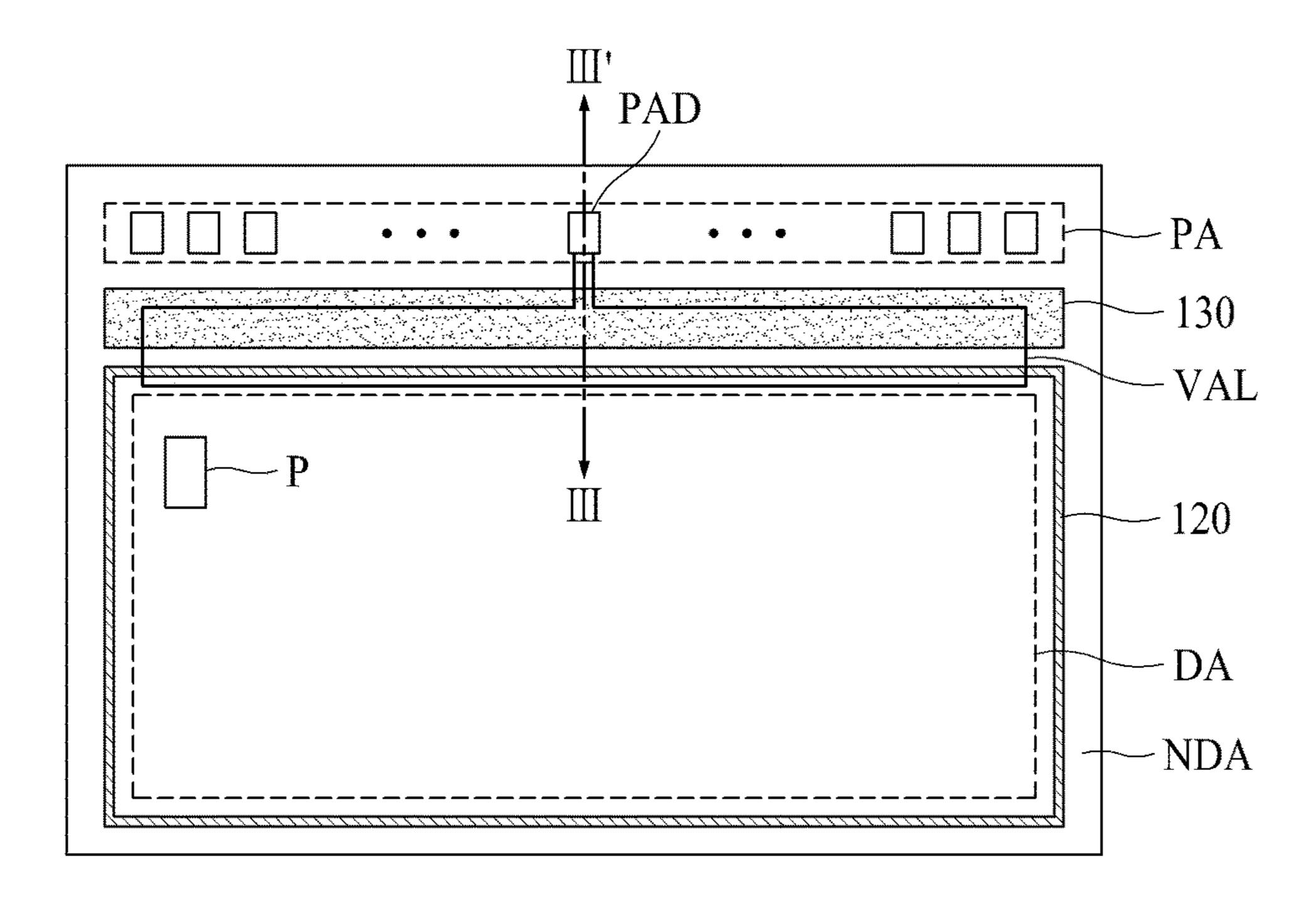

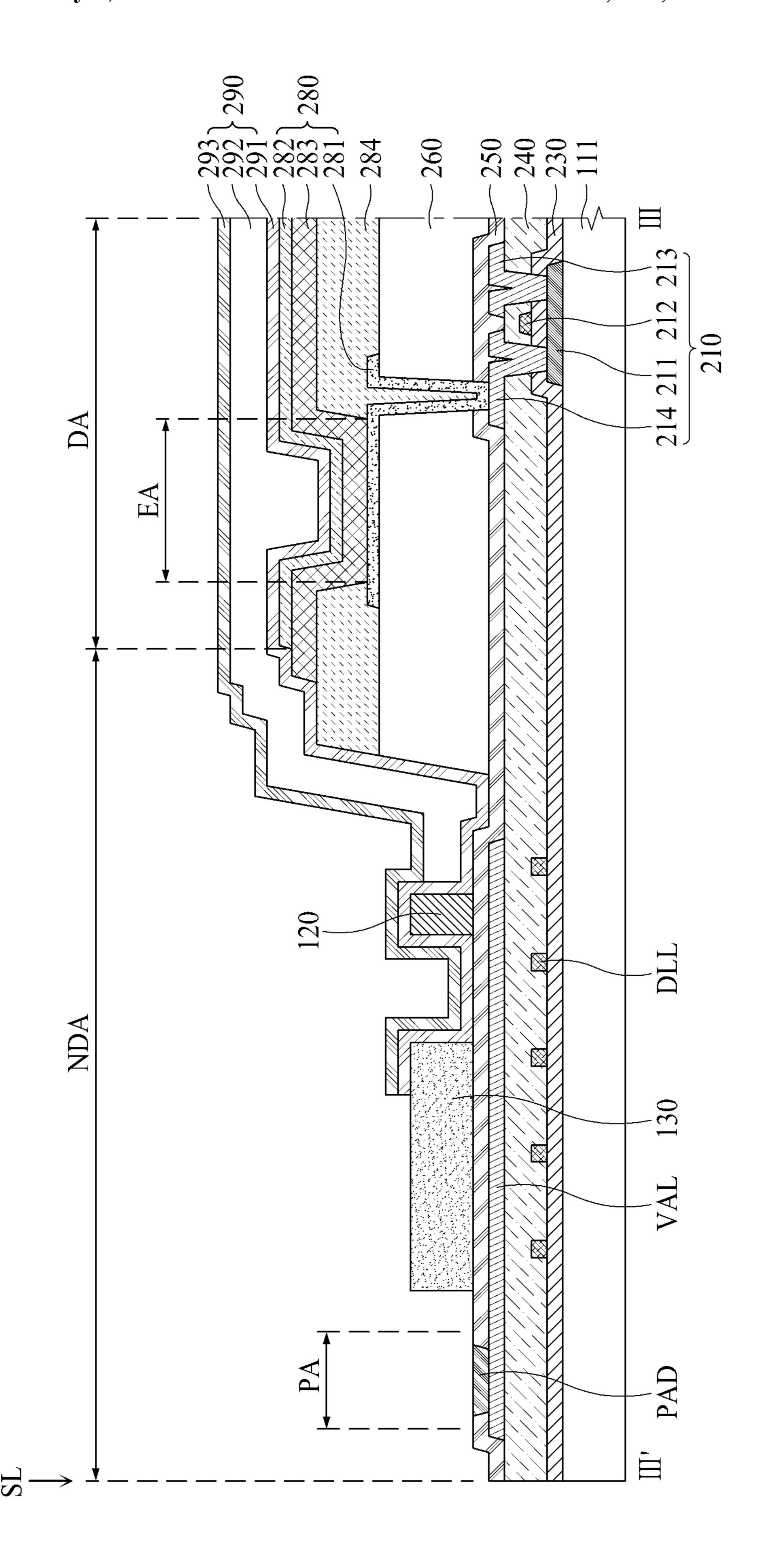

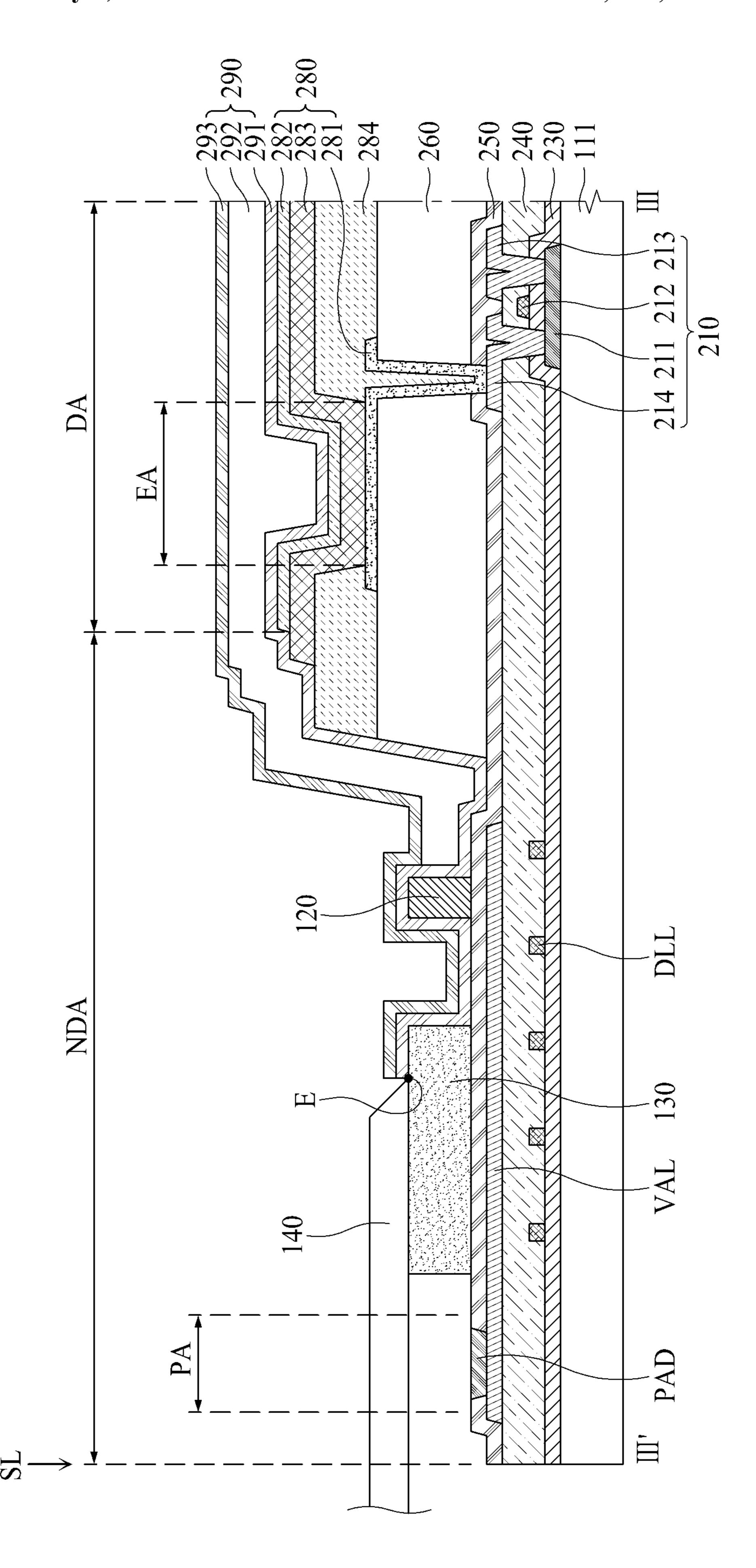

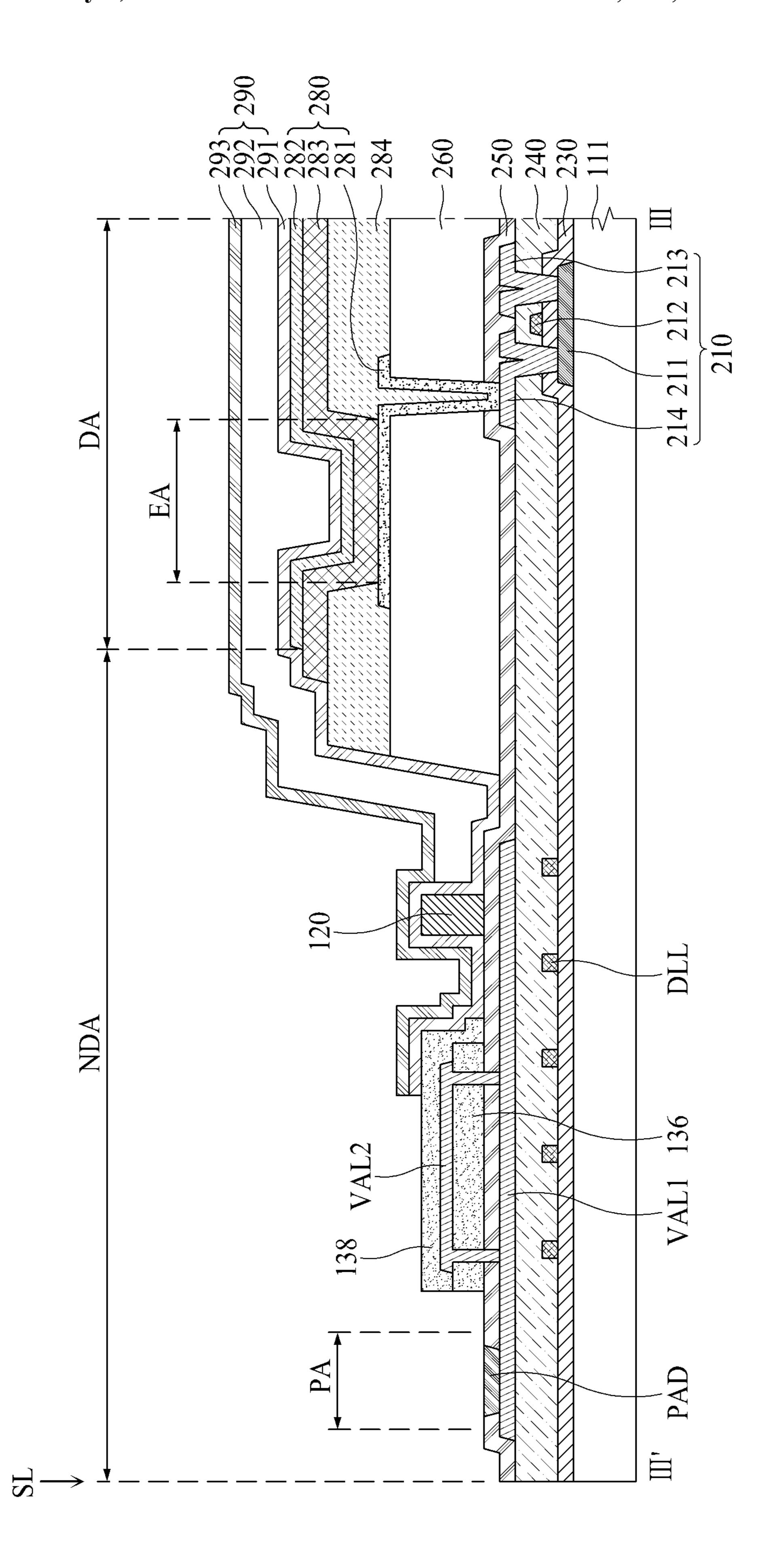

FIG. 9 is a cross-sectional view taken along line III-III' of FIG. 6;

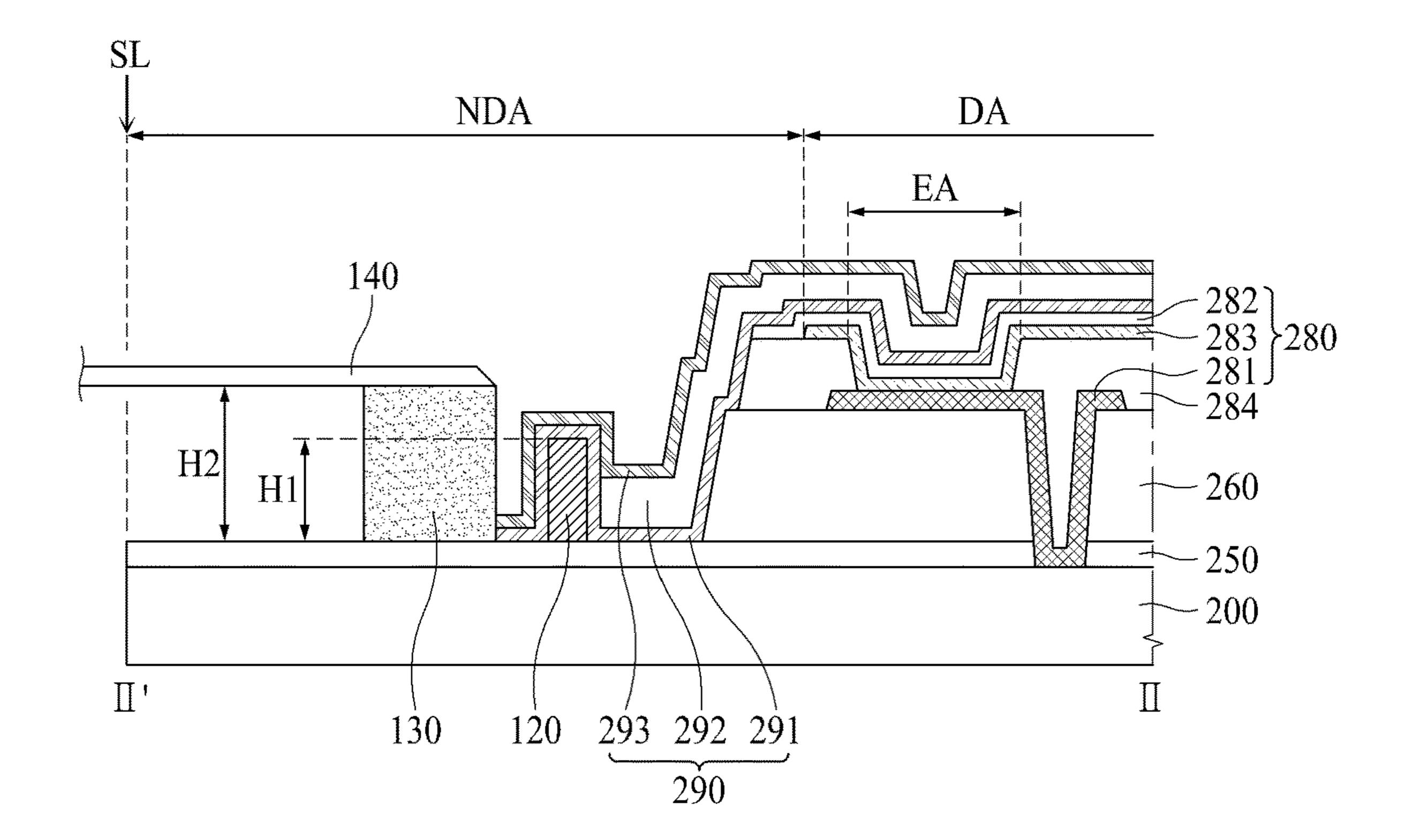

FIG. 10 is a cross-sectional view illustrating an example where a mask is disposed on a buffer layer of FIG. 8;

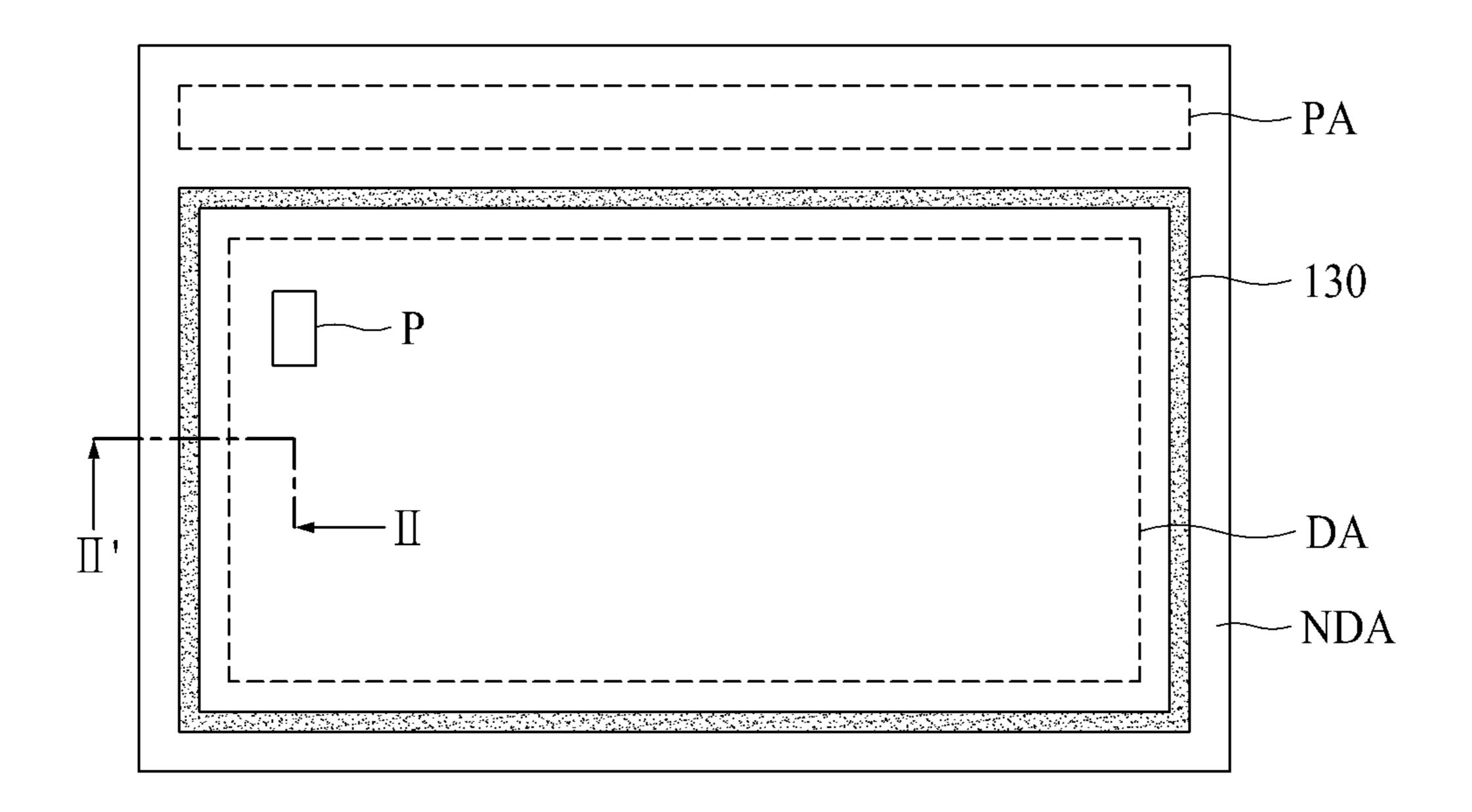

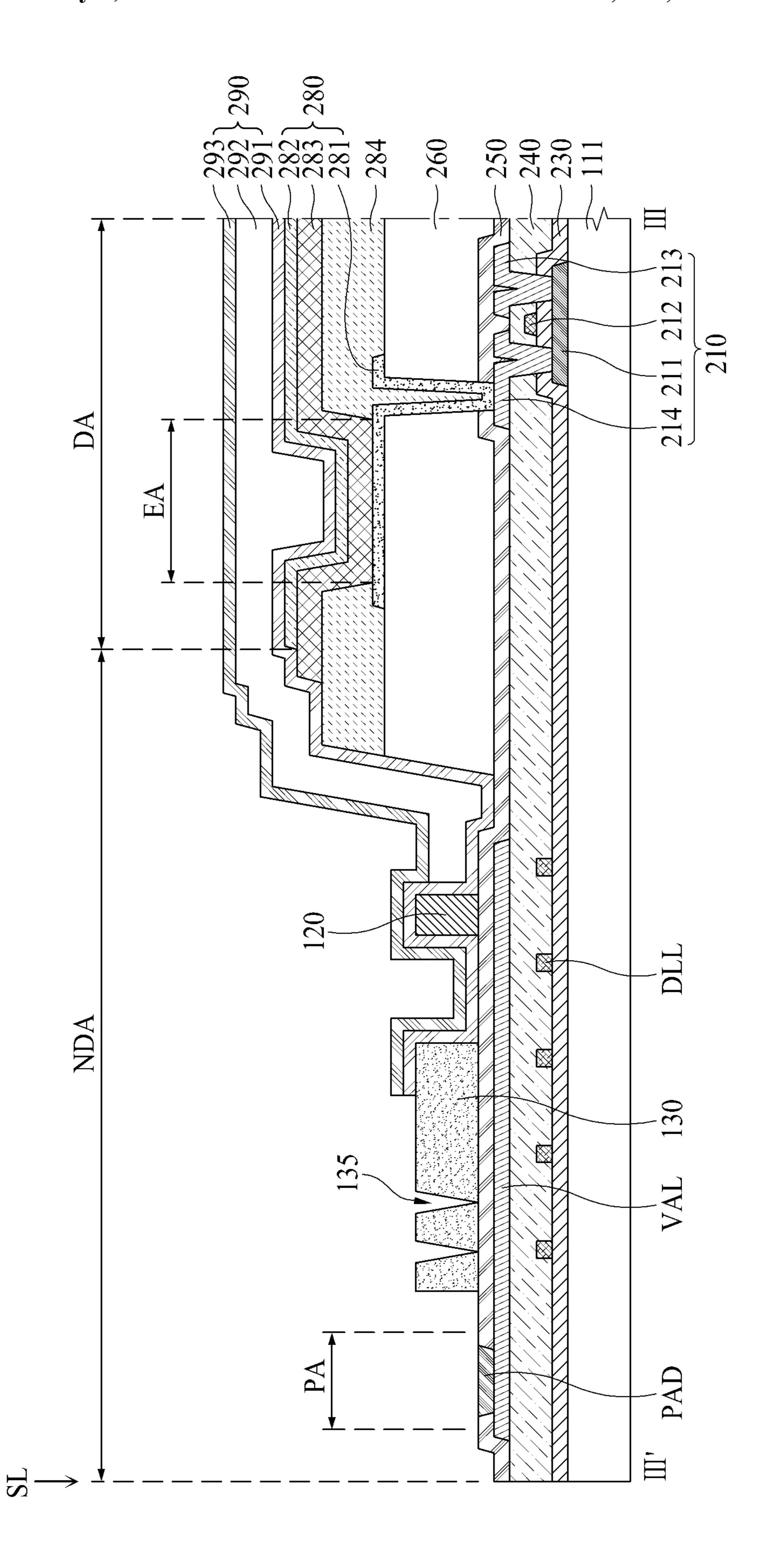

FIG. 11 is a plan view illustrating a first substrate of a display apparatus according to a second embodiment of the present disclosure;

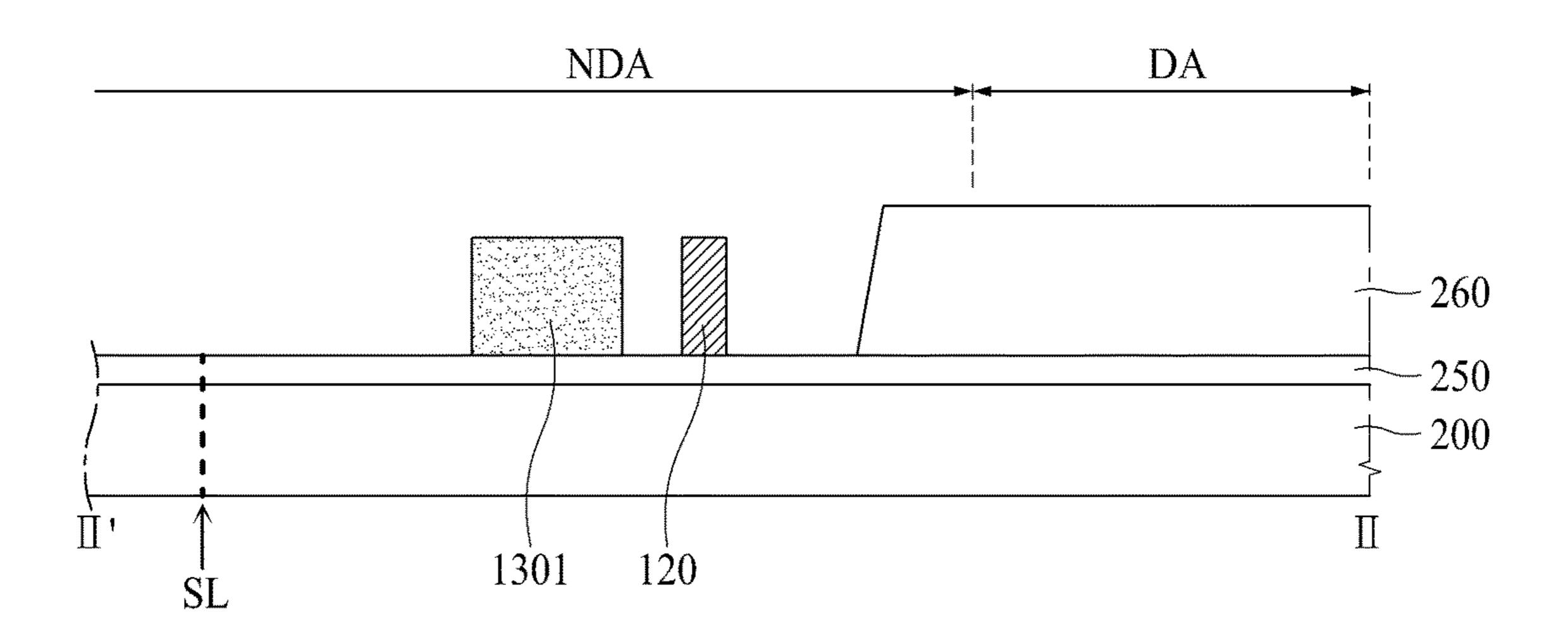

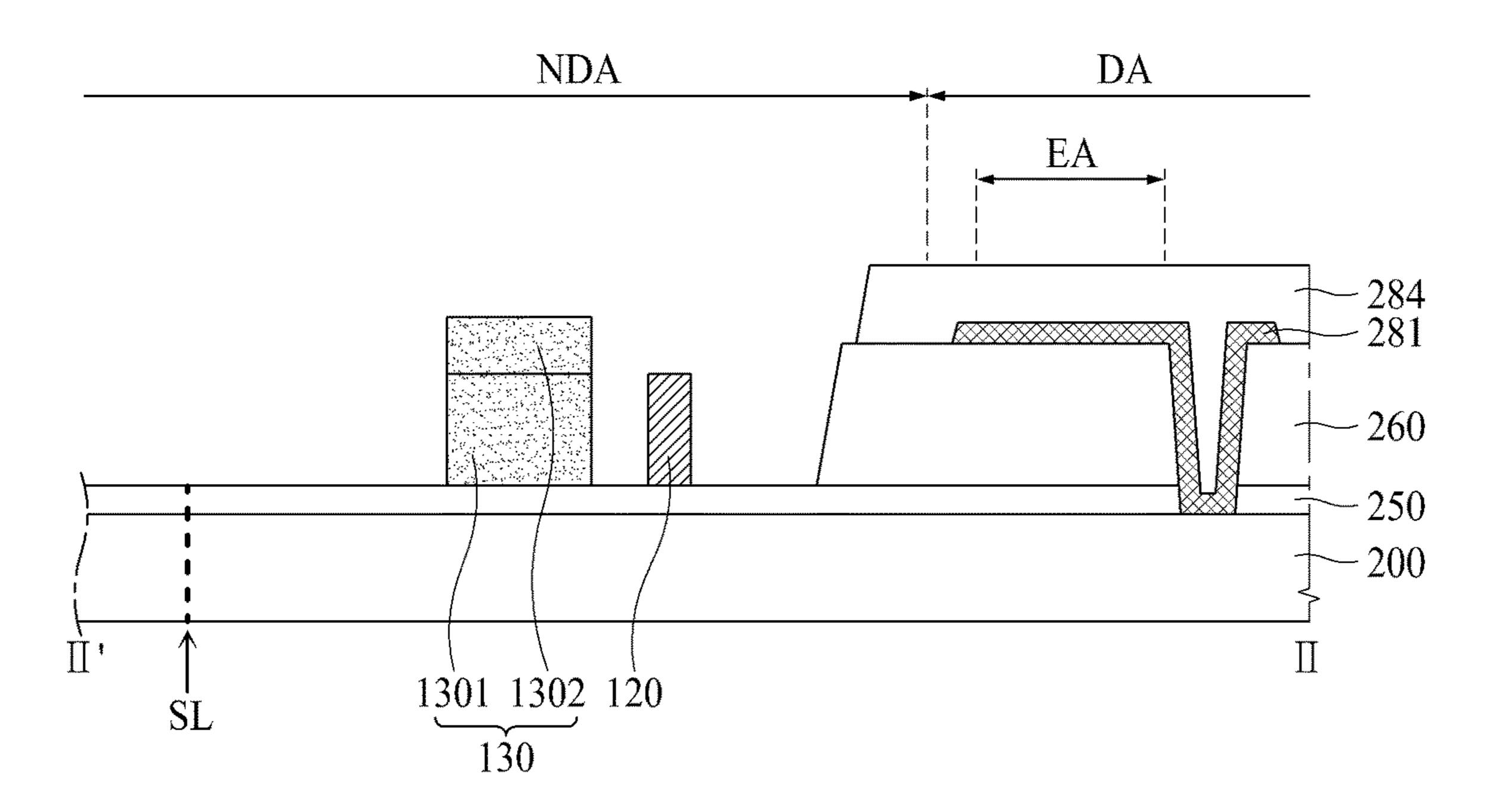

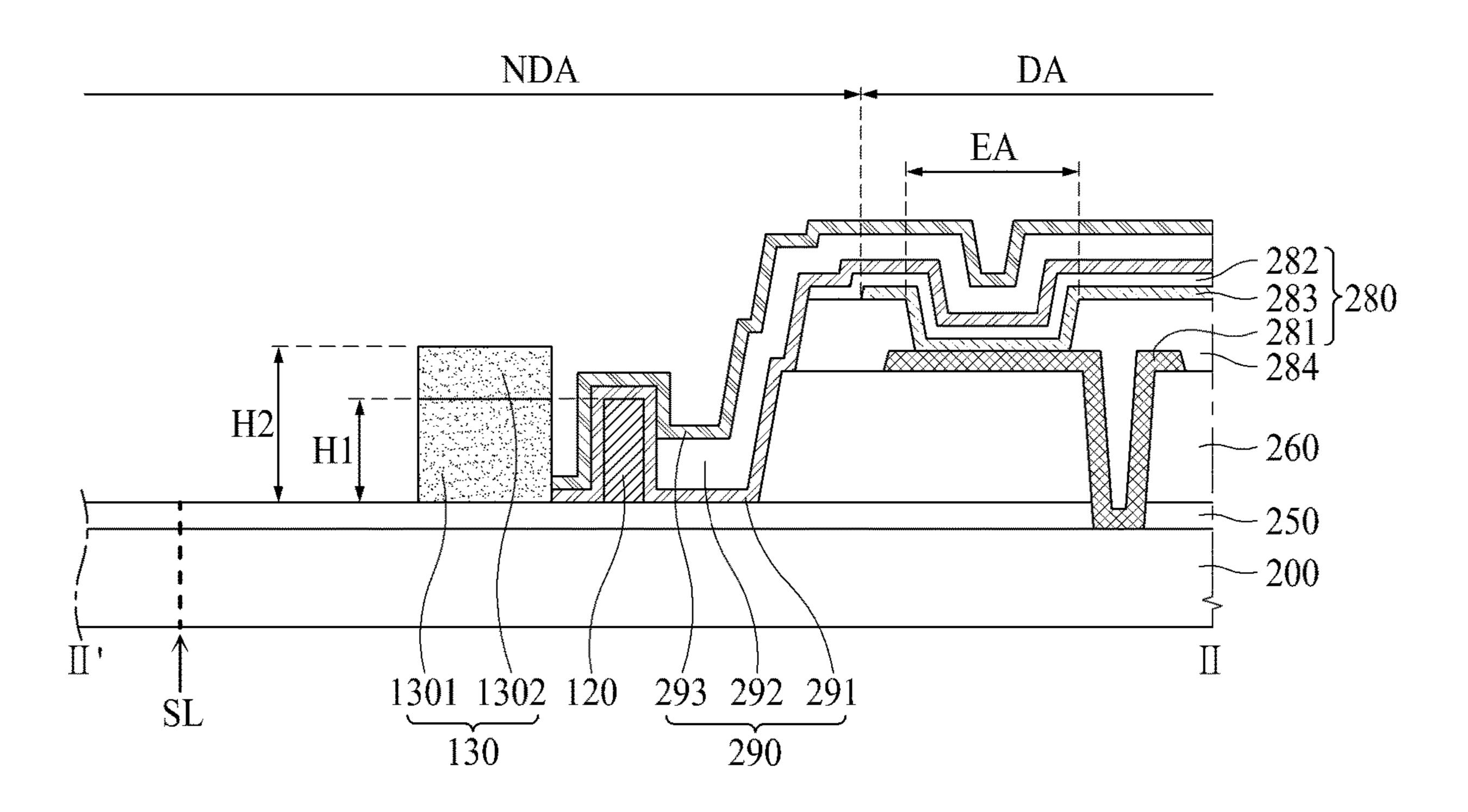

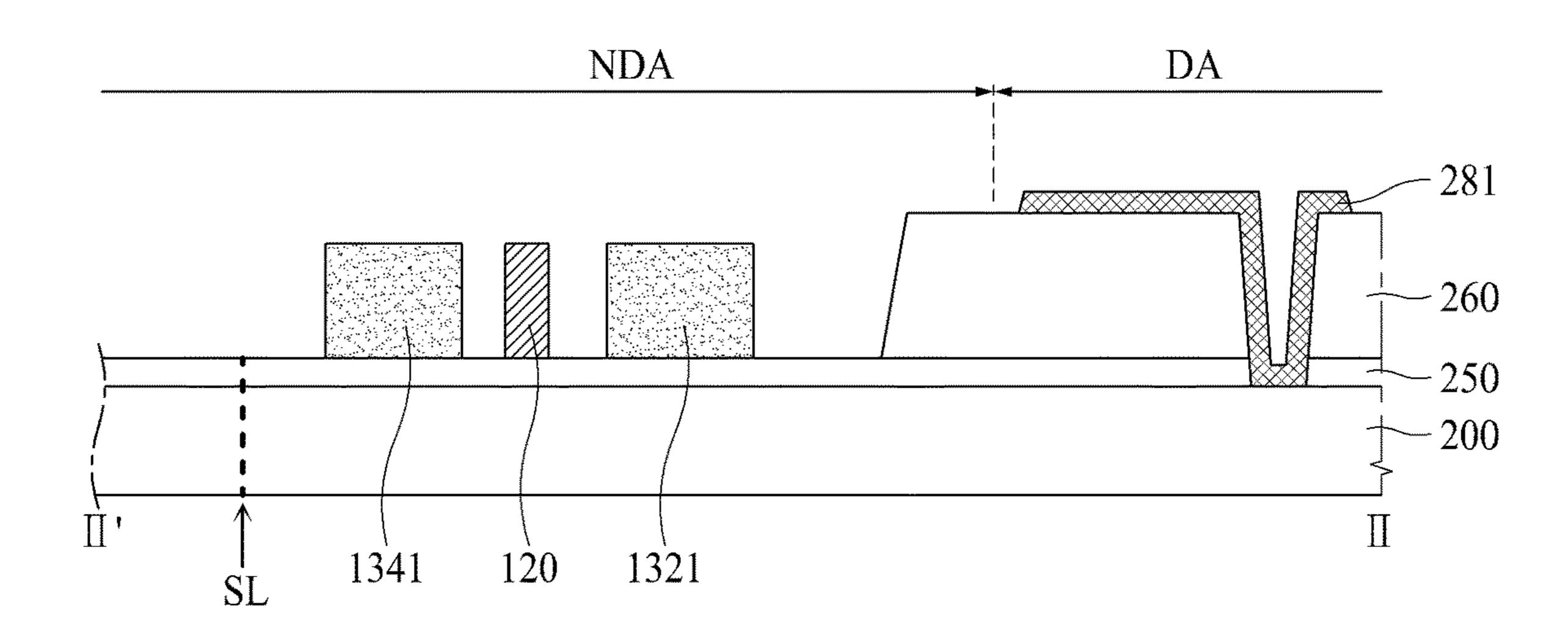

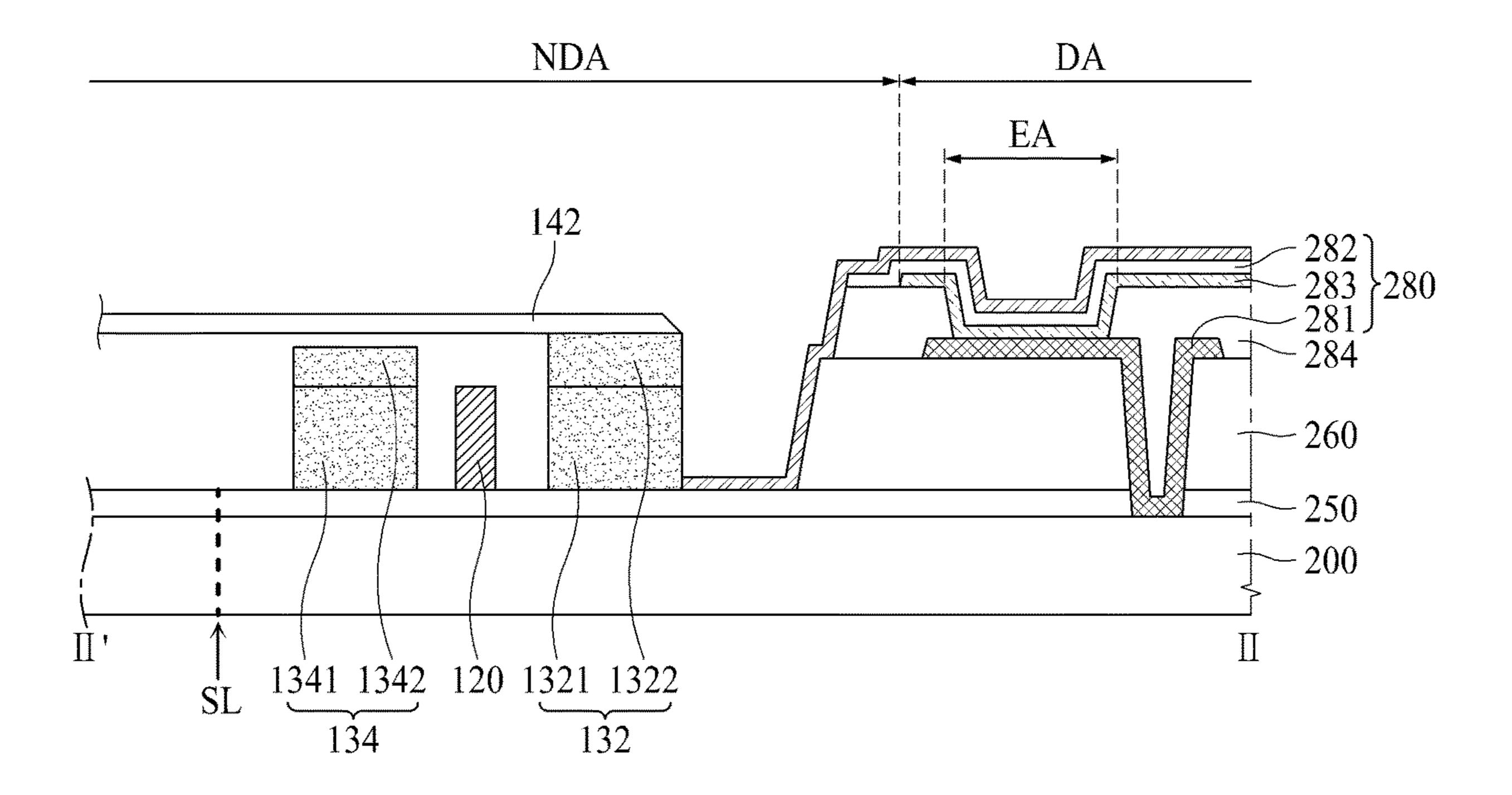

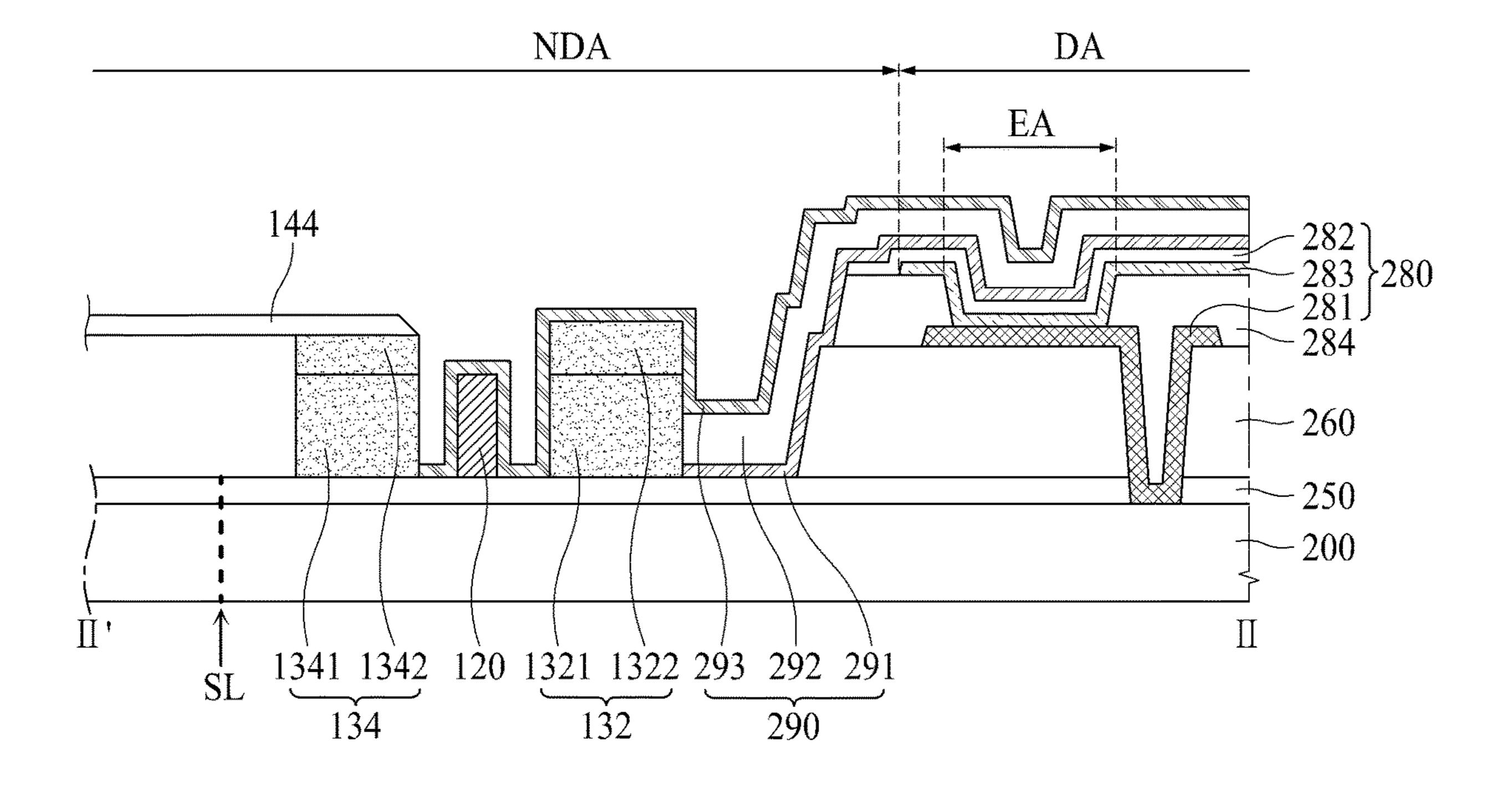

FIG. 12 is a cross-sectional view taken along line II-II' of FIG. 11;

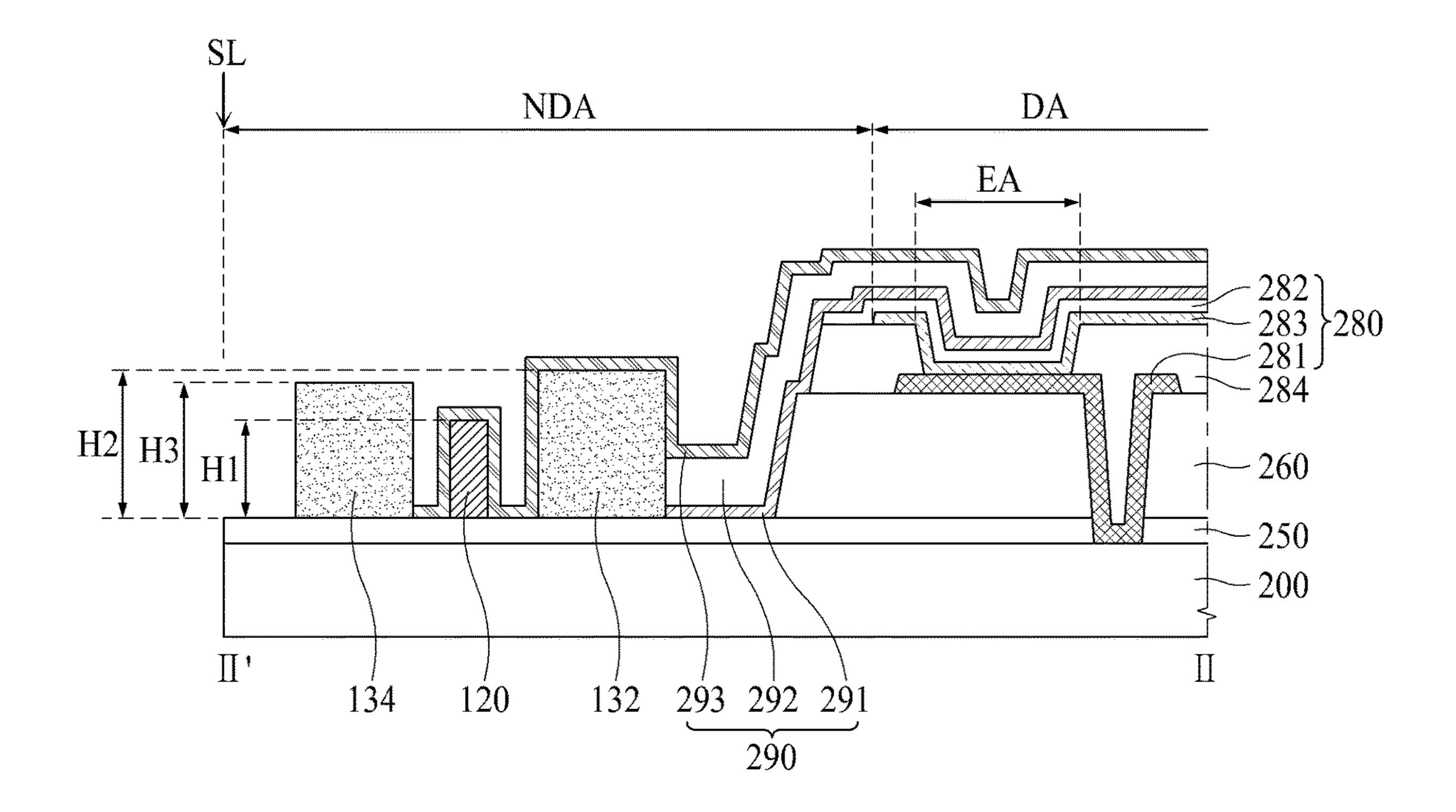

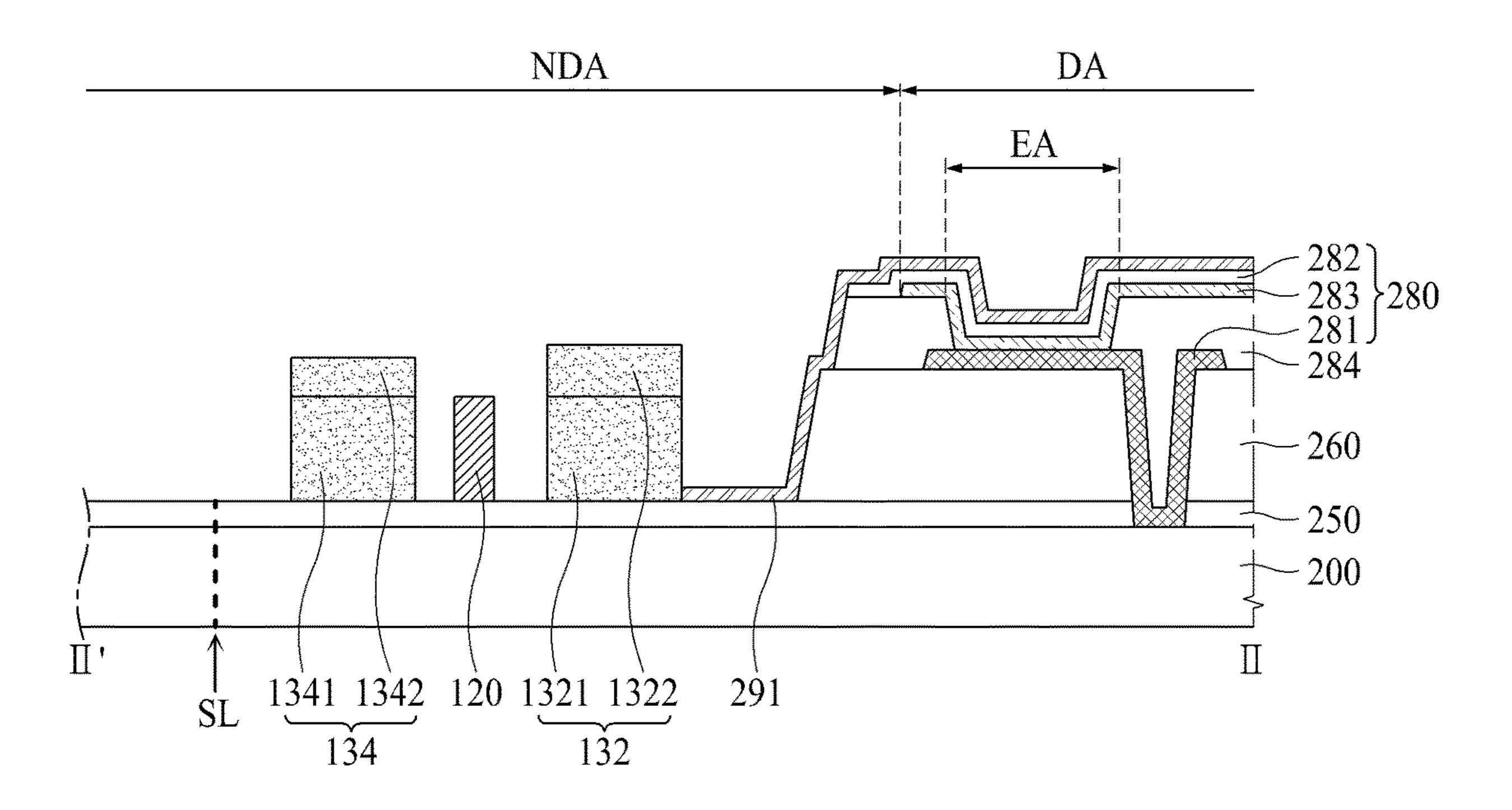

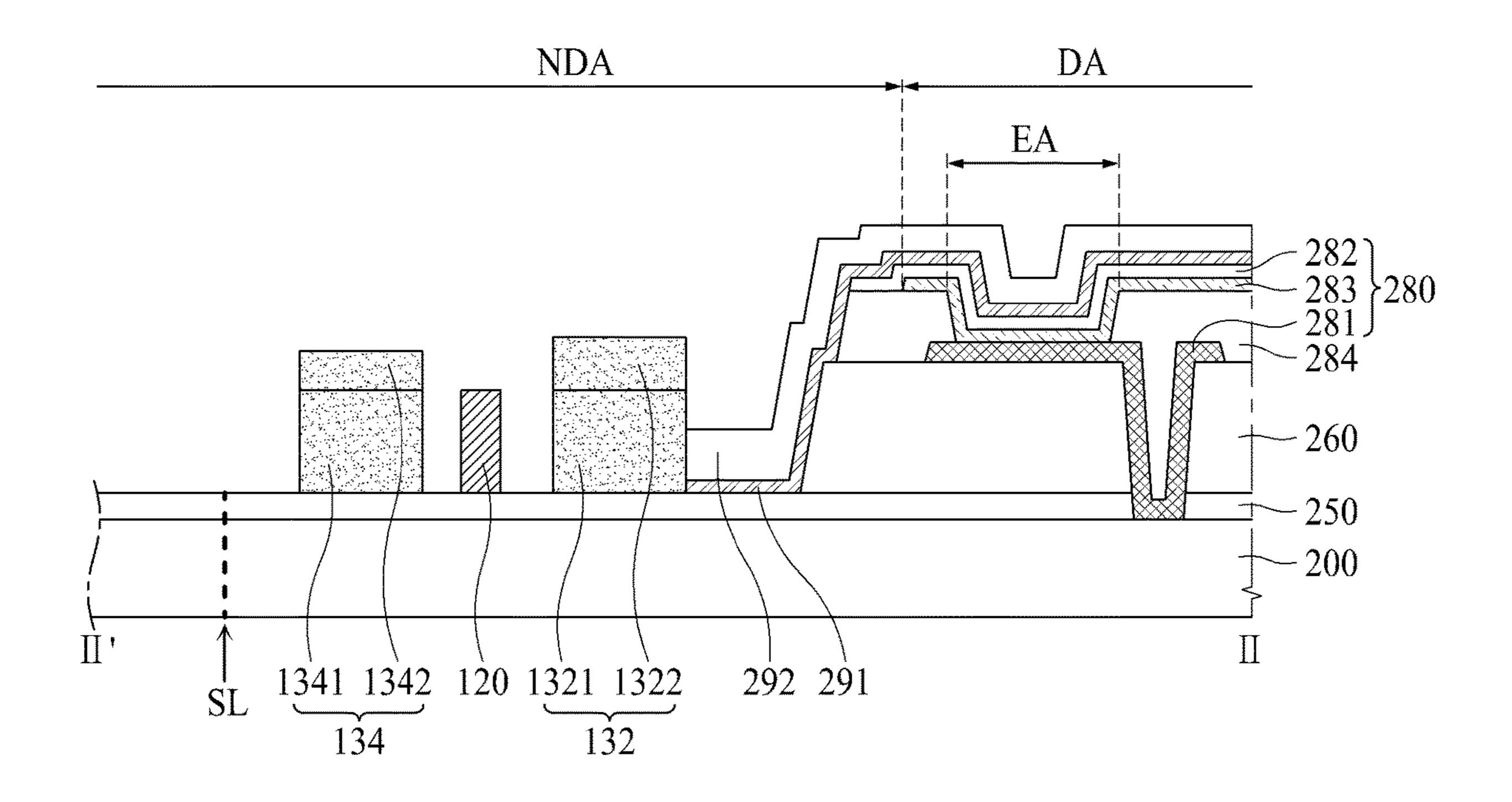

FIG. 13 is a plan view illustrating a first substrate of a display apparatus according to a third embodiment of the present disclosure;

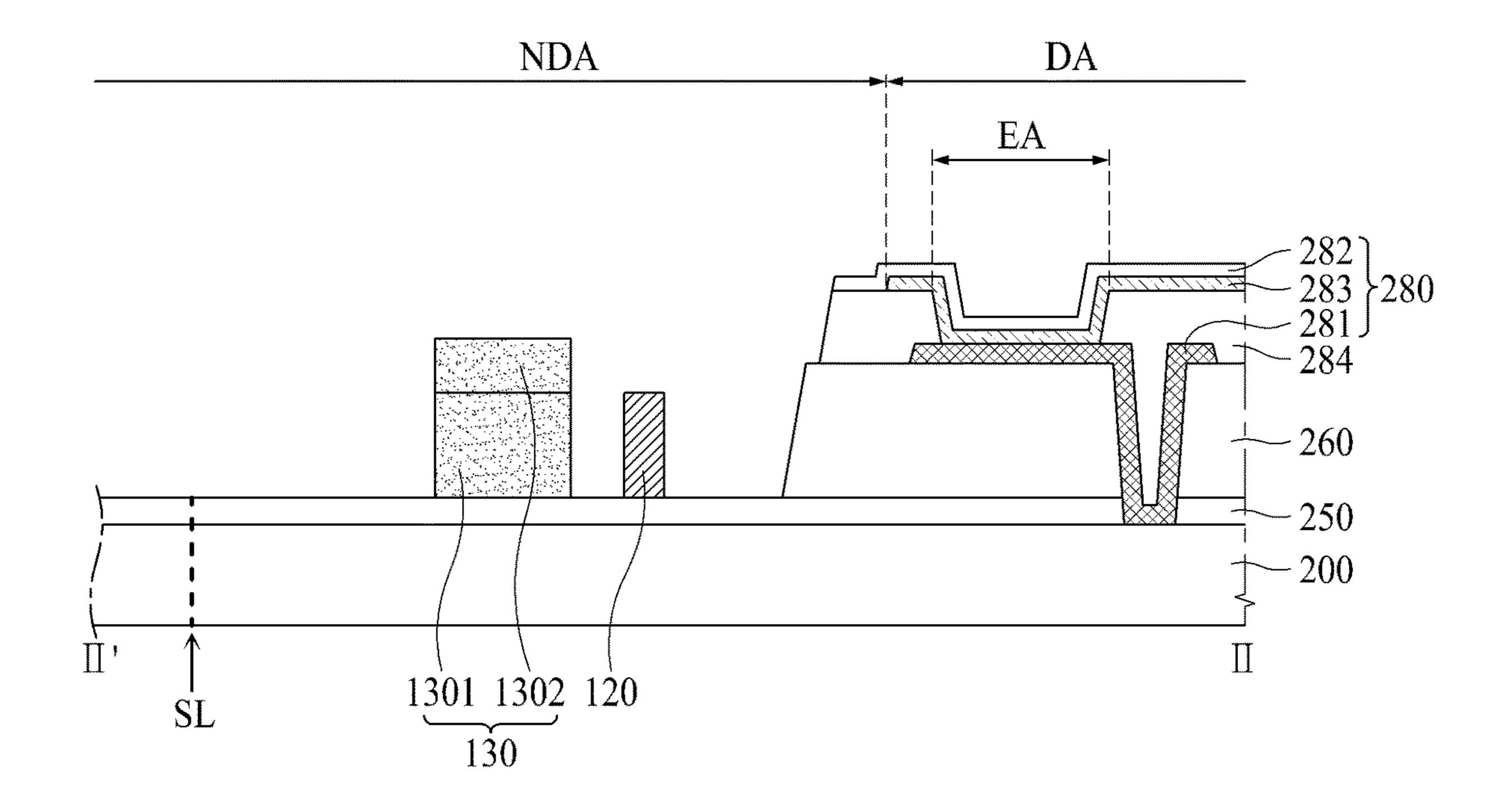

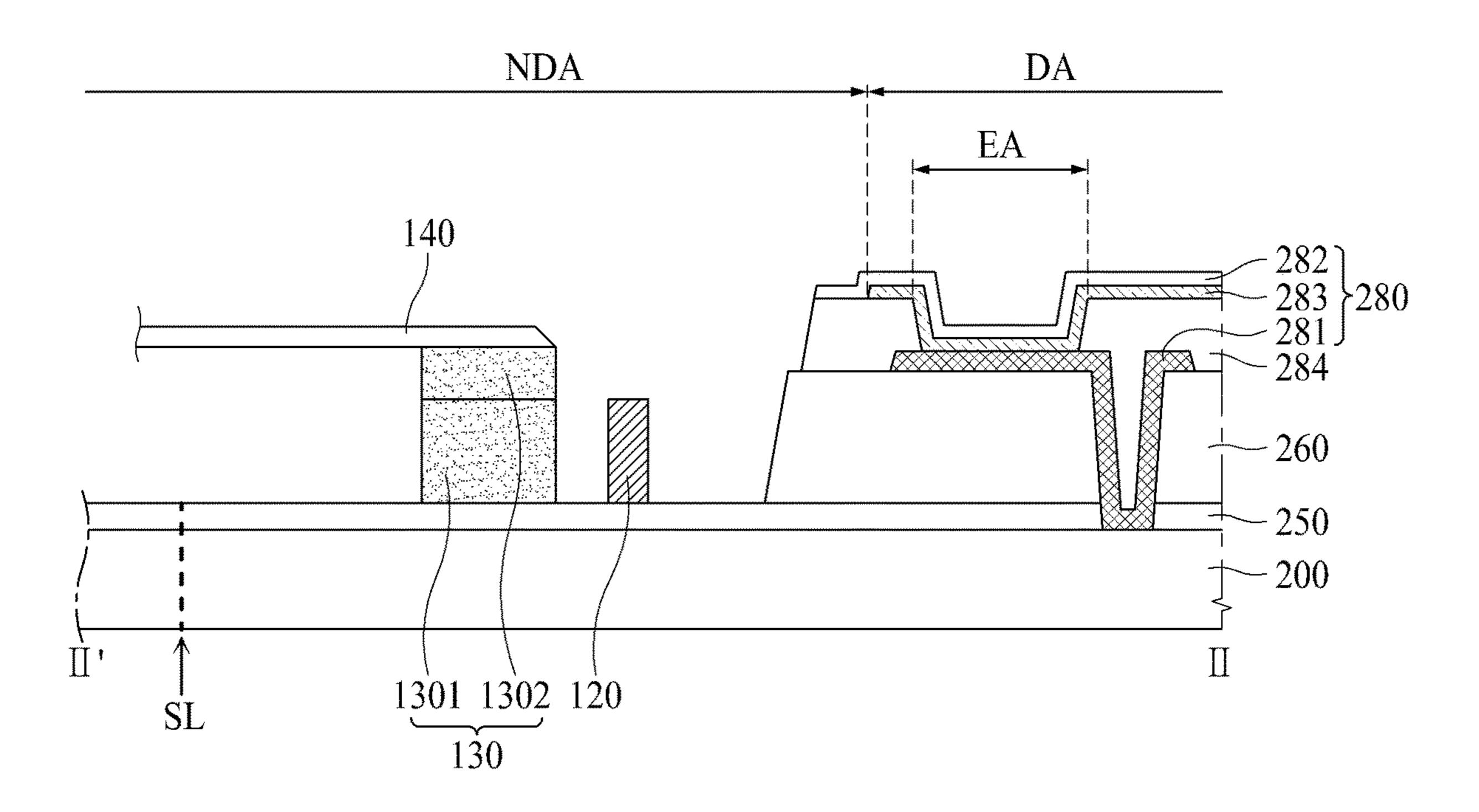

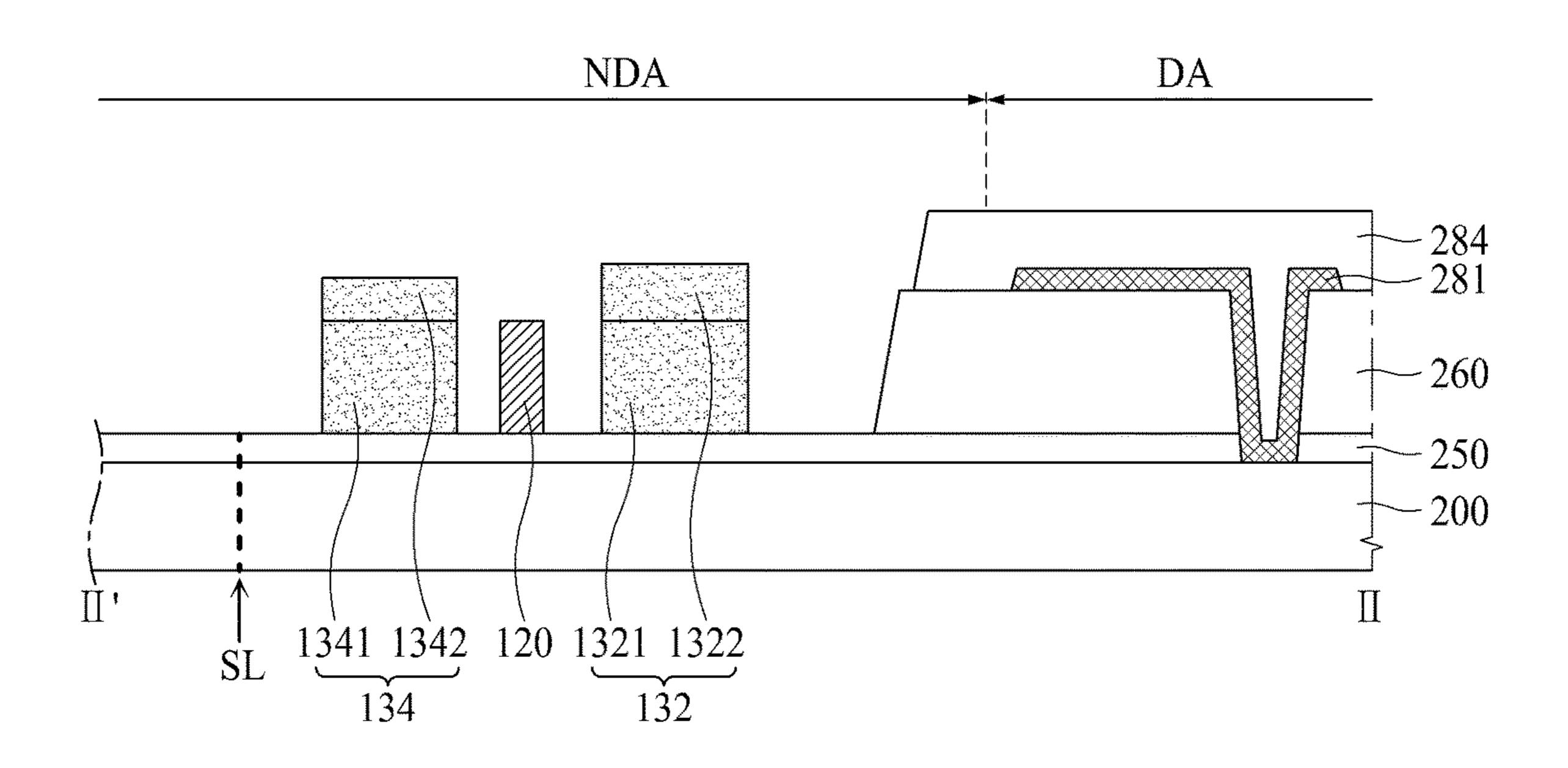

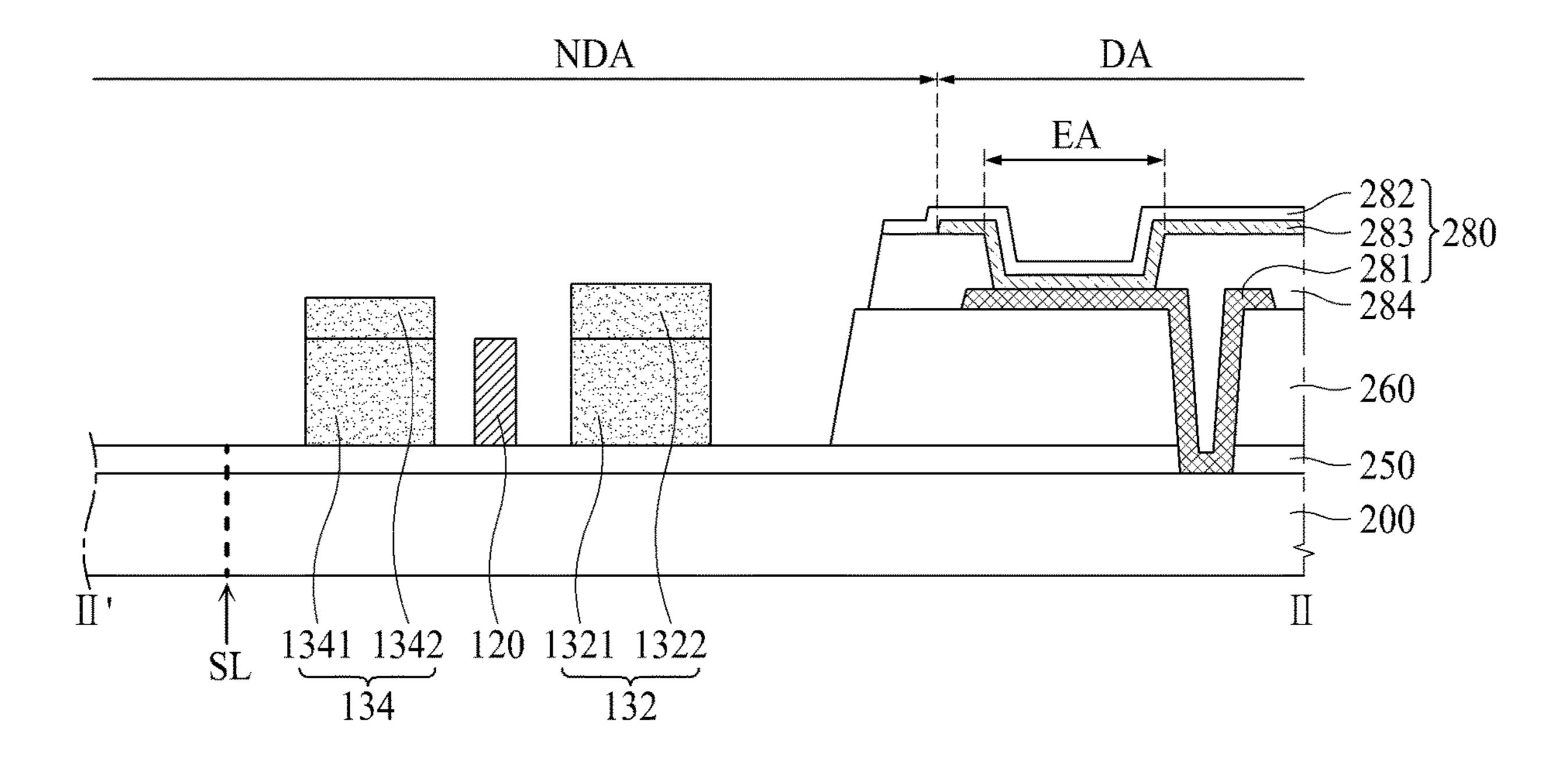

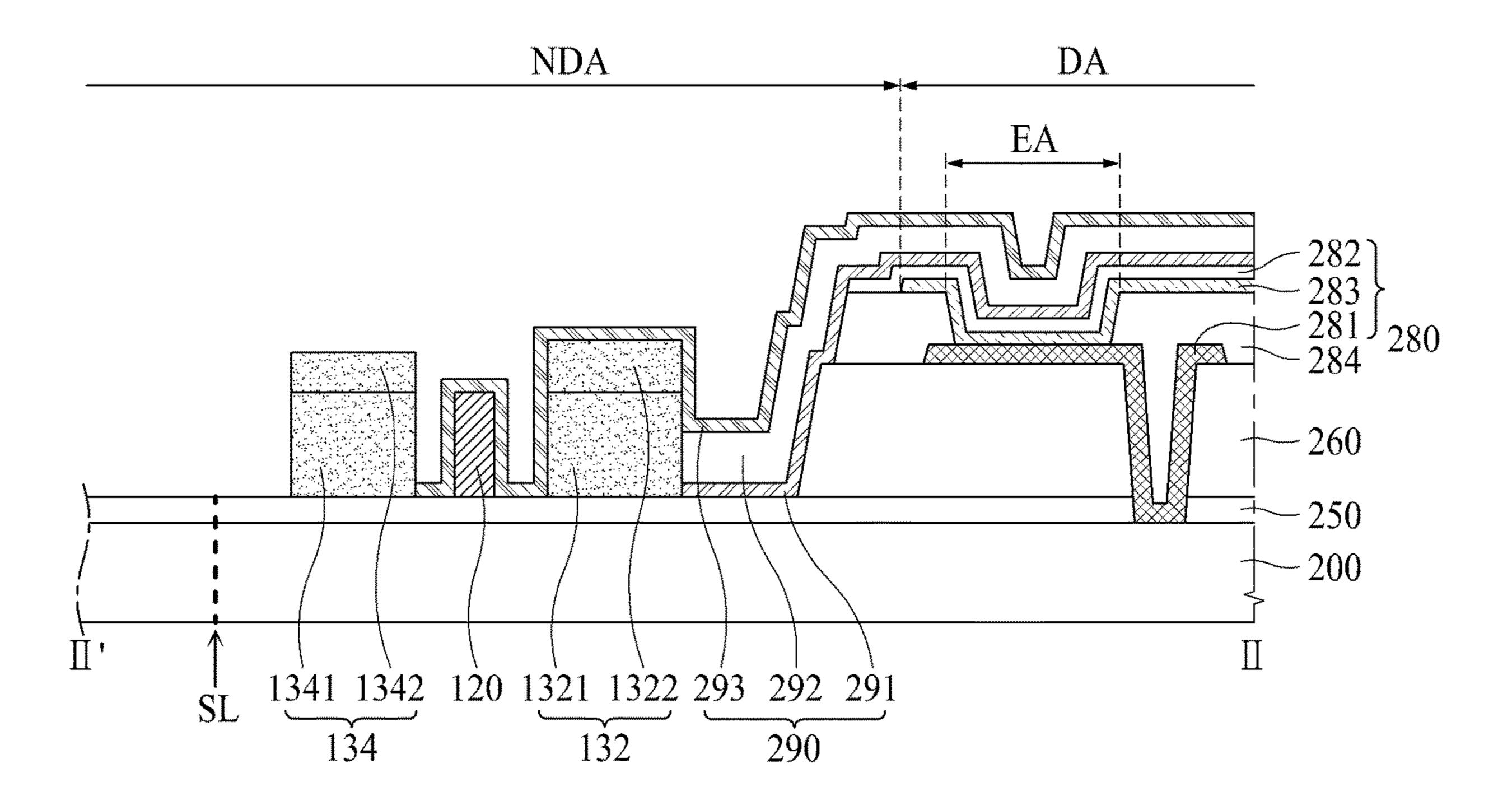

FIG. 14 is a cross-sectional view taken along line II-II' of FIG. 13;

5

FIG. 15 is a plan view illustrating a first substrate of a display apparatus according to a fourth embodiment of the present disclosure;

FIG. 16 is a cross-sectional view taken along line II-II' of FIG. 15;

FIG. 17 is a plan view illustrating a first substrate of a display apparatus according to a fifth embodiment of the present disclosure;

FIG. 18 is a plan view illustrating a first substrate of a display apparatus according to a sixth embodiment of the present disclosure;

FIG. 19 is a cross-sectional view taken along line III-III' of FIG. 18;

FIG. 20 is a cross-sectional view illustrating an example where a mask is disposed on a buffer layer of FIG. 19;

FIG. 21 is a cross-sectional view illustrating a modification embodiment of FIG. 19;

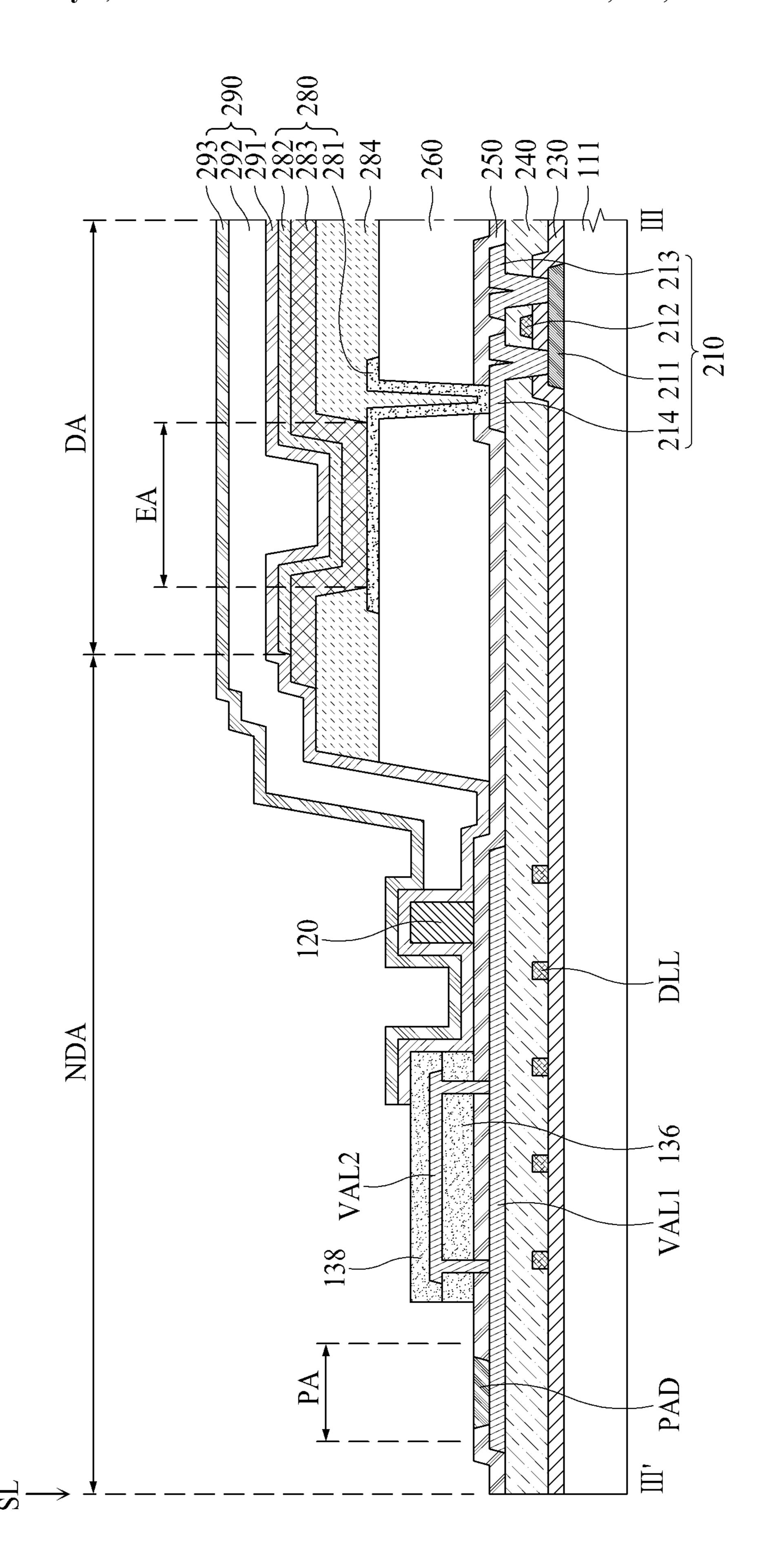

FIG. **22** is a plan view illustrating a first substrate of a display apparatus according to a seventh embodiment of the 20 present disclosure;

FIG. 23 is a cross-sectional view taken along line III-III' of FIG. 22;

FIG. 24 is a cross-sectional view illustrating a modification embodiment of FIG. 23;

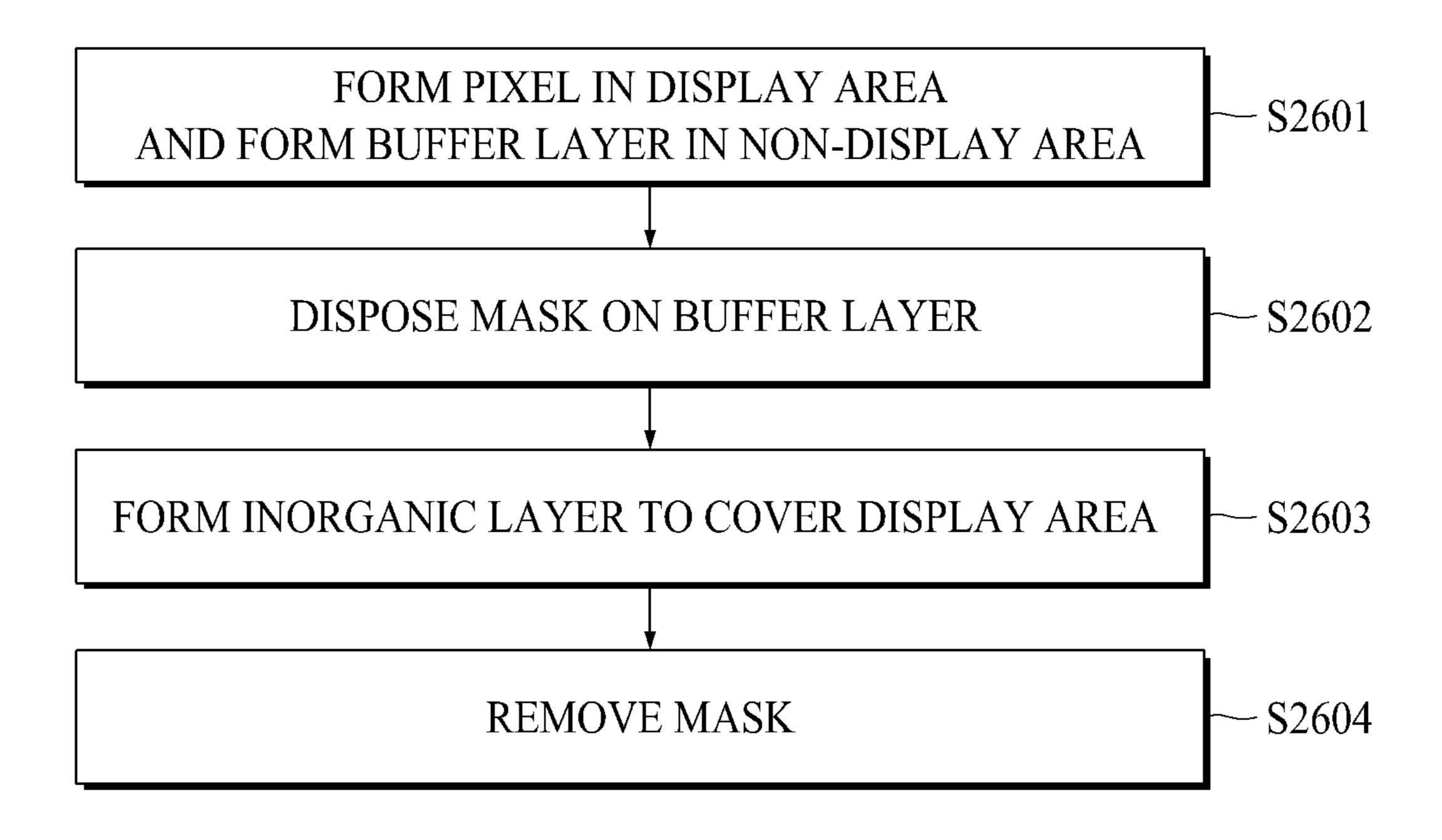

FIG. 25 is a flowchart for describing a method of manufacturing a display apparatus according to a first embodiment of the present disclosure;

FIGS. 26A to 26H are cross-sectional views for describing the method of manufacturing the display apparatus according to the first embodiment of the present disclosure;

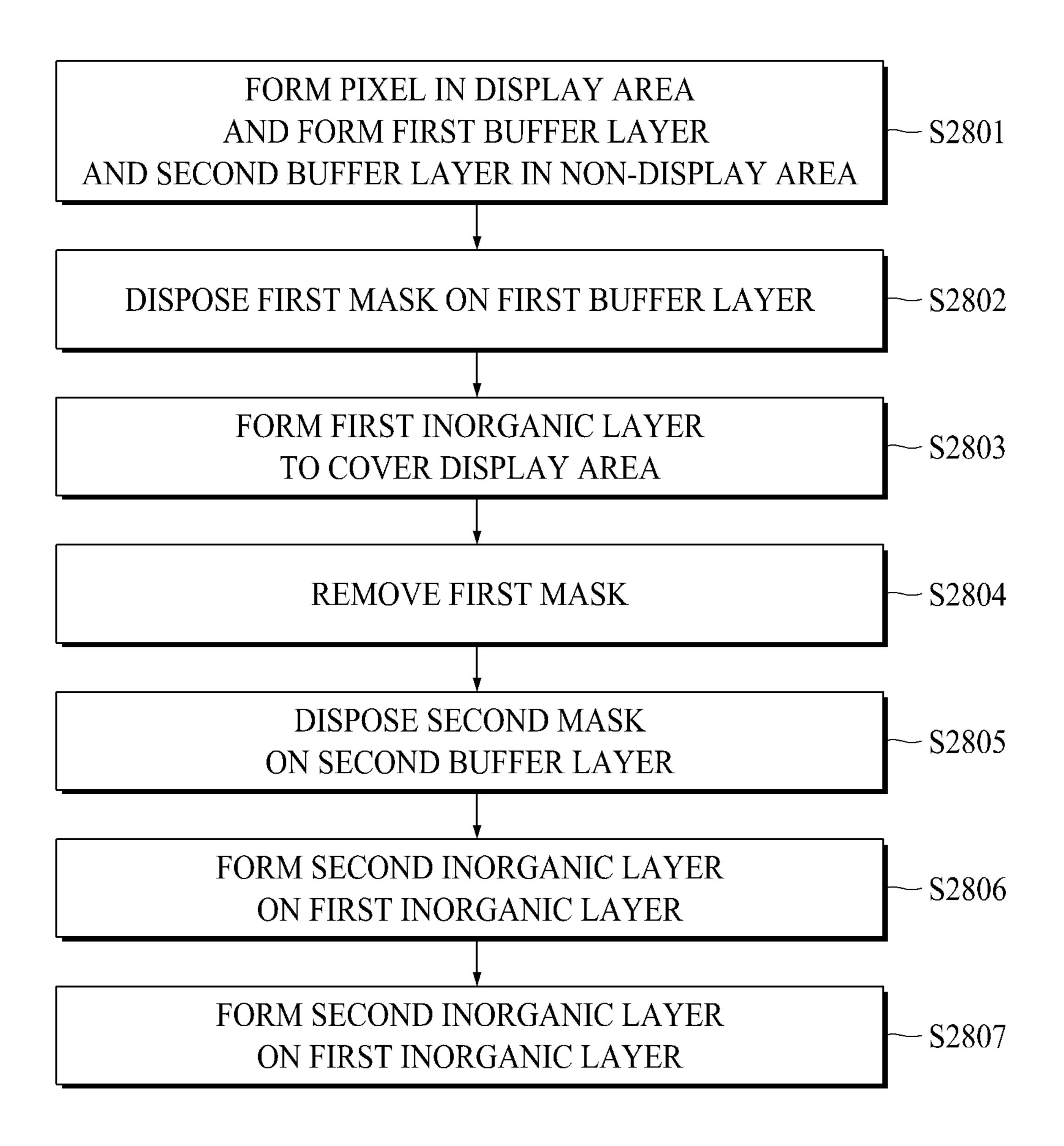

FIG. 27 is a flowchart for describing a method of manufacturing a display apparatus according to a second embodiment of the present disclosure;

FIGS. 28Å to 28L are cross-sectional views for describing the method of manufacturing the display apparatus according to the second embodiment of the present disclosure;

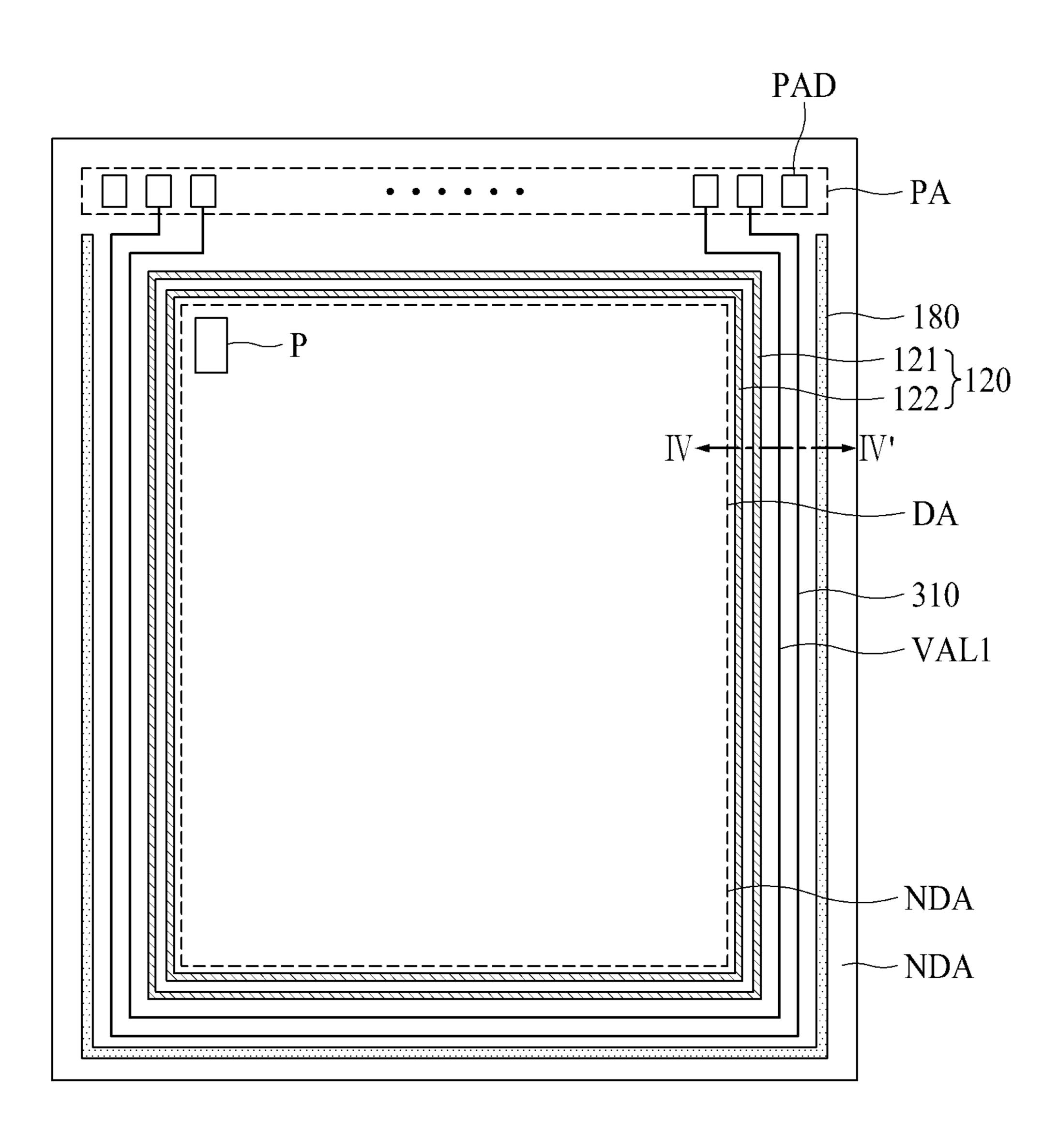

FIG. **29** is a plan view illustrating a first substrate of a display apparatus according to an eighth embodiment of the 40 present disclosure;

FIG. 30 is a cross-sectional view taken along line III-III' of FIG. 29;

FIG. 31 is a cross-sectional view taken along line II-II' of FIG. 29;

FIG. 32 is a plan view illustrating a first substrate of a display apparatus according to a ninth embodiment of the present disclosure; and

FIG. 33 is a cross-sectional view taken along line IV-IV' of FIG. 32.

### DETAILED DESCRIPTION OF THE DISCLOSURE

Reference will now be made in detail to the exemplary 55 embodiments of the present disclosure, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts.

Advantages and features of the present disclosure, and 60 implementation methods thereof will be clarified through following embodiments described with reference to the accompanying drawings. The present disclosure may, however, be embodied in different forms and should not be construed as limited to the embodiments set forth herein. 65 Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey

6

the scope of the present disclosure to those skilled in the art. Further, the present disclosure is only defined by scopes of claims.

A shape, a size, a ratio, an angle, and a number disclosed in the drawings for describing embodiments of the present disclosure are merely an example, and thus, the present disclosure is not limited to the illustrated details. Like reference numerals refer to like elements throughout. In the following description, when the detailed description of the relevant known function or configuration is determined to unnecessarily obscure the important point of the present disclosure, the detailed description will be omitted.

In a case where 'comprise', 'have', and 'include' described in the present specification are used, another part can be added unless 'only~' is used. The terms of a singular form can include plural forms unless referred to the contrary.

In construing an element, the element is construed as including an error range although there is no explicit description.

In describing a position relationship, for example, when a position relation between two parts is described as 'on~', 'over~', 'under~', and 'next~', one or more other parts can be disposed between the two parts unless 'just' or 'direct' is used.

In describing a time relationship, for example, when the temporal order is described as 'after~', 'subsequent~', 'next~', and 'before~', a case which is not continuous can be included unless 'just' or 'direct' is used.

It will be understood that, although the terms "first", "second", etc. can be used herein to describe various elements, these elements should not be limited by these terms. These terms are only used to distinguish one element from another. For example, a first element could be termed a second element, and, similarly, a second element could be termed a first element, without departing from the scope of the present disclosure.

An X axis direction, a Y axis direction, and a Z axis direction should not be construed as only a geometric relationship where a relationship therebetween is vertical, and can denote having a broader directionality within a scope where elements of the present disclosure operate functionally.

The term "at least one" should be understood as including any and all combinations of one or more of the associated listed items. For example, the meaning of "at least one of a first item, a second item, and a third item" denotes the combination of all items proposed from two or more of the first item, the second item, and the third item as well as the first item, the second item, or the third item.

Features of various embodiments of the present disclosure can be partially or overall coupled to or combined with each other, and can be variously inter-operated with each other and driven technically as those skilled in the art can sufficiently understand. The embodiments of the present disclosure can be carried out independently from each other, or can be carried out together in co-dependent relationship.

Hereinafter, exemplary embodiments of the present disclosure will be described in detail with reference to the accompanying drawings.

FIG. 4 is a perspective view illustrating a display apparatus 100 according to an embodiment of the present disclosure. FIG. 5 is a plan view illustrating a first substrate, a source drive integrated circuit (IC), a flexible film, a circuit board, and a timing controller illustrated in FIG. 4. Hereinafter, an example where the display apparatus 100 according to an embodiment of the present disclosure is an organic light emitting display apparatus will be mainly described,

but the present disclosure is not limited thereto. For example, the display apparatus according to an embodiment of the present disclosure can be implemented as a liquid crystal display (LCD) apparatus, an electroluminescence display apparatus, a quantum dot lighting emitting diode, and an electrophoresis display apparatus, in addition to an organic light emitting display apparatus. All the components of the display apparatus according to all embodiments of the present disclosure are operatively coupled and configured.

Referring to FIGS. 4 and 5, the display apparatus 100 according to an embodiment of the present disclosure can include a display panel 110, a source drive IC 140, a flexible film 150, a circuit board 160, and a timing controller 170.

The display panel 110 can include a first substrate 111 and a second substrate 112. The second substrate 112 can be an 15 encapsulation substrate. The first substrate 111 can be a plastic film or a glass substrate, but is not limited thereto. The second substrate 112 can be a plastic film, a glass substrate, or an encapsulation film, but is not limited thereto.

A plurality of gate lines, a plurality of data lines, and a plurality of pixels can be provided on one surface of the first substrate 111 facing the second substrate 112. The plurality of pixels can be respectively provided in a plurality of areas defined by an intersection structure of the gate lines and the data lines.

Each of the pixels can include a thin film transistor (TFT) and a light emitting device including a first electrode, a light emitting layer, and a second electrode. When a gate signal is input through a corresponding gate line by using the TFT, each of the pixels can supply a current to the light emitting device with a data voltage of a corresponding data line. Therefore, the light emitting device of each pixel can emit light having certain brightness, based on the current. A structure of each pixel will be described below with reference to FIGS. 6 and 7.

The display panel 110, as in FIG. 5, can be divided into a display area DA where the pixels are provided to display an image and a non-display area NDA which does not display an image. The gate lines, the data lines, and the pixels can be provided in the display area DA. A gate driver 40 and a plurality of pads can be provided in the non-display area NDA.

The gate driver can supply gate signals to the gate lines according to a gate control signal input from the timing controller 170. The gate driver can be provided as a gate 45 driver in panel (GIP) type in the non-display area NDA outside one side or both sides of the display area DA of the display panel 110. Alternatively, the gate driver can be manufactured as a driving chip, mounted on the flexible film, and attached on the non-display area NDA outside the 50 one side or both sides of the display area DA of the display panel 110 in a tape automated bonding (TAB) type.

The source driver IC 140 can receive digital video data and a source control signal from the timing controller 170. The source drive IC 140 can convert the digital video data 55 into analog data voltages according to the source control signal and can supply the analog data voltages to the data lines. When the source drive IC 140 is manufactured as a driving chip, the source drive IC 140 can be mounted on the flexible film 150 in a chip on film (COF) type or a chip on 60 plastic (COP) type.

The plurality of pads such as data pads can be provided in the non-display area NDA of the display panel 110. A plurality of lines for connecting the pads to the source drive IC 140 and a plurality of lines for connecting the pads to 65 lines of the circuit board 160 can be provided on the flexible film 150. The flexible film 150 can be attached on the pads

8

by using an anisotropic conductive film, and thus, the pads can be connected to the lines of the circuit board 330.

The circuit board 160 can be attached on the flexible film 150 which is provided in plurality. A plurality of circuits implemented as driving chips can be mounted on the circuit board 160. For example, the timing controller 170 can be mounted on the circuit board 160. The circuit board 160 can be a printed circuit board (PCB) or a flexible PCB (FPCB).

The timing controller 170 can receive digital video data and a timing signal from an external system through a cable of the circuit board 160. The timing controller 170 can generate the gate control signal for controlling an operation timing of the gate driver and the source control signal for controlling the source drive IC 140 which is provided in plurality, based on the timing signal. The timing controller 170 can supply the gate control signal to the gate driver and can supply the source control signal to the source drive ICs 140.

### First Embodiment

FIG. 6 is a plan view illustrating an example of the first substrate 111 according to a first embodiment of the present disclosure.

Referring to FIG. 6, the first substrate 111 can be divided into a display area DA and a non-display area NDA. A pad area PA where a plurality of pads are provided, a dam 120, and a buffer layer 130 can be provided in the non-display area NDA.

A plurality of pixels P for displaying an image can be provided in the display area DA. Each of the pixels P can include a TFT and a light emitting device including a first electrode, a light emitting layer, and a second electrode. When a gate signal is input through a corresponding gate line by using the TFT, each of the pixels P can supply a current to the light emitting device with a data voltage of a corresponding data line. Therefore, the light emitting device of each pixel P can emit light having certain brightness, based on the current.

Hereinafter, a structure of a pixel P in a display area DA according to embodiments of the present disclosure will be described in detail with reference to FIG. 7.

FIG. 7 is a cross-sectional view taken along line I-I' of FIG. 6 and is a cross-sectional view illustrating an example of a pixel P in a display area.

Referring to FIG. 7, a plurality of TFTs 210 and a plurality of capacitors 220 can be provided on one surface of the first substrate 111 facing the second substrate 112.

A buffer layer can be provided on the first substrate 111, for protecting the TFTs 210 from water penetrating through the first substrate 111 vulnerable to penetration of water.

The TFTs 210 can each include an active layer 211, a gate electrode 212, a source electrode 213, and a drain electrode 214. In FIG. 7, the TFTs 210 are exemplarily illustrated as being provided as a top gate type where the gate electrode 212 is disposed on the active layer 211, but is not limited thereto. That is, the TFTs 210 can be provided as a bottom gate type where the gate electrode 212 is disposed under the active layer 211 or a double gate type where the gate electrode 212 is disposed both on and under the active layer 211.

The active layer 211 can be provided on the buffer layer of the first substrate 111. The active layer 211 can be formed of a silicon-based semiconductor material, an oxide-based semiconductor material, and/or the like. A light blocking layer for blocking external light incident on the active layer 211 can be provided on the first substrate 111.

A gate insulation layer 230 can be provided on the active layer 211. The gate insulation layer 230 can be formed of an inorganic layer, and for example, can be formed of silicon oxide (SiOx), silicon nitride (SiNx), or a multilayer thereof. However, the present embodiment is not limited thereto.

The gate electrode 212 can be provided on the gate insulation layer 230. The gate electrode 212 can be formed of a single layer or a multilayer which includes one of molybdenum (Mo), aluminum (Al), chromium (Cr), gold (Au), titanium (Ti), nickel (Ni), neodymium (Nd), and 10 copper (Cu), or an alloy thereof, but is not limited thereto.

An interlayer insulation layer 240 can be provided on the gate electrode 212. The interlayer insulation layer 240 can be formed of an inorganic layer, and for example, can be formed of SiOx, SiNx, or a multilayer thereof. However, the 15 present embodiment is not limited thereto.

The source electrode 213 and the drain electrode 214 can be provided on the interlayer insulation layer **240**. The source electrode 213 can be connected to the active layer 211 through a contact hole CH1 which passes through the gate 20 insulation layer 220 and the interlayer insulation layer 230, and the drain electrode 214 can be connected to the active layer 211 through a contact hole CH2 which passes through the gate insulation layer 220 and the interlayer insulation layer 230. The source electrode 213 and the drain electrode 25 214 can each be formed of a single layer or a multilayer which includes one of Mo, Al, Cr, Au, Ti, Ni, Nd, and Cu, or an alloy thereof, but are not limited thereto.

The capacitors 220 can each include a bottom electrode 221 and a top electrode 222. The bottom electrode 221 can 30 be provided on the gate insulation layer 230 and can be formed of the same material as that of the gate electrode 212. The top electrode 222 can be provided on the interlayer insulation layer 240 and can be formed of the same material as that of each of the source electrode 223 and the drain 35 electrode 224.

A passivation layer 250 can be provided on the TFTs 210 and the capacitors 220. The passivation layer 250 can act as an insulation layer. The passivation layer 250 can be formed of an inorganic layer, and for example, can be formed of 40 SiOx, SiNx, or a multilayer thereof. However, the present embodiment is not limited thereto.

A planarization layer 260 for planarizing a step height caused by the TFTs 210 and the capacitors 220 can be provided on the passivation layer 250. The planarization 45 layer 260 can be formed of an organic layer such as acryl resin, epoxy resin, phenolic resin, polyamide resin, or polyimide resin, but is not limited thereto.

A light emitting device 280 and a bank 284 can be provided on the planarization layer **260**. The light emitting 50 device 280 can include a first electrode 282, a light emitting layer 283, and a second electrode 281. The first electrode 282 can be a cathode electrode, and the second electrode 281 can be an anode electrode. An area where the first electrode **282**, the light emitting layer **283**, and the second electrode 55 **281** are stacked can be defined as an emissive area EA.

The second electrode **281** can be provided on the planarization layer 260. The second electrode 281 can be connected to the drain electrode **214** of a corresponding TFT 210 through a contact hole CH3 which passes through the 60 provided in a green light emitting part. passivation layer 250 and the planarization layer 260. The second electrode 281 can be formed of a metal material, which is high in reflectivity, such as a stacked structure (Ti/Al/Ti) of Al and Ti, a stacked structure (ITO/Al/ITO) of Al and ITO, an APC alloy, or a stacked structure (ITO/APC/ 65 ITO) of an APC alloy and ITO. The APC alloy can be an alloy of silver (Ag), palladium (Pd), and copper (Cu).

**10**

The bank **284** can be provided on the planarization layer 260 to cover an edge of the second electrode 281, for dividing a plurality of emissive areas EA. The bank 284 can be formed of an organic layer such as acryl resin, epoxy resin, phenolic resin, polyamide resin, or polyimide resin, but is not limited thereto.

The light emitting layer 283 can be provided on the second electrode **281** and the bank **284**. The light emitting layer 283 can include a hole transporting layer, at least one light emitting layer, and an electron transporting layer. In this case, when a voltage is applied to the second electrode 281 and the first electrode 282, a hole and an electron can move to the light emitting layer through the hole transporting layer and the electron transporting layer and can be combined with each other in the light emitting layer to emit light.

The light emitting layer 283 can be a white light emitting layer which emits white light. In this case, the light emitting layer 283 can be provided to cover the second electrode 281 and the bank **284**. In this case, a color filter can be provided on the second substrate 112.

Moreover, the light emitting layer 283 can include a red light emitting layer which emits red light, a green light emitting layer which emits green light, or a blue light emitting layer which emits blue light. In this case, the light emitting layer 283 can be provided in an area corresponding to the second electrode **281**, and the color filter can not be provided on the second substrate 112.

The first electrode 282 can be provided on the light emitting layer 283. When an organic light emitting display apparatus is implemented in a top emission structure, the first electrode **282** can be formed of a transparent conductive material (or TCO), such as indium tin oxide (ITO) or indium zinc oxide (IZO) capable of transmitting light, or a semitransmissive conductive material such as Mg, Ag, or an alloy of Mg and Ag. A capping layer can be provided on the first electrode 282.

An encapsulation layer 290 can be provided on the light emitting device 280. The encapsulation layer 290 prevents oxygen or water from penetrating into the light emitting layer 283 and the first electrode 282. To this end, the encapsulation layer 290 can include at least one inorganic layer and at least one organic layer.

For example, the encapsulation layer **290** can include a first inorganic layer 291, an organic layer 292, and a second inorganic layer 293. In this case, the first inorganic layer 291 can be provided to cover the first electrode 282. The organic layer 292 can be provided on the first inorganic layer 291. The organic layer **292** can be provided to have a sufficient thickness, for preventing particles from penetrating into the light emitting layer 283 and the first electrode 282 via the first inorganic layer 291. The second inorganic layer 293 can be provided to cover the organic layer 292.

First to third color filters and a black matrix can be provided on the encapsulation layer **290**. The first color filter which is a red color filter 323 can be provided in a red light emitting part, the second color filter which is a blue color filter 322 can be provided in a blue light emitting part, and the third color filter which is a green color filter 321 can be

The encapsulation layer 290 of the first substrate 111 can be bonded to the color filters of the second substrate 112 by an adhesive layer, and thus, the first substrate 111 can be bonded to the second substrate 112. The adhesive layer can be a transparent adhesive resin, but is not limited thereto.

To provide description with reference to FIG. 6, a pad area PA can be disposed in one edge of the first substrate 111. The

pad area PA can include a plurality of pads, and the plurality of pads can be electrically connected to wirings of the flexible film 150 by an anisotropic conductive film.

A dam 120 can be disposed to surround the display area DA and can block a flow of the organic layer 292. Also, the dam 120 can be disposed between the display area DA and the pad area PA and can block a flow of the organic layer 292 so that the organic layer 292 configuring the encapsulation layer 290 of a pixel P does not penetrate into the pad area PA.

The buffer layer 130 can be spaced apart from the display area DA in the non-display area NDA and can contact the first inorganic layer 291 or the second inorganic layer 293 configuring the encapsulation layer 290 of the pixel P.

Hereinafter, a dam and a buffer layer according to the first embodiment of the present disclosure will be described in detail with reference to FIGS. 8 to 10.

FIG. **8** is a cross-sectional view taken along line II-II' of FIG. **6**, and FIG. **9** is a cross-sectional view taken along line III-III' of FIG. **6**. FIG. **10** is a cross-sectional view illustrataging an example where a mask is disposed on a buffer layer of FIG. **8**.

In FIGS. 8 to 10, for convenience of description, a detailed configuration of each of TFTs 210 and capacitors 220 are omitted, and a TFT substrate 200 including the TFTs 25 210 and the capacitors 220 is illustrated. The TFT substrate 200 can include a first substrate 111, a gate insulation layer 230, and an interlayer insulation layer 240 illustrated in FIG. 8

A display apparatus illustrated in FIG. 8 can include an 30 encapsulation layer 290, a dam 120, and a buffer layer 130, which are provided on the TFT substrate 200. Also, the TFT substrate 200 including the first substrate 111 can include a display area DA where a plurality of pixels P are provided and a pad area PA where a plurality of pads are provided. 35

The encapsulation layer 290 can be provided to cover the light emitting device 280 provided in the display area DA and can prevent oxygen or water from penetrating into the light emitting device 280. The encapsulation layer 290 can include at least one inorganic layer and at least one organic 40 layer. For example, the encapsulation layer 290 can include a first inorganic layer 291, an organic layer 292, and a second inorganic layer 293. In this case, the first inorganic layer 291 can be provided to cover a first electrode 282, the organic layer 292 can be provided on the first inorganic layer 45 291, and the second inorganic layer 293 can be provided to cover the organic layer 292.

The first and second inorganic layers 291 and 293 can each be formed of silicon nitride, aluminum nitride, zirconium nitride, titanium nitride, hafnium nitride, tantalum 50 nitride, silicon oxide, aluminum oxide, or titanium oxide, but are not limited thereto. The first and second inorganic layers 291 and 293 can be deposited through a chemical vapor deposition (CVD) process or an atomic layer deposition (ALD) process, but are not limited thereto.

The organic layer 292 can be formed of a transparent material, for transmitting light emitted from the light emitting layer 283. The organic layer 292 can be formed of an organic material (for example, acryl resin, epoxy resin, phenolic resin, polyamide resin, or polyimide resin) capable 60 of transmitting 99% or more of the light emitted from the light emitting layer 283. The organic layer 292 can be formed through a vapor deposition process, a printing process, or a slit coating process, which uses an organic material, but is not limited thereto. In other embodiments, 65 the organic layer 292 can be formed through an ink-jet process.

12

The dam 120 can be provided to surround an outer portion of the display area DA and can block a flow of the organic layer 292 configuring the encapsulation layer 290. The organic layer 292 configuring the encapsulation layer 290 is good in coverage performance, but is low in barrier performance. Therefore, the organic layer 292 can be encapsulated by the second inorganic layer 293. Also, if the organic layer 292 flows into a region where the organic layer 292 is to be formed, water or oxygen penetrates into the inside through the organic layer 292 which is exposed without being encapsulated by the second inorganic layer 293. In order to solve such a problem, the dam 120 can block a flow of the organic layer 292, thereby preventing the organic layer 292 from being exposed at the outside of the display apparatus.

Moreover, the dam 120 can be disposed between the display area DA and the pad area PA and can block a flow of the organic layer 292 so that the organic layer 292 configuring the encapsulation layer 290 does not flow into the pad area PA. When the organic layer 292 configuring the encapsulation layer 290 penetrates into the pad area PA, an electrical contact is not normally made in a pad due to the organic layer 292, and for this reason, a driving error or a lighting test error occurs. In order to solve such a problem, the dam 120 can block a flow of the organic layer 292 configuring the encapsulation layer 290, thereby preventing the organic layer 292 from penetrating into the pad area PA.

In FIGS. 8 to 10, one dam 120 is illustrated, but the present embodiment is not limited thereto. In other embodiments, the dam 120 can include a first dam and a second dam which is disposed in a non-display area and is spaced apart from the first dam. The second dam can block a flow of the organic layer 292 flowing out to an outer portion of the first dam. Also, the dam 120 can be provided as one or more.

Moreover, the dam 120 can be formed at the same time with at least one of a planarization layer 260 and a bank 284 which are provided in a pixel P, and can be formed of the same material as that of at least one of the planarization layer 260 and the bank 284. In this case, the dam 120 can be formed of an organic material such as acryl resin, epoxy resin, phenolic resin, polyamide resin, or polyimide resin, but is not limited thereto.

The buffer layer 130 can be spaced apart from the display area DA in a non-display area NDA and can contact at least one of the first inorganic layer 291 and the second inorganic layer 293. Referring to FIG. 10, for example, the buffer layer 130 can be provided between the dam 120 and a scribing line SL, in the non-display area NDA and can support a mask 140 so as to maintain a certain distance between the mask 140 and the TFT substrate 200 when performing a process of depositing the first inorganic layer 291 or the second inorganic layer 293. To this end, the mask 140 can be disposed on the buffer layer 130 to contact the buffer layer 130.

When the first inorganic layer 291 or the second inorganic layer 293 is deposited after the mask 140 is disposed on the buffer layer 130, the first inorganic layer 291 or the second inorganic layer 293 can be provided in a region other than a region where the mask 140 is disposed. Also, since a space is not formed between the mask 140 and the TFT substrate 200 by the buffer layer 130, the first inorganic layer 291 or the second inorganic layer 293 is prevented from penetrating into the region where the mask 140 is disposed. Therefore, in the present embodiment, since the buffer layer 130 is disposed between the dam 120 and the scribing line SL and the mask 140 is disposed on the buffer layer 130 to contact the buffer layer 130, the first inorganic layer 291 or the

second inorganic layer 293 is prevented from being formed in an outer portion (for example, the scribing line SL) of the buffer layer 130.

Moreover, the buffer layer 130 can be provided between the dam 120 and the pad area PA as illustrated in FIG. 9 and 5 can prevent the first inorganic layer 291 or the second inorganic layer 293 from being formed in the pad area PA, thereby solving a problem where a driving error or a lighting test error occurs because an electrical contact is not made in a pad part due to the first inorganic layer 291 or the second 10 inorganic layer 293.

Moreover, as described above, the buffer layer 130 can contact an edge of at least one of the deposited first inorganic layer 291 and second inorganic layer 293. FIG. 8 illustrates an example where the buffer layer 130 contacts an edge of 15 the first inorganic layer 291 and an edge of the second inorganic layer 293, but the present embodiment is not limited thereto.

In another embodiment, the buffer layer 130 can contact only an edge of the second inorganic layer 293. For example, 20 the first inorganic layer 291 and the second inorganic layer 293 can be deposited by using different masks. The first inorganic layer 291 can be deposited by using a first mask, and the second inorganic layer 293 can be deposited by using a second mask. Also, the first mask can be formed 25 greater in area than the second mask, in order for the first inorganic layer 291 to be formed smaller than the second inorganic layer 293 and can be disposed close to the light emitting device 280. Therefore, the first inorganic layer 291 can be formed less in area than the second inorganic layer 30 293. The second inorganic layer 293 can fully cover the first inorganic layer 291 and the organic layer 292 provided on the first inorganic layer 291.

In another embodiment, the buffer layer 130 can contact only an edge of the first inorganic layer **291**. For example, 35 the first inorganic layer 291 and the second inorganic layer 293 can be deposited by using different deposition processes. Since the light emitting device 280 is not flatly formed, the first inorganic layer 291 can be deposited by using an ALD process which is high in step coverage. The 40 mask 140 can be disposed on the buffer layer 130 to contact the buffer layer 130, and then, the first inorganic layer 291 can be deposited by using the ALD process. Therefore, the buffer layer 130 can contact the edge of the first inorganic layer 291. On the other hand, the second inorganic layer 293 can be provided on the organic layer 292 which is relatively flat, and thus, can be deposited by using a CVD process. The mask 140 can be disposed on the buffer layer 130 so as to be spaced apart from the buffer layer 130, and then, the second inorganic layer 293 can be deposited by using the 50 CVD process. Therefore, the second inorganic layer 293 can fully cover the first inorganic layer **291** and the organic layer **292**.

A height H2 of the buffer layer 130 can be set equal to or greater than a height H1 of the dam 120. When the height H2 55 of the buffer layer 130 is less than the height H1 of the dam 120, the dam 120 is damaged by the mask 140 while the mask 140 is being disposed on the buffer layer 130 in a process of depositing the first inorganic layer 291 or the second inorganic layer 293. Also, when the organic layer 60 292 contacts the damaged dam 120, oxygen or water penetrating into the damaged dam 120 is absorbed by the organic layer 292 and penetrates into the light emitting device 280, causing deterioration of the light emitting device 280.

Moreover, as illustrated in FIG. 8, the height H2 of the buffer layer 130 can be set greater than the height H1 of the

14

dam 120, and thus, the damage of the dam 120 is reduced when disposing the mask 140 on the buffer layer 130. However, the present embodiment is not limited thereto. When control of the mask 140 is precisely performed, a possibility that the dam 120 is damaged by the mask 140 is reduced. In this case, a need where the height H2 of the buffer layer 130 is set greater than the height H1 of the dam 120 is reduced.

Moreover, the buffer layer 130 can be formed at the same time with at least one of a planarization layer 260 and a bank 284 which are provided in a pixel P, and can be formed of the same material as that of at least one of the planarization layer 260 and the bank 284. In this case, the buffer layer 130 can be formed of an organic material such as acryl resin, epoxy resin, phenolic resin, polyamide resin, or polyimide resin, but is not limited thereto.

### Second Embodiment

FIG. 11 is a plan view illustrating a first substrate of a display apparatus according to a second embodiment of the present disclosure, and FIG. 12 is a cross-sectional view taken along line II-II' of FIG. 11. Here and in the below embodiments, the first substrate in each embodiment can be another example of the first substrate 111 of FIG. 4.

In FIGS. 11 and 12, for convenience of description, a detailed configuration of each of TFTs 210 and capacitors 220 are omitted, and a TFT substrate 200 including the TFTs 210 and the capacitors 220 is illustrated. The TFT substrate 200 can include a first substrate 111, a gate insulation layer 230, and an interlayer insulation layer 240 illustrated in FIG.

Referring to FIG. 11, the TFT substrate 200 including the first substrate 111 can be divided into a display area DA and a non-display area NDA, and a pad area PA where a plurality of pads are provided, a dam 120, and a buffer layer 130 can be provided in the non-display area NDA. Also, the buffer layer 130 illustrated in FIGS. 11 and 12 can be disposed between the dam 120 and the display area DA. Hereinafter, therefore, the same descriptions as descriptions given above with reference to FIGS. 6 to 10 can be omitted or will be briefly given.

The dam 120 can be disposed to surround an outer portion of the buffer layer 130 in the non-display area NDA and can block a flow of an organic layer 292 flowing out to the outer portion of the buffer layer 130. Also, the dam 120 can be disposed between the buffer layer 130 and the pad area PA and can block a flow of the organic layer 292 so that the organic layer 292 does not penetrate into the pad area PA.

In FIGS. 11 to 12, one dam 120 is illustrated, but the present embodiment is not limited thereto. In other embodiments, the dam 120 can include a first dam and a second dam which is disposed in the non-display area and is spaced apart from the first dam. The second dam can block a flow of the organic layer 292 flowing out to an outer portion of the first dam. Also, the dam 120 can be provided as one or more.

The buffer layer 130 can be provided in the non-display area NDA and can contact at least one of a first inorganic layer 291 and a second inorganic layer 293. For example, the buffer layer 130 can be provided between the dam 120 and the display area DA, in the non-display area NDA and can support a mask 140 (see FIG. 10) so as to maintain a certain distance between the mask 140 and the TFT substrate 200 when performing a process of depositing the first inorganic layer 291 or the second inorganic layer 293. To this end, the mask 140 can be disposed on the buffer layer 130 to contact the buffer layer 130.

When the first inorganic layer 291 or the second inorganic layer 293 is deposited after the mask 140 is disposed on the buffer layer 130, the first inorganic layer 291 or the second inorganic layer 293 can be provided in a region other than a region where the mask 140 is disposed. Also, since a space 5 is not formed between the mask 140 and the TFT substrate 200 by the buffer layer 130, the first inorganic layer 291 or the second inorganic layer 293 is prevented from penetrating into the region where the mask 140 is disposed. Therefore, in the present embodiment, since the buffer layer 130 is 10 disposed between the dam 120 and the display area DA and the mask 140 is disposed on the buffer layer 130 to contact the buffer layer 130, the first inorganic layer 291 or the second inorganic layer 293 is prevented from being formed in an outer portion (for example, a scribing line SL) of the 15 buffer layer 130.

Moreover, as described above, the buffer layer 130 can contact an edge of at least one of the deposited first inorganic layer 291 and second inorganic layer 293. FIG. 12 illustrates an example where the buffer layer 130 contacts an edge of 20 the first inorganic layer 291 and an edge of the second inorganic layer 293, but the present embodiment is not limited thereto.

In another embodiment, the buffer layer 130 can contact only an edge of the first inorganic layer **291**. For example, 25 the first inorganic layer **291** and the second inorganic layer 293 can be deposited by using different deposition processes and different masks. Since a light emitting device 280 is not flatly formed, the first inorganic layer 291 can be deposited by using an ALD process which is high in step coverage. A 30 first mask can be disposed on the buffer layer 130 to contact the buffer layer 130, and then, the first inorganic layer 291 can be deposited by using the ALD process. Therefore, the buffer layer 130 can contact the edge of the first inorganic layer **291**. On the other hand, the second inorganic layer **293** 35 can be provided on the organic layer 292 which is relatively flat, and thus, can be deposited by using a CVD process. A second mask can be disposed on the TFT substrate 200 so as to be spaced apart from the buffer layer 130 and the dam 120, and then, the second inorganic layer 293 can be 40 deposited by using the CVD process. In this case, the second mask can be less in area than the first mask so that the second inorganic layer 293 is formed wider than the first inorganic layer **291**, but can have a large open area. Therefore, the second inorganic layer 293 can fully cover the first inorganic 45 layer 291 and the organic layer 292 provided on the first inorganic layer 291.

A height H2 of the buffer layer 130 can be set greater than a height H1 of the dam 120. When the height H2 of the buffer layer 130 is equal to or less than the height H1 of the 50 dam 120, the dam 120 is damaged by the mask 140 contacting the dam 120 while the mask 140 is being disposed on the buffer layer 130 in a process of depositing the first inorganic layer 291 or the second inorganic layer 293. Also, when the organic layer 292 contacts the damaged dam 55 120, oxygen or water penetrating into the damaged dam 120 is absorbed by the organic layer 292 and penetrates into the light emitting device 280, causing deterioration of the light emitting device 280.

Moreover, the height H2 of the buffer layer 130 can be set 60 greater than the height H1 of the dam 120, and thus, the damage of the dam 120 is reduced when disposing the mask 140 on the buffer layer 130 in a process of depositing the first inorganic layer 291 or the second inorganic layer 293. However, the present embodiment is not limited thereto. 65

Moreover, the buffer layer 130 can be provided not to overlap a first electrode 282. In a case where the buffer layer

**16**

130 is provided to overlap the first electrode 282, the first electrode 282 is damaged because the mask 140 moves when disposing the mask 140 on the buffer layer 130 in the process of depositing the first inorganic layer 291 or the second inorganic layer 293. Due to a damaged second electrode, a pixel is not normally driven, and a black spot occurs.

According to the present embodiment, the buffer layer 130 can be provided not to overlap the first electrode 282, and thus, the damage of the first electrode 282 is reduced when disposing the mask 140 on the buffer layer 130 in the process of depositing the first inorganic layer 291 or the second inorganic layer 293.

#### Third Embodiment

FIG. 13 is a plan view illustrating a first substrate of a display apparatus according to a third embodiment of the present disclosure, and FIG. 14 is a cross-sectional view taken along line II-II' of FIG. 13.

In FIGS. 13 and 14, for convenience of description, a detailed configuration of each of TFTs 210 and capacitors 220 are omitted, and a TFT substrate 200 including the TFTs 210 and the capacitors 220 is illustrated. The TFT substrate 200 can include a first substrate 111, a gate insulation layer 230, and an interlayer insulation layer 240 illustrated in FIG.

Referring to FIGS. 13 and 14, the first substrate 111 can be divided into a display area DA and a non-display area NDA, and a pad area PA where a plurality of pads are provided, a dam 120, a first buffer layer 132, and a second buffer layer 134 can be provided in the non-display area NDA. Also, a buffer layer 130 illustrated in FIGS. 13 and 14 can include the first buffer layer 132 and the second buffer layer 134. Hereinafter, therefore, the same descriptions as descriptions given above with reference to FIGS. 6 to 10 can be omitted or will be briefly given.

The dam 120 can be disposed to surround an outer portion of the first buffer layer 132 in the non-display area NDA and can block a flow of an organic layer 292 flowing out to the outer portion of the first buffer layer 132. Also, the dam 120 can be disposed between the first buffer layer 132 and the pad area PA and can block a flow of the organic layer 292 so that the organic layer 292 does not penetrate into the pad area PA.

In FIGS. 13 to 14, one dam 120 is illustrated, but the present embodiment is not limited thereto. In other embodiments, the dam 120 can include a first dam and a second dam which is disposed in the non-display area and is spaced apart from the first dam. The second dam can block a flow of the organic layer 292 flowing out to an outer portion of the first dam. Also, the dam 120 can be provided as one or more.

The first buffer layer 132 can be provided in the non-display area NDA and can contact an edge of a first inorganic layer 291. For example, the first buffer layer 132 can be provided between the dam 120 and the display area DA, in the non-display area NDA and can support a first mask so as to maintain a certain distance between the first mask and the TFT substrate 200 when performing a process of depositing the first inorganic layer 291. To this end, the first mask can be disposed on the first buffer layer 132 to contact the first buffer layer 132.

When the first inorganic layer **291** is deposited after the first mask is disposed on the first buffer layer **132**, the first inorganic layer **291** can be provided in a region other than a region where the first mask is disposed. Also, since a space is not formed between the first mask and the TFT substrate

200 by the first buffer layer 132, the first inorganic layer 291 is prevented from penetrating into the region where the first mask is disposed. Therefore, in the present embodiment, since the first buffer layer 132 is disposed between the dam 120 and the display area DA and the first mask is disposed on the first buffer layer 132 to contact the first buffer layer 132, the first inorganic layer 291 is prevented from being formed in an outer portion (for example, a scribing line SL) of the first buffer layer 132.

Moreover, the first buffer layer 132 can be provided not to overlap a first electrode 282. In a case where the first buffer layer 132 is provided to overlap the first electrode 282, the first electrode 282 is damaged because the first mask moves when disposing the first mask on the first buffer layer 132 in the process of depositing the first inorganic layer 291. Due 15 to a damaged second electrode, a pixel is not normally driven, and a black spot occurs.

According to the present embodiment, the first buffer layer 132 can be provided not to overlap the first electrode 282, and thus, the damage of the first electrode 282 is 20 reduced when disposing the first mask on the first buffer layer 132 in the process of depositing the first inorganic layer 291.

The second buffer layer 134 can be provided in the non-display area NDA and can contact an edge of a second 25 inorganic layer 293. For example, the second buffer layer 134 can be provided between the dam 120 and the scribing line SL, in the non-display area NDA and can support a second mask so as to maintain a certain distance between the second mask and the TFT substrate 200 when performing a 30 process of depositing the second inorganic layer 293. To this end, the second mask can be disposed on the second buffer layer 134 to contact the second buffer layer 134.

When the second inorganic layer 293 is deposited after the second mask is disposed on the second buffer layer 134, the second inorganic layer 293 can be provided in a region other than a region where the second mask is disposed. Also, since a space is not formed between the second mask and the TFT substrate 200 by the second buffer layer 134, the second inorganic layer 293 is prevented from penetrating into the region where the second mask is disposed. As a result, in the present embodiment, since the second buffer layer 134 is disposed between the dam 120 and the scribing line SL and the second mask is disposed on the second buffer layer 134 to contact the second buffer layer 134, the second inorganic 45 or layer 293 is prevented from being formed in an outer portion (for example, the scribing line SL) of the second buffer layer 134.

Moreover, according to the present embodiment, since the first buffer layer 132 and the second buffer layer 134 are provided, the first inorganic layer 291 and the second inorganic layer 293 can be provided between the dam 120 and the display area DA, and the second buffer layer 134 can be provided in an outer portion of the dam 120, whereby the second inorganic layer 293 can fully cover the organic layer 292, of which flow is blocked by the first inorganic layer 291 and the dam 120, to prevent penetration of oxygen and water. In this case, the first inorganic layer 291 and the second inorganic layer 292 can be formed by using the same deposition process or different deposition processes.

A height H2 of the first buffer layer 132 can be set greater than a height H1 of the dam 120. When the height H2 of the first buffer layer 132 is equal to or less than the height H1 of the dam 120, the dam 120 is damaged by the first mask while the first mask is being disposed on the first buffer layer thereto. In the layer 292, and the result of the dam 120 is damaged by the first mask thereto. In the layer 292, and the layer 292 is damaged by the first mask area NDA area ND

18

132 in a process of depositing the first inorganic layer 291. Also, a height H3 of the second buffer layer 134 can be set equal to or greater than the height H1 of the dam 120. When the height H3 of the second buffer layer 134 is less than the height H1 of the dam 120, the dam 120 is damaged by the second mask while the second mask is being disposed on the second buffer layer 134 in a process of depositing the second inorganic layer 293. Also, when the organic layer 292 contacts the damaged dam 120, oxygen or water penetrating into the damaged dam 120 is absorbed by the organic layer 292 and penetrates into a light emitting device 280, causing deterioration of the light emitting device 280.

The first buffer layer 132 and the second buffer layer 134 can be formed at the same time with at least one of a planarization layer 260 and a bank 284 which are provided in a pixel P, and can be formed of the same material as that of at least one of the planarization layer 260 and the bank 284. In this case, the first buffer layer 132 and the second buffer layer 134 can each be formed of an organic material such as acryl resin, epoxy resin, phenolic resin, polyamide resin, or polyimide resin, but is not limited thereto.

### Fourth Embodiment

FIG. 15 is a plan view illustrating a first substrate of a display apparatus according to a fourth embodiment of the present disclosure, and FIG. 16 is a cross-sectional view taken along line II-II' of FIG. 15.

In FIGS. 15 and 16, for convenience of description, a detailed configuration of each of TFTs 210 and capacitors 220 are omitted, and a TFT substrate 200 including the TFTs 210 and the capacitors 220 is illustrated. The TFT substrate 200 can include a first substrate 111, a gate insulation layer 230, and an interlayer insulation layer 240 illustrated in FIG. 8.

Referring to FIGS. 15 and 16, the first substrate 111 can be divided into a display area DA and a non-display area NDA, and a pad area PA where a plurality of pads are provided and a buffer layer 130 can be provided in the non-display area NDA. Also, the first substrate 111 illustrated in FIGS. 15 and 16 does not include a dam, and an encapsulation layer does not include an organic layer. Hereinafter, therefore, the same descriptions as descriptions given above with reference to FIGS. 6 to 10 can be omitted or will be briefly given.

The encapsulation layer 290 can be provided to cover a light emitting device 280 provided in the display area DA and can prevent oxygen or water from penetrating into the light emitting device 280. Also, the encapsulation layer 290 can include at least one inorganic layer. For example, the encapsulation layer 290 can include one first inorganic layer 291. In this case, the first inorganic layer 291 can be provided to cover a first electrode 282.

The first inorganic layer **291** can be formed of silicon nitride, aluminum nitride, zirconium nitride, titanium nitride, hafnium nitride, tantalum nitride, silicon oxide, aluminum oxide, or titanium oxide, but are not limited thereto. The first inorganic layer **291** can be deposited through a CVD process or an ALD process, but is not limited thereto.

In FIGS. 15 and 16, one first inorganic layer 291 is illustrated, but the present embodiment is not limited thereto. In other embodiments, an inorganic layer can include a first inorganic layer 291 and a second inorganic layer 292.

The buffer layer 130 can be provided in the non-display area NDA and can contact an edge of the first inorganic layer

291. For example, the buffer layer 130 can be provided in the non-display area NDA, can be spaced apart from a scribing line SL, and can support a mask 140 so as to maintain a certain distance between the mask 140 and the TFT substrate 200 when performing a process of depositing the first inorganic layer 291. To this end, the mask 140 can be disposed on the buffer layer 130 to contact the buffer layer 130.

When the first inorganic layer **291** is deposited after the mask **140** is disposed on the buffer layer **130**, the first inorganic layer **291** can be provided in a region other than a region where the mask **140** is disposed. Also, since a space is not formed between the mask **140** and the TFT substrate **200** by the buffer layer **130**, the first inorganic layer **291** is prevented from penetrating into the region where the mask **15 140** is disposed. Therefore, in the present embodiment, since the buffer layer **130** is disposed in the non-display area NDA so as to be spaced apart from the scribing line SL and the mask **140** is disposed on the buffer layer **130** to contact the buffer layer **130**, the first inorganic layer **291** is prevented from being formed in an outer portion (for example, the scribing line SL) of the buffer layer **130**.

Moreover, the buffer layer 130 can be formed at the same time with at least one of a planarization layer 260 and a bank 284 which are provided in a pixel P, and can be formed of the same material as that of at least one of the planarization layer 260 and the bank 284. In this case, the buffer layer 130 can be formed of an organic material such as acryl resin, epoxy resin, phenolic resin, polyamide resin, or polyimide resin, but is not limited thereto.

# Fifth Embodiment

FIG. 17 is a plan view illustrating a first substrate of a display apparatus according to a fifth embodiment of the 35 present disclosure.

Referring to FIG. 17, the first substrate 111 can be divided into a display area DA and a non-display area NDA. A pad area PA where a plurality of pads are provided, a dam 120, and a buffer layer 130 can be provided in the non-display 40 area NDA. Also, the buffer layer 130 illustrated in FIG. 18 can be provided in a plurality of island type patterns. The buffer layer 130 provided in the plurality of island type patterns can be applied to other embodiments.

The buffer layer 130 can be provided in the plurality of 45 island type patterns along an outer portion of the dam 120. According to the fifth embodiment of the present disclosure, since the buffer layer 130 is provided in the plurality of island type patterns instead of a line pattern, an increase in stress caused by forming of the buffer layer 130 is reduced 50 in the non-display area NDA.

## Sixth Embodiment

FIG. 18 is a plan view illustrating a first substrate of a 55 lines. display apparatus according to a sixth embodiment of the present disclosure.

Referring to FIG. 18, a plurality of data lines and a plurality of gate lines intersecting the data lines can be provided in a display area DA. Also, a plurality of pixels P 60 for displaying an image can be provided in a matrix type in a plurality of areas defined by intersections of the data lines and the gate lines in the display area DA. When a gate signal is input through a corresponding gate line, each of the pixels P can supply a current to a light emitting device 260 with a 65 data voltage of a corresponding data line. Therefore, the light emitting device of each pixel P can emit light having

**20**

certain brightness, based on the current. Also, a source voltage can be supplied to a power line. The power line can supply the source voltage to each of the pixels P.

A dam 120, a power auxiliary line VAL connected to power lines, a plurality of pads PAD connected to the power auxiliary line VAL, and a buffer layer 130 can be provided in the non-display area NDA. Also, a plurality of data link lines DLL connected to the data lines can be further provided in the non-display area NDA.

A pad area PA can be disposed in one edge of the first substrate 111. The pad area PA can include a plurality of pads, and the plurality of pads can be electrically connected to wirings of a flexible film 150 by an anisotropic conductive film.

The dam 120 can be disposed to surround the display area DA and can block a flow of an organic layer 292. Also, the dam 120 can be disposed between the display area DA and the pad area PA and can block a flow of the organic layer 292 so that the organic layer 292 configuring an encapsulation layer 290 of a pixel P does not penetrate into the pad area PA.

The data link lines DLL can be respectively connected to the pads PAD disposed in the pad area PA and can be respectively connected to the data lines disposed in the display area DA. For example, one end of each of the data link lines DLL can be connected to a corresponding data line through a first contact hole, and the other end can be connected to a corresponding pad PAD through a second contact hole. Each of the plurality of pads PAD can be electrically connected to the wirings of the flexible film 150 through a third contact hole by using an anisotropic conductive film.

Each of the data link lines DLL can be arranged in parallel with a corresponding data line at one end connected to the corresponding data line, and then, can be arranged obliquely with respect to the corresponding data line by a certain length. Also, each of the data link lines DLL can be arranged in parallel with a corresponding pad PAD from an end of the certain length to the other end connected to the corresponding to pad PAD.

The data link lines DLL can be provided in a gate metal pattern including the same material as that of a gate electrode 212. The data lines and the pads PAD can each be provided in a source/drain metal pattern including the same material as that of a source/drain electrode 213/214.

The power auxiliary line VAL can be arranged in parallel with the gate lines and can be connected to the pad PAD disposed in the pad area PA and the power lines disposed in the display area DA. When the source voltage is applied from the pad PAD, the power auxiliary line VAL can supply the applied source voltage to the power line. In this case, the power auxiliary line VAL can not directly be connected to the power lines but can be connected to the power lines by using connection lines respectively connected to the power lines.

The connection lines can be provided in a gate metal pattern including the same material as that of the gate electrode 212. The power auxiliary line VAL and the power line can each be provided in a source/drain metal pattern including the same material as that of the source/drain electrode 213/214.

The buffer layer 130 can be disposed on a metal pattern (for example, the power auxiliary line VAL to which the source voltage is applied from the pad PAD) in the non-display area NDA and can contact a first inorganic layer 291 or a second inorganic layer 293 configuring an encapsulation layer 290 of a pixel P. In the sixth embodiment of the present

disclosure, the first inorganic layer 291 or the second inorganic layer 293 can cover a portion of a top of the buffer layer 130.

Hereinafter, a buffer layer according to the sixth embodiment of the present disclosure will be described in detail <sup>5</sup> with reference to FIG. **19**.

FIG. 19 is a cross-sectional view taken along line III-III' of FIG. 18, and FIG. 20 is a cross-sectional view illustrating an example where a mask is disposed on a buffer layer of FIG. 19. FIG. 21 is a cross-sectional view illustrating a modification embodiment of FIG. 19. Hereinafter, a difference with the first embodiment will be mainly described, and the same description as the first embodiment is omitted or may be brief.

A display apparatus illustrated in FIG. 19 can include an encapsulation layer 290, a dam 120, and a buffer layer 130, which are provided on a first substrate 111. Also, the first substrate 111 can include a display area DA where a plurality of pixels P are provided and a non-display area NDA, and 20 the non-display area NDA can include a pad area PA where a plurality of pads PAD are provided.

The encapsulation layer 290 can be provided to cover a light emitting device 280 provided in the display area DA and can prevent oxygen or water from penetrating into the 25 light emitting device 280. In this case, the encapsulation layer 290 can include at least one inorganic layer and at least one organic layer. For example, the encapsulation layer 290 can include a first inorganic layer 291, an organic layer 292, and a second inorganic layer 293. In this case, the first 30 inorganic layer 291 can be provided to cover a first electrode 282, the organic layer 292 can be provided on the first inorganic layer 291, and the second inorganic layer 293 can be provided to cover the organic layer 292.

The dam 120 can be provided to surround an outer portion of the display area DA and can block a flow of the organic layer 292 configuring the encapsulation layer 290. The organic layer 292 configuring the encapsulation layer 290 is good in coverage performance, but is low in barrier performance. Therefore, the organic layer 292 can be encapsulated by the second inorganic layer 293. Also, if the organic layer 292 is to be formed, water or oxygen penetrates into the inside through the organic layer 292 which is exposed without being encapsulated by the second inorganic layer 293. In order to solve such a problem, the dam 120 can block a flow of the organic layer 292, thereby preventing the organic layer 292 from being exposed at the outside of the display apparatus.

buffer layer 130.