### US010984743B2

# (12) United States Patent

### Kurokawa

# (10) Patent No.: US 10,984,743 B2

# (45) **Date of Patent:** Apr. 20, 2021

### (54) SEMICONDUCTOR DEVICE

(71) Applicant: SEMICONDUCTOR ENERGY

LABORATORY CO., LTD., Atsugi

(JP)

(72) Inventor: Yoshiyuki Kurokawa, Kanagawa (JP)

(73) Assignee: Semiconductor Energy Laboratory

Co., Ltd., Atsugi (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 6 days.

(21) Appl. No.: 16/477,238

(22) PCT Filed: **Jan. 11, 2018**

(86) PCT No.: **PCT/IB2018/050160**

§ 371 (c)(1),

(2) Date: Jul. 11, 2019

(87) PCT Pub. No.: WO2018/130954

PCT Pub. Date: Jul. 19, 2018

### (65) Prior Publication Data

US 2020/0342825 A1 Oct. 29, 2020

# (30) Foreign Application Priority Data

| Jan. 16, 2017 | (JP) | JP2017-004871 |

|---------------|------|---------------|

| Jan. 16, 2017 | (JP) | JP2017-004872 |

(51) Int. Cl. *G09G* 3/3/

G09G 3/36 (2006.01) G11C 19/28 (2006.01)

(Continued)

(52) **U.S. Cl.**

CPC ...... *G09G 3/3648* (2013.01); *G11C 19/28* (2013.01); *G09G 2310/0286* (2013.01)

(58) Field of Classification Search

See application file for complete search history.

### (56) References Cited

#### U.S. PATENT DOCUMENTS

7,164,405 B1 1/2007 Jeong et al. 7,674,650 B2 3/2010 Akimoto et al.

(Continued)

### FOREIGN PATENT DOCUMENTS

EP 2187379 A 5/2010 JP 07-287556 A 10/1995 (Continued)

#### OTHER PUBLICATIONS

International Search Report (Application No. PCT/IB2018/050160) dated Apr. 24, 2018.

(Continued)

Primary Examiner — Chineyere D Wills-Burns (74) Attorney, Agent, or Firm — Fish & Richardson P.C.

### (57) ABSTRACT

A novel semiconductor device is provided.

The semiconductor device has a function of changing a pixel selection period in accordance with a distance from a driver circuit. Specifically, when the distance between a first pixel and the driver circuit is longer than the distance between a second pixel and the driver circuit, the pulse width of a selection signal supplied to the first pixel is set larger than the pulse width of a selection signal supplied to the second pixel. Accordingly, writing of image signals to pixels provided far from the driver circuit can be accurately performed while the selection period for pixels provided near the driver circuit is kept short.

### 5 Claims, 24 Drawing Sheets

# US 10,984,743 B2 Page 2

| H01L<br>H01L<br>H01L<br>H01L<br>G02F                                                                                                        | 19/00<br>29/786<br>27/12<br>27/06<br>21/822<br>1/133<br>51/50                                                              |                                                                                                              | (2013.01)<br>(2006.01)<br>(2006.01)<br>(2006.01)<br>(2006.01)<br>(2006.01)<br>(2006.01)<br>(2006.01)                           | 2017<br>2017<br>2017<br>2018<br>2018<br>2018<br>2018<br>2018                                                                               | /0138249 A1<br>/0116512 A1<br>/0118479 A1<br>/0140722 A1<br>/0352328 A1*<br>/0076231 A1*<br>/0122336 A1<br>/0130423 A1*<br>/0158393 A1*<br>/0182355 A1<br>/0180709 A1*            | 4/2017<br>4/2017<br>5/2017<br>12/2017<br>3/2018<br>5/2018<br>5/2018<br>6/2018<br>6/2018                   | Miyata et al. Kurokawa Kurokawa Miyata et al. Jeong                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| (56) References Cited                                                                                                                       |                                                                                                                            |                                                                                                              |                                                                                                                                | EODEICI                                                                                                                                    | NI DATEI                                                                                                                                                                          | NIT DOCLIMENTS                                                                                            |                                                                                                                      |

| 7,773,05<br>8,487,86<br>9,653,01<br>9,773,83<br>9,954,53<br>9,992,44<br>10,128,24<br>10,345,97<br>2003/001618<br>2004/021257<br>2006/002291 | 3 B2<br>3 B2<br>3 B2<br>3 B2<br>9 B2<br>7 B2<br>9 A1*                                                                      | 8/2010<br>7/2013<br>5/2017<br>9/2017<br>4/2018<br>6/2018<br>11/2018<br>7/2019<br>1/2003<br>10/2004<br>2/2006 | DOCUMENTS  Takayanagi et al. Itoh Miyata et al. Kurokawa Ikeda et al. Aoki et al. Aoki et al. Akasawa et al. Kimura et al. Abe | JP<br>JP<br>JP<br>JP<br>JP<br>JP<br>KR<br>KR<br>TW<br>WO                                                                                   | 3333-<br>2004-117-<br>2006-039-<br>2006-178-<br>2006-332-<br>2007-096-<br>2007-123-<br>2009-230-<br>2013-246-<br>10-0567-<br>2014-0082-<br>200725-<br>WO-2009/022-<br>WO-2012/157 | 470<br>758 A<br>457 A<br>689 A<br>109 A<br>055 A<br>861 A<br>103 A<br>230 A<br>500<br>413 A<br>525<br>486 | NT DOCUMENTS  10/2002 4/2004 2/2006 7/2006 12/2006 4/2007 5/2007 10/2009 12/2013 4/2006 7/2014 7/2007 2/2009 11/2012 |

| 2007/015944                                                                                                                                 | 7/02/03/03/04 A1 12/2000 Tanabe et al.<br>7/01/01/01/02/04 A1 7/2007 Yang et al.<br>7/02/19/242 A1 9/2009 Fuchigami et al. |                                                                                                              | OTHER PUBLICATIONS                                                                                                             |                                                                                                                                            |                                                                                                                                                                                   |                                                                                                           |                                                                                                                      |

| 2010/014185                                                                                                                                 | 50 A1*                                                                                                                     | 6/2010                                                                                                       | Itoh                                                                                                                           | Written Opinion (Application No. PCT/IB2018/050160) dated Apr. 24, 2018.<br>Kawashima.S et al., "13.3-in. 8K×4K 664-ppi OLED Display Using |                                                                                                                                                                                   |                                                                                                           |                                                                                                                      |

| 2014/009235                                                                                                                                 |                                                                                                                            |                                                                                                              | Teranuma G09G 3/3655<br>349/139                                                                                                | CAAC-OS FETs", SID Digest '14 : SID International Symposium Digest of Technical Papers, Jun. 3, 2014, pp. 627-630.                         |                                                                                                                                                                                   |                                                                                                           |                                                                                                                      |

| 2014/017640                                                                                                                                 | 7 A1*                                                                                                                      | 6/2014                                                                                                       | Choi G09G 3/3677                                                                                                               |                                                                                                                                            |                                                                                                                                                                                   |                                                                                                           |                                                                                                                      |

345/87

\* cited by examiner

200 [22] 22 22 **[22]** 40(1,1) 40(2,1) 22 [22] 22 22 ಹ

0

FIG. 2

FIG. 3B

GSRO

GPWC

GSEL

FIG. 4

FIG. 5A

FIG. 5B

FIG. 6

FIG. 8

FIG. 9

FIG. 10A

FIG. 10B

FIG. 11

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17A

FIG. 17B

FIG. 17C

FIG. 17D

FIG. 17E

FIG. 17F

FIG. 17G

FIG. 18A

FIG. 18B

FIG. 18C

FIG. 18D

FIG. 18E

FIG. 21A

FIG. 21B

FIG. 21C

FIG. 22

FIG. 23

### SEMICONDUCTOR DEVICE

# CROSS REFERENCE TO RELATED APPLICATIONS

This application is a U.S. National Phase Application under 35 U.S.C. § 371 of International Application PCT/IB2018/050160, filed on Jan. 11, 2018, which claims the benefit of foreign priority applications filed in Japan as 10 Application Nos. 2017-004871 and 2017-004872 on Jan. 16, 2017, all of which are incorporated by reference.

### TECHNICAL FIELD

One embodiment of the present invention relates to a semiconductor device.

Note that one embodiment of the present invention is not limited to the above technical field. Examples of the tech- 20 nical field of one embodiment of the present invention disclosed in this specification and the like include a semi-conductor device, a display device, a light-emitting device, a power storage device, a memory device, a display system, an electronic device, a lighting device, an input device, an 25 input/output device, a driving method thereof, and a manufacturing method thereof.

In this specification and the like, a semiconductor device means all devices that can function by utilizing semiconductor characteristics. A transistor, a semiconductor circuit, <sup>30</sup> an arithmetic device, a memory device, and the like are embodiments of the semiconductor device. In addition, a display device, an imaging device, an electro-optical device, a power generation device (including a thin film solar cell, an organic thin film solar cell, and the like), and an electronic <sup>35</sup> device may include a semiconductor device.

### BACKGROUND ART

With the increase in screen size, a television (TV) capable of displaying high-resolution images has been desired, and ultra-high-definition television broadcasting has been promoted. Experimental 8K digital television broadcasting started in 2016, and the full-scale launch of the broadcasting 45 is planned. Accordingly, various electronic devices that are compatible with 8K broadcasting have been developed (e.g., Non-Patent Document 1).

Flat panel displays typified by liquid crystal display devices and light-emitting display devices are widely used for displaying images. As a semiconductor material of transistors included in these display devices, silicon, for example, is chiefly used. Recently, a technique in which a transistor using a metal oxide is used in a pixel of a display device has also been developed (e.g., Patent Documents 1 and 2).

# REFERENCE

### Patent Document

[Patent Document 1] Japanese Published Patent Application No. 2007-96055

[Patent Document 2] Japanese Published Patent Application No. 2007-123861

### 2

### Non-Patent Document

[Non-Patent Document 1] S. Kawashima, et al., "13.3-In. 8K×4K 664-ppi OLED Display Using CAAC-OS FETs", SID 2014 DIGEST, pp. 627-630.

### SUMMARY OF THE INVENTION

### Problems to be Solved by the Invention

An object of one embodiment of the present invention is to provide a novel semiconductor device. Another object of one embodiment of the present invention is to provide a semiconductor device capable of high-speed operation.

15 Another object of one embodiment of the present invention is to provide a semiconductor device capable of displaying a high-quality image. Another object of one embodiment of the present invention is to provide a semiconductor device capable of displaying an image on a large screen. Another object of one embodiment of the present invention is to provide a semiconductor device with low power consumption.

Note that one embodiment of the present invention does not necessarily achieve all the above objects and only needs to achieve at least one of the objects. The description of the above objects does not preclude the existence of other objects. Objects other than the above will be apparent from and can be derived from the description of the specification, the claims, the drawings, and the like.

### Means for Solving the Problems

A semiconductor device according to one embodiment of the present invention includes a pixel portion, first to fourth driver circuits, and first to sixth wirings. The pixel portion includes a first region including a first pixel and a second pixel, and a second region including a third pixel and a fourth pixel. The first driver circuit has a function of supplying a first selection signal to the first wiring and a 40 function of supplying a second selection signal to the second wiring. The second driver circuit has a function of supplying a third selection signal to the third wiring and a function of supplying a fourth selection signal to the fourth wiring. The third driver circuit has a function of supplying a first image signal to the fifth wiring. The fourth driver circuit has a function of supplying a second image signal to the sixth wiring. The first pixel is electrically connected to the first wiring and the fifth wiring. The second pixel is electrically connected to the second wiring and the fifth wiring. The third pixel is electrically connected to the third wiring and the sixth wiring. The fourth pixel is electrically connected to the fourth wiring and the sixth wiring. The distance between the third driver circuit and the second pixel is longer than the distance between the third driver circuit and the first pixel. 55 The distance between the fourth driver circuit and the fourth pixel is longer than the distance between the fourth driver circuit and the third pixel. The second pixel and the fourth pixel are provided adjacent to each other. The pulse width of the second selection signal is larger than the pulse width of 60 the first selection signal. The pulse width of the fourth selection signal is larger than the pulse width of the third selection signal.

Moreover, the semiconductor device according to one embodiment of the present invention may include a first signal generator circuit and a second signal generator circuit. The first signal generator circuit may have a function of controlling the waveforms of a first clock signal and a first

control signal. The second signal generator circuit may have a function of controlling the waveforms of a second clock signal and a second control signal. The first clock signal and the first control signal may be used to generate the first selection signal and the second selection signal. The second 5 clock signal and the second control signal may be used to generate the third selection signal and the fourth selection signal.

In the semiconductor device according to one embodiment of the present invention, a first signal generator circuit and a second signal generator circuit may each include a register, a counter, a first comparator circuit, and a second comparator circuit. The register may have a function of outputting a first parameter to the first comparator circuit and a function of outputting a second parameter to the second comparator circuit. The first comparator circuit may have a function of generating a first clock signal or a second clock signal by using the first parameter and a count value of the counter. The second comparator circuit may have a function of generating a first control signal or a second control signal by using the second parameter and the count value of the counter.

In the semiconductor device according to one embodiment of the present invention, the register may include a first 25 scan chain register portion, a second scan chain register portion, and a register portion. First data may be sequentially input to the first scan chain register portion. Second data may be sequentially input to the second scan chain register portion. The register portion may have a function of selecting and outputting one of the first data and the second data.

In the semiconductor device according to one embodiment of the present invention, the first scan chain register portion and the second scan chain register portion may each include a retention circuit. The retention circuit may include a transistor and a capacitor. One of a source and a drain of the transistor may be electrically connected to the capacitor. The transistor may contain a metal oxide in a channel formation region.

In the semiconductor device according to one embodiment of the present invention, the first to fourth pixels may each include a transistor containing hydrogenated amorphous silicon in a channel formation region.

In the semiconductor device according to one embodi- 45 of a transistor. ment of the present invention, the first to fourth pixels may each include a transistor containing a metal oxide in a channel formation region.

FIG. 22 A description of a transistor.

FIG. 23 A description of a transistor.

### Effect of the Invention

One embodiment of the present invention can provide a novel semiconductor device. Alternatively, one embodiment of the present invention can provide a semiconductor device capable of high-speed operation. Alternatively, one embodiment of the present invention can provide a semiconductor device capable of displaying a high-quality image. Alternatively, one embodiment of the present invention can provide a semiconductor device capable of displaying an image on a large screen. Alternatively, one embodiment of the present invention can provide a semiconductor device with low power consumption.

Note that the description of these effects does not preclude the existence of other effects. Moreover, one embodiment of 65 the present invention does not necessarily have all of these effects. Effects other than the above will be apparent from 4

and can be derived from the description of the specification, the claims, the drawings, and the like.

#### BRIEF DESCRIPTION OF DRAWINGS

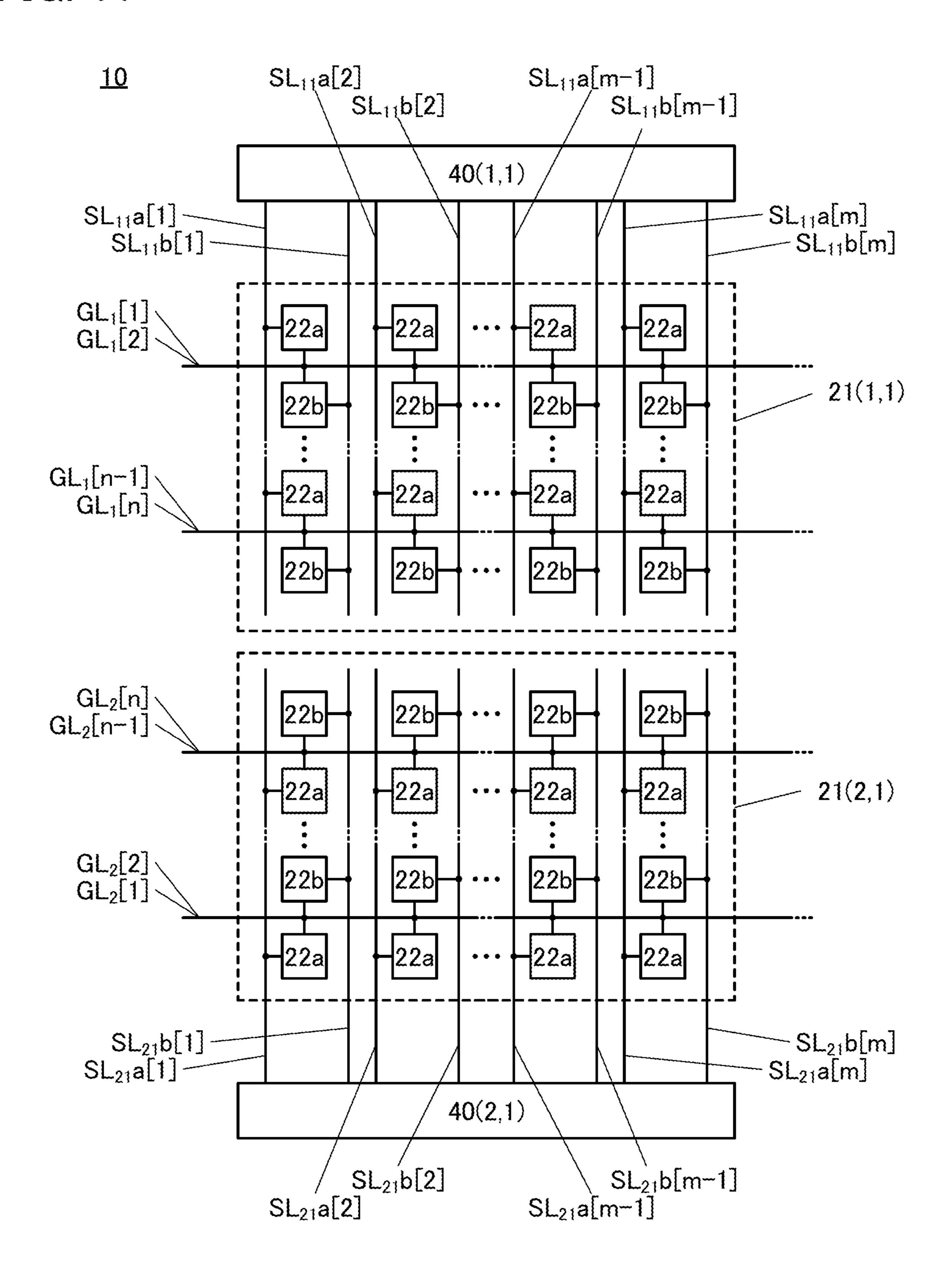

FIG. 1 A diagram illustrating a structure example of a semiconductor device.

FIG. 2 A diagram illustrating an operation example of a semiconductor device.

FIGS. 3A and 3B Diagrams illustrating a structure example of a driver circuit.

FIG. 4 A timing chart.

FIGS. **5**A and **5**B Diagrams illustrating a structure example of a signal generator circuit.

FIG. 6 A diagram illustrating a structure example of a register.

FIG. 7 A diagram illustrating a structure example of a register.

FIG. 8 A diagram illustrating a structure example of a register.

FIG. 9 A timing chart.

FIGS. 10A and 10B Diagrams illustrating structure examples of a pixel.

FIG. 11 A diagram illustrating a structure example of a semiconductor device.

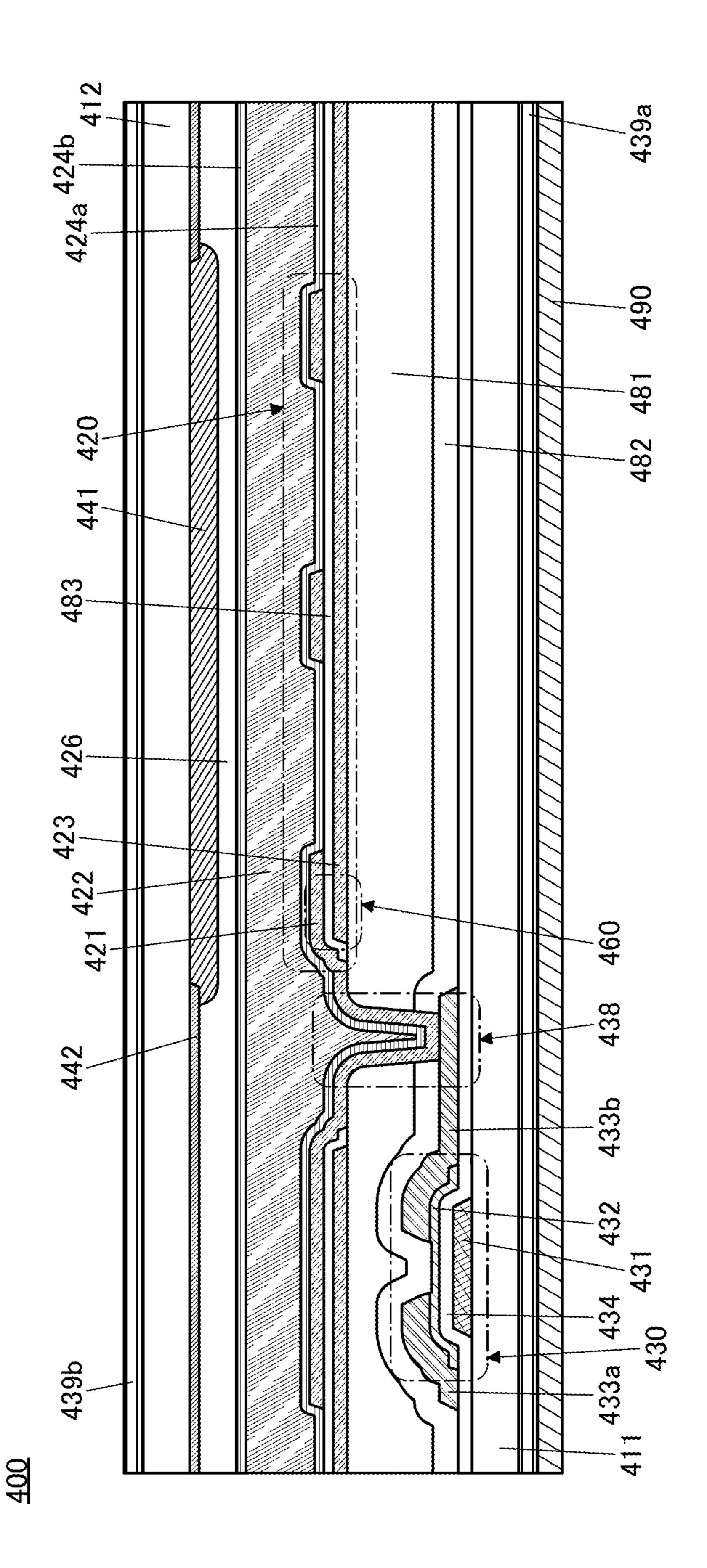

FIG. 12 A diagram illustrating a structure example of a display panel.

FIG. 13 A diagram illustrating a structure example of a display device.

FIG. **14** A diagram illustrating a structure example of a display device.

FIG. 15 A diagram illustrating a structure example of a display device.

FIG. 16 A diagram illustrating a structure example of a display device.

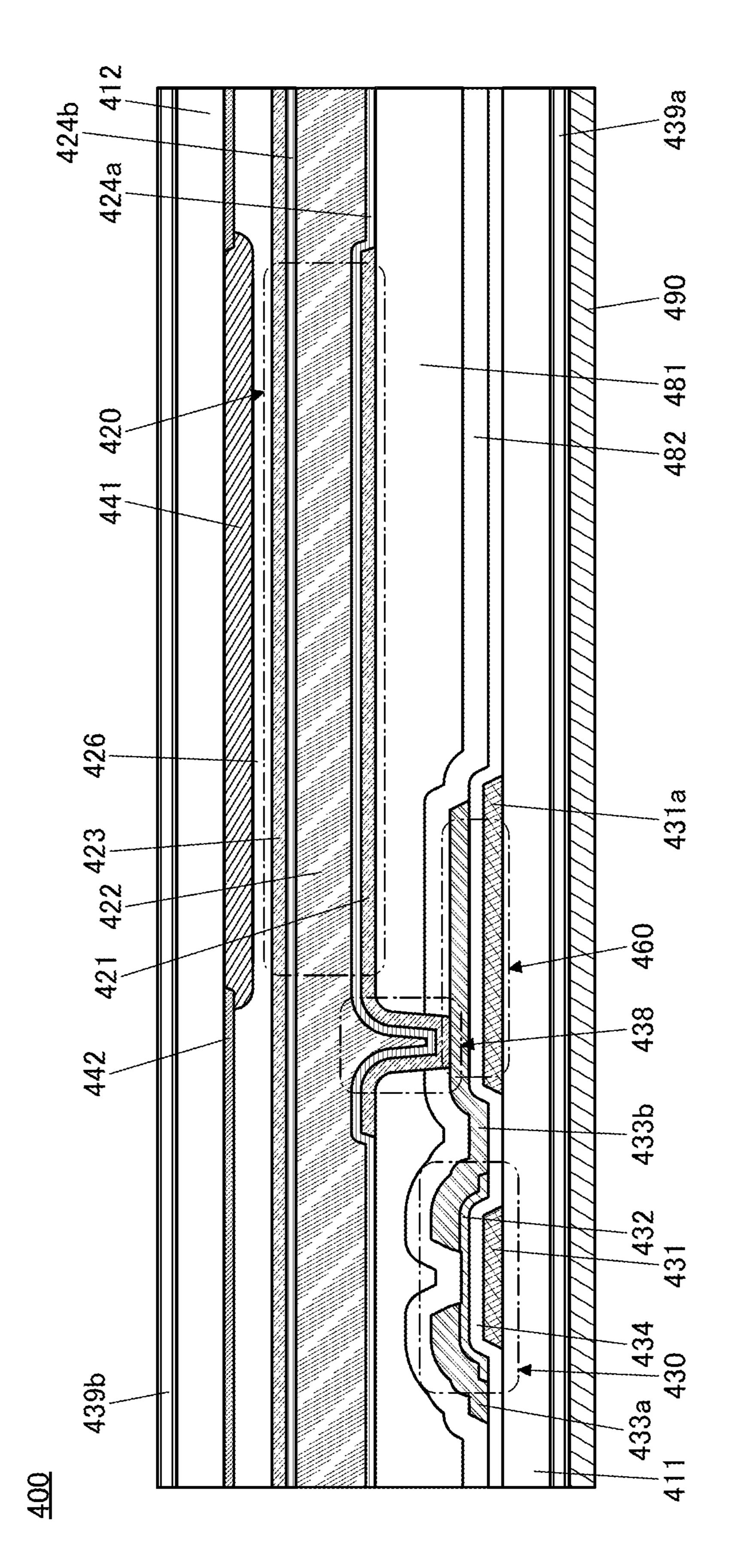

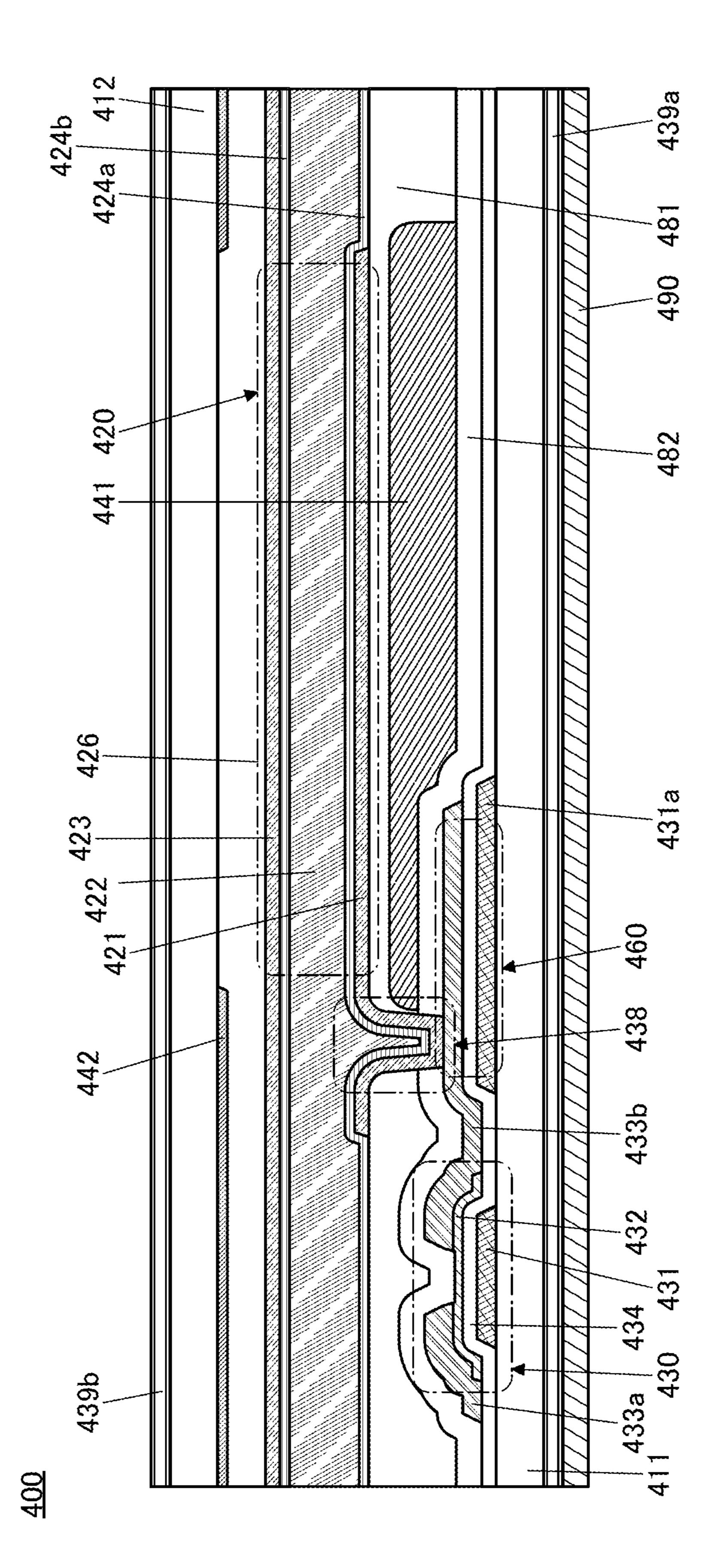

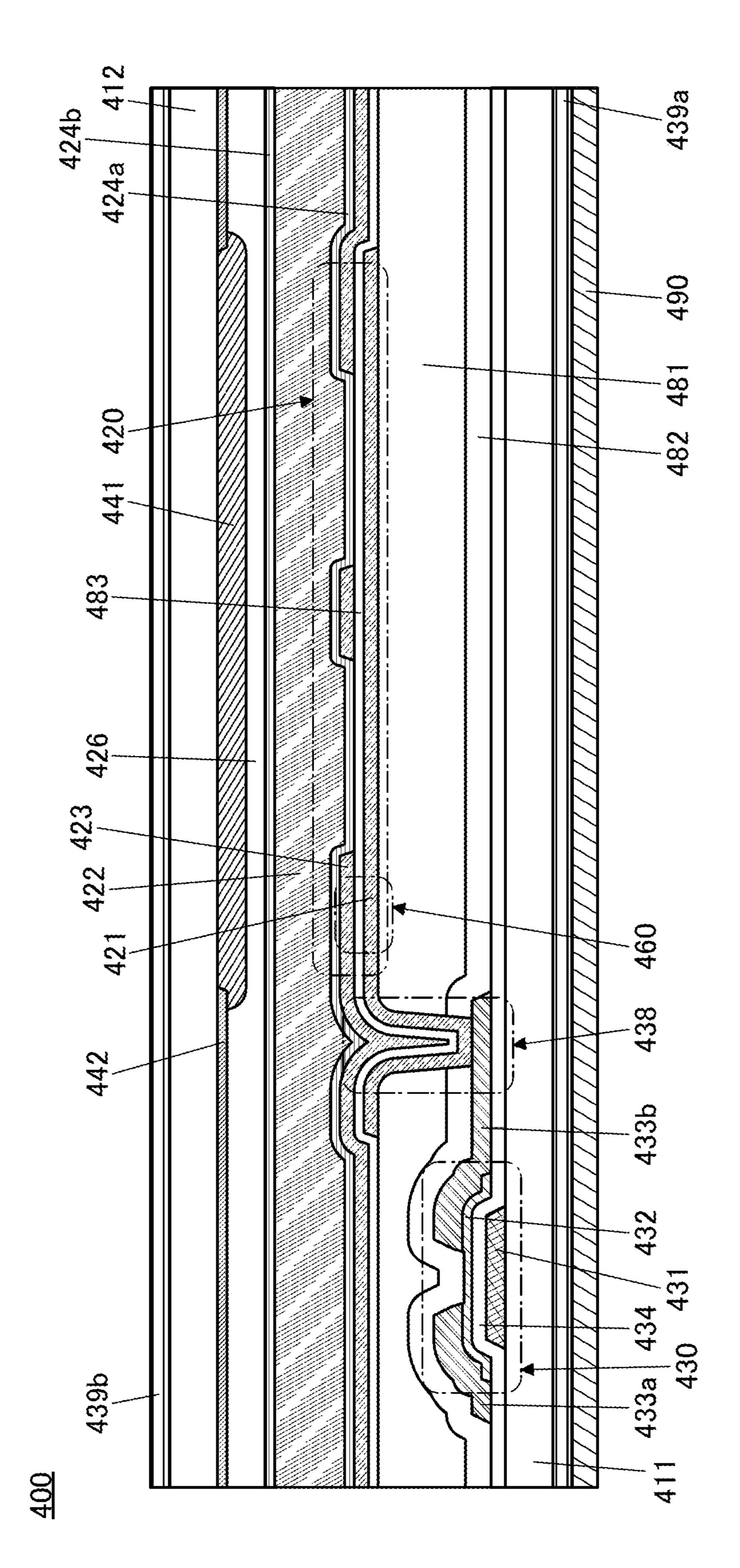

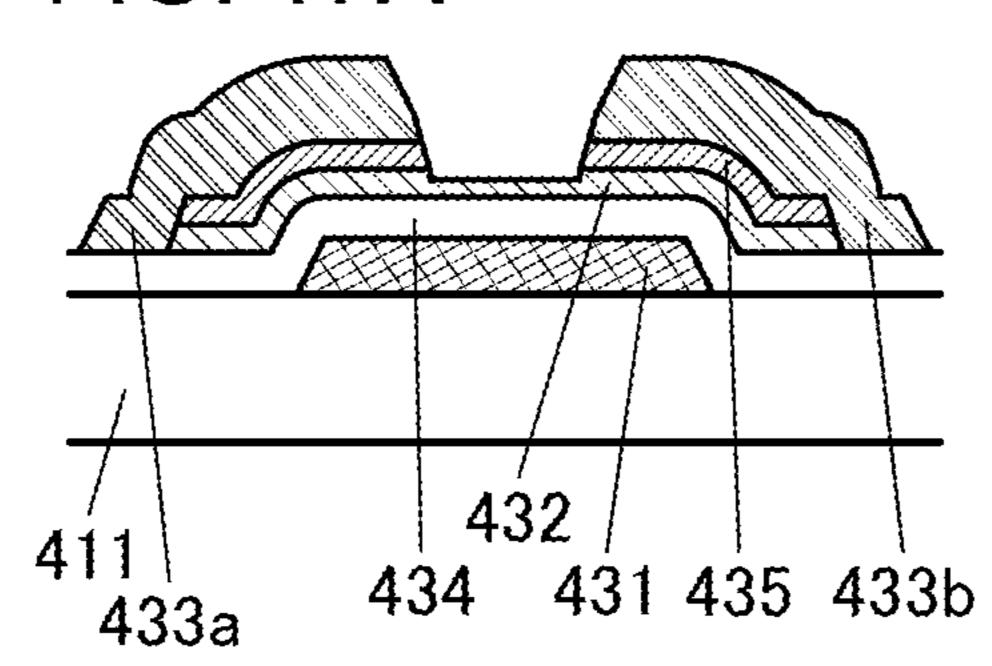

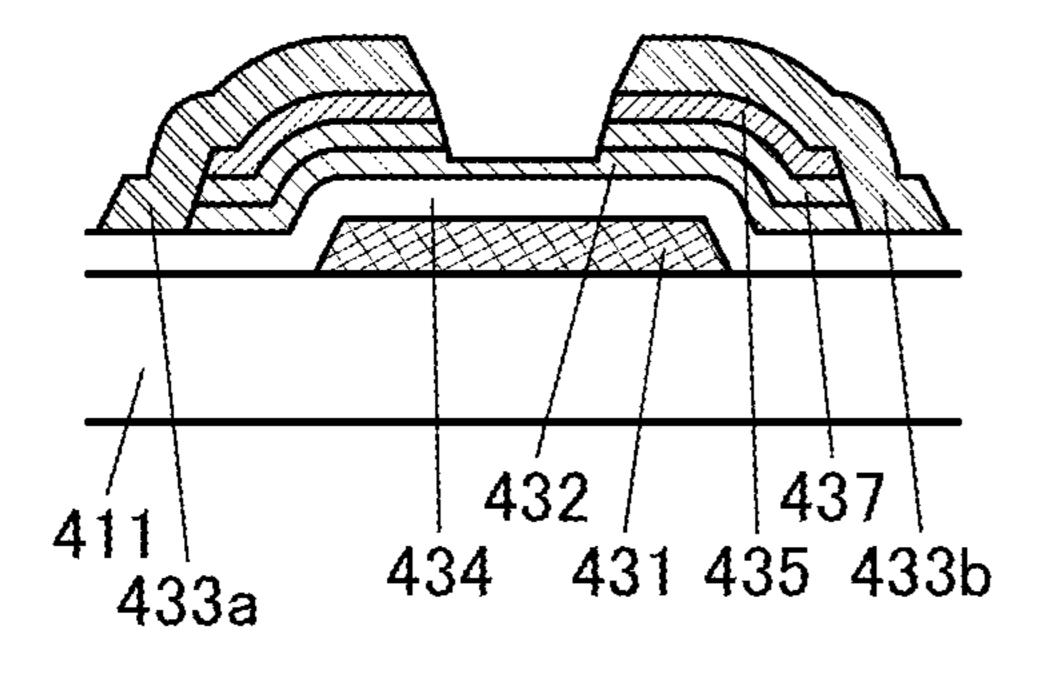

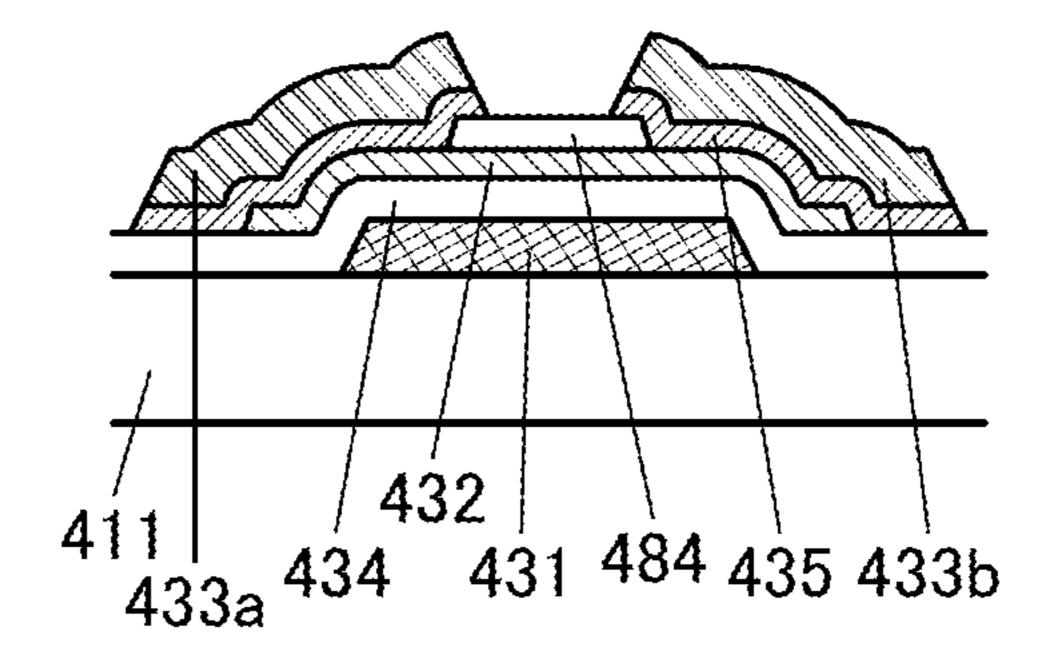

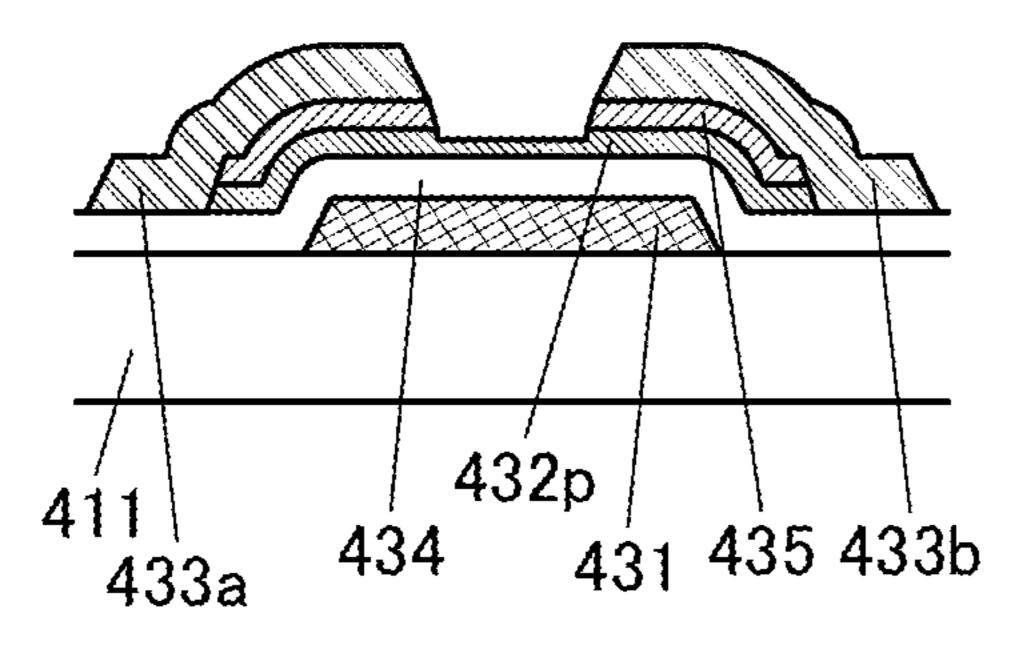

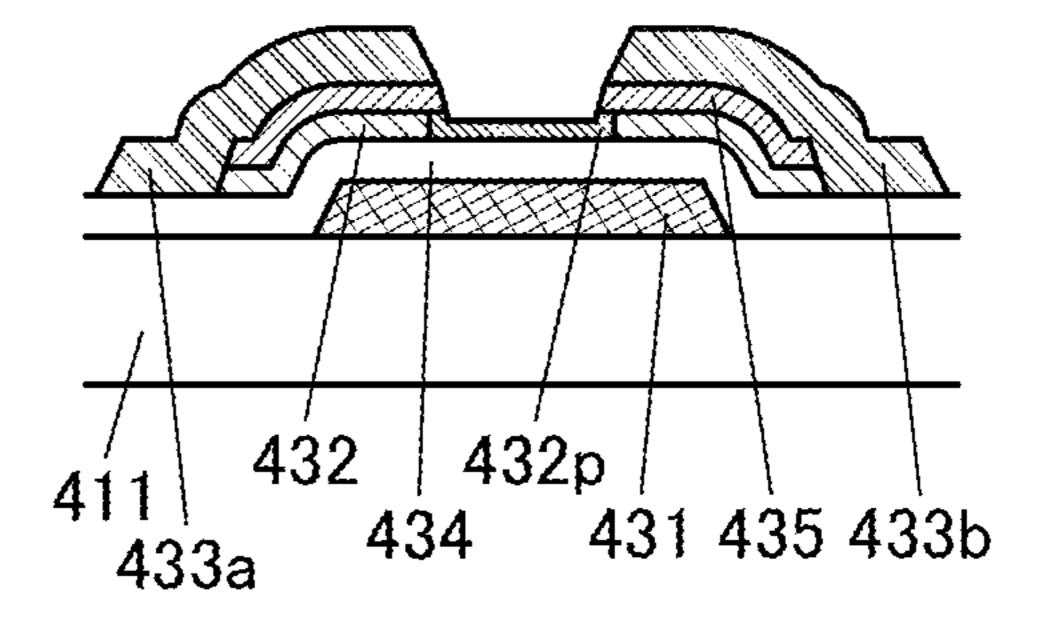

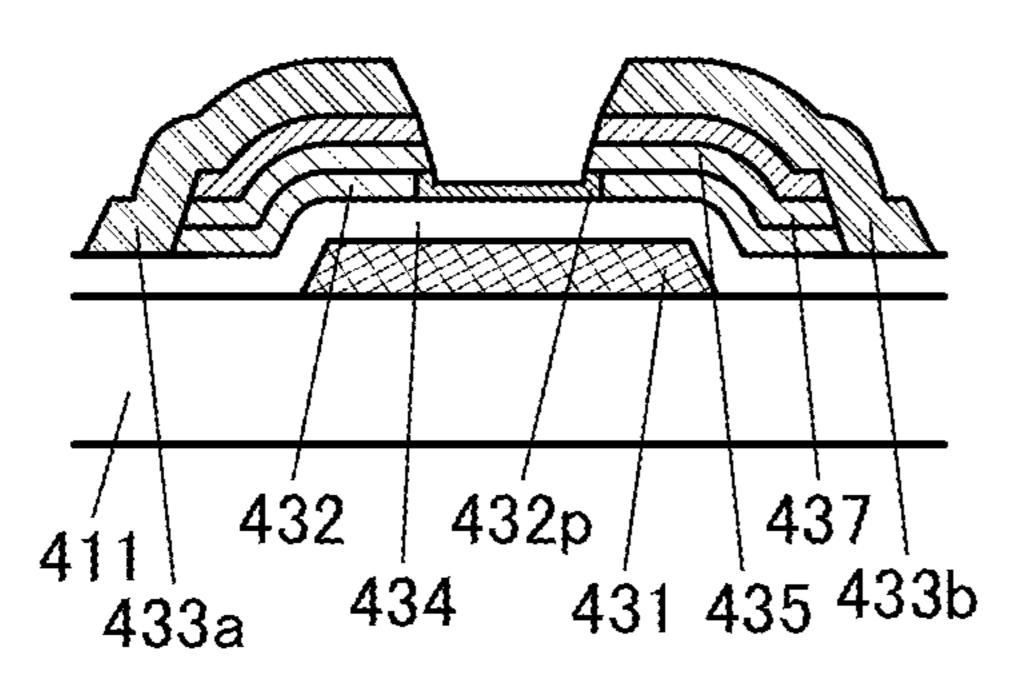

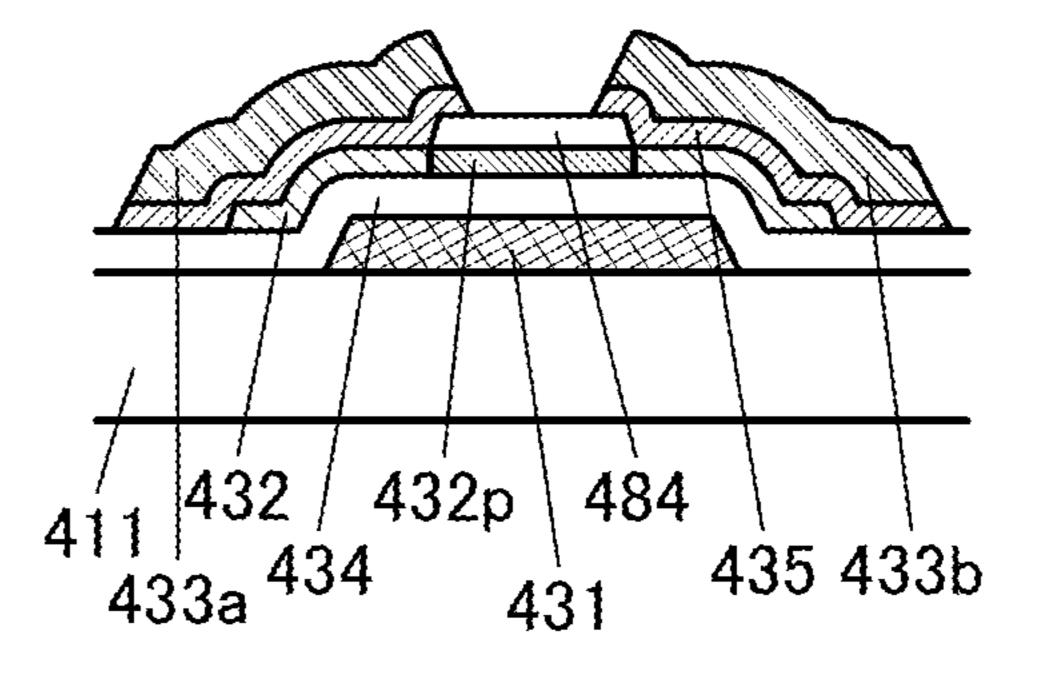

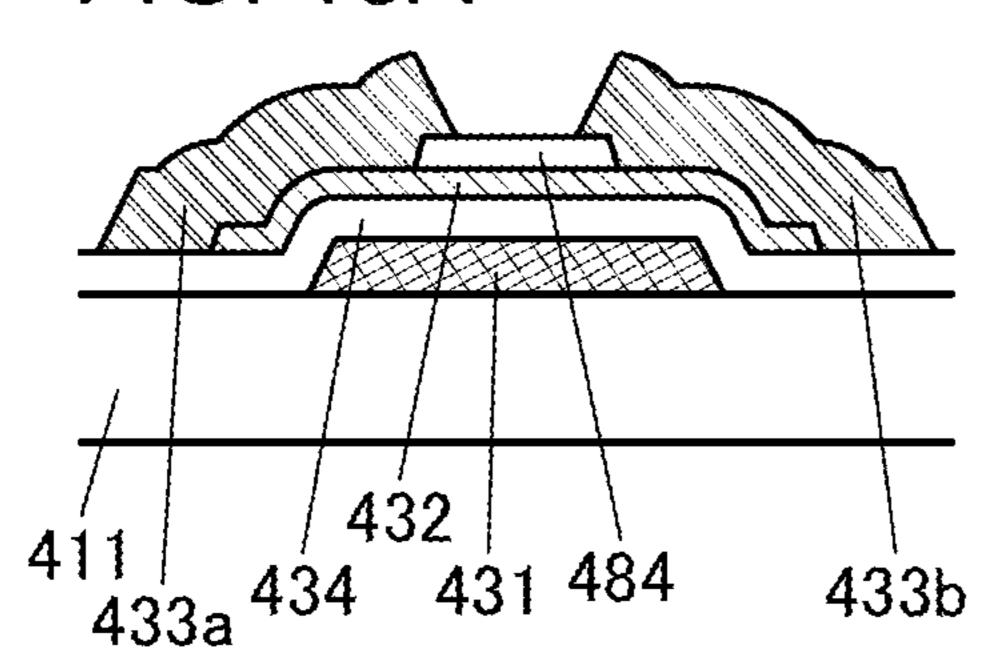

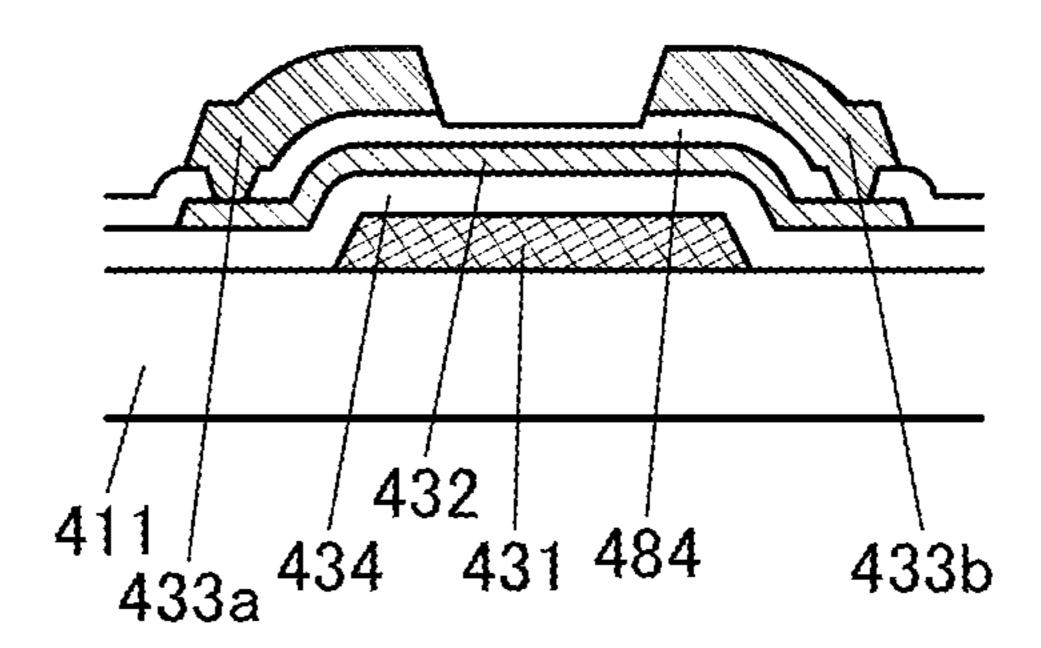

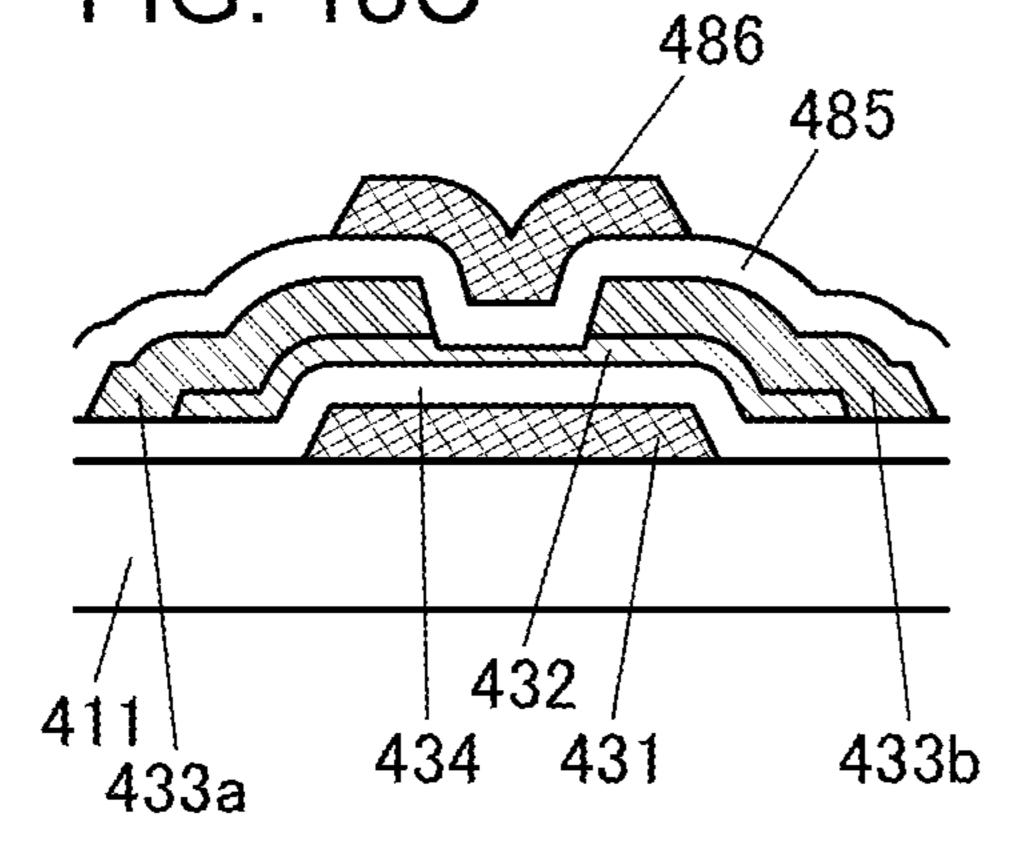

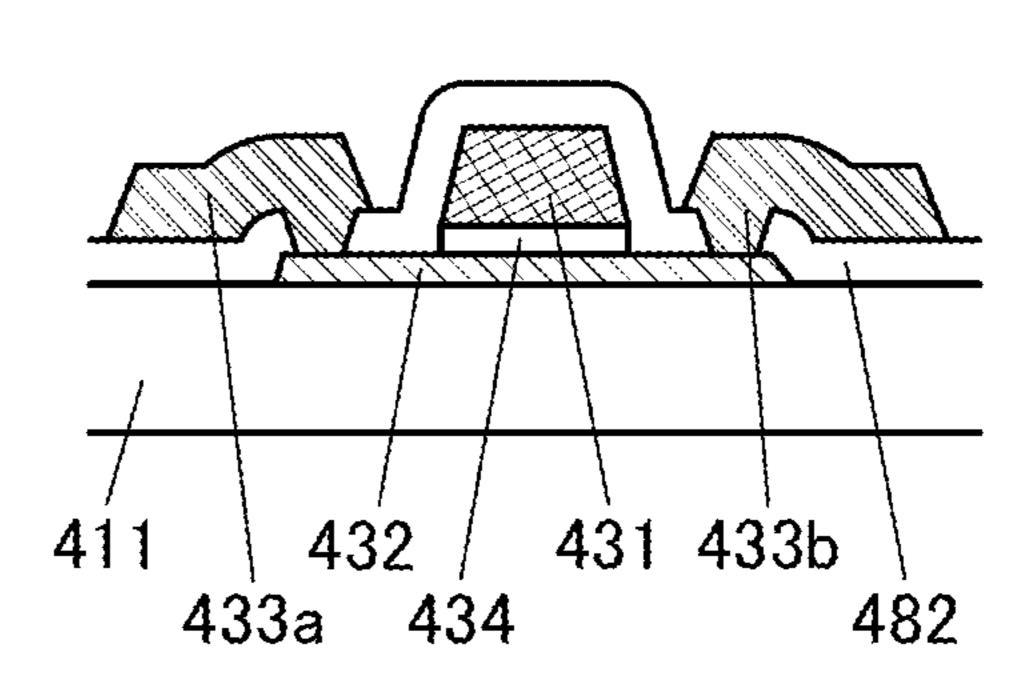

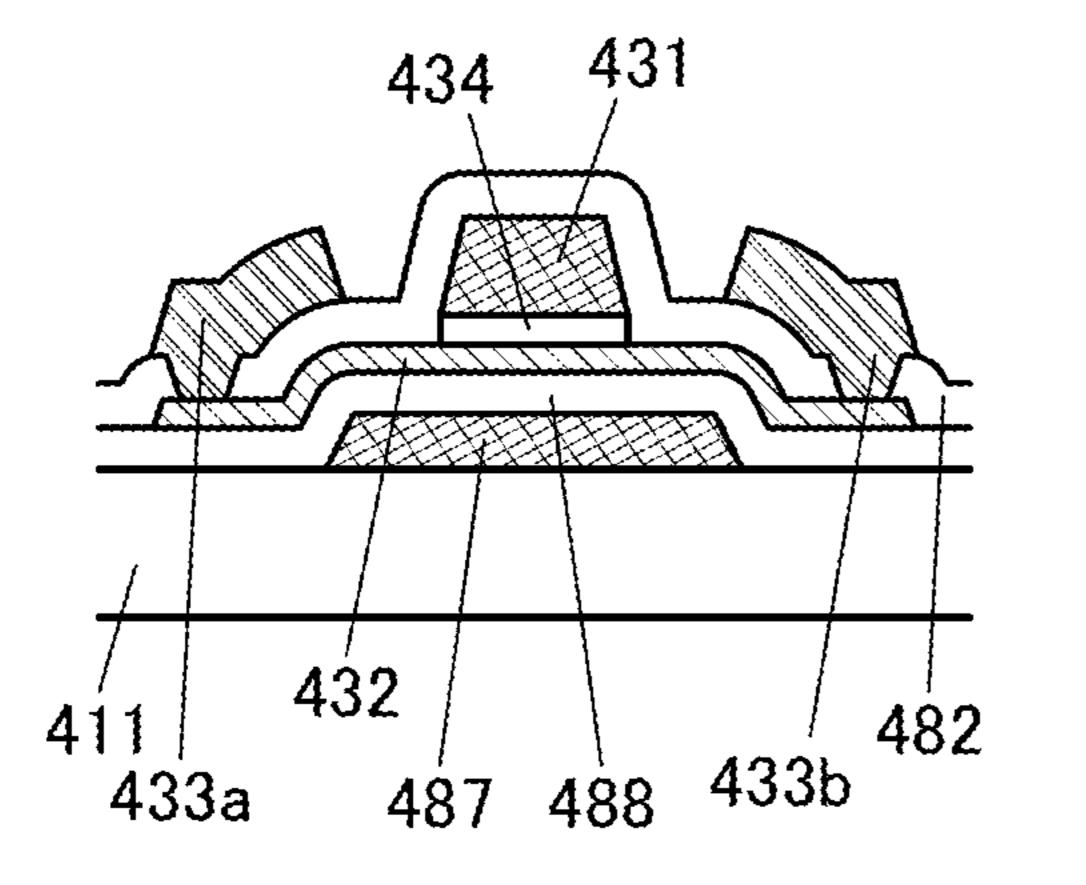

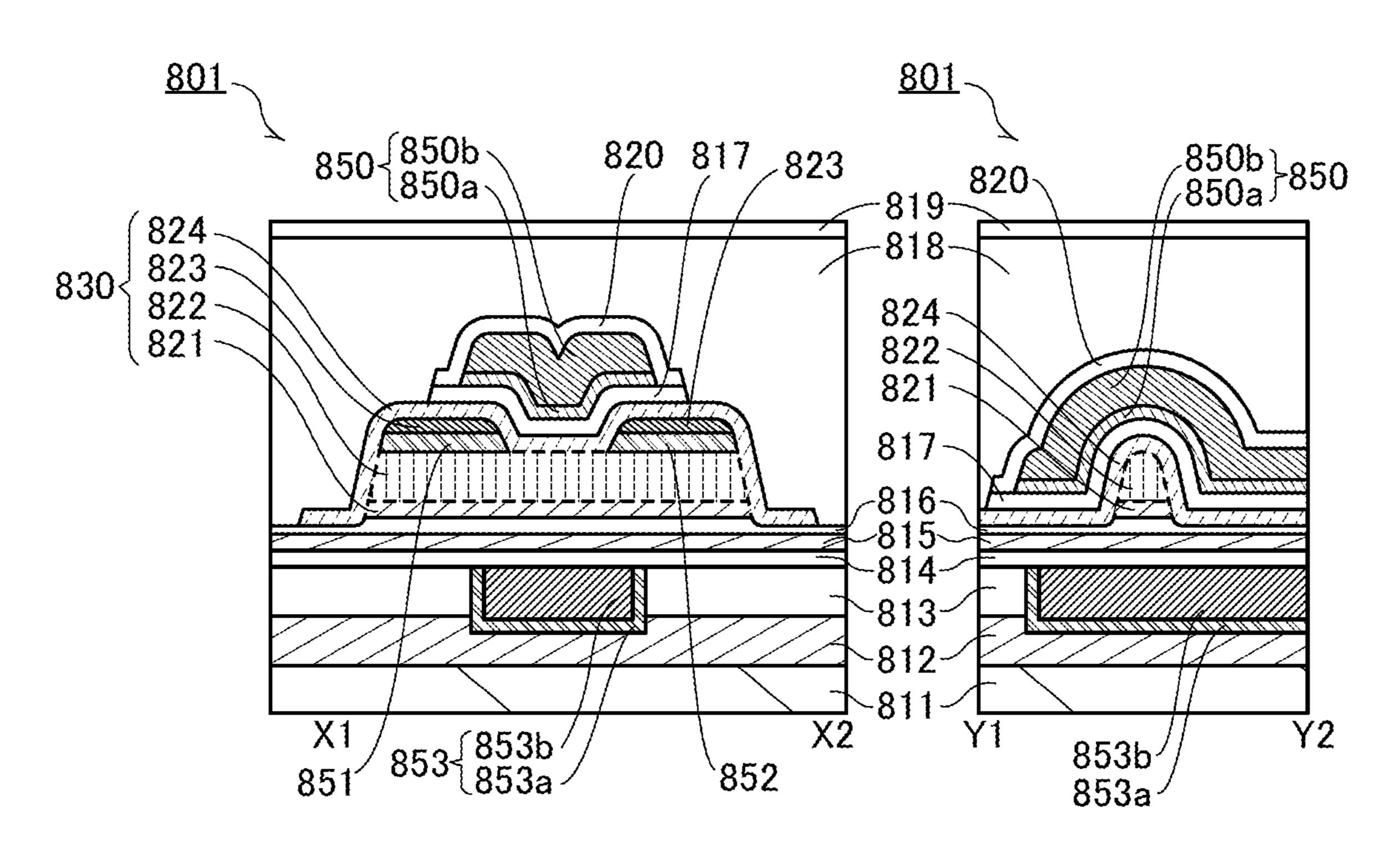

FIGS. 17A-17G Diagrams illustrating structure examples of a transistor.

FIGS. **18**A-**18**E Diagrams illustrating structure examples of a transistor.

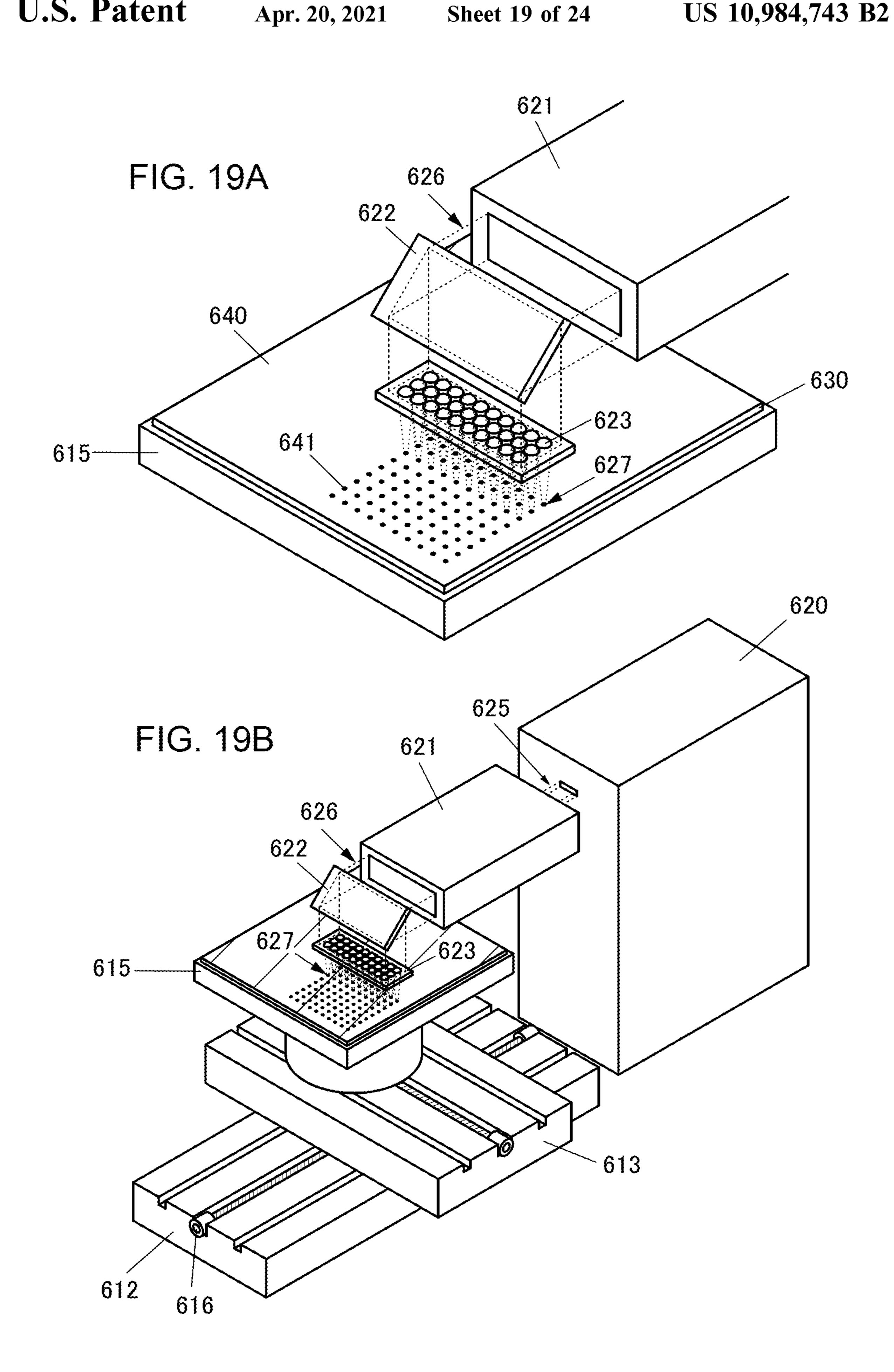

FIGS. 19A and 19B Diagrams showing a laser irradiation method and a laser crystallization apparatus.

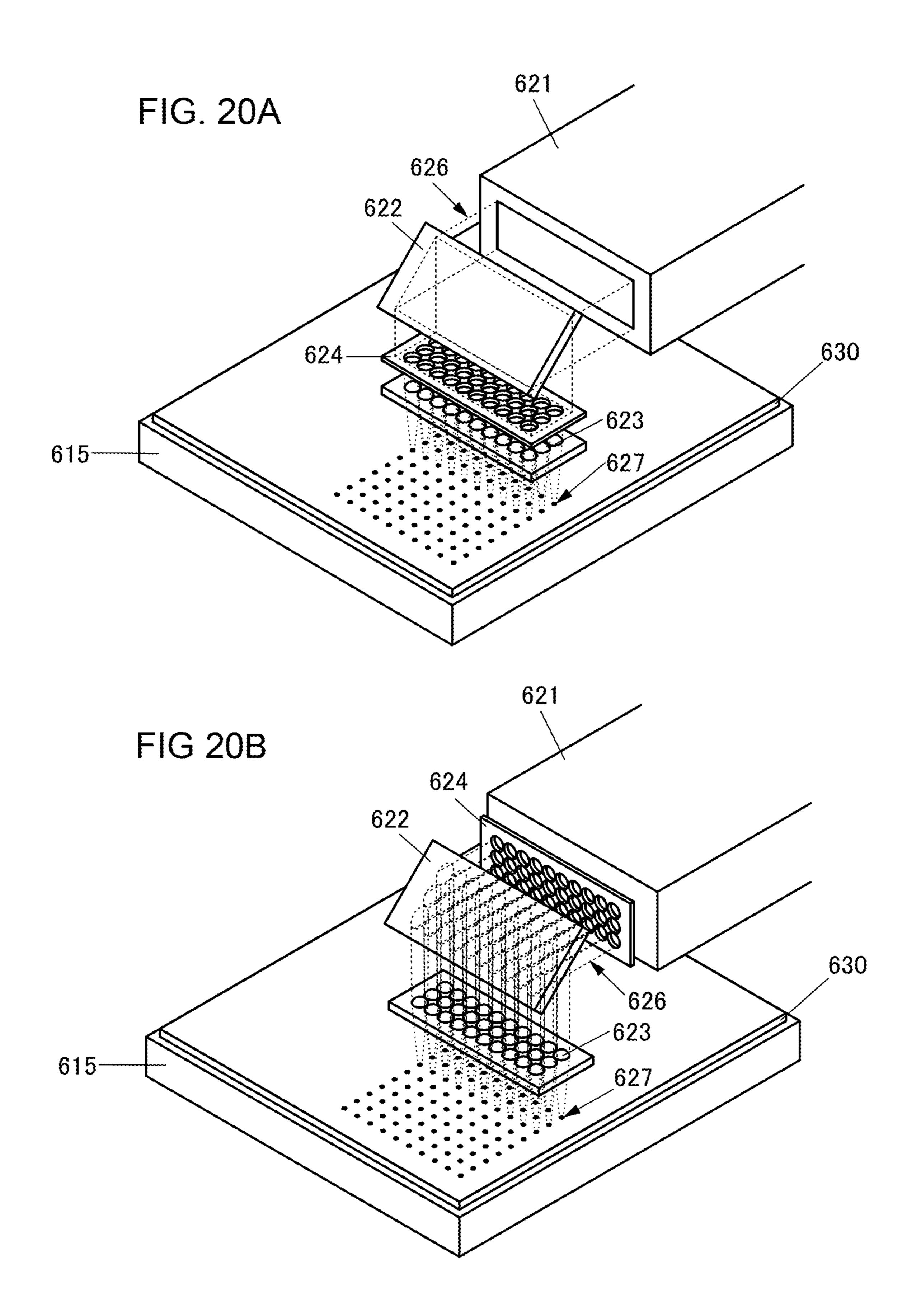

FIGS. 20A and 20B Diagrams showing laser irradiation methods.

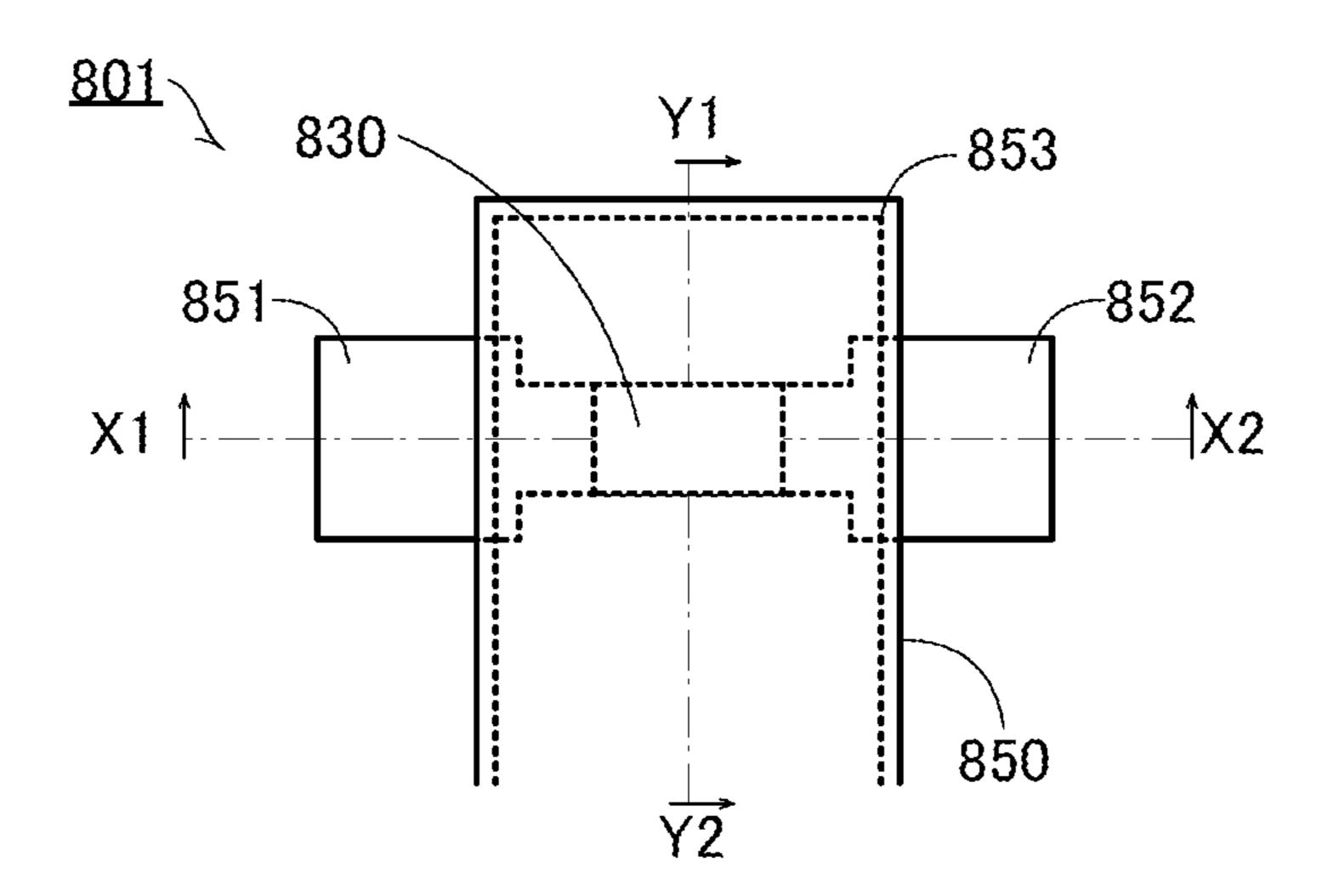

FIGS. 21A-21C Diagrams illustrating a structure example

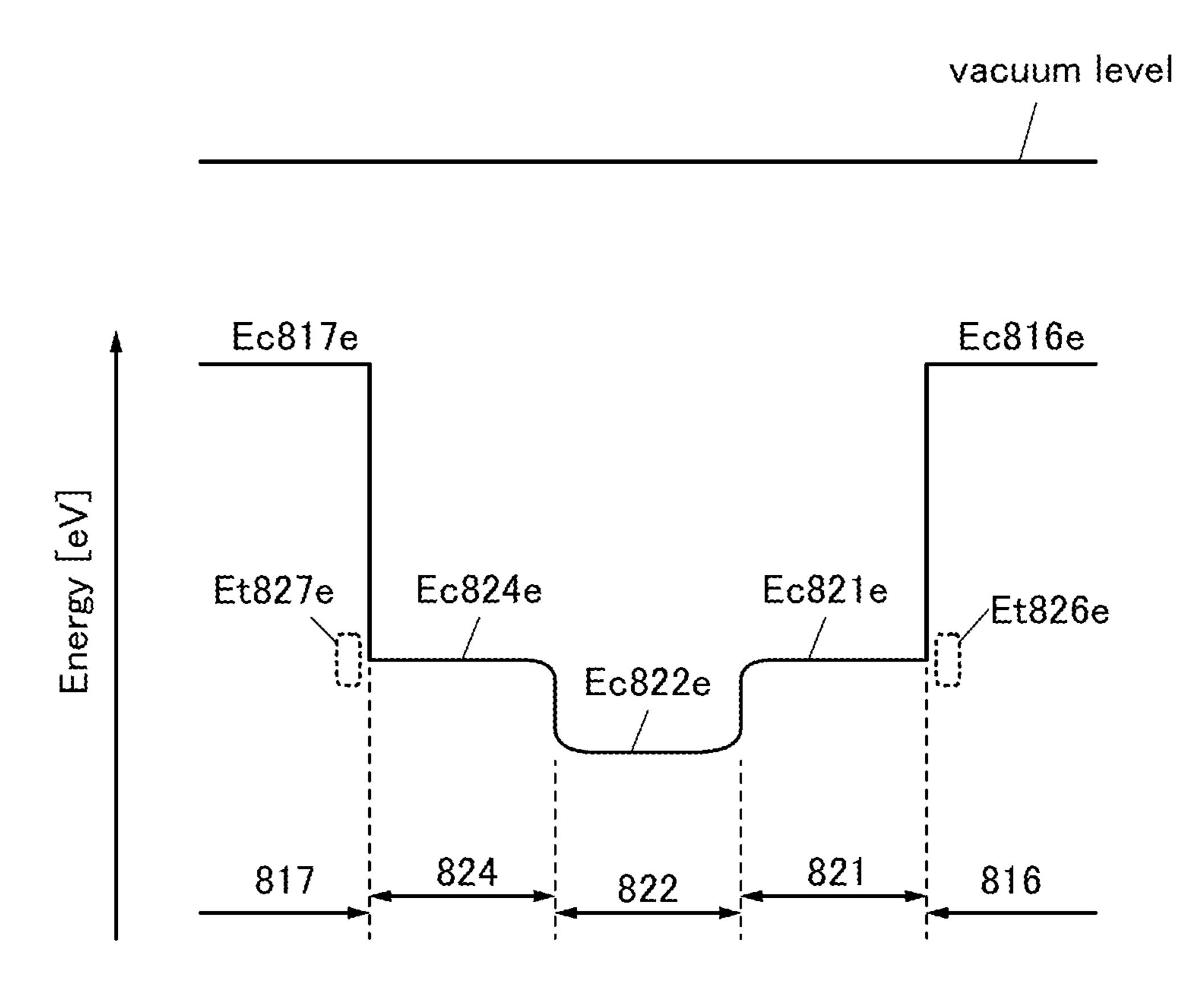

FIG. 22 A diagram showing an energy band structure.

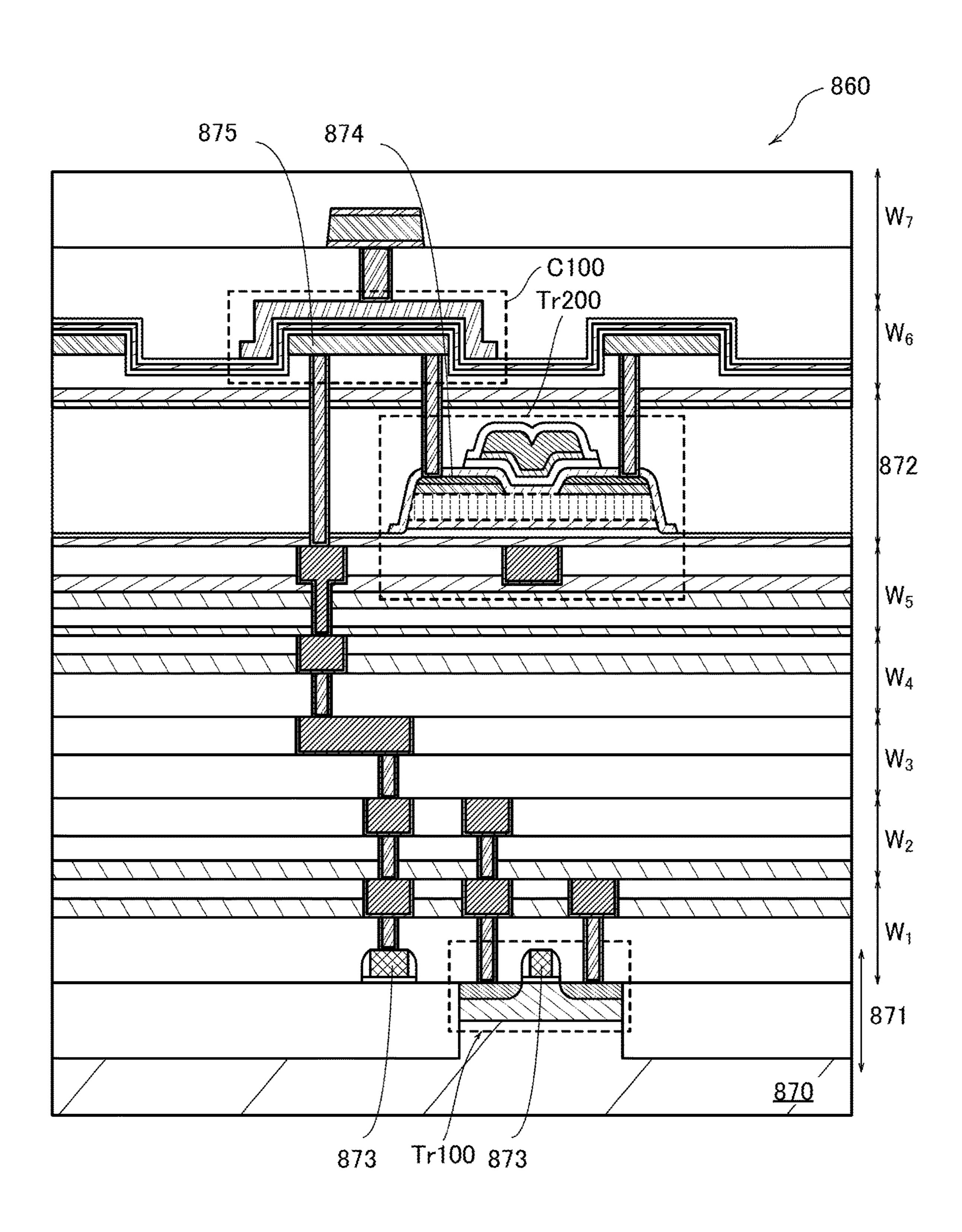

FIG. 23 A diagram illustrating a structure example of a semiconductor device.

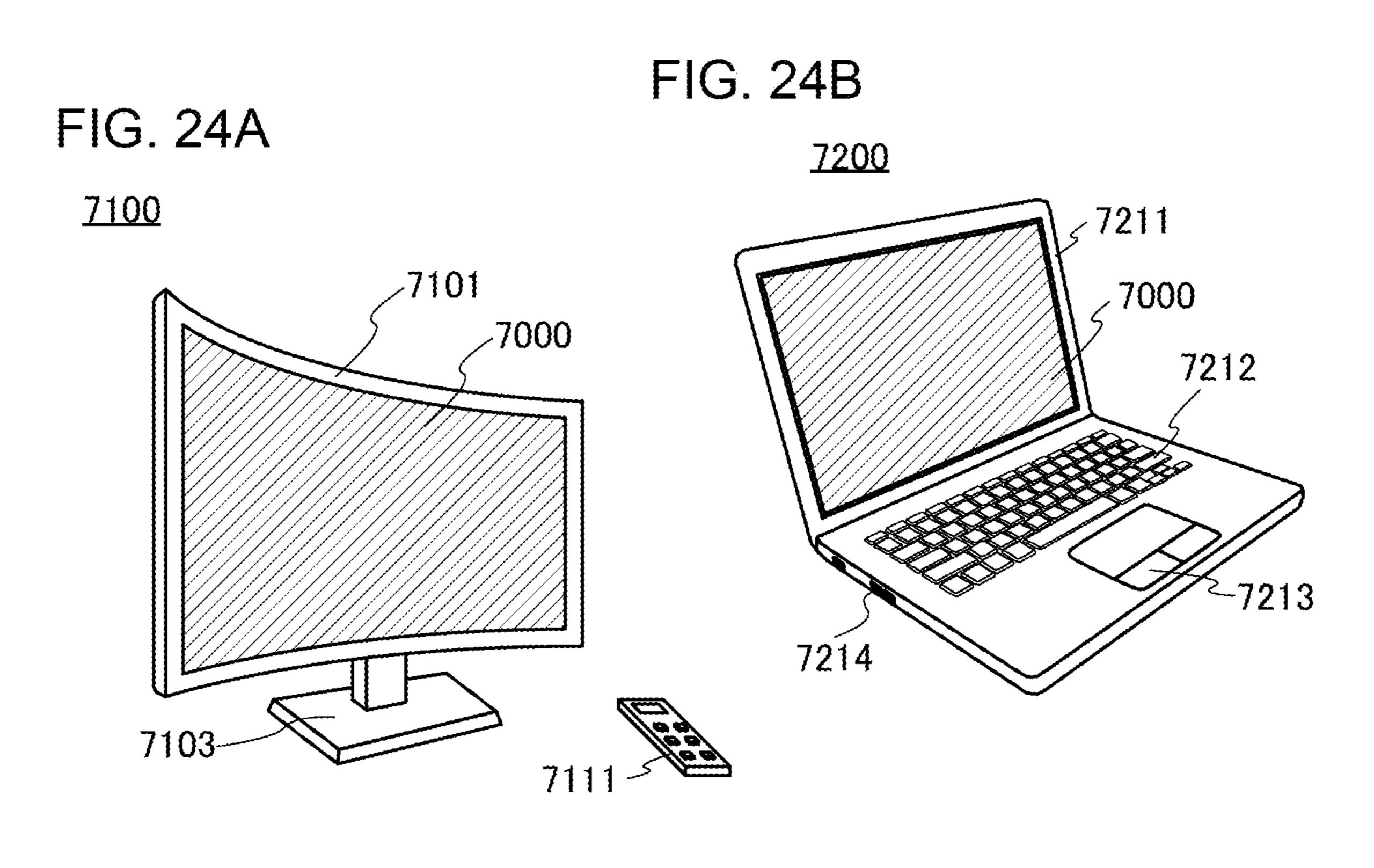

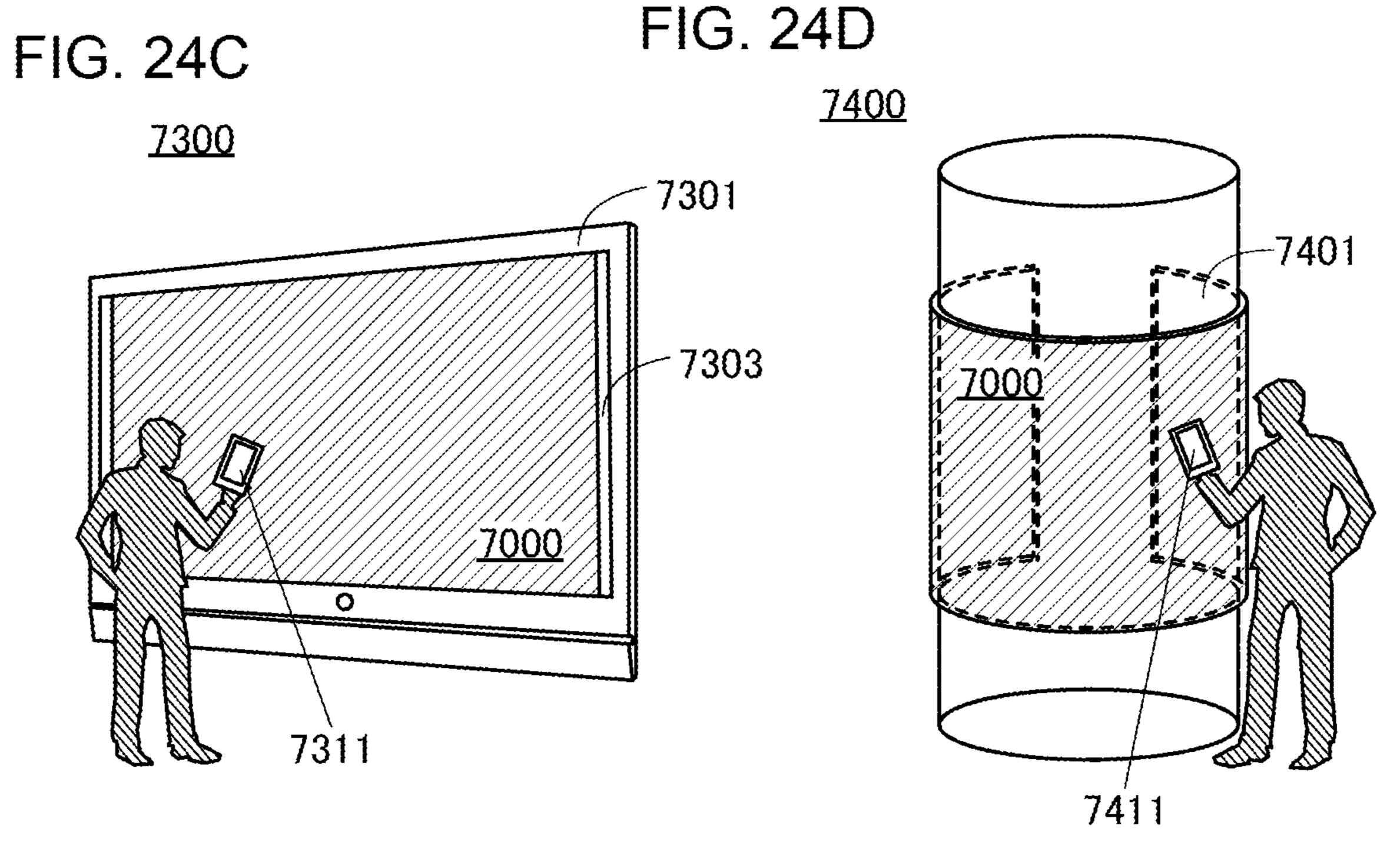

FIGS. **24**A-**24**D Diagrams illustrating structure examples of electronic devices.

### MODE FOR CARRYING OUT THE INVENTION

Embodiments of the present invention will be described below in detail with reference to the drawings. Note that the present invention is not limited to the description in the following embodiments, and it is easily understood by those skilled in the art that the modes and details can be changed in various ways without departing from the spirit and scope of the present invention. Thus, the present invention should not be interpreted as being limited to the following description of the embodiments.

One embodiment of the present invention includes, in its category, all devices such as a semiconductor device, a memory device, a display device, an imaging device, and an RF (Radio Frequency) tag. A display device includes, in its category, a liquid crystal display device, a light-emitting

device in which each pixel is provided with a light-emitting element typified by an organic light-emitting element, electronic paper, a DMD (Digital Micromirror Device), a PDP (Plasma Display Panel), an FED (Field Emission Display), and the like.

In this specification and the like, a metal oxide means an oxide of metal in a broad sense. Metal oxides are classified into an oxide insulator, an oxide conductor (including a transparent oxide conductor), an oxide semiconductor (also simply referred to as an OS), and the like. When a metal 10 oxide is used in a channel region of a transistor, for example, the metal oxide is called an oxide semiconductor in some cases. That is, when a metal oxide has at least one of an amplifying function, a rectifying function, and a switching function, the metal oxide can be referred to as a metal oxide 15 semiconductor, or an OS for short. Hereinafter, a transistor containing a metal oxide in a channel region is also referred to as an OS transistor.

In this specification and the like, a metal oxide containing nitrogen is also referred to as a metal oxide in some cases. 20 Moreover, a metal oxide containing nitrogen may be referred to as a metal oxynitride. The details of a metal oxide will be described later.

When this specification and the like explicitly state that X and Y are connected, the case where X and Y are electrically 25 connected, the case where X and Y are functionally connected, and the case where X and Y are directly connected are regarded as being disclosed in this specification and the like. Accordingly, without limitation to a predetermined connection relation, for example, a connection relation 30 shown in drawings or text, another connection relation is regarded as being disclosed in the drawings or the text. Here, X and Y denote an object (e.g., a device, an element, a circuit, a wiring, an electrode, a terminal, a conductive film, or a layer).

An example of the case where X and Y are directly connected is the case where an element that allows electrical connection between X and Y (e.g., a switch, a transistor, a capacitor, an inductor, a resistor, a diode, a display element, a light-emitting element, or a load) is not connected between 40 X and Y, and is the case where X and Y are connected without an element that allows electrical connection between X and Y (e.g., a switch, a transistor, a capacitor, an inductor, a resistor, a diode, a display element, a light-emitting element, or a load) placed therebetween.

In an example of the case where X and Y are electrically connected, at least one element that allows electrical connection between X and Y (e.g., a switch, a transistor, a capacitor, an inductor, a resistor, a diode, a display element, a light-emitting element, or a load) can be connected 50 between X and Y. Note that a switch has a function of being controlled to be turned on or off. That is, a switch has a function of being turned on or off to control whether current flows therethrough or not. Alternatively, a switch has a function of selecting and changing a path through which 55 current flows. Note that the case where X and Y are electrically connected includes the case where X and Y are directly connected.

In an example of the case where X and Y are functionally connected, at least one circuit that allows functional connection between X and Y (e.g., a logic circuit (an inverter, a NAND circuit, a NOR circuit, or the like); a signal converter circuit (a DA converter circuit, an AD converter circuit, a gamma correction circuit, or the like), a potential level converter circuit (a power supply circuit (a step-up 65 circuit, a step-down circuit, or the like), a level shifter circuit for changing the potential level of a signal, or the like), a

6

voltage source, a current source, a switching circuit, an amplifier circuit (a circuit capable of increasing signal amplitude, the amount of current, or the like, an operational amplifier, a differential amplifier circuit, a source follower circuit, a buffer circuit, or the like), a signal generator circuit, a memory circuit, or a control circuit) can be connected between X and Y. Note that even if another circuit is provided between X and Y, for example, X and Y are regarded as being functionally connected when a signal output from X is transmitted to Y. Note that the case where X and Y are functionally connected includes the case where X and Y are directly connected and the case where X and Y are electrically connected.

Note that in the case where there is an explicit description "X and Y are electrically connected," the case where X and Y are electrically connected (i.e., the case where X and Y are connected with another element or another circuit placed therebetween), the case where X and Y are functionally connected (i.e., the case where X and Y are functionally connected with another circuit placed therebetween), and the case where X and Y are directly connected (i.e., the case where X and Y are connected without another element or another circuit placed therebetween) are regarded as being disclosed in this specification and the like. That is, in the case where there is an explicit description "being electrically connected," the same contents as the case where there is only an explicit description "being connected" are regarded as being disclosed in this specification and the like.

Components denoted by the same reference numerals in different drawings represent the same components, unless otherwise specified.

Even when a diagram shows that independent components are electrically connected to each other, one component has functions of a plurality of components in some cases. For example, when part of a wiring also functions as an electrode, one conductive film has functions of both of the components, the function of the wiring and the function of the electrode. Thus, "electrical connection" in this specification also includes such a case where one conductive film has functions of a plurality of components, in its category.

### Embodiment 1

In this embodiment, a semiconductor device according to one embodiment of the present invention will be described. <a href="Structure Example of Semiconductor Device">Structure Example of Semiconductor Device</a>>

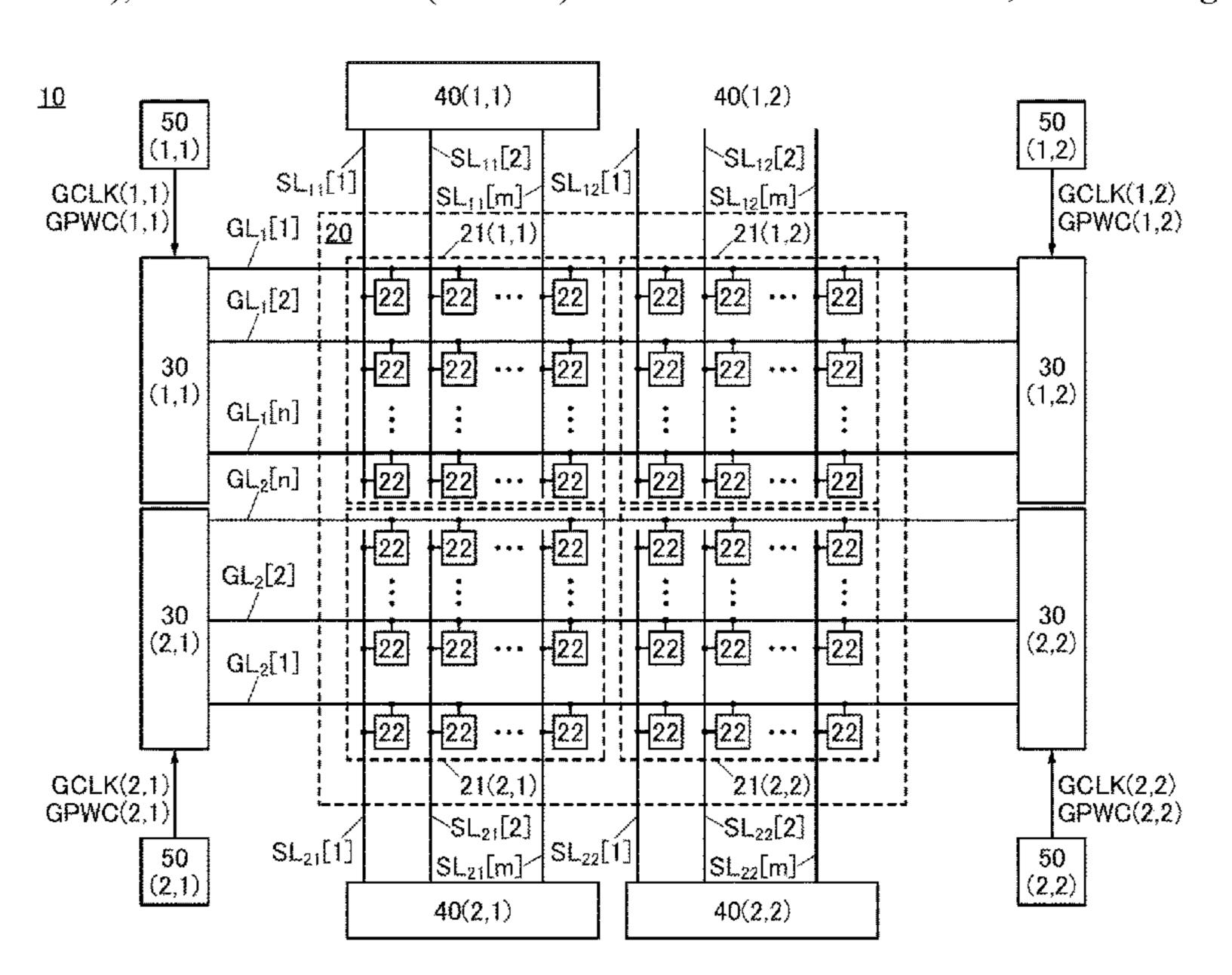

FIG. 1 illustrates a structure example of a semiconductor device 10. The semiconductor device 10 includes a pixel portion 20, a driver circuit 30, a driver circuit 40, and a signal generator circuit 50. The semiconductor device 10 has a function of displaying a predetermined image on the pixel portion 20 with the use of the driver circuit 30 and the driver circuit 40. Thus, the semiconductor device 10 can be used as a display device.

The pixel portion 20 is composed of a plurality of pixels 22 and has a function of displaying an image. The pixels 22 each include a display element and have a function of expressing a predetermined gray level. The gray levels of the pixels 22 are controlled with signals output from the driver circuit 30 and the driver circuit 40, and a predetermined image is displayed on the pixel portion 20.

Examples of the display element provided in the pixel 22 include a liquid crystal element and a light-emitting element. As the liquid crystal element, a transmissive liquid crystal element, a reflective liquid crystal element, a transflective liquid crystal element, or the like can be used. Moreover, as the display element, a MEMS (Micro Electro Mechanical

Systems) shutter element, an optical interference type MEMS element, or a display element using a microcapsule method, an electrophoretic method, an electrowetting method, an Electronic Liquid Powder (registered trademark) method, or the like can be used, for instance. In addition, examples of the light-emitting element include self-luminous light-emitting elements such as an OLED (Organic Light Emitting Diode), an LED (Light Emitting Diode), a QLED (Quantum-dot Light Emitting Diode), and a semiconductor laser. Specific structure examples of the pixel 22 will be described later.

The pixels 22 are connected to wirings SL and wirings GL. The wirings GL are connected to the driver circuit 30, and the wirings SL are connected to the driver circuit 40. The wiring GL is supplied with a signal for selecting the pixel 22 (hereinafter also referred to as a selection signal). The wiring SL is supplied with a signal for making the pixel 22 express a predetermined gray level (hereinafter also referred to as an image signal). An image signal is supplied to the pixel 22 that has been supplied with a selection signal, whereby the 20 image signal is written to the pixel 22.

The driver circuit 30 has a function of supplying a selection signal to the pixel 22. Specifically, the driver circuit 30 has a function of supplying a selection signal to the wiring GL, and the wiring GL has a function of trans- 25 mitting the selection signal output from the driver circuit 30 to the pixel 22. Note that the wiring GL can also be referred to as a selection signal line, a gate line, or the like.

The driver circuit 40 has a function of supplying an image signal to the pixel 22. Specifically, the driver circuit 40 has 30 a function of supplying an image signal to the wiring SL, and the wiring SL has a function of transmitting the image signal output from the driver circuit 40 to the pixel 22. Note that the wiring SL can also be referred to as an image signal line, a source line, or the like.

The number of pixels 22 included in the pixel portion 20 can be set freely. In order to display a high-resolution image, it is preferable to arrange many pixels 22. For example, pixels 22 of 1920×1080 or more are preferably provided in the case of displaying 2K images. Furthermore, pixels 22 of 40 3840×2160 or more or 4096×2160 or more are preferably provided in the case of displaying 4K images. Moreover, pixels 22 of 7680×4320 or more are preferably provided in the case of displaying 8K images.

In the case where a large number of pixels 22 are provided 45 in the pixel portion 20 to display high-resolution images such as the above-described 2K, 4K, and 8K images, the length of the wirings GL and the wirings SL is increased, and the parasitic resistance of the wirings GL and the wirings SL is increased accordingly. In addition, as illustrated in FIG. 1, 50 the wirings GL and the wirings SL are provided so as to intersect with each other. Thus, when the number of pixels 22 is increased, the number of intersections is also increased, and parasitic capacitance formed by the wirings GL and the wirings SL is increased. For this reason, FIG. 1 employs a 55 structure where the pixel portion 20 is divided into a plurality of regions 21, and each region 21 is provided with the driver circuit 30 and the driver circuit 40.

Specifically, in FIG. 1, the pixel portion 20 is divided into four regions 21 (21(1, 1) to (2, 2)), and the four regions 21 60 each include m columns and n rows of pixels 22 (m and n are natural numbers). In addition, four driver circuits 30 (30(1, 1) to (2, 2)) and four driver circuits 40 (40(1, 1) to (2, 2)) are provided in FIG. 1.

In FIG. 1, the wirings GL connected to the driver circuits 65 30(1, 1) and (1, 2) are denoted by wirings  $GL_1$ , and the wirings GL connected to the driver circuits 30(2, 1) and (2, 1)

8

2) are denoted by wirings  $GL_2$ . The wirings SL connected to the driver circuits 40(1, 1), (1, 2), (2, 1), and (2, 2) are denoted by wirings  $SL_{11}$ , wirings  $SL_{12}$ , wirings  $SL_{21}$ , and wirings  $SL_{22}$ , respectively. The wiring SL and the wiring GL connected to the pixel C in the i-th column and the j-th row (i is an integer of 1 to m; j is an integer of to 1 to n) are denoted by a wiring SL[i] and a wiring GL[j], respectively.

Image signals are supplied to the regions 21(1, 1) to (2, 2) from the respective driver circuits 40(1, 1) to (2, 2). Thus, image signals can be supplied from the driver circuits 40(40(1, 1)) and (1, 2) to the pixels 22 that belong to the regions 21(21(1, 1)) and (1, 2) in the pixel portion 20, and image signals can be supplied from the driver circuits 40(40(2, 1)) and (2, 2) to the pixels 22 that belong to the regions 21(21(2, 1)) and (2, 2) in the pixel portion 20. Consequently, the wirings SL connected to one driver circuit 40 can be shortened; hence, the parasitic resistance and parasitic capacitance can be reduced, and image signals can be supplied at high speed.

Note that FIG. 1 illustrates a structure example in which the pixel portion 20 region is divided into the four regions 21(1, 1), (1, 2), (2, 1),and (2, 2). In this case, the timings for outputting image signals from the driver circuits 40(1, 1) and (1, 2) are synchronized, and the timings for outputting image signals from the driver circuits 40(2, 1) and (2, 2) are synchronized. Note that the driver circuit 40 that supplies image signals to the regions 21(1, 1) and (1, 2) may be formed of a circuit in which the driver circuits 40(1, 1) and (1, 2) are integrated. Moreover, the driver circuit 40 that supplies image signals to the regions 21(2, 1) and (2, 2) may be formed of a circuit in which the driver circuits 40(2, 1) and (2, 2) are integrated. Furthermore, each of the driver circuits 40(1, 1), (1, 2), (2, 1),and (2, 2) may be formed of a plurality of driver circuits.

In FIG. 1, two driver circuits 30 are connected to one wiring GL. Specifically, the pixels 22 included in the regions 21(1, 1) and (1, 2) are connected to the driver circuits 30(1, 1) and (1, 2) through the wirings GL. Moreover, the pixels 22 included in the regions 21(2, 1) and (2, 2) are connected to the driver circuits 30(2, 1) and (2, 2) through the wirings GL. Thus, selection signals can be supplied from opposite ends of the wiring GL, which enables the selection signals to be supplied at high speed. Note that in the case where transmission of selection signals is not hindered, one of the driver circuits 30(1, 1) and (1, 2) and one of the driver circuits 30(2, 1) and (2, 2) can be omitted.

Although FIG. 1 shows the case where the pixel portion 20 is divided into four regions 21, the divisor is not particularly limited and can be set freely. Moreover, although FIG. 1 illustrates an example in which the numbers of columns and the numbers of rows of the pixels 22 included in the four regions 21 are the same, the number of columns and the number of rows of the pixels 22 are not limited thereto and can be set freely in each region 21.

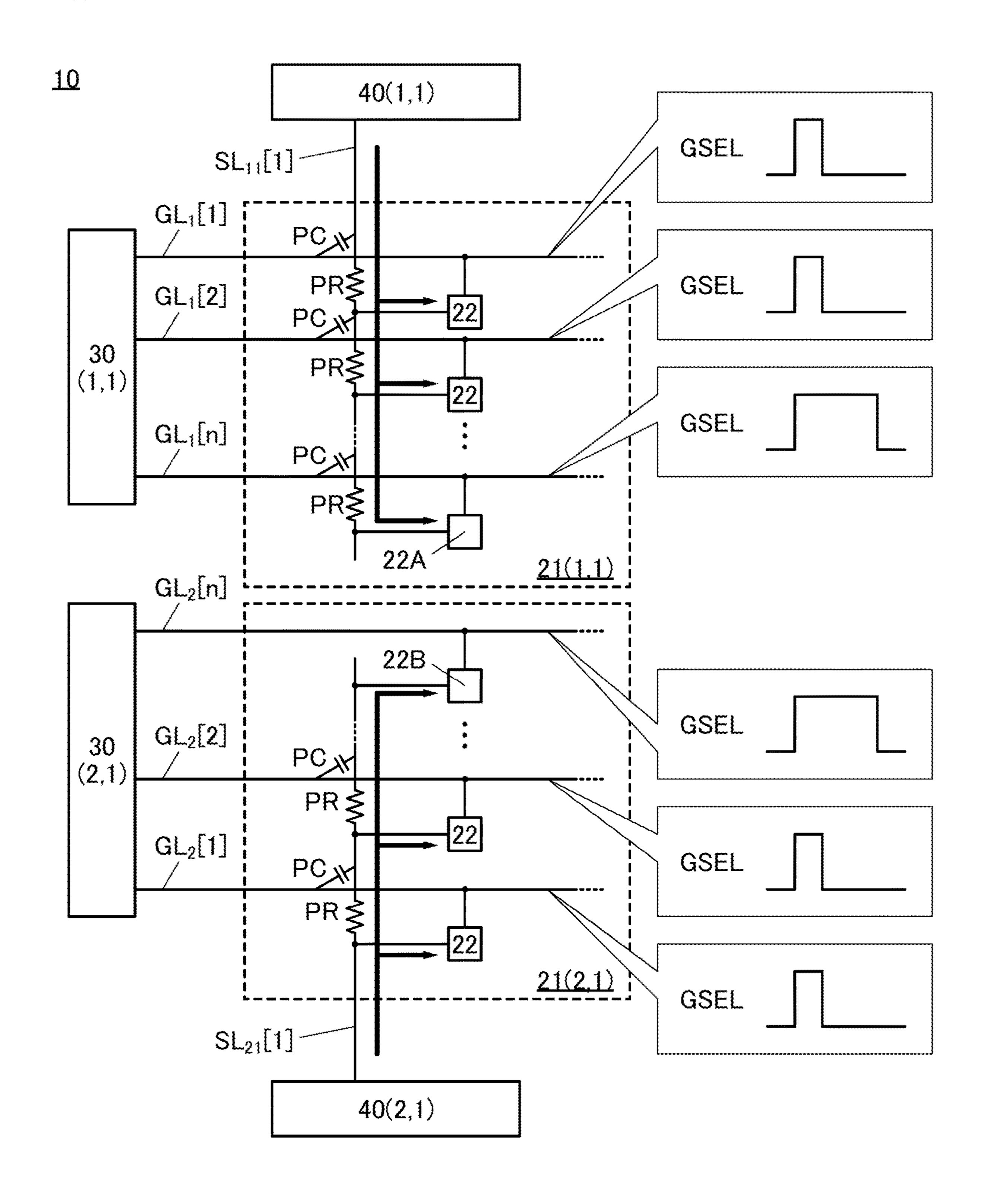

In the case where the pixel portion 20 is divided into a plurality of regions 21 as described above, the image continuity is preferably ensured at a junction of the regions 21. However, gray levels expressed by the pixels 22 around the junctions particularly tend to vary owing to the influence of the parasitic resistance and parasitic capacitance of the wirings SL or the like. For example, the case where image signals are supplied to the wiring SL[1] in the regions 21(1, 1) and (2, 1) as illustrated in FIG. 2 is considered. Here, parasitic capacitance PC, wiring resistance PR, and the like formed at the intersections with the wirings GL and the like are added to the wiring SL; hence, image signals may delay. More specifically, as the distance between the driver circuit

40 and the pixel 22 is longer and the path of an image signal formed in the wiring SL is longer, the parasitic resistance PR increases. Moreover, as the number of intersections of the wirings GL and the wiring SL is larger, the parasitic capacitance PC increases. Thus, the image signal delay increases. The image signal delay reaches its maximum when the image signal is supplied to the pixel 22 that is farthest from the driver circuit 40 (pixels 22A and 22B in the diagram).

If the pulse width of selection signals supplied to the wirings GL[1] to [n] (n here is an integer of 1 or more) is set in accordance with the pixel 22 that is provided comparatively close to the driver circuit 40, before writing of image signals is completed, the pixels 22A and 22B may become a non-selected state because of the above-described image signal delay. Consequently, writing of image signals to the pixels 22A and 22B may vary levels expressed by the pixels 22A and 22B may vary. Furthermore, in a region at the junction of the regions 21(1, 1) and (2, 1) shown in FIG. 2, the pixels 22A and 22B, where a variation in gray level due to the signal delay is most likely to occur, are adjacent to each other. Thus, a discontinuous image may be generated in this region.

On the other hand, to ensure the image continuity, the pulse width of selection signals can be set in accordance with the pixels 22A and 22B provided near the ends of the 25 wirings SL. However, in this case, selection periods for all the pixels 22 need to be set long, so that the time required to select all the rows is increased. Thus, the time required to update an image is increased, and the operating speed is lowered.

Here, the semiconductor device 10 according to one embodiment of the present invention has a function of changing the selection period of the pixel 22 in accordance with the distance from the driver circuit 40. Specifically, when the distance between a first pixel 22 and the driver 35 circuit 40 is longer than the distance between a second pixel 22 and the driver circuit 40, the pulse width of a selection signal supplied to the first pixel 22 is set larger than the pulse width of a selection signal supplied to the second pixel 22. Accordingly, writing of image signals to the pixels 22 provided far from the driver circuit 40 can be accurately performed while the selection period for the pixels 22 provided near the driver circuit 40 is kept short.

Note that the above-described distance between the pixel 22 and the driver circuit 40 means the length of an image 45 signal path formed between the pixel 22 and the driver circuit 40 when an image signal is supplied from the driver circuit 40 to the pixel 22 through the wiring SL. In addition, the pulse width of a selection signal corresponds to a period during which the selection signal is continuously supplied. 50 For example, when a high-level signal is supplied as a selection signal, a period during which the potential of the wiring GL is kept at high level corresponds to the pulse width of the selection signal. Moreover, the pulse width of a selection signal corresponds to a selection period of the 55 pixel 22 connected to the wiring GL (a period during which a selected state is maintained).

FIG. 2 shows an operation example in which the pulse width of a selection signal is controlled. A signal GSEL with a small pulse width can be supplied to the wirings GL 60 (wirings GL<sub>1</sub>[1] and [2] and wirings GL<sub>2</sub>[1] and [2]) connected to the pixels 22 provided near the driver circuit 40, and the signal GSEL with a large pulse width can be supplied to the wirings GL (a wiring GL<sub>1</sub>[n] and a wiring GL<sub>2</sub>[n]) connected to the pixels 22 provided far from the 65 driver circuit 40. Note that the signal GSEL shown in FIG. 2 is a selection signal. Accordingly, image signals can be

**10**

accurately written to the pixels 22, and the image continuity around the junction of the regions 21 (a region where the pixels 22A and 22B are adjacent to each other) can be secured.

The pulse width of the signal GSEL can be set freely without being limited to the above. For example, the pulse width of the signal GSEL can be changed for every wiring GL so that the signal GSEL with a larger pulse width is supplied to the pixel 22 placed further from the driver circuit 40. Alternatively, the pulse width can be widened only for the signal GSEL supplied to the pixels 22 belonging to a predetermined row that is distant from the driver circuit 40 (e.g., a row around the n-th row in the regions 21(1, 1) and (2, 1)).

The pulse width of a selection signal can be controlled by controlling a variety of signals supplied to the driver circuit 30. FIG. 1 illustrates a structure example in which signals supplied to the driver circuit 30 are controlled using the signal generator circuit 50.

The signal generator circuit **50** has a function of generating a signal used in the driver circuit **30**. Specifically, the signal generator circuit **50** has a function of generating a clock signal GCLK and a control signal GPWC that are used to generate a selection signal. Note that the control signal GPWC is used to control the pulse width of a selection signal. The signal generator circuit **50** is provided for each driver circuit **30**, and four signal generator circuits **50** (**50**(**1**, **1**) to (**2**, **2**)) are provided in FIG. **1**. When the clock signal GCLK and the control signal GPWC are supplied from the signal generator circuit **50** to the driver circuit **30**, the driver circuit **30** generates a selection signal and supplies it to the wiring GL.

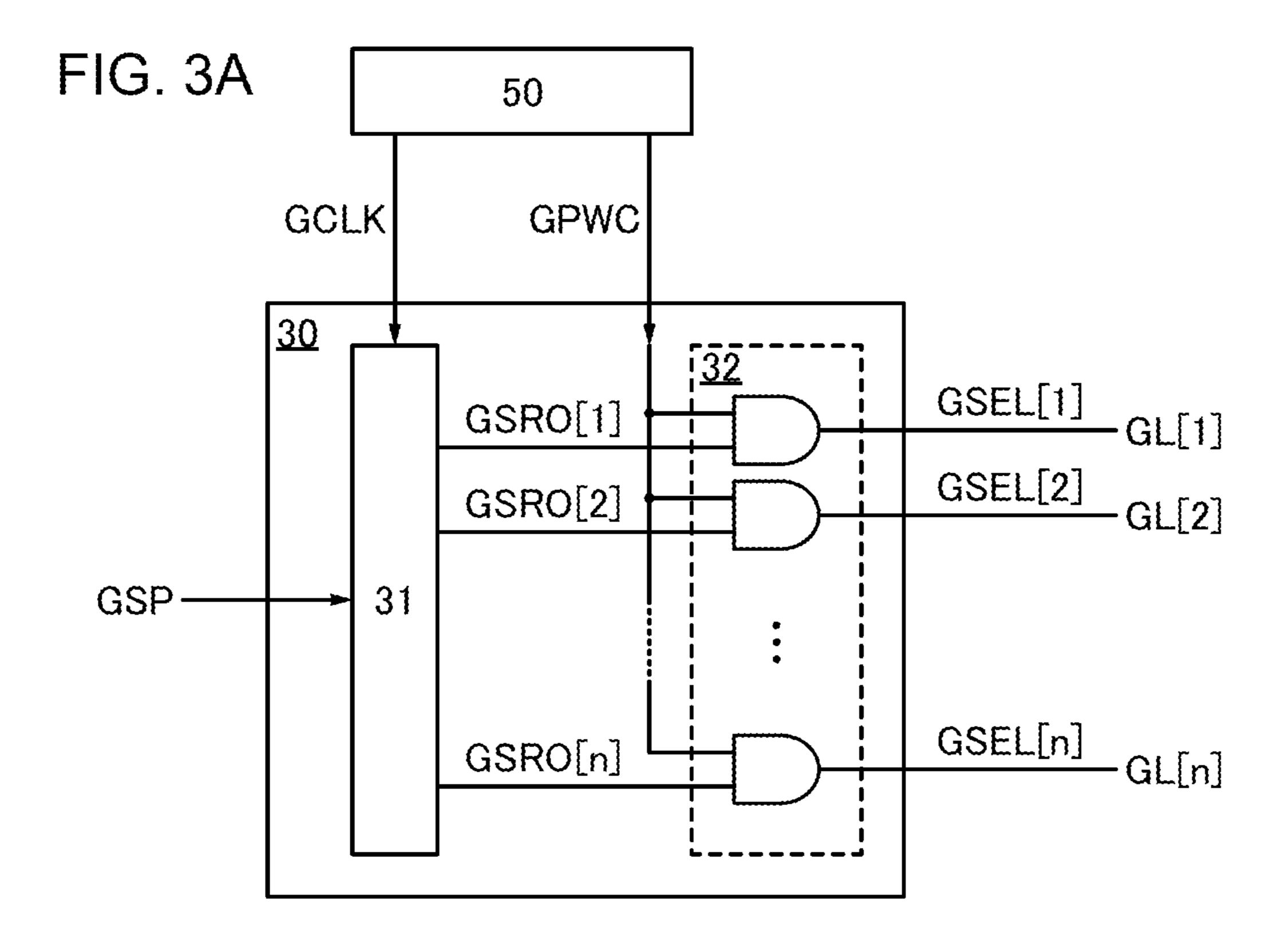

FIG. 3(A) illustrates a structure example of the driver circuit 30 supplied with the clock signal GCLK and the control signal GPWC from the signal generator circuit 50. The driver circuit 30 includes a shift register 31 and a control circuit 32 that is composed of a plurality of AND circuits.

The shift register 31 has a function of generating signals GSRO[1] to [n] by using a start pulse GSP input from the outside and the clock signal GCLK. The number of stages of the register 31 is n, and the signals GSRO[1] to [n] correspond to output signals of the respective stages of the shift register 31.

The control circuit 32 has a function of controlling the pulse width of the signal GSRO. The control circuit 32 includes n AND circuits to which the signals GSRO[1] to [n] are input. The signal GSRO and the control signal GPWC are input to the AND circuit, and the logical product thereof is output to the wiring GL as the signal GSEL (see FIG. 3(B)).

The signal generator circuit **50** has a function of controlling the cycle and pulse width of the clock signal GCLK and the cycle and pulse width of the control signal GPWC. Thus, the waveforms of the signal GSRO and the control signal GPWC can be controlled, and the pulse width of the signal GSEL can be controlled.

<Operation Example of Semiconductor Device>

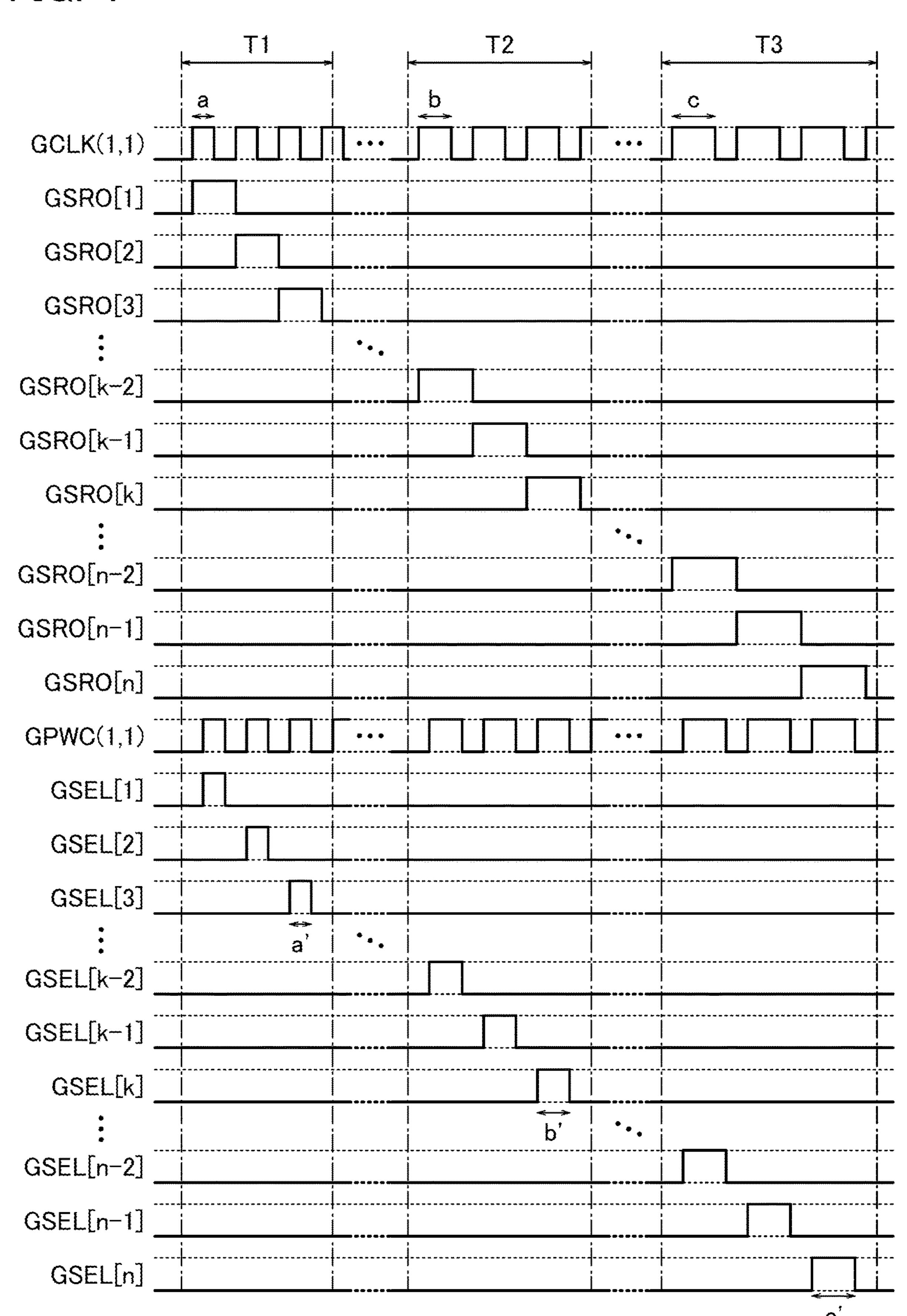

Next, an operation example of the semiconductor device 10 in which the pulse width of a selection signal is changed in accordance with the distance between the pixel 22 and the driver circuit 40 is described. FIG. 4 is a timing chart showing an operation example of the semiconductor device 10. Here, the case where the region 21(1, 1) in FIG. 1 is supplied with three types of signals GSEL from the driver circuit 30(1, 1) is described as an example; the other regions

21 can be operated in a similar manner. Note that k in FIG. 4 is an integer of 6 to n-3, and n here is an integer of 9 or more.

First, in a period T1, selection signals supplied to the pixels 22 provided in a region nearest to the driver circuit 40 5 (here, the pixels 22 in the first to third rows) are generated. First, a clock signal GCLK(1, 1) with a pulse width a and a control signal GPWC(1, 1) generated in accordance with the cycle and pulse width of the clock signal GCLK(1, 1) are output from the signal generator circuit 50 to the driver 10 circuit 30(1, 1). When the clock signal GCLK(1, 1) is input to the shift register 31, the shift register 31 outputs signals GSRO[1] to [3] to the control circuit 32. Then, the control circuit 32 generates signals GSEL[1] to [3] on the basis of the control signal GPWC(1, 1) and the signals GSRO[1] to 15 [3] and sequentially outputs them to the wirings GL<sub>1</sub>[1] to [3]. The pulse width of the signal GSEL generated in the period T1 is represented by a'.

Next, in a period T2, selection signals supplied to the pixels 22 provided in a region further from the driver circuit 20 40 than the pixels 22 in the first to third rows (here, the pixels 22 in the (k-2)th to k-th rows) are generated. First, the pulse width of the clock signal GCLK(1, 1) supplied from the signal generator circuit 50 to the driver circuit 30(1, 1) is changed to b (>a), and the cycle and pulse width of the 25 control signal GPWC(1, 1) are changed accordingly. Then, by the operation similar to that in the period T1, signals GSEL[k-2] to [k] are generated on the basis of the changed clock signal GCLK(1, 1) and control signal GPWC(1, 1) and sequentially output to the wirings  $GL_1[k-2]$  to [k]. The pulse 30 width of the signal GSEL generated in the period T2 is represented by b' (>a').

Note that a period during which the selection signal GSEL is output in the period T2 is longer than that in the period T1. Thus, the period T2 becomes longer than the period T1.

Next, in a period T3, selection signals supplied to the pixels 22 provided in a region farthest from the driver circuit 40 (here, the pixels 22 in the (n-2)th to n-th rows) are generated. First, the pulse width of the clock signal GCLK (1, 1) supplied from the signal generator circuit 50 to the 40 driver circuit 30(1, 1) is changed to c > b, and the cycle and pulse width of the control signal GPWC(1, 1) are changed accordingly. Then, by the operation similar to that in the period T1, signals GSEL[n-2] to [n] are generated on the basis of the changed clock signal GCLK(1, 1) and control 45 signal GPWC(1, 1) and sequentially output to the wirings  $GL_1[n-2]$  to [n]. The pulse width of the signal GSEL in the period T3 is represented by c' > b'.

Note that a period during which the selection signal GSEL is output in the period T3 is longer than that in the period T2. 50 Thus, the period T3 becomes longer than the period T2.

As described above, by controlling the waveforms of the control signal GPWC and the signal GCLK by the signal generator circuit **50**, the signal GSEL with a pulse width corresponding to the distance from the driver circuit **40** to 55 the pixel **22** can be supplied from the driver circuit **30**. Note that although an operation example in which the pulse width of the selection signal is changed for every certain number of wirings GL is described here, the pulse width of the selection signal can alternatively be changed for every 60 wiring GL. Alternatively, the pulse width can be widened only for the signal GSEL supplied to the pixels **22** belonging to a certain row that is distant from the driver circuit **40**. <Structure Example of Signal Generator Circuit>

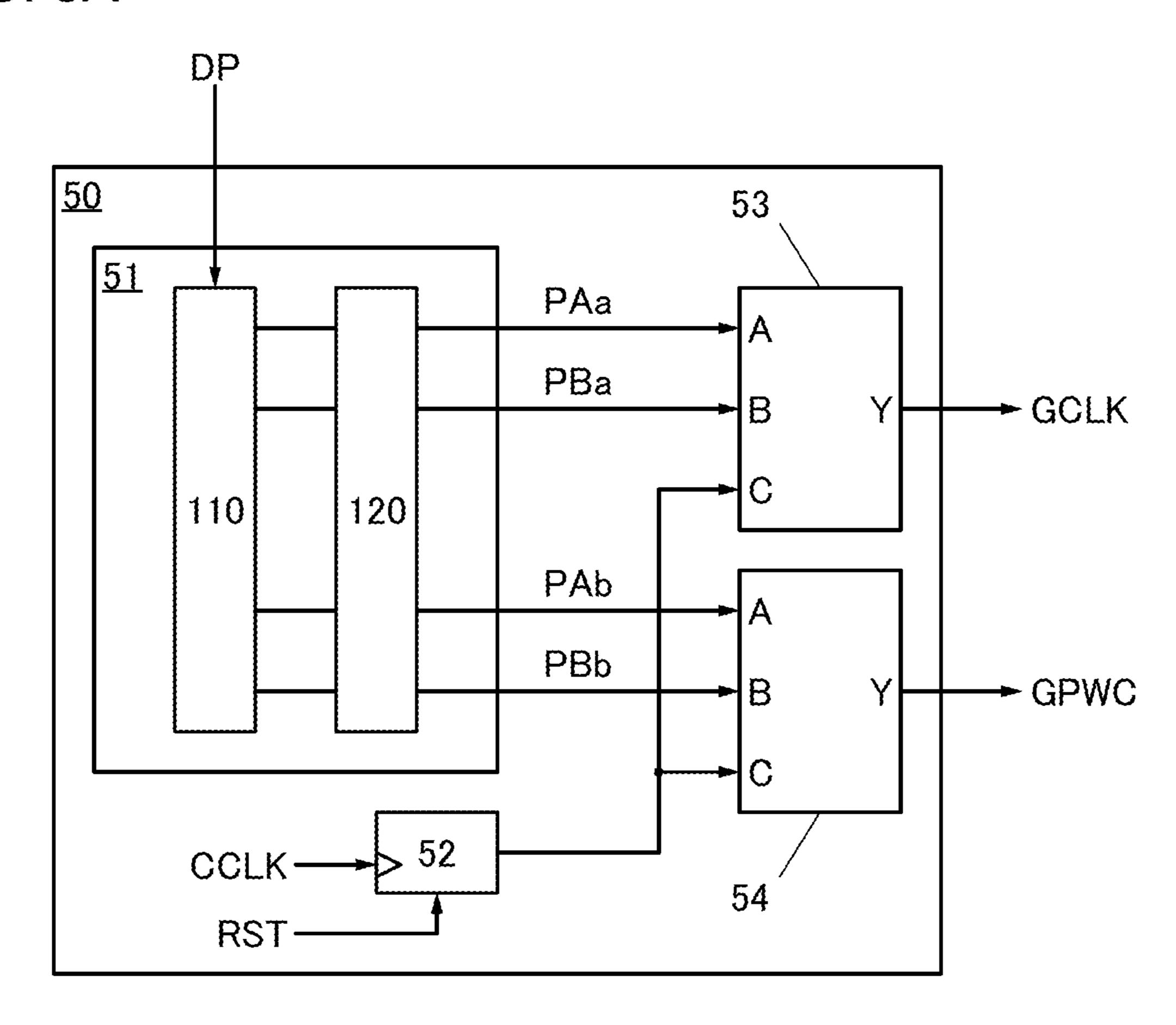

Next, a structure example of the signal generator circuit 65 50 is described. FIG. 5(A) illustrates the signal generator circuit 50 having a function of controlling the waveforms of

12

the clock signal GCLK and the control signal GPWC. The signal generator circuit 50 includes a register 51, a counter 52, a comparator circuit 53, and a comparator circuit 54.

The register 51 has a function of storing and collectively outputting data DP including parameters for determining the waveform of the control signal GPWC or the signal GCLK. The register 51 includes a scan chain register portion 110 and a register portion 120. The data DP is sequentially input to and stored in the scan chain register portion 110. Then, the data DP stored in the scan chain register portion 110 is collectively transferred to the register portion 120 and output to the comparator circuit 53 and the comparator circuit 54 at the same time.

The data DP includes a variety of parameters used in the comparator circuit **53** and the comparator circuit **54**. Specifically, the data DP includes parameters PAa and PBa determining the waveform of the signal GCLK, parameters PAb and PBb determining the waveform of the control signal GPWC, and the like.

The counter 52 has a function of counting in synchronization with a clock signal CCLK. A count value of the counter 52 is output to the comparator circuit 53 and the comparator circuit 54. When a reset signal RST is input to the counter 52, the count value of the counter 52 is reset.

The comparator circuit **53** has a function of generating the signal GCLK by using the parameters input from the register **51** and the count value of the counter. The parameter PAa is input to an input terminal A of the comparator circuit **53**, the parameter PBa is input to an input terminal B, and the count value of the counter **52** is input to an input terminal C. The comparator circuit **53** has a function of determining the waveform of the signal GCLK by using the parameters PAa and PBa as parameters determining the rise timing and fall timing, respectively, of the signal GCLK. The signal GCLK generated by the comparator circuit **53** is output from an output terminal Y to the driver circuit **30**.

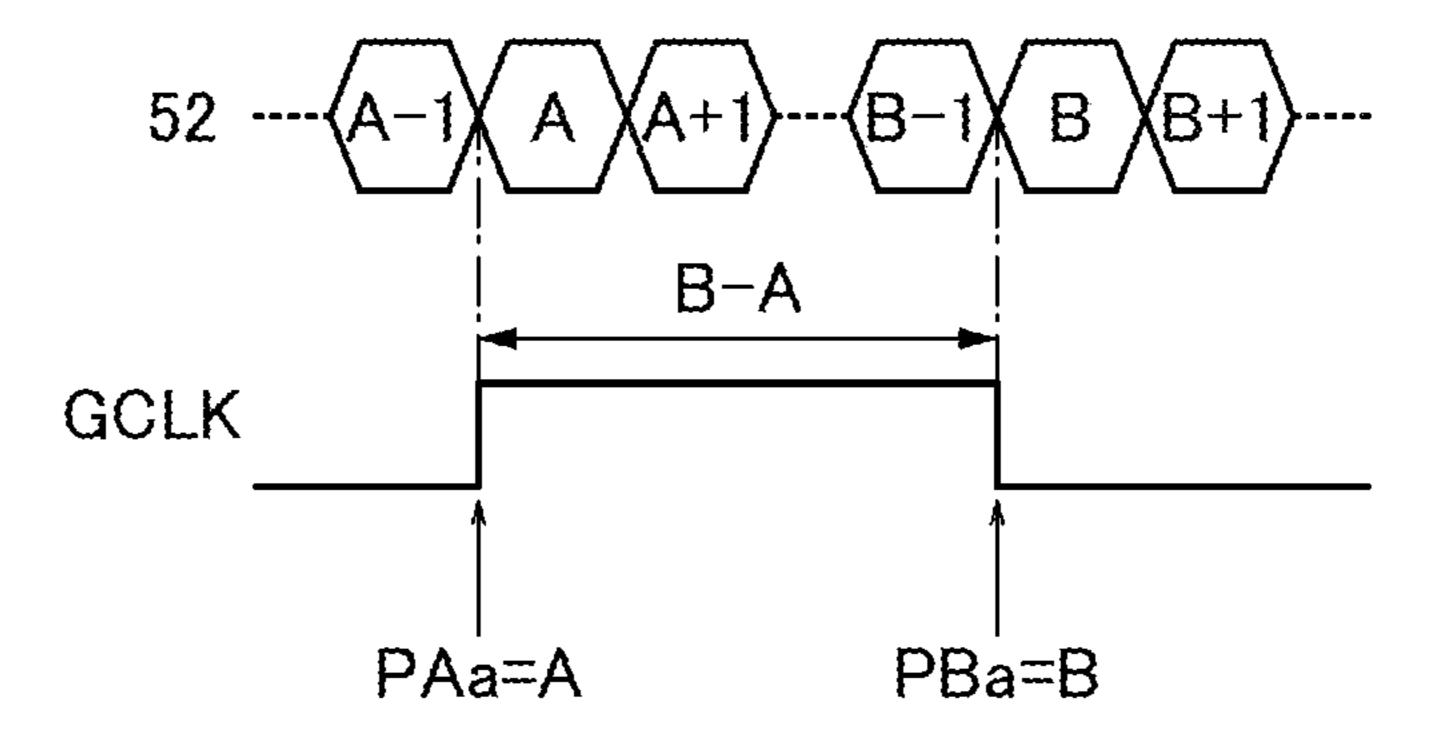

For example, as shown in FIG. 5(B), the comparator circuit 53 can be configured to output a high-level signal when the count value of the counter 52 reaches the value of the parameter PAa (here, A) and output a low-level signal when the count value of the counter 52 reaches the value of the parameter PBa (here, B). Thus, the waveform of the signal GCLK can be controlled. Note that the pulse width of the signal GCLK at this time becomes a value corresponding to (B-A). More specifically, it becomes (B-A) times the cycle of the clock signal CCLK (the count up cycle of the counter).

The comparator circuit **54** has a function of generating the control signal GPWC by using the parameters input from the register **51** and the count value of the counter. The parameter PAb is input to an input terminal A of the comparator circuit **54**, the parameter PBb is input to an input terminal B, and the count value of the counter **52** is input to an input terminal C. The comparator circuit **54** has a function of determining the waveform of the control signal GPWC by using the parameters PAb and PBb as parameters determining the rise timing and fall timing, respectively, of the control signal GPWC. The control signal GPWC generated by the comparator circuit **54** is output from an output terminal Y to the driver circuit **30**. Specific operation of the comparator circuit **54** is similar to that of the comparator circuit **53**.

The parameters are collectively output from the register 51 to the comparator circuit 53 and the comparator circuit 54 at the same time. Thus, the timings of updating the signal GCLK and the control signal GPWC can be synchronized, and the change in pulse width of a selection signal in the driver circuit 30 can be accurately performed.

In addition, by controlling the timing at which the reset signal RST is input to the counter 52, the cycles of the signal GCLK and the control signal GPWC can be controlled. The timing at which the reset signal RST is input may be determined by a parameter stored in the register 51. [Structure Example of Register]

In one embodiment of the present invention, the pulse width of a selection signal output from the driver circuit 30 is changed in a period during which the wirings GL are sequentially scanned. Thus, it is preferred that parameters 10 output from the register 51 be updated at high speed. High-speed parameter update is required particularly when the number of pulse width switching is large, for example, when the pulse width of a selection signal is changed for every wiring GL.

Here, for high-speed parameter update, a structure where a plurality of scan chain register portions 110 are provided and a set of parameters corresponding a selection signal with a predetermined pulse width is stored in each of the scan chain portions 110 is effective. In this case, the output of 20 parameters can be switched quickly by switching between the scan chain register portions 110 that will output parameters to the register portion 120. A structure example of the register 51 having such a structure will be described below.

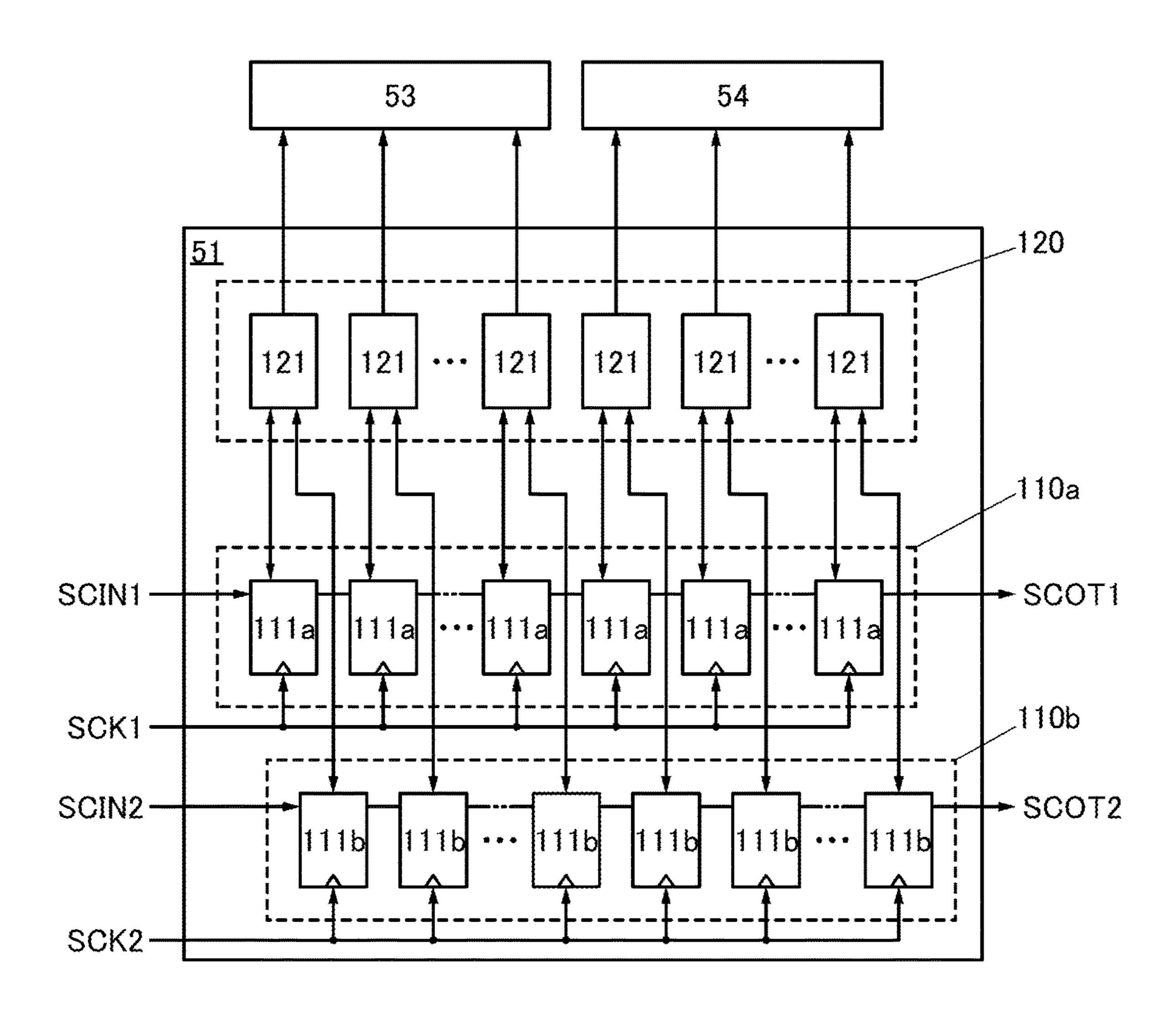

FIG. 6 illustrates a structure example of the register 51. 25 The register 51 includes a plurality of scan chain register portions 110 and the register portion 120. Although a structure where two scan chain register portions 110 (110a and 110b) are provided is shown here, the number of scan chain register portions 110 can be set freely. Each of the scan chain 30 register portions 110a and 110b can store a set of parameters for generating a selection signal with a predetermined pulse width.

The register portion 120 includes a plurality of registers **121**. The scan chain register portion 110a includes a plural- 35 ity of registers 111a and nodes SCIN1 and SCOT1. The scan chain register portion 110b includes a plurality of registers 111b and nodes SCIN2 and SCOT2.

The registers 111a and 111b are nonvolatile registers, which do not lose data even in a state where the power is 40 shut off. The registers 111a and 111b are provided with a retention circuit using an OS transistor so that the registers 111a and 111b become nonvolatile.

A metal oxide has a larger energy gap than a semiconductor such as silicon and can have a lower minority carrier 45 density. Thus, a current flowing between a source and a drain of an OS transistor when the OS transistor is in an off state (hereinafter also referred to as an off-state current) is extremely low. Accordingly, when OS transistors are used in the registers 111a and 111b, data can be retained for a long 50 period compared with the case of using transistors containing silicon in their channel regions (hereinafter also referred to as Si transistors) or the like. This enables data retention even in a period when power supply to the registers 111a and 111b is stopped.

Meanwhile, the register 121 is a volatile register. There is no particular limitation on the circuit structure of the register 121; the register 121 can be any circuit capable of storing data and can be composed of a latch circuit, a flip-flop the comparator circuit 53 and the comparator circuit 54 are controlled with parameters output from the register portion **120**.

To update data stored in the register **51**, first, data in the scan chain register portions 110a and 110b is changed. To 65 change the data in the scan chain register portion 110a, data is input from the node SCIN1 while a scan clock signal

14

SCK1 is toggled. By the data input from the node SCIN1, data in each register 111a is updated in accordance with the scan clock signal SCK1. The last-stage register 111a outputs data from the node SCOT1. Similarly, to change the data in the scan chain register portion 110b, data is input from the node SCIN2 while a scan clock signal SCK2 is toggled. By the data input from the node SCIN2, data in each register 111b is updated in accordance with the scan clock signal SCK2. The last-stage register 111b outputs data from the node SCOT2.

To store parameters for generating a selection signal with a predetermined pulse width in the scan chain register portions 110a and 110b, the data DP in FIG. 5 is input from the node SCIN1 and the node SCIN2.

After the data of each register 111a in the scan chain register portion 110a is rewritten, the data of the registers 111a is collectively loaded into the registers 121 in the register portion 120. Alternatively, after the data of each register 111b in the scan chain register portion 110b is rewritten, the data of the registers 111b is collectively loaded into the registers 121 in the register portion 120. Thus, the comparator circuit 53 and the comparator circuit 54 can generate a signal by using parameters that are collectively updated. Since the simultaneity of data update is maintained, stable operation of the signal generator circuit 50 can be achieved. Moreover, including the scan chain register portions 110a and 110b and the register portion 120 enables data in the scan chain register portions 110a and 110b to be updated even while the comparator circuit 53 and the comparator circuit **54** are in operation.

Note that in a period during which the register **51** is not accessed, power supply to the register 51 can be temporarily stopped (power gating). To implement power gating of the register 51, the power is shut off after data is stored (saved) in the retention circuit of the registers 111a and 111b. After the power supply is resumed, the data in the register 111a or the register 111b is restored (loaded) to the register 121 and normal operation is restarted. Note that in the case where the data stored in the register 111a or the register 111b and the data stored in the register 121 do not match, it is preferable to save the data of the register 121 in the register 111a or the register 111b and then store the data again in the retention circuit of the registers 111a and 111b. An example of the case where the data do not match includes the case where data in the scan chain register portions 110a and 110b has been changed.

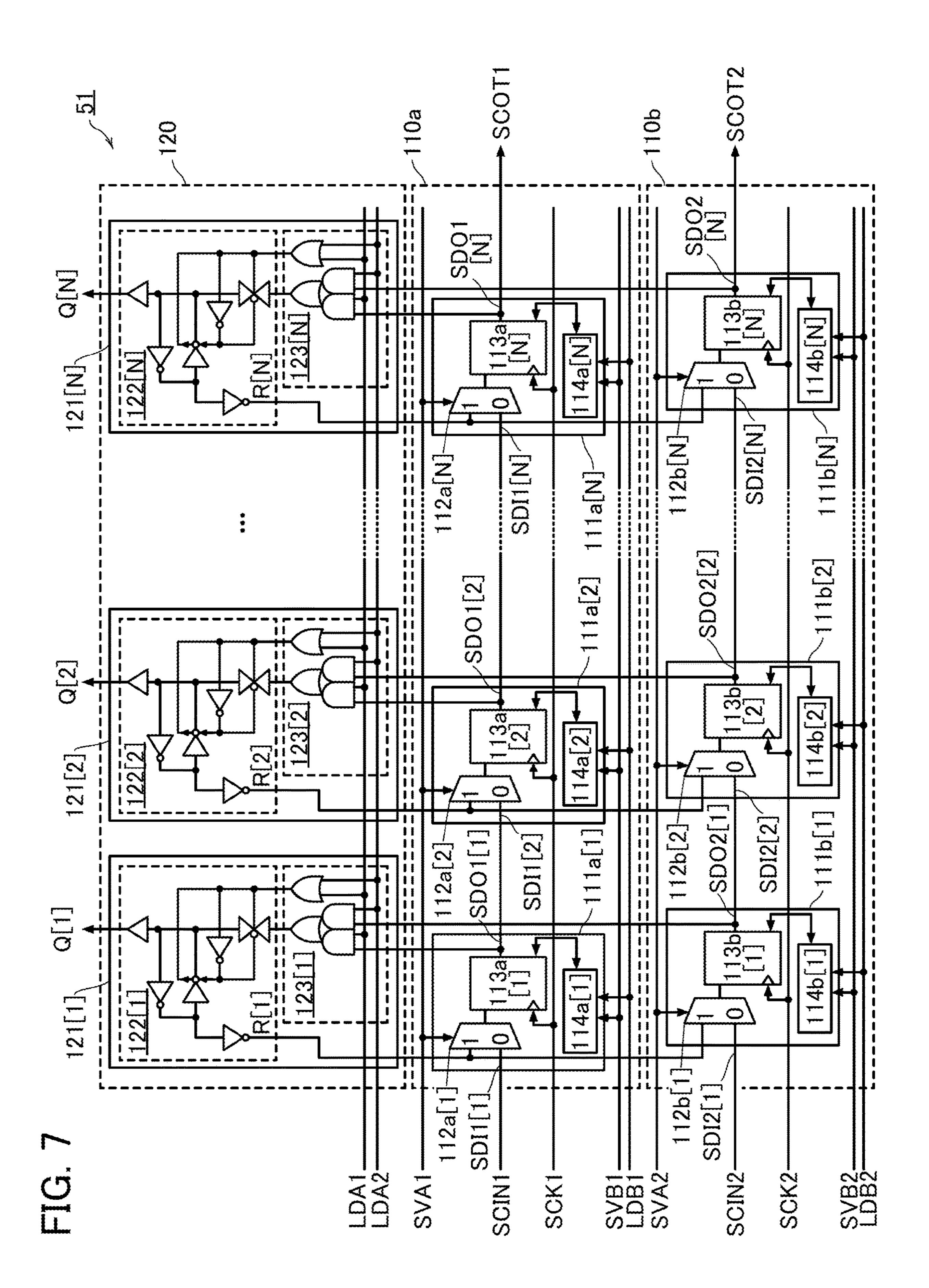

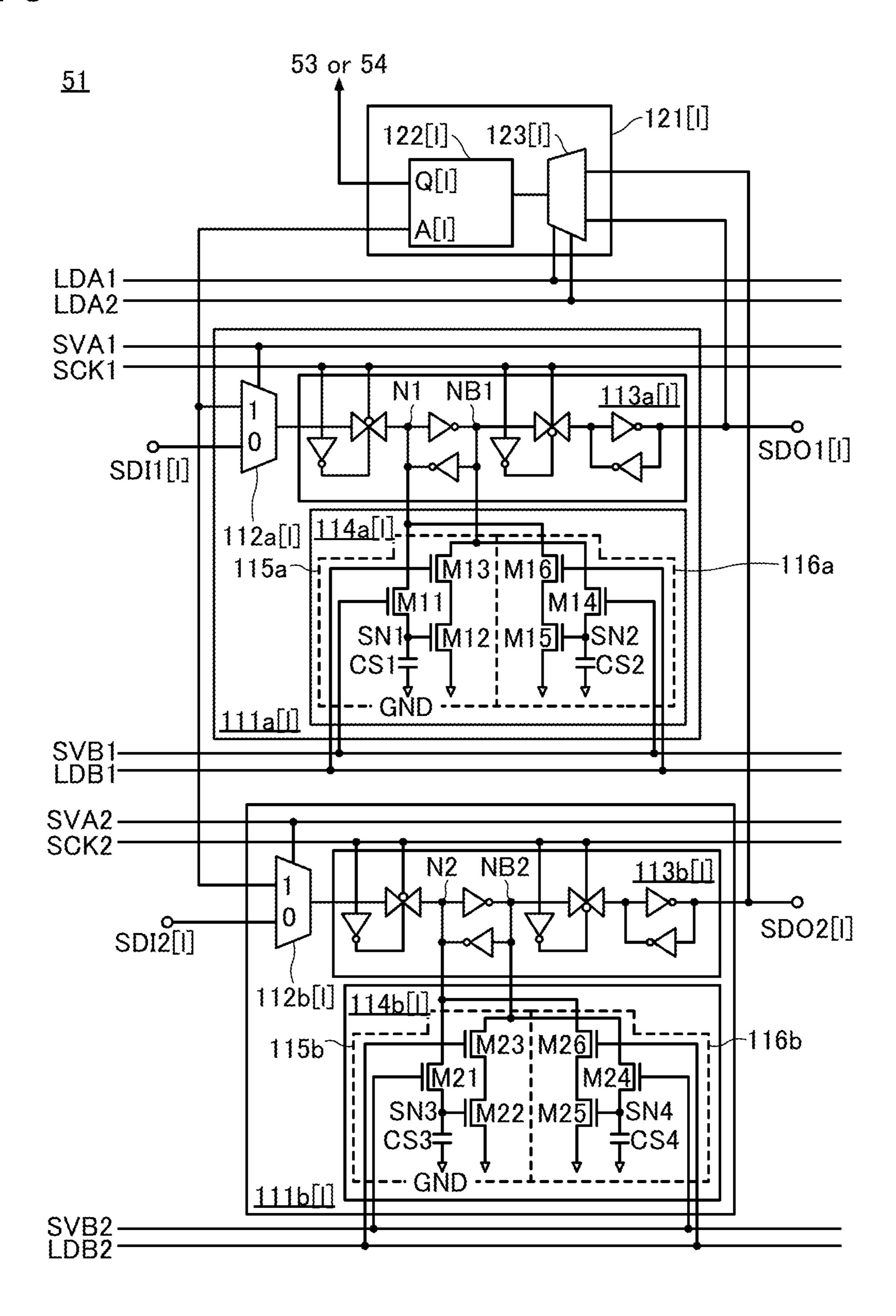

A circuit structure example of the register **51** is described with reference to FIG. 7 and FIG. 8.

The register portion 120 includes N registers 121 (N is an integer of 2 or more). Signals LDA1 and LDA2 are input to the register portion 120. The signals LDA1 and LDA2 are signals for controlling data loading.

The scan chain register portions 110a and 110b include 55 respective N registers 111a and 111b. The scan clock signal SCK1 and signals SVA1, SVB1, and LDB1 are input to the scan chain register portion 110a. The scan clock signal SCK2 and signals SVA2, SVB2, and LDB2 are input to the scan chain register portion 110b. The signals LDB1 and circuit, or the like. The waveforms of signals generated by 60 LDB2 are signals for controlling data loading. The signals SVA1, SVA2, SVB1, and SVB2 are signals for controlling data saving.

The register **121** includes a latch circuit **122** and a MUX (multiplexer) 123. The register 111a includes a selector 112a, a flip-flop circuit 113a, a retention circuit 114a, and nodes SDI1 and SDO1. The register 111b includes a selector 112b, a flip-flop circuit 113b, a retention circuit 114b, and

nodes SDI2 and SDO2. The nodes SDI1 and SDI2 are nodes to which data is input. The nodes SDO1 and SDO2 are nodes from which data is output.

The register 121 is a volatile register. Nodes Q and R are output nodes of the latch circuit 122 and output data with the same logic. The node Q is connected to the comparator circuit 53 or the comparator circuit 54. The node R is connected to the registers 111a and 111b. There is no particular limitation on the latch circuit 122, and another circuit such as a flip-flop circuit may alternatively be provided.

The MUX 123 has a function of selecting data to be input to the latch circuit 122. The signals LDA1 and LDA2 are control signals for the MUX 123. In the example of FIG. 7, data in the latch circuit 122 is updated by data of the node SDO1 when the signal LDA1 is at high level and LDA2 is at low level. On the other hand, data in the latch circuit 122 is updated by data of the node SDO2 when the signal LDA1 is at low level and LDA2 is at high level.

The registers 111a and 111b are nonvolatile registers. A more specific circuit structure example of the registers 111a and 111b is described with reference to FIG. 8.

In the register 111a, the selector 112a and the flip-flop circuit 113a constitute a scan flip-flop circuit. When the scan 25 chain register portion 110a operates as a shift register, the register 111a takes data from the node SDI1 and outputs the data from the node SDO1. The data of the node SDO1 is input to the node SDI1 in the next-stage register 111a.

The signal SVA1 is a control signal for the selector 112a. When the signal SVA1 is at high level, the selector 112a establishes electrical continuity between an input node of the flip-flop circuit 113a and the node R of the register 121. When the signal SVA1 is at low level, the selector 112a establishes electrical continuity between the input node of the flip-flop circuit 113a and the node SDI1.

The flip-flop circuit 113a is not limited to the circuit structure in FIG. 8, and a variety of flip-flop circuits can be employed. The retention circuit 114a is connected to nodes 40 N1 and NB1 of the flip-flop circuit 113a. The signals LDB1 and SVB1 are control signals for the retention circuit 114a.

The retention circuit 114a is a circuit for storing data retained in the flip-flop circuit 113a and includes two memory circuits 115a and 116a. Here, the memory circuits 45 115a and 116a are composed of a three-transistor gain cell. The memory circuit 115a includes transistors M11 to M13, a capacitor CS1, and a node SN1. The memory circuit 116a includes transistors M14 to M16, a capacitor CS2, and a node SN2. The nodes SN1 and SN2 are retention nodes of 50 the memory circuits 115a and 116a.

The memory circuit 115a has a function of backing up data of the node N1 and loading the backed-up data into the node NB1. The memory circuit 116a has a function of backing up data of the node NB1 and loading the backed-up 55 data into the node N1. In accordance with the signal SVB1, the memory circuit 115a writes data of the node N1 to the node SN1 and the memory circuit 116a writes data of the node NB1 to the node SN2. In accordance with the signal LDB1, the memory circuit 115a writes data of the node SN1 60 to the node NB1 and the memory circuit 116a writes data of the node SN2 to the node N1.

The transistors M11 and M14 are OS transistors; thus, the retention circuit 114a can retain data for a long time even in a state where the power is shut off. In the register 111a, the 65 transistors other than the transistors M11 and M14 may be Si transistors.

**16**

The circuit structure of the register 111b is similar to that of the register 111a; therefore, the description of the register 111a is referred to for the details of the register 111b.

In the register 111b, the selector 112b and the flip-flop circuit 113b constitute a scan flip-flop circuit. The selector 112b selects one of the node R and the node SDI2 in accordance with the signal SVA2, and establishes electrical continuity between the selected node and an input node of the flip-flop circuit 113b.

The retention circuit 114b is connected to nodes N2 and NB2 of the flip-flop circuit 113b. The retention circuit 114b includes memory circuits 115b and 116b. The memory circuit 115b includes transistors M21 to M23, a capacitor CS3, and a node SN3. The memory circuit 116b includes transistors M24 to M26, a capacitor CS4, and a node SN4. The memory circuit 115b stores data of the flip-flop circuit 113b in accordance with the signal SVB2, and loads the retained data into the flip-flop circuit 113b in accordance with the signal LDB2.

The transistors M21 and M24 are OS transistors; thus, the retention circuit 114b can retain data for a long time even in a state where the power is shut off. The transistor M21 and the transistor M24 may be a transistor having a back gate. The same applies to the transistors M11 and M14.

In the register 111b, the transistors other than the transistors M21 and M24 may be Si transistors.

Note that FIG. **8** shows an example where the retention circuit **114***b* backs up complementary data of the first-stage inverter loop in the flip-flop circuit **113***b*. The retention circuit **114***b* may be provided so as to back up complementary data of the subsequent-stage inverter loop in the flip-flop circuit **113***b*. The same applies to the register **111***a*. With the retention circuits **114***a* and **114***b* having such a structure, backed-up data can be loaded asynchronously, resulting in high-speed data loading. Thus, it is possible to shorten the time it takes during power gating to restore the register **51** to a normal operation state from a power-off state. [Operation Example of Register]

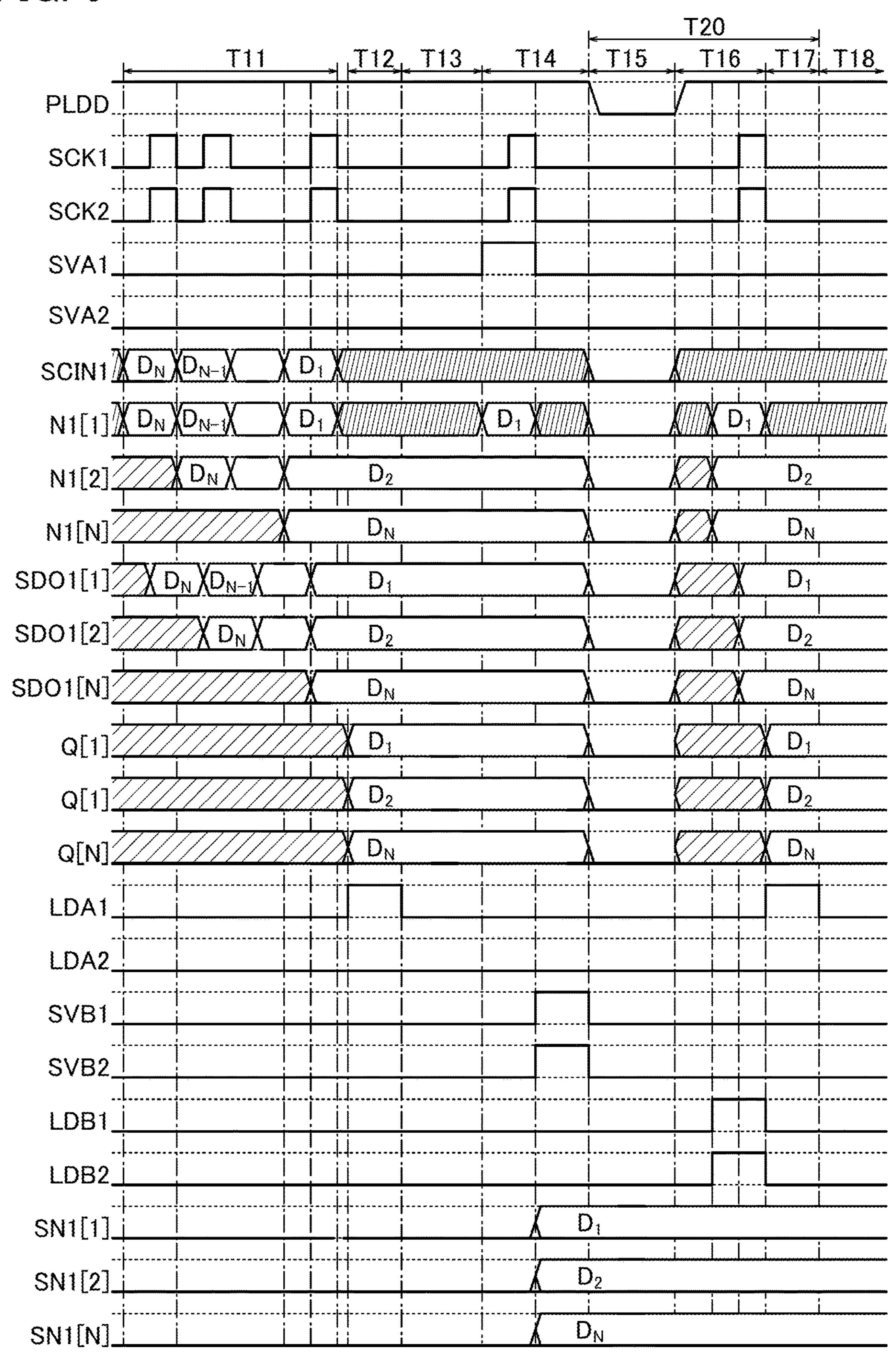

An operation example of the register **51** is described with reference to FIG. **9**. FIG. **9** is a timing chart showing an operation example of the register **51**. PLDD is a wiring that supplies a potential VDD to the register **51**. The potential VDD is a power supply potential. A hatched portion of a waveform for the node N1 and the like denotes an indeterminate value where the logic is not fixed at high level or low level.

In a period T11, the scan chain register portions 110a and 110b perform scan operation so that data is written to each of them. During this, the signals SVA1 and SVA2 are at low level, and the scan clock signals SCK1 and SCK2 are active. Thus, electrical continuity between the node SDI1 and the input node of the flip-flop circuit 113a is established by the selector 112a, and electrical continuity between the node SDI2 and the input node of the flip-flop circuit 113b is established by the selector 112b.

To write data to the N registers 111a in the scan chain register portion 110a, data of the node SCIN1 is updated in synchronization with the scan clock signal SCK1. In the register 111a[l] (I is an integer of 1 to N), data of the node SDO1[l] is updated in synchronization with the rising edge of the scan clock signal SCK1, and data of the node N1[l+1] is updated by the data of the node SDO1[l] in synchronization with the falling edge of the scan clock signal SCK1. As the scan clock signal SCK1 is repeatedly toggled, data of the node SCIN1 is shifted within the registers 111a. Data stored in each register 111a can be sequentially obtained from the node SCOT1.

Shift operation of the scan chain register portion 110b is performed in a similar manner to that of the scan chain register portion 110a. Data of the node SDO2 is updated in synchronization with the rising edge of the scan clock signal SCK2.

In a period T12, operation of updating data in the register portion 120 is performed. The signal LDA1 changes to high level, whereby electrical continuity between the node SDO1 [l] and an input node of the latch circuit 122[1] is established by the MUX 123[l]. The latch circuit 122[l] stores data Dk 10 that is retained in the register 111a[l]. Data D1 is output from the nodes Q[1] and A[1]. In other words, by setting the signal LDA1 to high level, data D1 to DN retained in the scan chain register portion 110a are collectively loaded into the register portion 120. Accordingly, parameters and the like that the 15 however, data in the retention circuits 114a and 114b is not comparator circuit 53 or the comparator circuit 54 uses can be collectively changed.

To update data in the register portion 120 by data retained in the scan chain register portion 110b, the signal LDA1 is kept at low level and the signal LDA2 is set to high level. 20

Note that in the period T12, electrical continuity is established between the node N1[1] and the node SCIN1 when the scan clock signal SCK1 and the signal SVA1 become low level; hence, the potential of the node N1[1] changes in accordance with the potential of the node SCIN1. 25 Similarly, when the scan clock signal SCK2 and the signal SVA2 become low level, the potential of the node N1[2] changes in accordance with the potential of the node SCIN2.

In a period T13, the register 51 performs normal operation. The data D1 to DN, which are written in the period T12, 30 are output from the nodes Q[1] to Q[N]. During this, the scan chain register portion 110a may perform scan operation to change data in the scan chain register portion 110a. Data in the register portion 120 may be rewritten by setting the signal LDA1 to high level after data in the scan chain 35 recovery operation is completed. register portion 110a is changed. The same applies to the scan chain register portion 110b.

In a period T20, power gating operation of the register 51 is performed. The power gating operation is broadly divided into backup operation for the register 51, operation of 40 turning off power, and recovery operation for the register 51.

In a period T14, the backup operation for the register 51 is performed. First, the signal SVA1 is set to high level, and then the scan clock signal SCK1 is set to high level, whereby the data D1 to DN stored in the register portion 120 are 45 written to the flip-flop circuit 113a in the scan chain register portion 110a. In the example of FIG. 9, the scan clock signal SCK2 is set to high level together with the scan clock signal SCK1 to simplify signal control; however, the scan clock signal SCK2 may be kept at low level.

When the signal SVA1 becomes high level, the selector 112a establishes electrical continuity between the node A of the latch circuit 122 and the input node of the flip-flop circuit 113a. Since the scan clock signal SCK1 is at low level, data of the node A is written to the node N1 of the flip-flop circuit 55 113a. When the scan clock signal SCK1 changes to high level, electrical continuity between the node N1 and the node A is broken, and electrical continuity between the node N1[1] and the node SCIN1 is broken.

Note that in the case where data stored in the register 60 portion 120 is data loaded from the scan chain register portion 110b, the data in the register portion 120 is backed up in the scan chain register portion 110b. In this case, the signal SVA2 is set to high level, and then the scan clock signal SCK2 is set to high level.

Next, backup operation for the scan chain register portions 110a and 110b is performed. During this, the signals **18**

SVB1 and SVB2 are set to high level. When the signal SVB1 becomes high level, data of the nodes N1 and NB1 in the flip-flop circuit 113a is written to the nodes SN1 and SN2 in the retention circuit 114a. When the signal SVB2 becomes high level, data of the nodes N2 and NB2 in the flip-flop circuit 113b is written to the nodes SN3 and SN4 in the retention circuit 114b.

By setting the signals SVB1 and SVB2 to low level, the backup operation for the register **51** is completed.

In a period T15, the operation of turning off power is performed. Supply of the potential VDD to the wiring PLDD is stopped. The wiring PLDD is gradually discharged. Since the potential of the wiring PLDD decreases, data in the latch circuit 122 and the flip-flop circuits 113a and 113b is lost; lost.

In a period T16, recovery operation for the scan chain register portions 110a and 110b is performed. First, supply of the potential VDD to the wiring PLDD is started. The potential of the wiring PLDD increases and then becomes the potential VDD.

Next, the signals LDB1 and LDB2 are set to high level, and one clock of each of the scan clock signals SCK1 and SCK2 is input. When the signal LDB1 becomes high level, the retention circuit 114a writes data of the nodes SN1 and SN2 to the nodes N1 and NB1 in the flip-flop circuit 113a. The data of the node N1 is input to the node SDO1 in synchronization with the rising edge of the scan clock signal SCK1. When the signal LDB2 becomes high level, the retention circuit 114b writes data of the nodes SN3 and SN4 to the nodes N2 and NB2 in the flip-flop circuit 113b. The data of the node N2 is input to the node SDO2 in synchronization with the rising edge of the scan clock signal SCK2.

By setting the signals LDB1 and LDB2 to low level, the

In a period T17, recovery operation for the register portion 120 is performed. The signal LDA1 is set to high level to restore the register portion 120 to the state in the period T13. The recovery operation in the period T17 is the same as the operation of updating data in the register portion 120 in the period T13; the data D1 to DN retained in the scan chain register portion 110a are collectively loaded into the register portion 120. By setting the signal LDA1 to low level, the recovery operation is completed.

In a period T18, the register 51 performs normal operation and outputs the data D1 to DN, which are written in the period T17, from the nodes Q[1] to Q[N].

With the above-described operation, collective change of parameters used in the comparator circuit 53 or the com-50 parator circuit **54** and power gating of the register **51** can be performed.

<Structure Example of Pixel>

Next, a specific structure example of the pixels 22 in FIG. 1 is described.

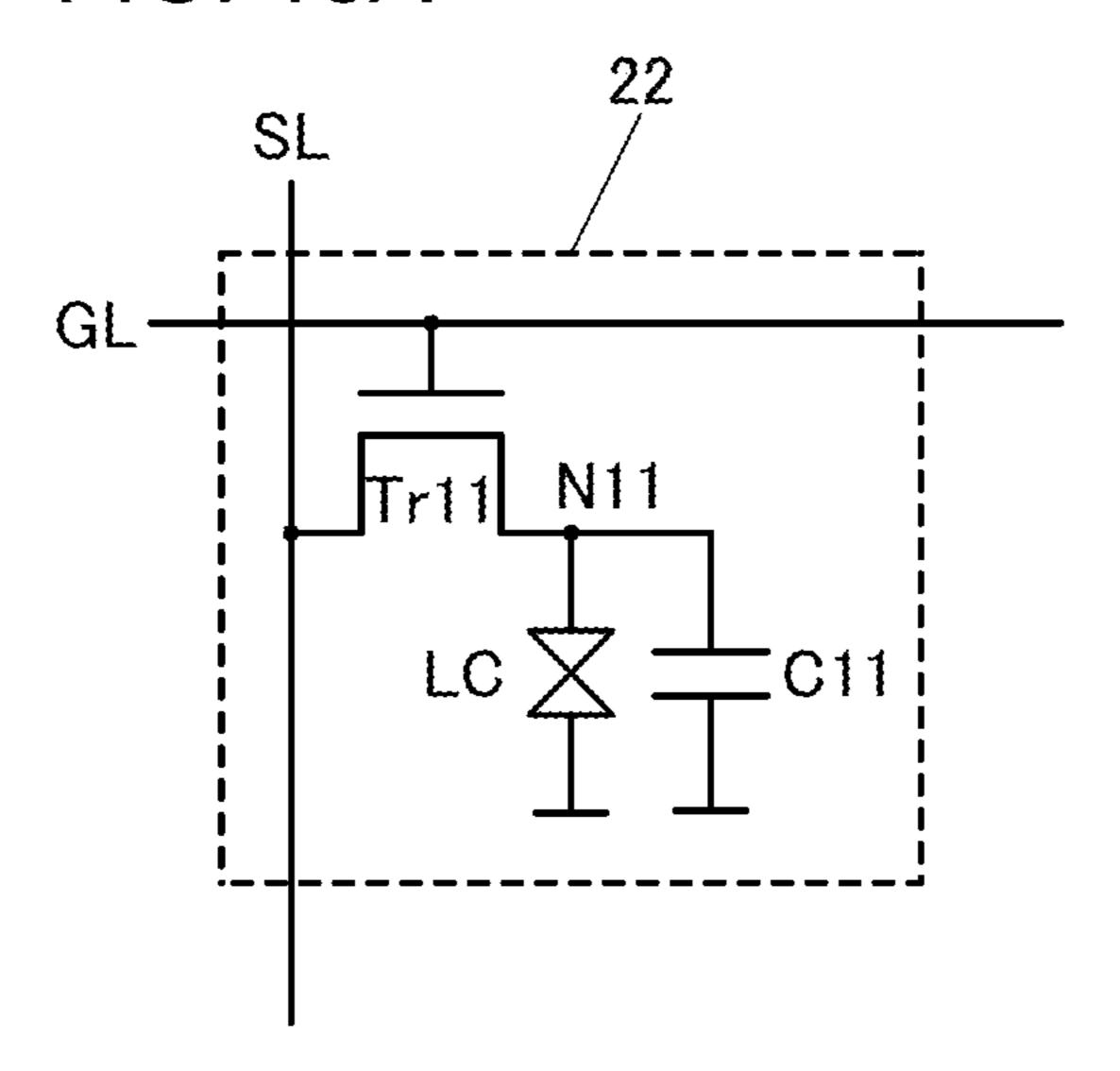

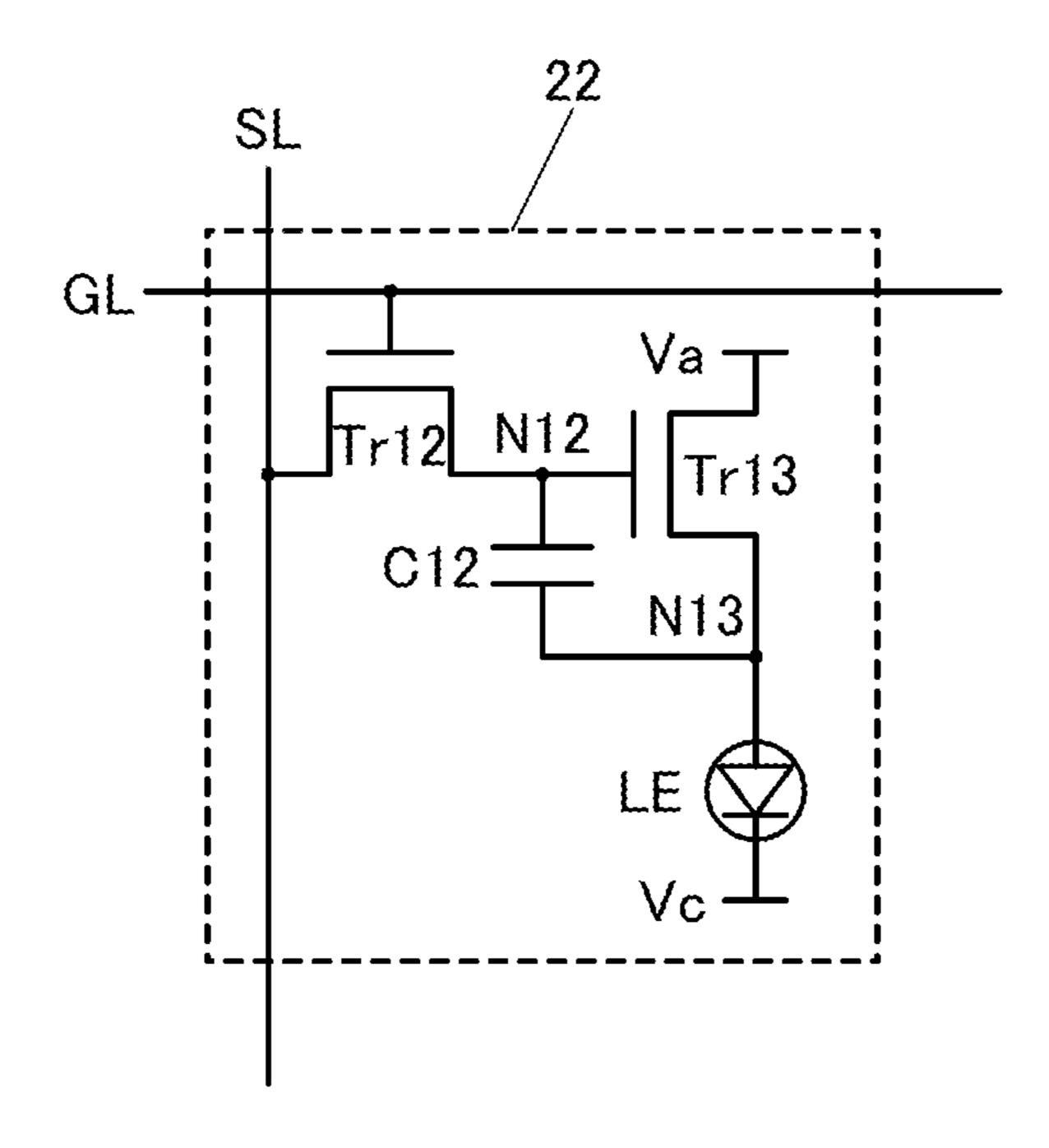

FIG. 10(A) illustrates a structure example of a pixel using a liquid crystal element.

The pixel 22 shown in FIG. 10(A) includes a transistor Tr11, a capacitor C11, and a liquid crystal element LC. Note that although the transistor Tr11 is of n-channel type here, the polarity of the transistor can be changed as appropriate.

A gate of the transistor Tr11 is connected to the wiring GL, one of a source and a drain is connected to one electrode of the liquid crystal element LC and one electrode of the capacitor C11, and the other of the source and the drain is 65 connected to the wiring SL. The other electrode of the liquid crystal element LC and the other electrode of the capacitor C11 are each connected to a wiring to which a predetermined

potential is supplied. A node that is connected to the one of the source and the drain of the transistor Tr11, the one electrode of the liquid crystal element LC, and the one electrode of the capacitor C11 is referred to as a node N11.

Note that in this specification and the like, a source of a transistor means a source region that is part of a semiconductor layer functioning as a channel region, a source electrode connected to the semiconductor layer, or the like. Similarly, a drain of a transistor means a drain region that is part of the semiconductor layer, a drain electrode connected 10 to the semiconductor layer, or the like. Moreover, a gate means a gate electrode or the like.

The terms "source" and "drain" of a transistor interchange with each other according to the conductivity type of the transistor and the levels of potentials applied to the termi15 nals. In general, in an n-channel transistor, a terminal to which a low potential is applied is called a source, and a terminal to which a high potential is applied is called a drain.

In addition, in a p-channel transistor, a terminal to which a low potential is applied is called a drain, and a terminal to which a high potential is applied is called a source. In this specification, the connection relation of a transistor is sometimes described assuming for convenience that its source and drain are fixed; actually, the names of the source and the drain interchange with each other according to the relation 25 of the above-described potentials.

The potential of the other electrode of the liquid crystal element LC may be a common potential among the plurality of pixels 22 or may be the same potential as the other electrode of the capacitor C11. Alternatively, the potential of 30 the other electrode of the liquid crystal element LC may differ between the pixels 22. Furthermore, the capacitor C11 has a function of a storage capacitor for retaining the potential of the node N11.