#### US010944694B2

# (12) United States Patent

# Tietz et al.

# (10) Patent No.: US 10,944,694 B2

# (45) Date of Patent: Mar. 9, 2021

#### (54) PREDICTIVE ARBITRATION CIRCUIT

(71) Applicant: HEWLETT PACKARD

ENTERPRISE DEVELOPMENT LP,

Houston, TX (US)

(72) Inventors: Joseph G. Tietz, Tinton Falls, NJ (US);

Eric C. Fromm, Eau Claire, WI (US)

(73) Assignee: Hewlett Packard Enterprise

Development LP, Houston, TX (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/370,485

(22) Filed: **Dec. 6, 2016**

### (65) Prior Publication Data

US 2018/0159799 A1 Jun. 7, 2018

(51) Int. Cl. *H04L 12/937* (2013.01)

(52)

U.S. Cl.

See application file for complete search history.

## (56) References Cited

# U.S. PATENT DOCUMENTS

| 4,499,578 A   | 2/1985  | Marouf et al.        |

|---------------|---------|----------------------|

| 4,644,496 A   | 2/1987  | Andrews              |

| 5,047,917 A   | 9/1991  | Athas et al.         |

| 5,151,900 A   | 9/1992  | Snyder et al.        |

| 5,267,235 A * | 11/1993 | Thacker H04L 12/5601 |

|               |         | 340/2.24             |

| 5,386,413 | A            |   | 1/1995  | McAuley et al.     |

|-----------|--------------|---|---------|--------------------|

| 5,649,108 | $\mathbf{A}$ |   |         | Spiegel et al.     |

| 5,659,796 | A            |   | 8/1997  | Thorson et al.     |

| 5,701,416 | A            |   | 12/1997 | Thorson et al.     |

| 5,732,087 | $\mathbf{A}$ |   | 3/1998  | Lauer              |

| 5,911,152 | A            | * | 6/1999  | Wooten G06F 13/387 |

|           |              |   |         | 711/201            |

#### (Continued)

#### FOREIGN PATENT DOCUMENTS

| KR | 10-0825754 B1   | 4/2008 |          |         |

|----|-----------------|--------|----------|---------|

| WO | WO-0013092 A2 * | 3/2000 | <br>G06F | 13/4208 |

| WO | 2017/040697 A1  | 3/2017 |          |         |

#### OTHER PUBLICATIONS

Manchanda et al., *Non-Uniform Memory Access (NUMA)*, New York University, http://www.cs.nyu.edu/~lerner/spring10/projects/NUMA.pdf, 4 pages, 2010.

(Continued)

Primary Examiner — Hassan Kizou

Assistant Examiner — Deepa Belur

(74) Attorney, Agent, or Firm — Park, Vaughan, Fleming & Dowler LLP

# (57) ABSTRACT

This patent application relates generally to a predictive arbitration circuit for use in arbitrating access by a number of data streams to a shared resource managed by a destination (arbiter), where each data stream is associated with a number of sources competing for the shared resource, and the destination provides access to the shared resource based on the number of sources competing for the shared resource rather than just on the number of data streams. Among other things, this approach can more fairly distribute access to the shared resource among the competing sources.

# 21 Claims, 20 Drawing Sheets

# US 10,944,694 B2 Page 2

| (56)                               | Referen          | ces Cited                                  | 2009/0210711 A1 8/2009 Moskowitz                                                                                       |

|------------------------------------|------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| U.S.                               | . PATENT         | DOCUMENTS                                  | 2009/0260083 A1 10/2009 Szeto et al.<br>2010/0125683 A1 5/2010 Soeda et al.                                            |

| 5,924,119 A                        | * 7/1999         | Sindhu G06F 13/364                         | 2010/0217949 A1 8/2010 Schopp et al.<br>2011/0047439 A1* 2/2011 Jorda                                                  |

| 5,933,610 A                        | * 8/1999         | 711/119<br>Chambers G06F 13/364<br>710/108 | 2011/0066753 A1 3/2011 Wang et al.<br>2011/0134797 A1 6/2011 Banks et al.                                              |

| 6,092,137 A                        | * 7/2000         | Huang G06F 13/364<br>710/107               | 2011/0149986 A1 6/2011 Sugawara<br>2011/0179208 A1* 7/2011 Koka H04J 3/1682                                            |

| 6,101,552 A<br>6,147,976 A         |                  | Chiang et al. Shand et al.                 | 710/117<br>2011/0185159 A1 7/2011 Bishop et al.                                                                        |

| 6,167,437 A<br>6,195,703 B1        | 2/2001           | Stevens et al.<br>Blumenau et al.          | 2011/0213928 A1 9/2011 Grube et al.<br>2012/0047310 A1* 2/2012 Satpathy G11C 7/10<br>710/317                           |

| 6,216,167 B1                       |                  | Momirov                                    | 2012/0072635 A1 3/2012 Yoshida et al.                                                                                  |

| 6,272,112 B1<br>6,407,999 B1       | 8/2001<br>6/2002 | Olkkonen et al.                            | 2013/0021910 A1 1/2013 Crisan et al.                                                                                   |

| 6,415,361 B1                       |                  | Moh et al.                                 | 2013/0051397 A1 2/2013 Guo et al.                                                                                      |

| 6,674,720 B1                       |                  | Passint et al.                             | 2013/0246715 A1 9/2013 Miyauchi                                                                                        |

| 6,687,756 B1                       |                  | Rawson, III                                | 2013/0250792 A1 9/2013 Yoshida et al.                                                                                  |

| 6,691,165 B1                       | 2/2004           | Bruck et al.                               | 2014/0052838 A1 2/2014 Giacomoni et al.                                                                                |

| 6,721,816 B1                       |                  | •                                          | 2014/0146666 A1 5/2014 Kwan et al.                                                                                     |

| 6,804,233 B1                       |                  | Congdon et al.                             | 2014/0241443 A1 8/2014 Nowick et al.<br>2014/0258620 A1 9/2014 Nagarajan et al.                                        |

| 6,839,794 B1                       | * 1/2005         | Schober H04L 45/302                        | 2014/0258020 A1 9/2014 Nagarajan et al.<br>2014/0359195 A1 12/2014 Nishiyashiki                                        |

| 6 007 041 D1                       | 6/2005           | 370/229                                    | 2015/0089053 A1 3/2015 Harper et al.                                                                                   |

| 6,907,041 B1<br>7,177,946 B1       |                  | Turner et al.<br>Kaluve et al.             | 2015/0172196 A1 6/2015 Avanindra                                                                                       |

| 7,177,940 B1<br>7,209,476 B1       |                  | Colloff et al.                             | 2016/0112282 A1 4/2016 Rochon                                                                                          |

| 7,395,346 B2                       |                  | Pinder et al.                              | 2016/0127191 A1 5/2016 Nair                                                                                            |

| 7,512,705 B2                       |                  |                                            | 2016/0188469 A1 6/2016 Nagarajan et al.                                                                                |

| 7,581,021 B2                       | 8/2009           | Errickson et al.                           | 2016/0191420 A1 6/2016 Nagarajan et al.                                                                                |

| 7,593,336 B2                       |                  | Varanasi et al.                            | 2016/0196233 A1 7/2016 Chen et al.<br>2016/0266898 A1* 9/2016 Kitamura G06F 9/3001                                     |

| 7,707,635 B1                       |                  | Kuo et al.                                 | 2016/0200398 A1 9/2010 Kitamula                                                                                        |

| 8,077,602 B2                       |                  | Arimilli et al.                            | 2016/0292423 A1 10/2016 Yao et al.                                                                                     |

| 8,081,646 B1<br>8,693,485 B2       |                  | Bishop et al.<br>Kotha et al.              | 2016/0295624 A1 10/2016 Novlan et al.                                                                                  |

| 8,706,893 B2                       |                  | Even et al.                                | 2016/0345307 A1 11/2016 Huang et al.                                                                                   |

| 8,767,587 B1                       |                  | Finn et al.                                | 2017/0046203 A1 2/2017 Singh et al.                                                                                    |

| 9,135,094 B2                       |                  | Vasters et al.                             | 2017/0086151 A1 3/2017 Chen                                                                                            |

| 9,237,093 B2                       |                  | Tietz et al.                               | 2017/0295112 A1 10/2017 Cheng et al.<br>2017/0318335 A1 11/2017 Ding et al.                                            |

| 9,866,467 B1                       |                  | Barnum et al.                              | 2017/0318333 A1 11/2017 Ding et al.<br>2018/0159800 A1 6/2018 Tietz et al.                                             |

| 10,237,198 B2;                     |                  | Tietz H04L 47/527                          | 2019/0334830 A1* 10/2019 Dropps                                                                                        |

|                                    |                  | Dropps                                     |                                                                                                                        |

| 2002/0039364 A1°                   |                  | 370/462<br>Kamiya H04L 47/10               | OTHER PUBLICATIONS                                                                                                     |

|                                    |                  | 370/389                                    | Wikipedia.org, Non-Uniform Memory Access, http://en.wikipedia.                                                         |

| 2002/0194182 A1<br>2003/0106052 A1 |                  | Fujita et al.<br>Morrison et al.           | org/wiki/Non-Uniform_Memory_Access, 4 pages, Feb. 22, 2013.                                                            |

| 2004/0019891 A1                    |                  | Koenen                                     | Wiki/Uniform Memory Access, http://en.wikipedia.org/                                                                   |

| 2004/0078459 A1                    | 4/2004           |                                            | wiki/Uniform_Memory_Access, 1 page, Mar. 8, 2013.<br>Tietz, J. G., et al.; "2mo. Office Action cited in U.S. Appl. No. |

| 2004/0228326 A1                    |                  | Pearson                                    | 15/370,529" dated Mar. 9, 2018; 13 pages.                                                                              |

| 2005/0102477 A1                    |                  | Sukegawa                                   | Tietz, J. G., et al.; "Non-Final Office Action cited in U.S. Appl. No.                                                 |

| 2005/0108444 A1                    |                  | Flauaus et al.<br>Smith et al.             | 15/370,508"; dated Mar. 28, 2018; 29 pages.                                                                            |

| 2005/0228926 A1<br>2005/0228952 A1 |                  | Mayhew et al.                              | Abeyratne, S. N.; "Studies in Exascale Computer Architecture";                                                         |

| 2005/0220552 AT<br>2006/0047907 A1 |                  | Shiga et al.                               | 2017; 153 pages.                                                                                                       |

| 2006/0187849 A1                    |                  | Hamedi                                     | Notice of Allowance received for U.S. Appl. No. 15/370,529, dated                                                      |

| 2007/0050563 A1°                   | * 3/2007         | Alsup G06F 9/3004                          | Jun. 21, 2018, 5 pages.                                                                                                |

| 2007/0064699 A1°                   |                  | 711/145<br>Bernick H04L 47/56              | Notice of Allowance received for U.S. Appl. No. 15/370,529, dated Aug. 29, 2018, 5 pages.                              |

|                                    |                  | 370/392                                    | Non-Final Office Action received for U.S. Appl. No. 15/370,545, dated Nov. 1, 2018, 8 pages.                           |

| 2007/0079045 A1<br>2007/0091911 A1 | 4/2007<br>4/2007 | Luke<br>Watanabe et al.                    | Non-Final Office Action Received for U.S. Appl. No. 15/370,508,                                                        |

| 2007/0091911 A1<br>2007/0133415 A1 |                  |                                            | dated Oct. 16, 2018, 20 pages.                                                                                         |

| 2007/0133413 A1<br>2007/0185682 A1 |                  | Eidson                                     | Search Report and Written Opinion received for PCT Application                                                         |

| 2007/0183082 A1<br>2008/0037544 A1 |                  | Yano et al.                                | No. PCT/US2019/053739, dated Feb. 26, 2020, 11 pages.                                                                  |

| 2009/0037344 A1                    |                  | Gobara et al.                              | ,,,,,, _                                                                                                               |

| 2009/0190588 A1                    |                  | Eder et al.                                | * cited by examiner                                                                                                    |

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6 <u>600</u>

| •   | Virtual VCm Dedicated Pool |

|-----|----------------------------|

| · · |                            |

| i   | Virtual VC0 Dedicated Pool |

| ·   |                            |

|     | Shared Pool                |

FIG. 11

FIG. 12 1200

FIG. 13 <u>1300</u>

FIG. 14 <u>1400</u>

FIG. 15 <u>1500</u>

FIG. 16

FIG. 17 <u>1700</u>

FIG. 18

FIG. 19

| Index                                    | Source Mask | Priority | Count              | Done                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Description                        |

|------------------------------------------|-------------|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|                                          |             |          |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |

|                                          |             | 00001    | Will.              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RR for source 0 for one grant      |

| Secretary Control                        |             | 00010    | Arriva<br>Transfer |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RR for source 1 for one grant      |

| 2                                        |             | 00100    | No.                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RR for source 2 for one grant      |

| 3                                        | 1111        | 01000    | ******             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RR for source 3 for one grant      |

| 4                                        | 1111        | 10000    |                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RR for source 4 for two grants     |

|                                          | 11110       | 00000    | 4                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Aging on Source 1-4 for four grant |

| б                                        | 00001       | 00000    | * Arrest           | Age and the same of the same o | Source O wins (if pending)         |

| . <b>4</b> X ( <b>4</b> 5, -2 <b>X</b> ) |             |          |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |

| 11                                       | ZZZZZ       | XXXXXX   | <b>X</b>           | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Not Used                           |

FIG. 20

FIG. 21

## PREDICTIVE ARBITRATION CIRCUIT

#### FIELD OF THE INVENTION

The invention generally relates to a crossbar switch <sup>5</sup> predictive arbitration circuit.

#### BACKGROUND OF THE INVENTION

High-performance computer ("HPC") systems typically 10 include many processors, each with its own local memory. At least some pairs of the processors are interconnected via links to enable each processor to access memory ("non-local" memory") of each, or at least some, of the other processors. Some such systems are constructed according to non-uni- 15 form memory access ("NUMA") designs, in which access to non-local memory is slower than access to local memory. Because a HPC system may not include a separate link between every pair of processors, some non-local memory accesses are routed through third (or more) processors, 20 thereby traversing multi-hop routes. However, determining routes quickly for each non-local memory access poses problems. Furthermore, congested links or routes retard non-local memory accesses, thereby negatively impacting performance of the affected processor(s).

A crossbar switch is an assembly of individual switches between a set of inputs and a set of outputs. The switches are arranged in a matrix. If the crossbar switch has M inputs and N outputs, then a crossbar has a matrix with M×N crosspoints or places where the connections cross. At each <sup>30</sup> crosspoint is a switch that, when closed, connects one of the inputs to one of the outputs. One exemplary crossbar is a single layer, non-blocking switch in which other concurrent connections do not prevent connecting other inputs to other outputs. Collections of crossbars can be used to implement <sup>35</sup> multiple layer and blocking switches.

A typical crossbar arbitration scheme can make use of various different protocols to flow traffic from competing sources. These algorithms typically include round robin and aging arbitration protocols. Arbiters that are configured to 40 support multiple algorithms are often very complex or make significant comprises in order to meet stringent timing requirements.

#### SUMMARY OF VARIOUS EMBODIMENTS

In accordance with one embodiment of the invention, a switch with predictive arbitration comprises a plurality of source ports, each source port associated with a respective data stream, a destination port, and a predictive arbitration 50 circuit for arbitrating accesses by the data streams to the destination port, wherein the predictive arbitration circuit is configured to determine, for each of a number of data streams having packets for the destination port, a count of the number of data sources associated with the data stream; 55 determine a count of the total number of data sources competing for access to the destination port based on the count determined for each of the number of data streams; and provide accesses for the data streams having packets for the destination port based on the total number of data 60 sources competing for the destination port.

In accordance with another embodiment of the invention, an arbiter for use in arbitrating accesses by a number of data streams to a shared resource comprises a shared resource and a predictive arbitration circuit configured to determine, 65 for each of a number of data streams having packets for the shared resource, a count of the number of data sources

2

associated with the data stream; determine a count of the total number of data sources competing for access to the shared resource based on the count determined for each of the number of data streams; and provide accesses for the data streams having packets for the shared resource based on the total number of data sources competing for the shared resource.

In accordance with another embodiment of the invention, a method for arbitrating accesses by a number of data streams to a shared resource comprises determining, for each of a number of data streams having packets for the shared resource, a count of the number of data sources associated with the data stream; determining a count of the total number of data sources competing for access to the shared resource based on the count determined for each of the number of data streams; and providing accesses for the data streams having packets for the shared resource based on the total number of data sources competing for the shared resource.

In various alternative embodiments, the predictive arbitration circuit may be configured to receive, from at least one source port, the count of the number of data sources associated with the respective data stream. The predictive arbitration circuit may be configured to receive the count on a communication connection between the source port and the destination port used for transporting packets of the respective data stream from the source port to the destination port and/or may be configured to receive the count outside of a communication connection between the source port and the destination port used for transporting packets of the respective data stream from the source port to the destination port. The predictive arbitration circuit may be configured to provide accesses for the data streams having packets for the destination port in proportion to the number of data sources associated with the data stream relative to the total number of data sources competing for the destination port. The predictive arbitration circuit may be further configured to output the count of the total number of data sources competing for access to the destination port, e.g., over the destination port.

### BRIEF DESCRIPTION OF THE DRAWINGS

Those skilled in the art should more fully appreciate advantages of various embodiments of the invention from the following "Description of Illustrative Embodiments," discussed with reference to the drawings summarized immediately below.

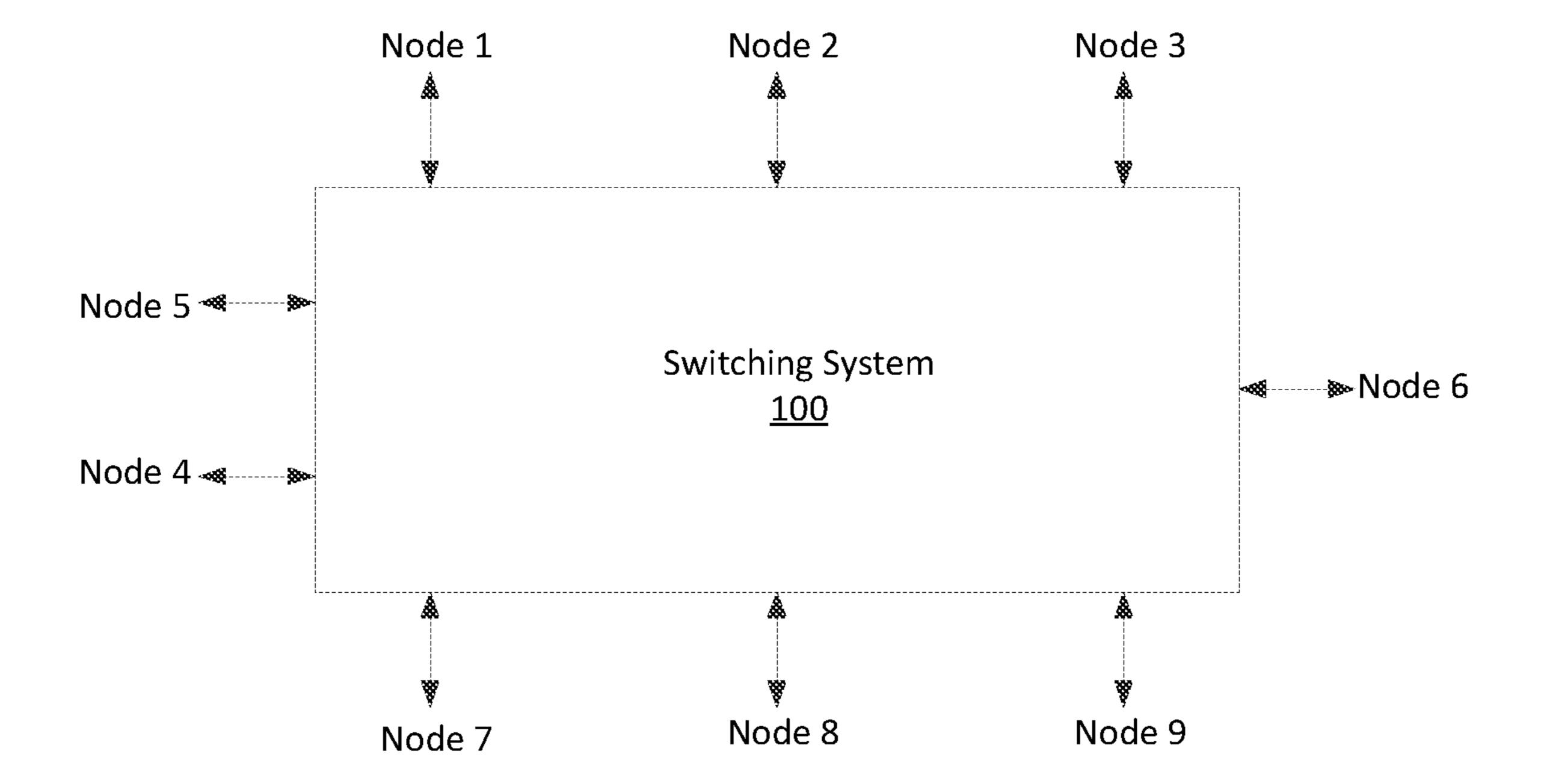

FIG. 1 is a schematic diagram showing an exemplary switching system that is configured to switch or route packets between nodes of a network.

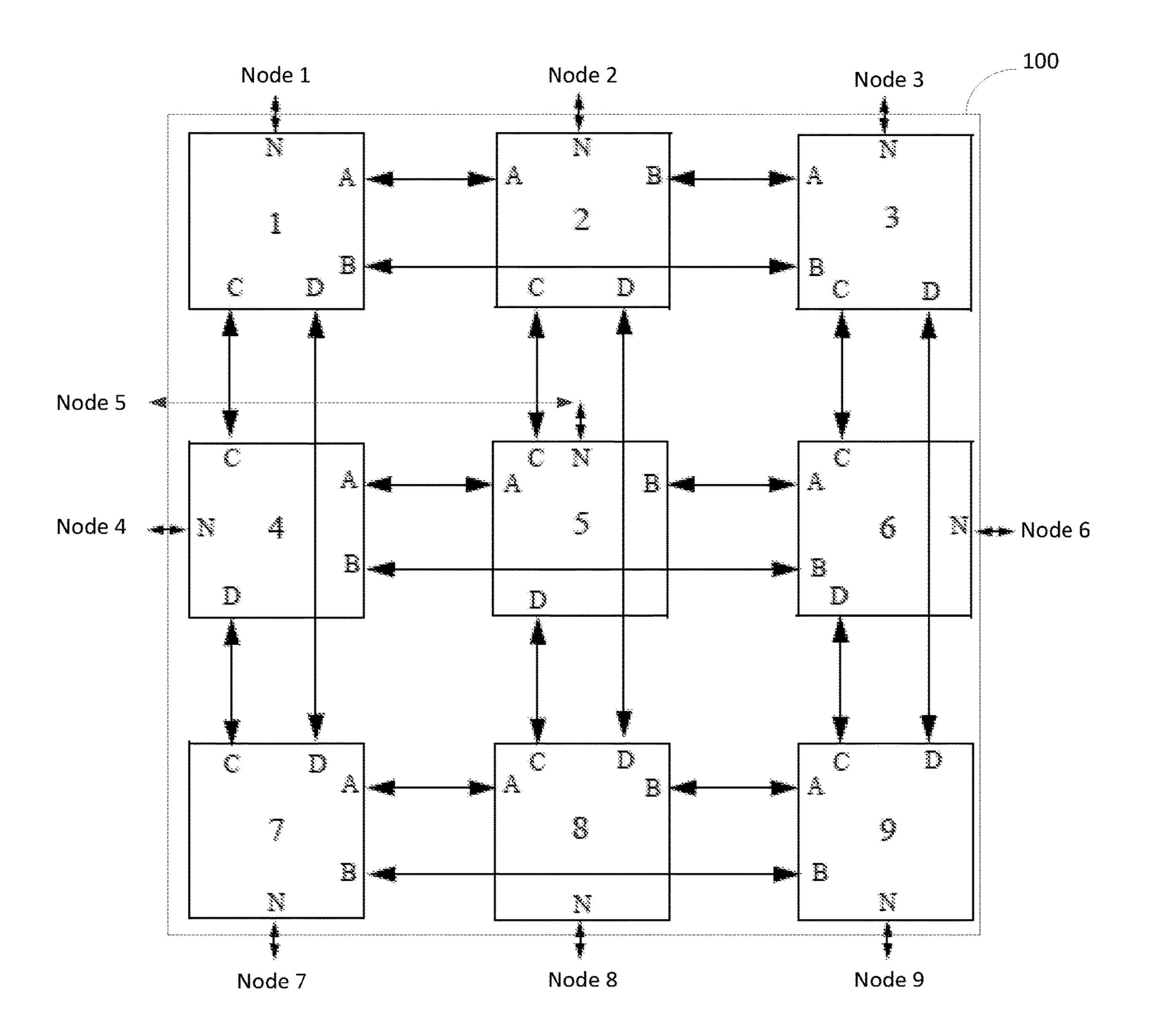

FIG. 2 is a schematic diagram showing an exemplary switching system in the form of a crossbar or matrix switch, in accordance with various exemplary embodiments.

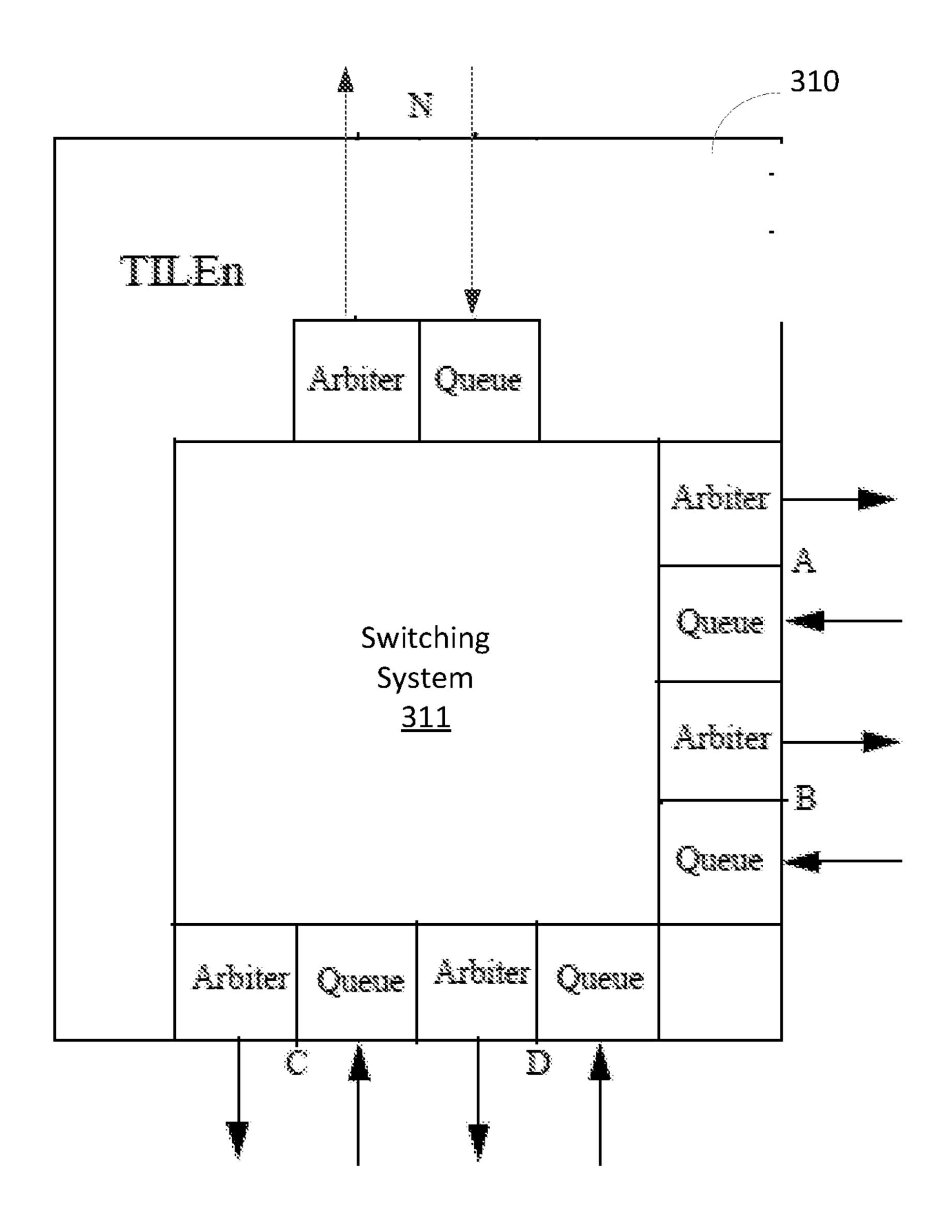

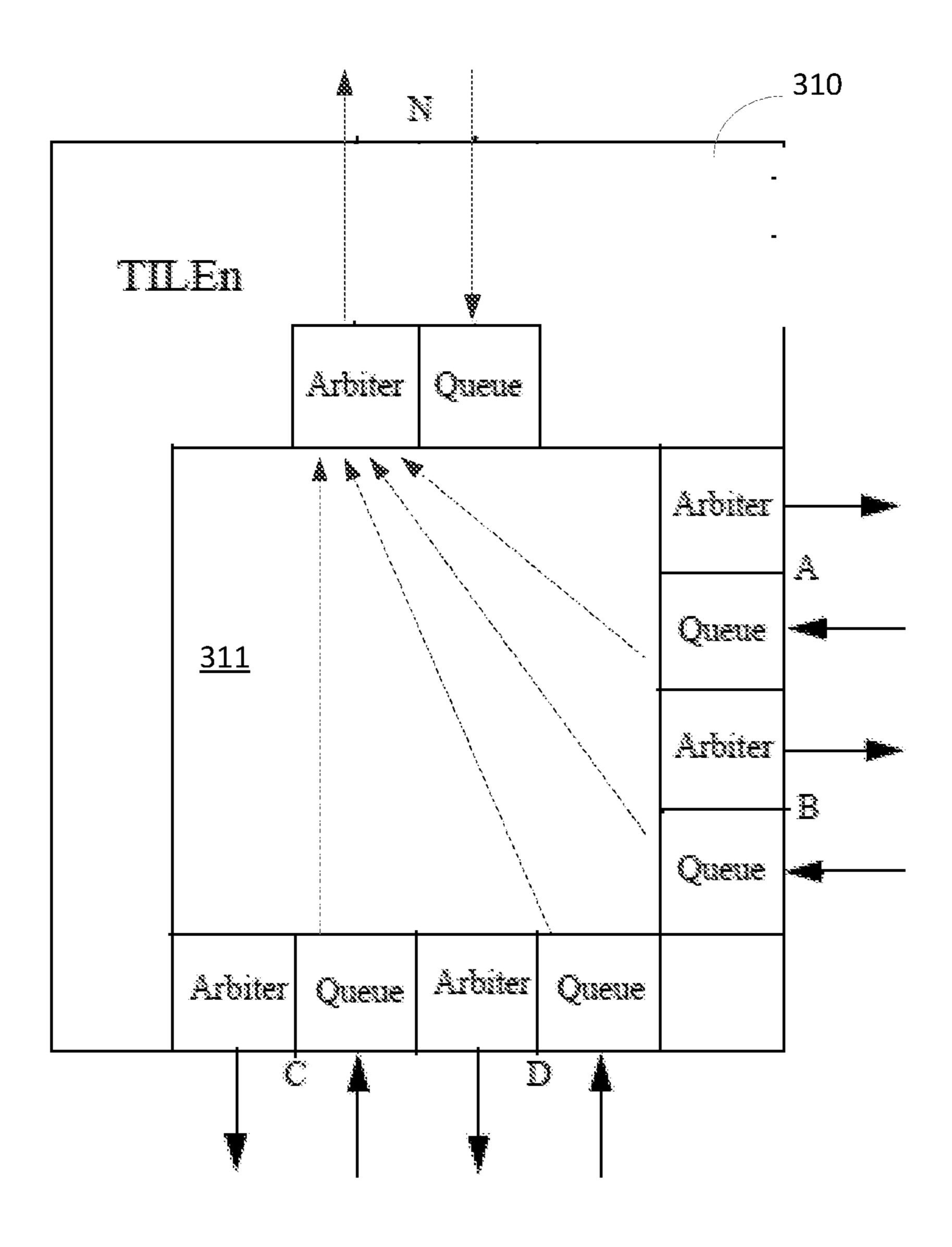

FIG. 3 is a schematic diagram showing elements of a tile of the exemplary switching system of FIG. 2, in accordance with various exemplary embodiments.

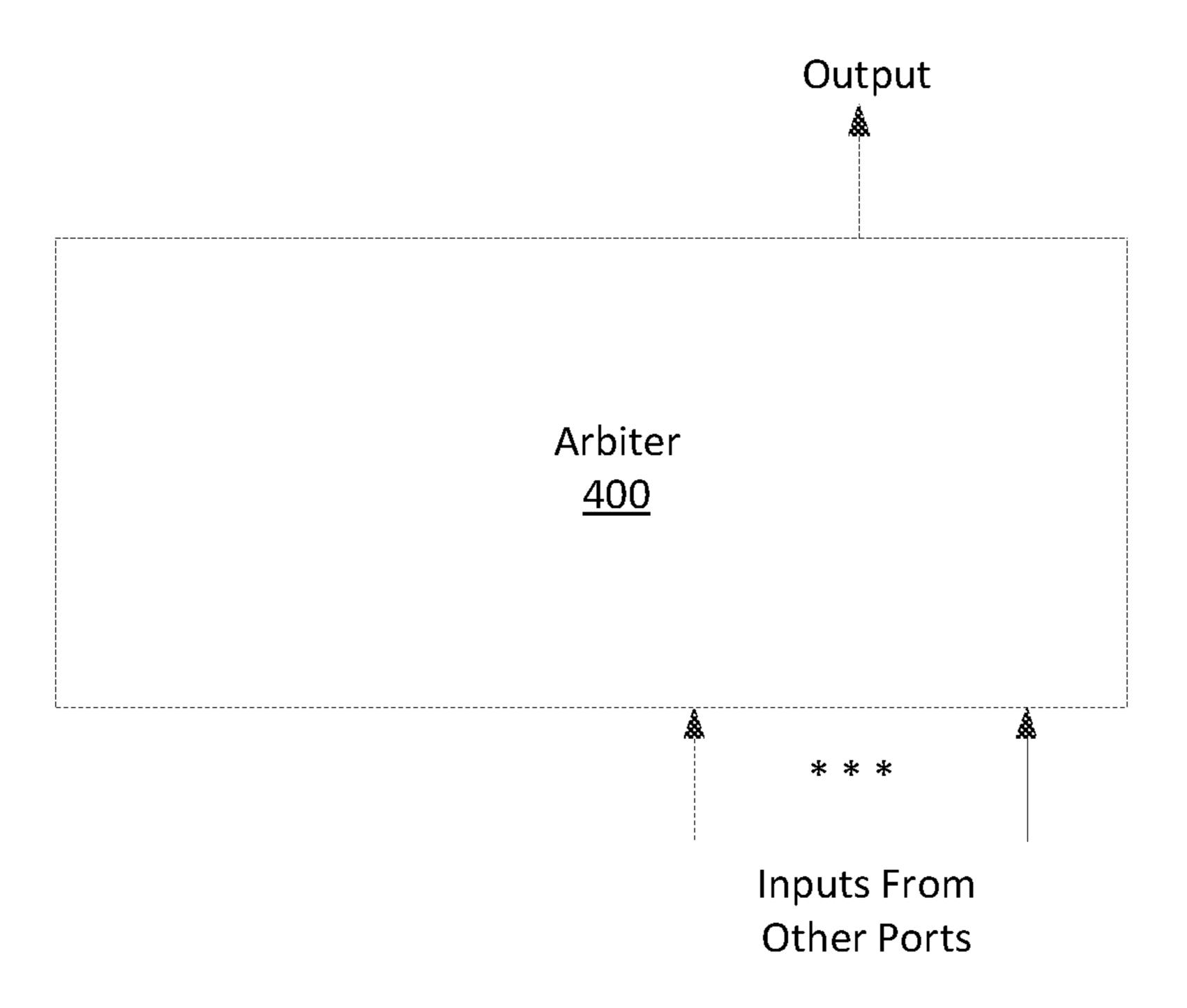

FIG. 4 is a schematic diagram of an arbiter of the exemplary tile of FIG. 3, in accordance with various exemplary embodiments.

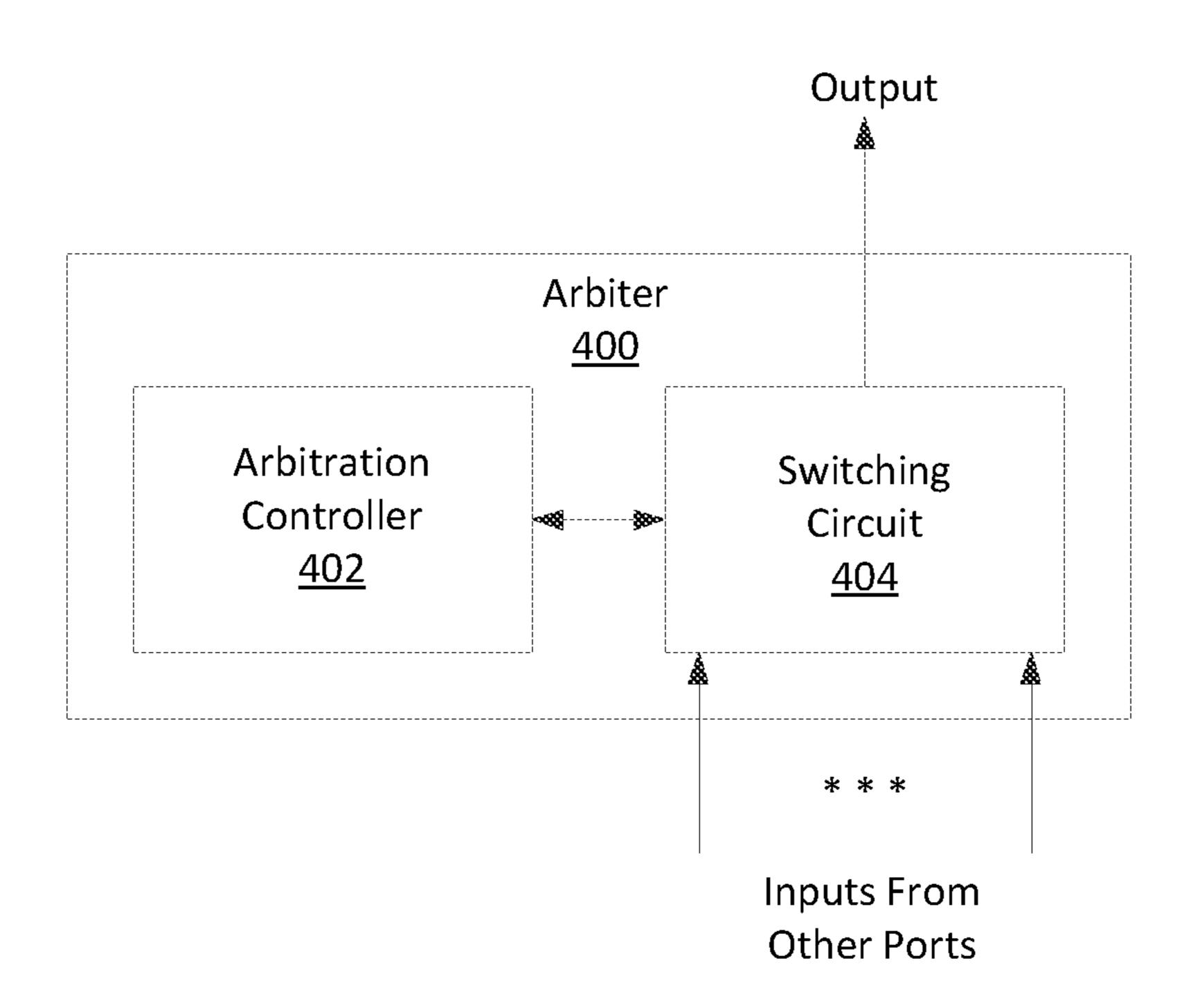

FIG. 5 is a schematic diagram showing elements of the arbiter of FIG. 4, in accordance with various exemplary embodiments.

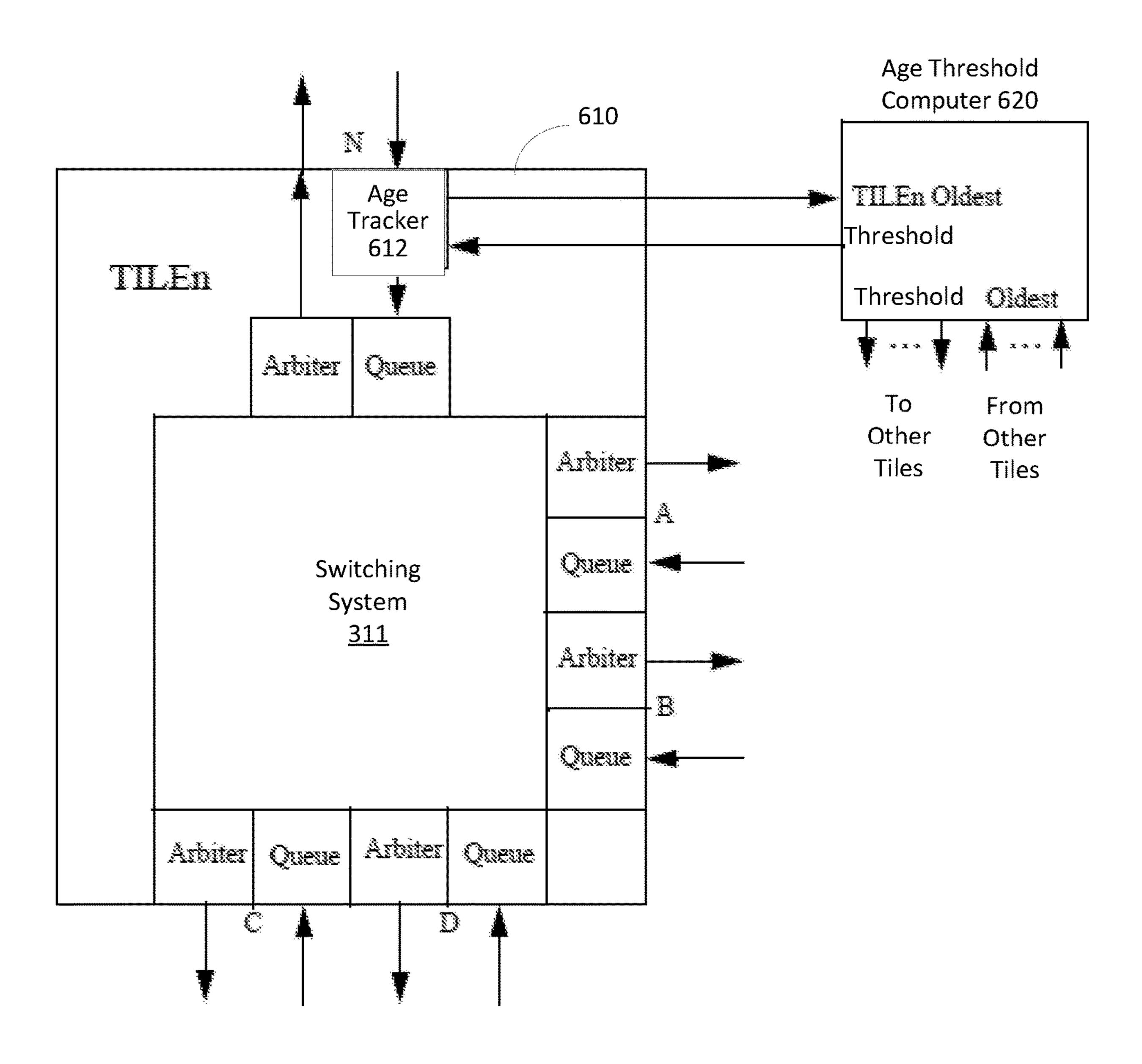

FIG. 6 is a schematic diagram showing an exemplary switching system with an age-based arbitration circuit, in accordance with various exemplary embodiments.

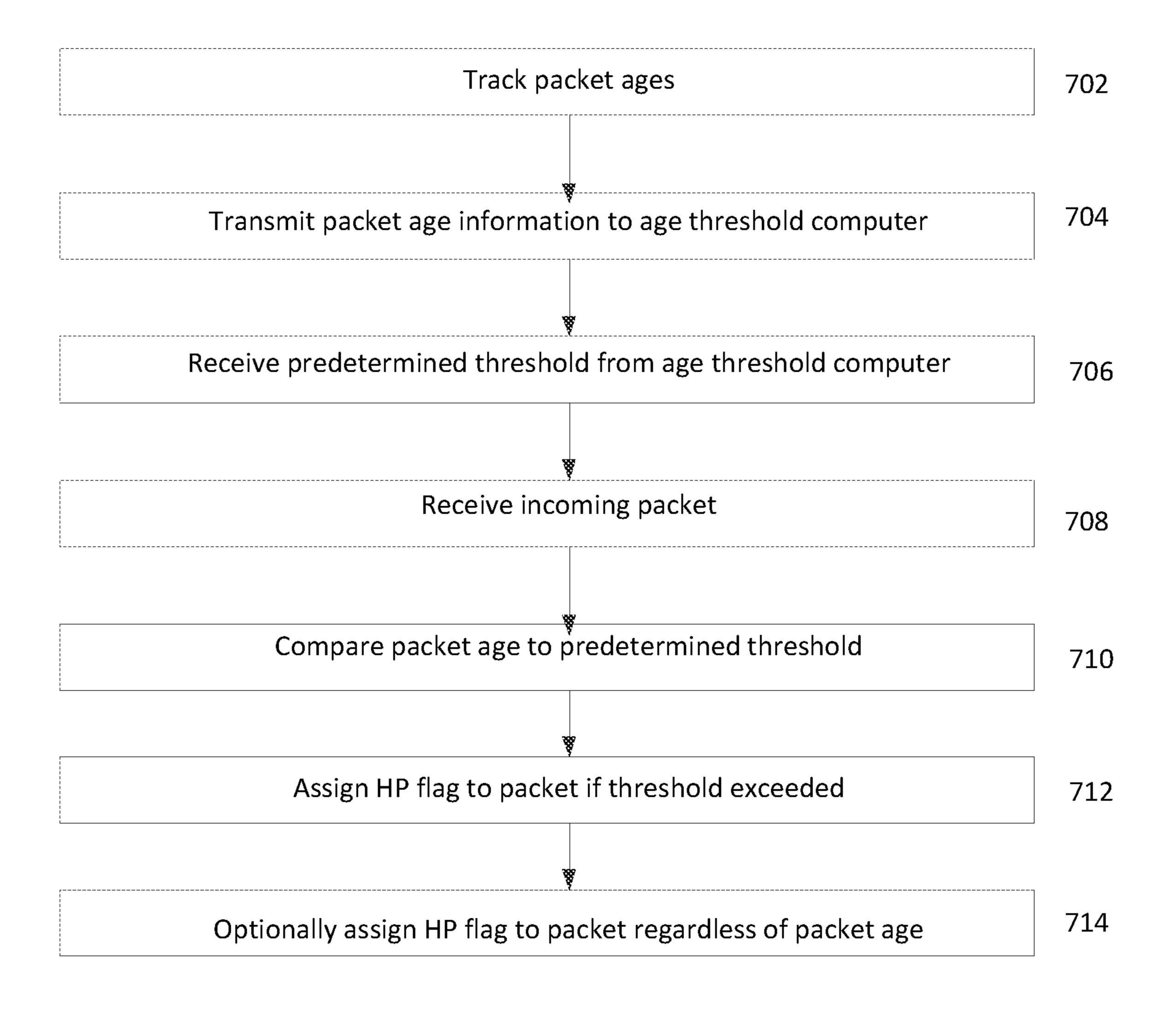

- FIG. 7 is a logic flow diagram for the age tracker of an age-based arbitration circuit, in accordance with various exemplary embodiments.

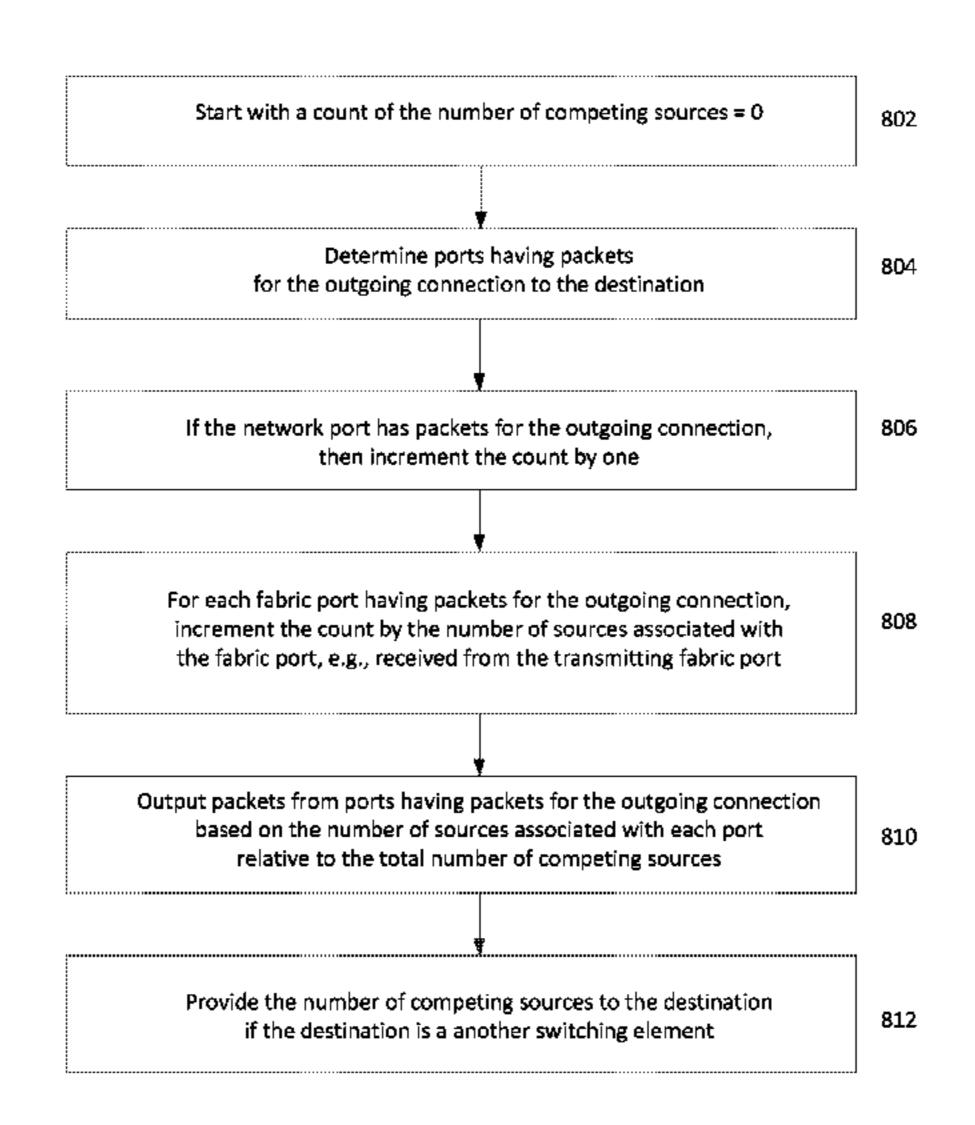

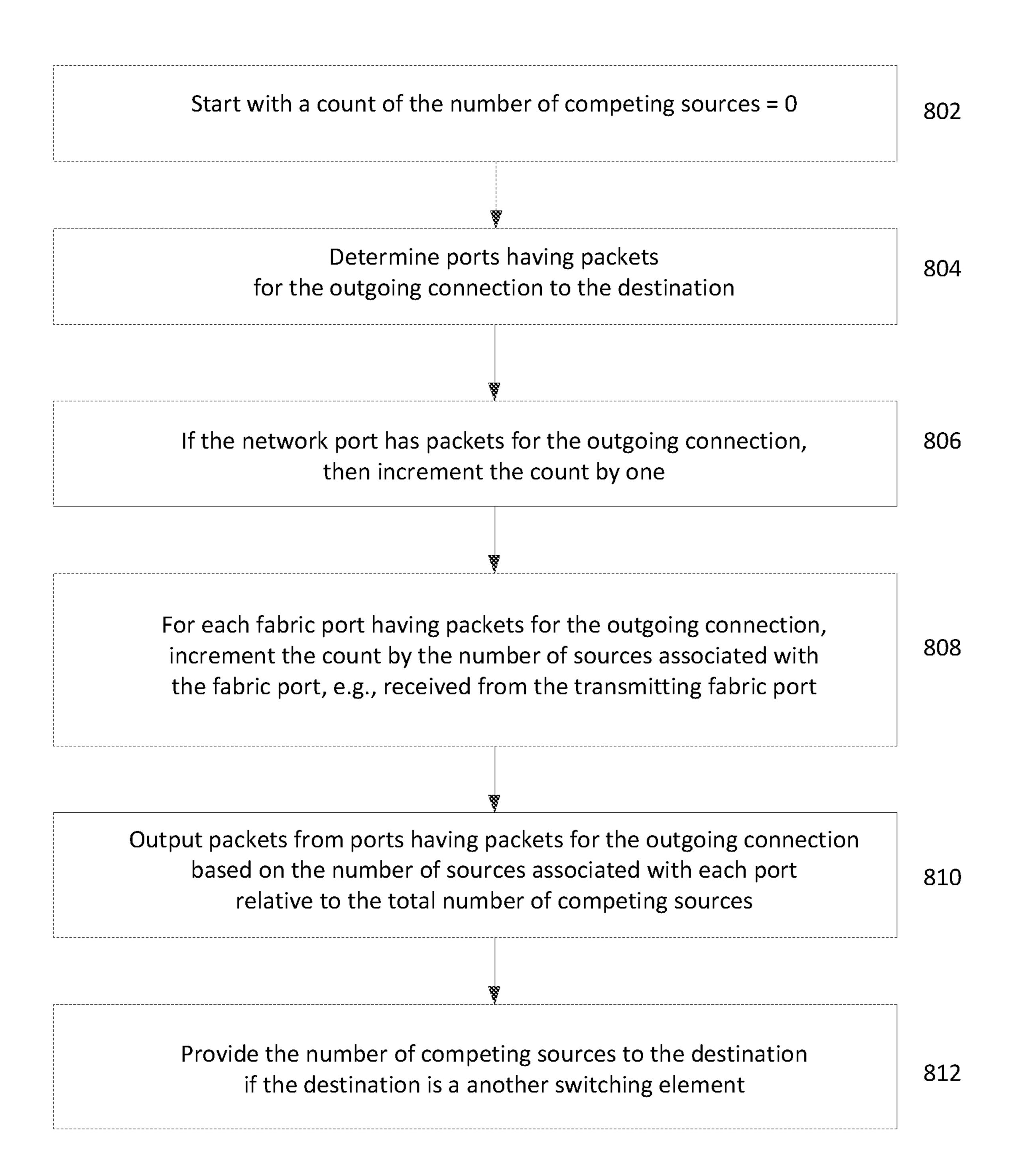

- FIG. 8 is a logic flow diagram for predictive arbitration by the arbiter of a port, in accordance with various exemplary embodiments, in accordance with various exemplary embodiments.

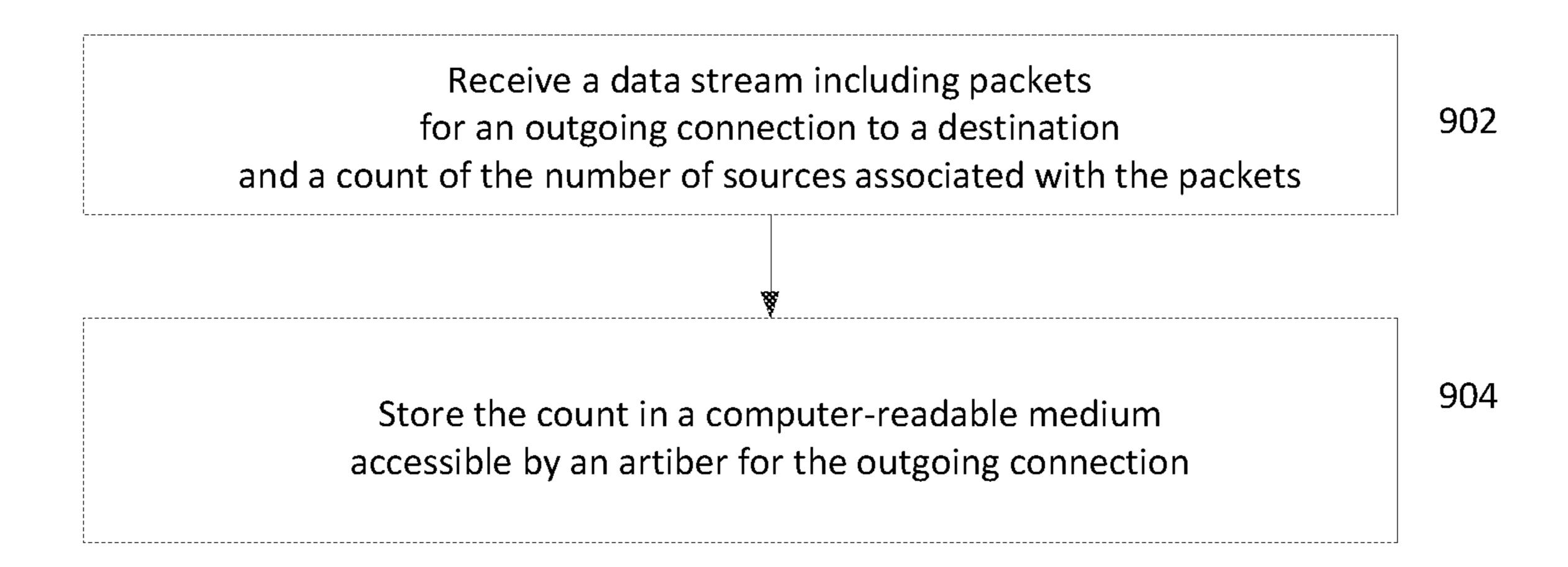

- FIG. 9 is a logic flow diagram for predictive arbitration by the queue circuit of a port, in accordance with various exemplary embodiments.

- FIG. 10 is a schematic diagram showing a shared resource pool maintained by a destination, in accordance with various exemplary embodiments.

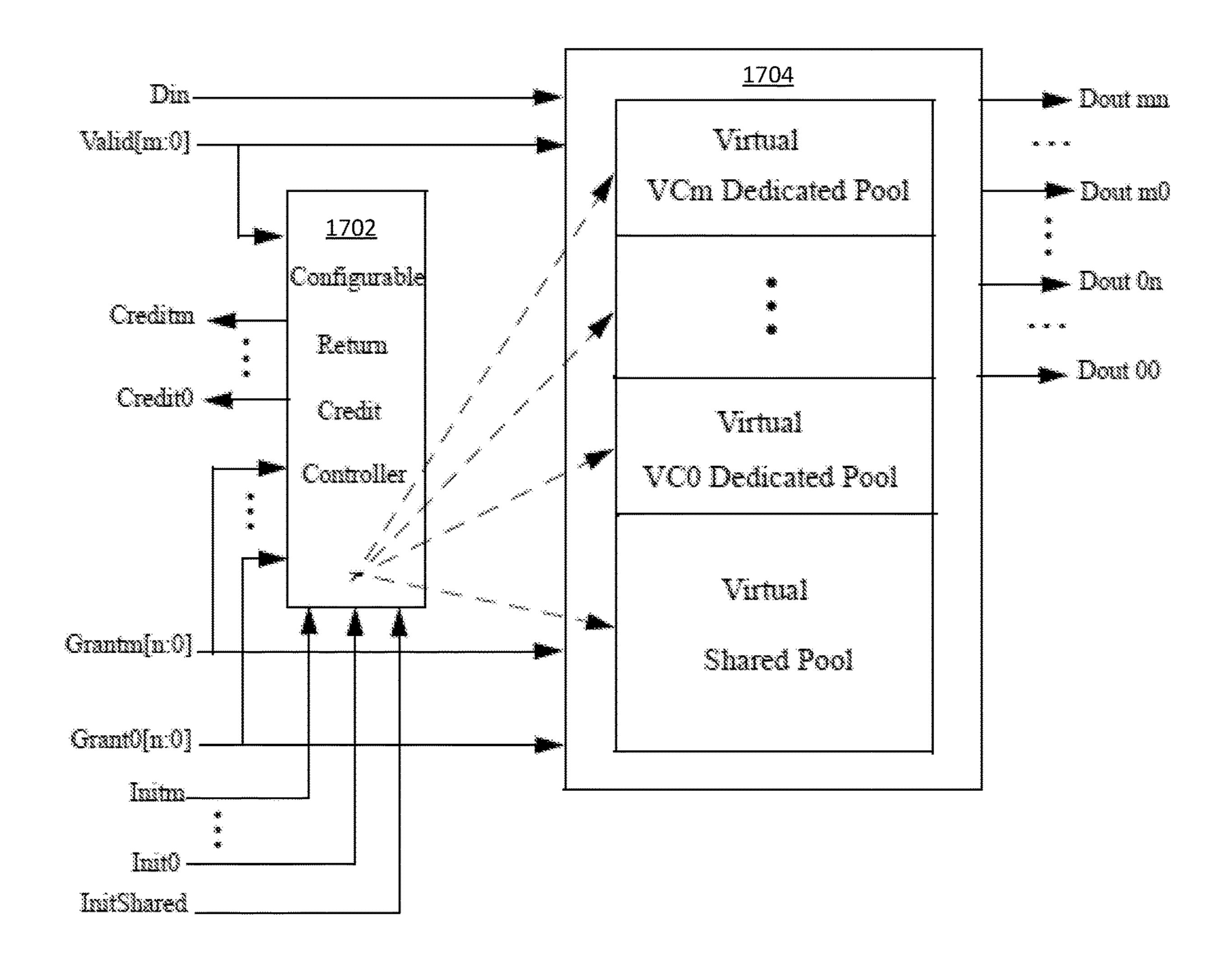

- FIG. 11 is a schematic diagram showing some possible arrangements of virtual channels for a shared-credit arbitration circuit in the context of a tile of a switching system such as of the type shown in FIG. 3, in accordance with various exemplary embodiments.

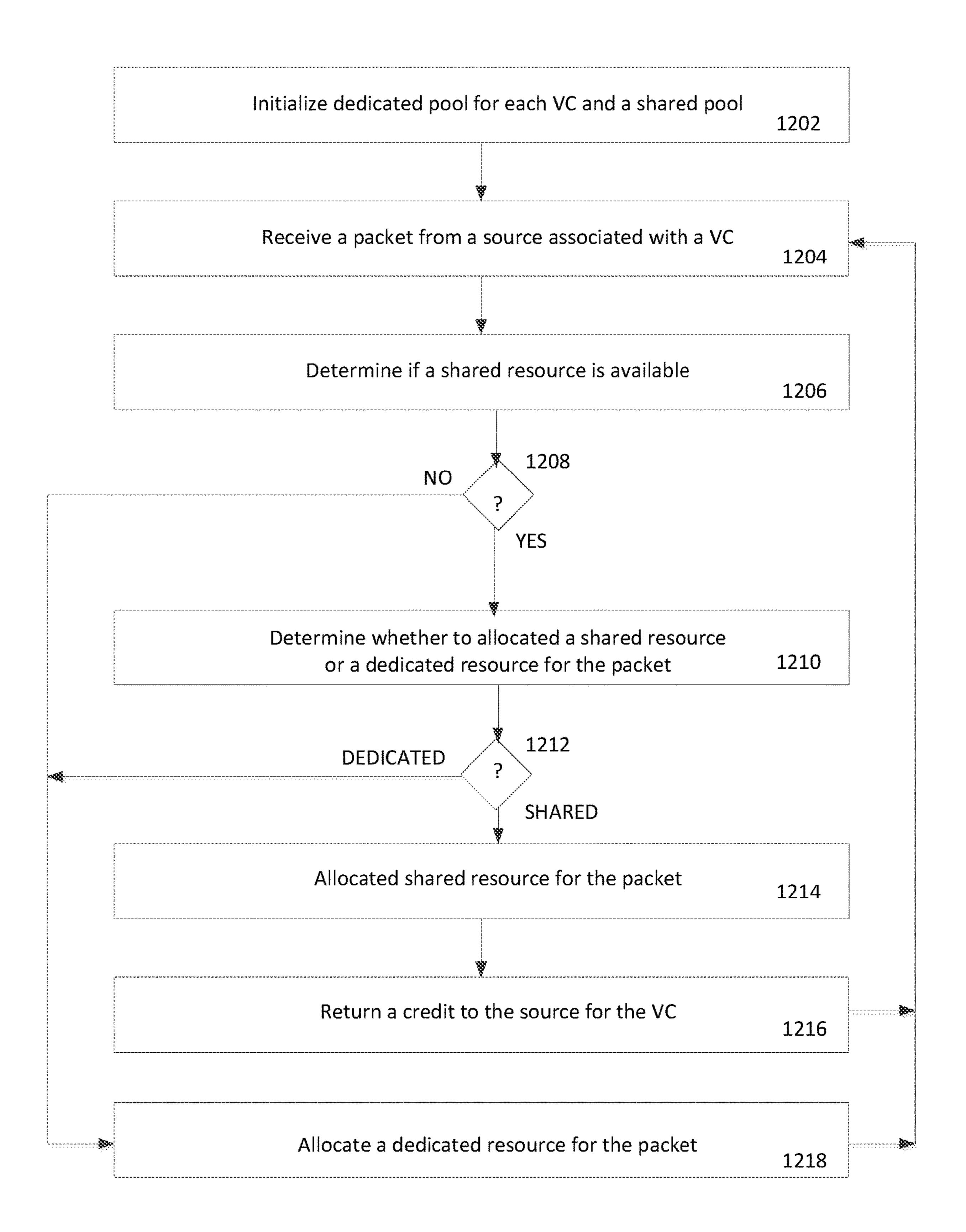

- FIG. 12 is a flow chart for processing packets by a 20 destination arbiter in a shared-credit arbitration circuit, in accordance with various exemplary embodiments.

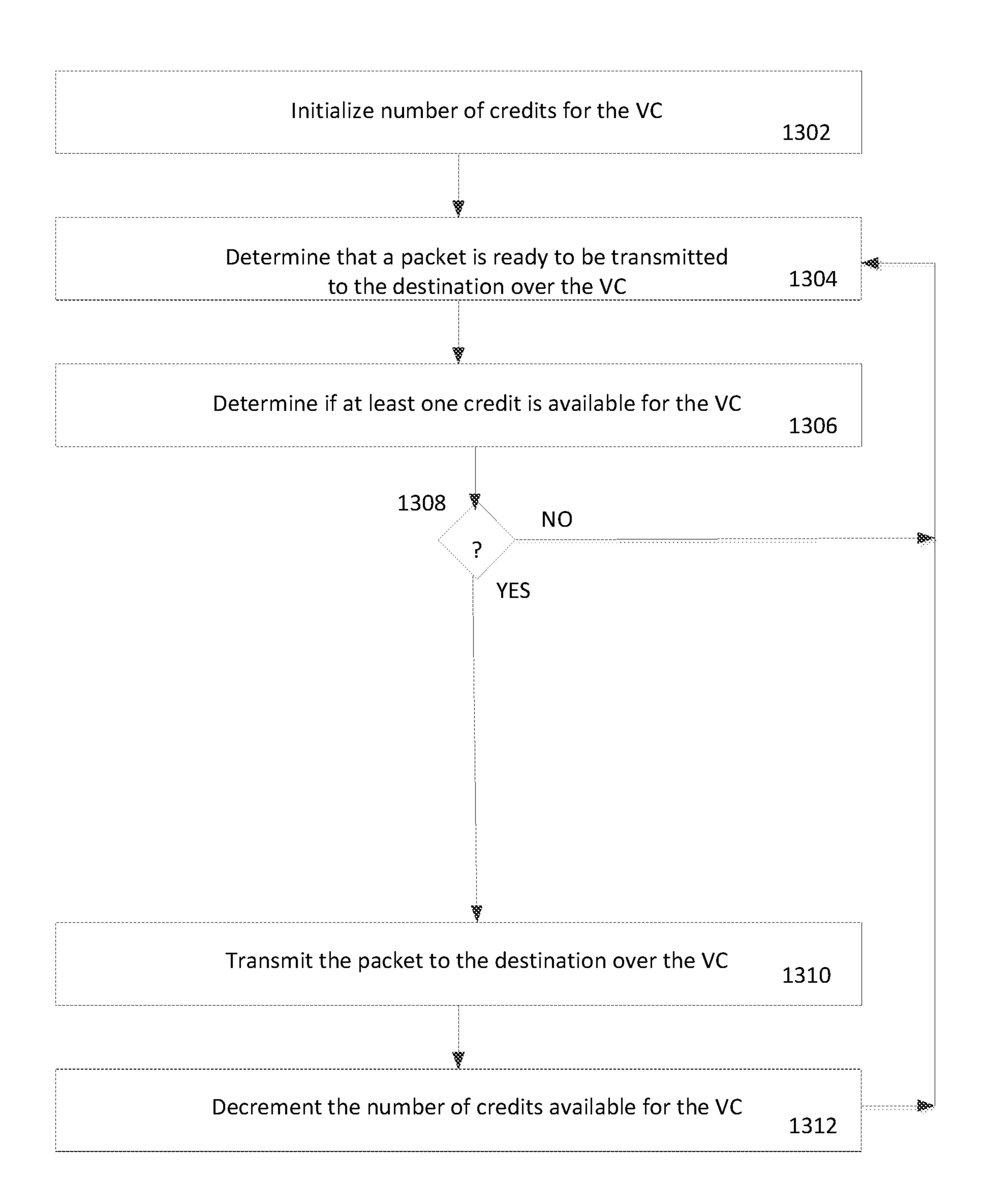

- FIG. 13 is a flow chart for processing packets by a source associated with a virtual channel in a shared-credit arbitration circuit, in accordance with various exemplary embodi- 25 ments.

- FIG. 14 is a flow chart for returning a credit to the source upon freeing a dedicated resource by the destination arbiter in a shared-credit arbitration circuit, in accordance with various exemplary embodiments.

- FIG. 15 is a flow chart for processing a returned credit by the source in a shared-credit arbitration circuit, in accordance with various exemplary embodiments.

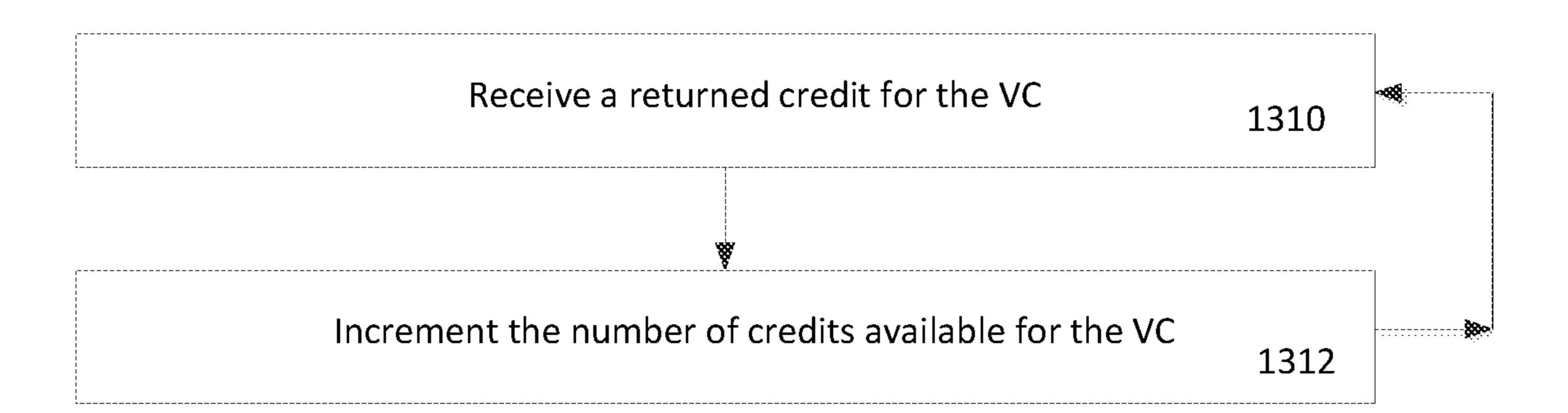

- FIG. **16** is a schematic diagram showing multiple virtual channels between a source device and a destination device <sup>35</sup> (arbiter) for a shared-credit arbitration circuit, in accordance with various exemplary embodiments.

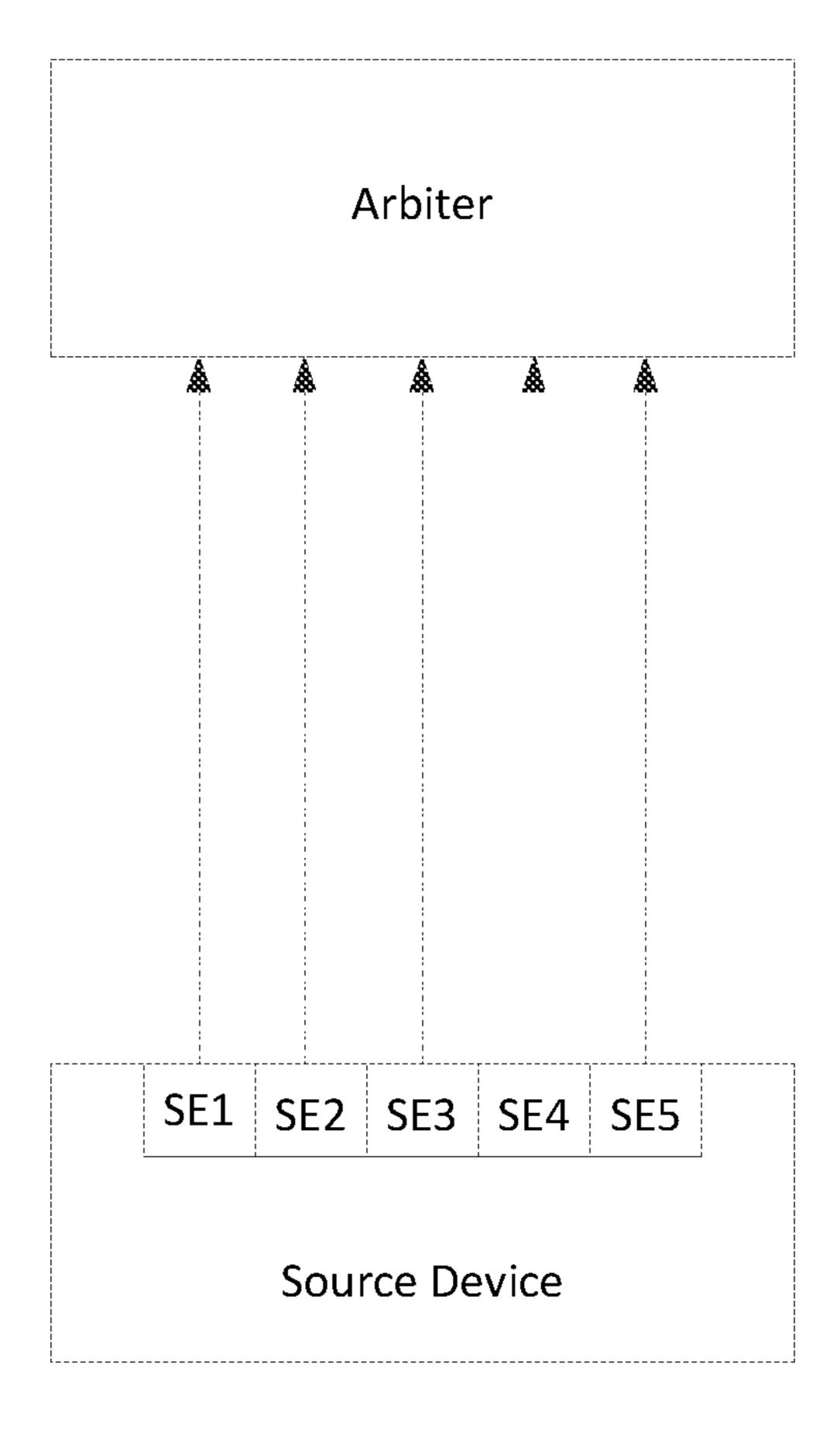

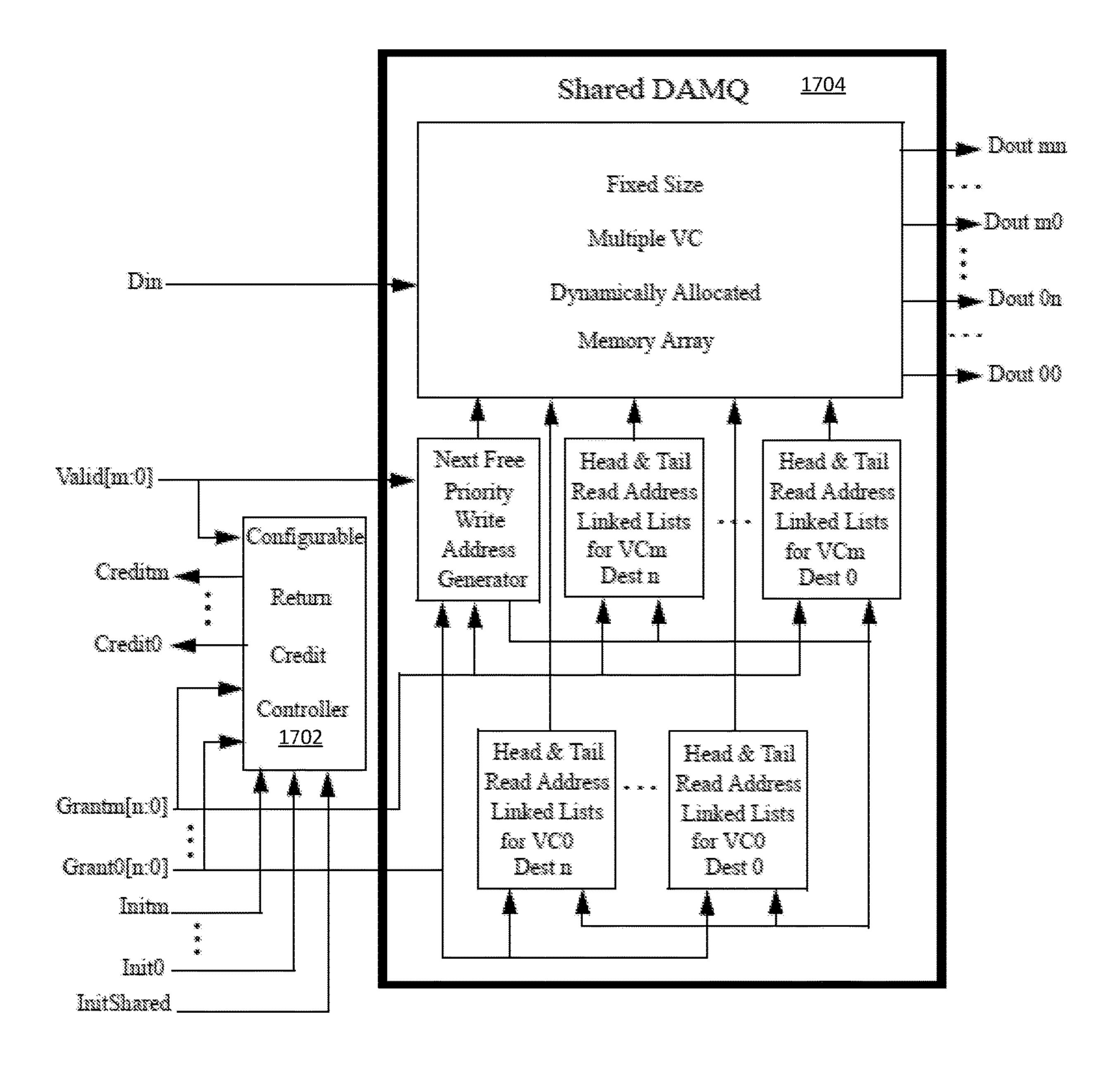

- FIG. 17 is a schematic diagram showing a DAMQ buffer system with credit-based arbitration, in accordance with various exemplary embodiments.

- FIG. 18 is a schematic diagram showing logic blocks associated with management of buffer pools in the shared DAMQ of FIG. 17, in accordance with various exemplary embodiments.

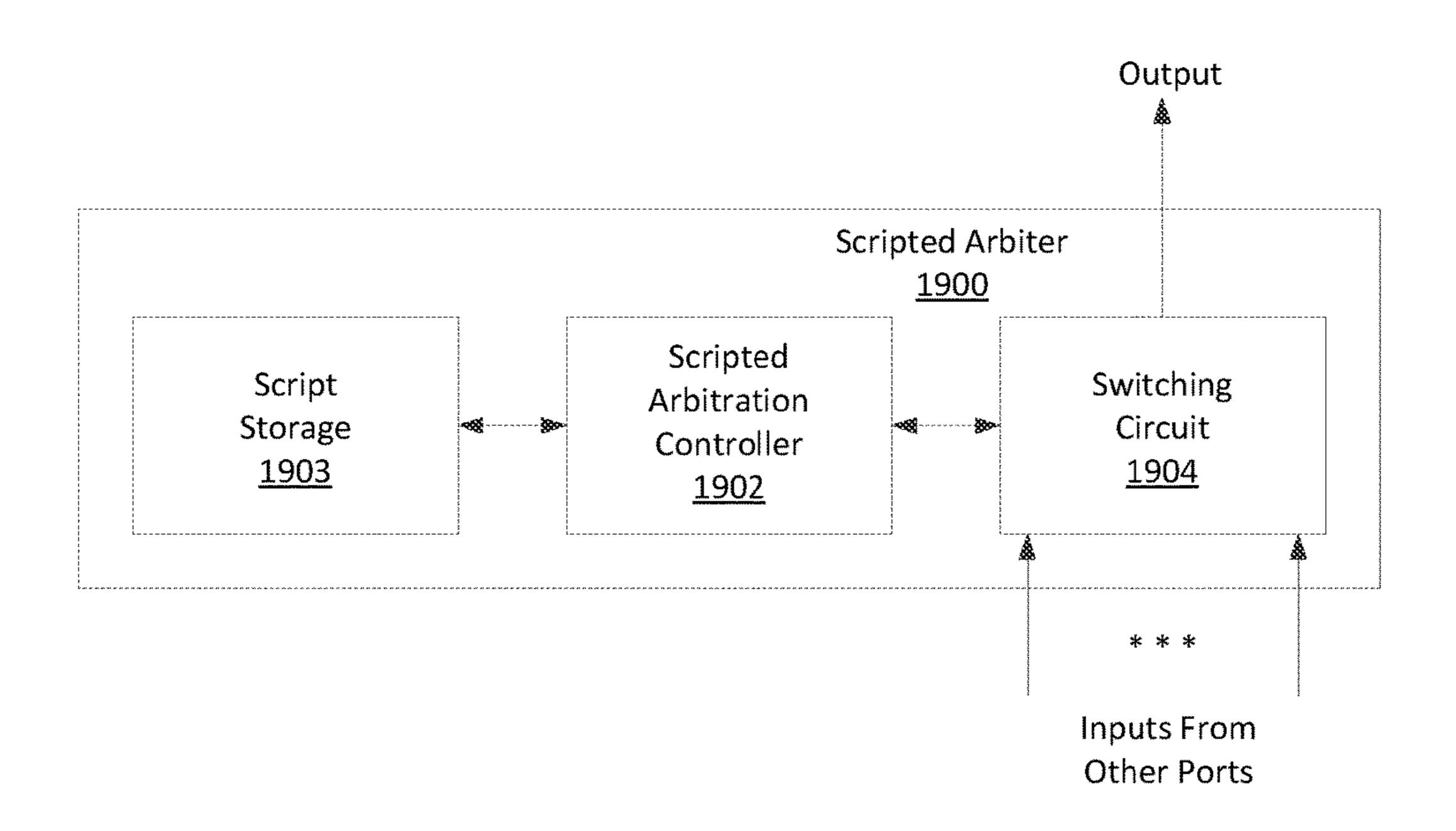

- FIG. 19 is a schematic diagram showing the elements of 45 a scripted arbiter, in accordance with various exemplary embodiments.

- FIG. 20 is a schematic diagram showing a sample script for use by a scripted arbiter, in accordance with one specific exemplary embodiment.

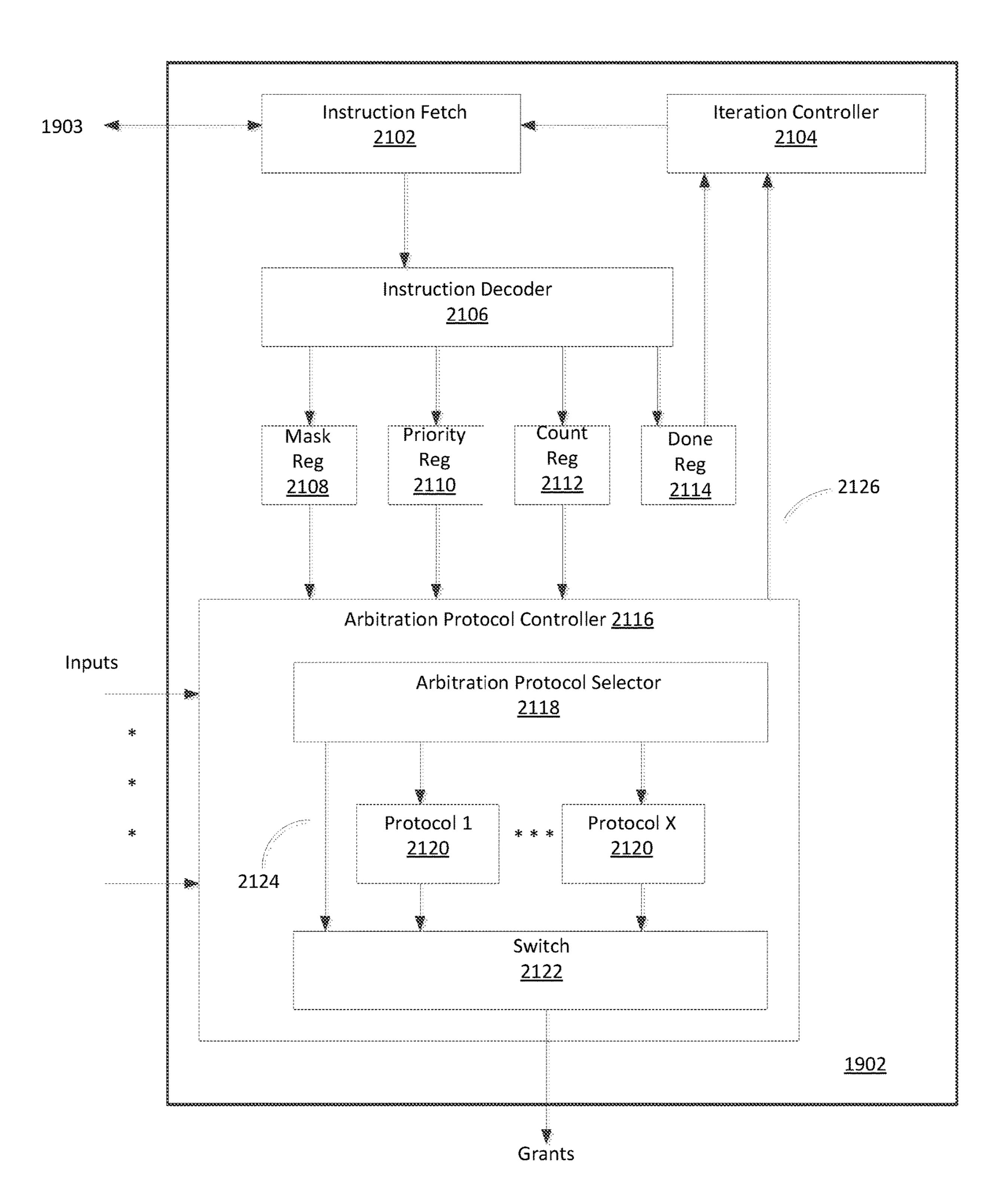

- FIG. 21 is a schematic diagram showing the elements of the scripted arbitration controller, in accordance with various exemplary embodiments.

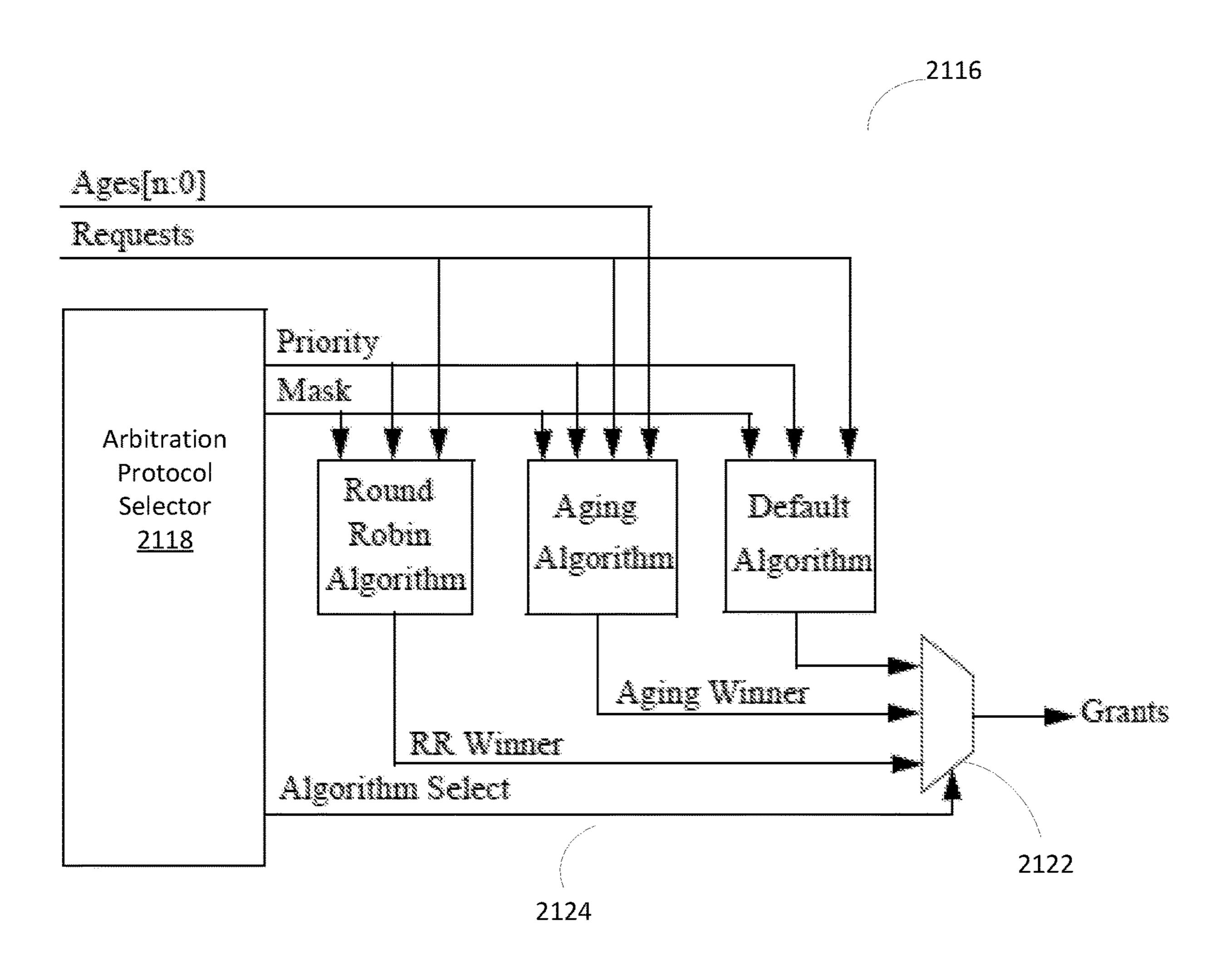

- FIG. **22** is a schematic diagram showing additional details of the arbitration protocol controller **2116**, in accordance 55 with various exemplary embodiments.

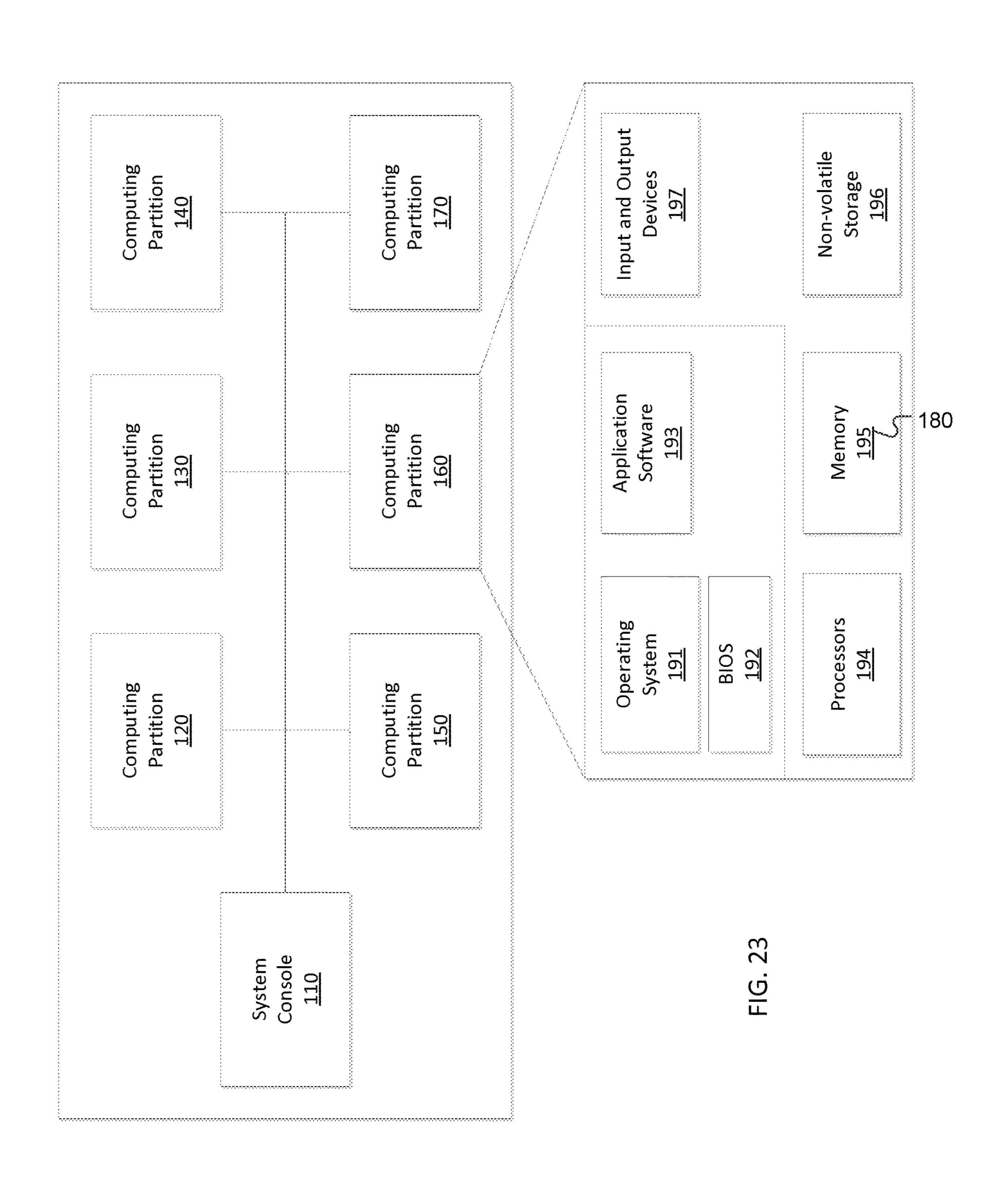

- FIG. 23 schematically shows a logical view of an exemplary high-performance computing system that may be used with illustrative embodiments of the present invention.

# DESCRIPTION OF ILLUSTRATIVE EMBODIMENTS

# Definitions

As used herein, the following terms have the following definitions, unless their context indicates otherwise.

4

A "network" is a communication system in which information can be transmitted unidirectionally and/or bidirectionally between two or more nodes.

A "packet" is a generic name for any unit of information that is processed in a network, switching system, computer, or other system such as for transmitting information or storing information. Unless the context otherwise requires, a packet is not limited to any particular type, format, or protocol. Thus, a packet generally may include, without limitation, a communication protocol message (e.g., a frame, packet, datagram, user datagram, cell, protocol data unit, inter-processor message, etc.), a data representation (e.g., a block, file, object, etc.), or other unit of information including portions thereof. In certain exemplary embodiments, a packet may be a "flit," where a "flit" is a single transmission unit of a communication message (i.e., a communication message may be transmitted as a single flit or may be divided into multiple flits).

A "node" in a network can be any type of device that can send and/or receive packets of information, such as, for example, and without limitation, a computer, a computer processor, a computer memory, a client device, a server device, or a socket, to name but a few. Some networks contain all the same type of nodes (e.g., all the nodes may be computer processors) while other networks contain a mixture of different types of nodes (e.g., some nodes may be computer processors while other nodes may be computer memories).

A "switching system" is an electronic device or group of devices that switches or routes packets of information between two or more nodes in a network. Such switching or routing can be performed based on information contained in the packets of information, such as, for example, a destination address or destination port number.

A "port" is a communication interface of a switching system. Generally speaking, a switching system includes a number of network ports, where each network port is coupled to a corresponding network node. It should be noted that a switching system can be a network node in some network configurations. For example, ports of one switching system can be coupled to ports of other switching systems to establish an internetwork containing multiple switching systems.

A "computer" is an electronic system that includes a memory that stores coded instructions and a processor coupled to the memory and configured to fetch and execute the instructions.

This patent application relates generally to a predictive arbitration circuit for use in arbitrating access by a number of data streams to a shared resource managed by a destination (arbiter), where each data stream is associated with a number of sources competing for the shared resource, and the destination provides access to the shared resource based on the number of sources competing for the shared resource rather than just on the number of data streams. Among other things, this approach can more fairly distribute access to the shared resource among the competing sources.

Various exemplary embodiments are now described with reference to an arbiter in switching system such as a crossbar or matrix switching system, although it should be noted that the present invention is not limited to use in crossbar or matrix switching systems but instead can be used more generally for arbitration in virtually any type of network or switching system including, without limitation, access to any of a wide variety of shared resources such as communication connections, cache memories, or buffers, to name but a few.

FIG. 1 is a schematic diagram showing an exemplary switching system 100 that is configured to switch or route packets between nodes of a network. In this example, the switching system 100 is configured to switch or route packets between nine nodes (for convenience, numbered 1 5 through 9), although it should be noted that switching systems generally can be configured to support any number of nodes. Generally speaking, any node can send packets of information to and receive packets of information from any other node in the network.

FIG. 2 is a schematic diagram showing switching system 100 in the form of a crossbar or matrix switch, in accordance with various exemplary embodiments. Here, the switching system 100 includes nine switching elements (referred to herein as "tiles") numbered 1 through 9. Each tile has a 15 network port (labeled "N") and four fabric ports (labeled "A" through "D"), where each fabric port is coupled to a corresponding fabric port of another tile to form a mesh configuration. With reference to FIG. 1, in this example, the network port of a given tile n would be coupled to Node n. 20 Thus, in this example, the network port of Tile 1 would be coupled to Node 1, the network port of Tile 2 would be coupled to Node 2, and so on. In certain exemplary embodiments, the entire switching system 100 shown in FIG. 2 preferably would be implemented in hardware, e.g., as an 25 Application Specific Integrated Circuit (ASIC) or using one or more Field Programmable Gate Arrays (FPGAs).

In this example, the tiles are interconnected in a matrix configuration through rows and columns, although other types of interconnections are possible in various alternative 30 embodiments. Specifically, in this example, the matrix configuration includes three rows of tiles (i.e., a first row including Tiles 1-3; a second row including Tiles 4-6; and a third row including Tiles 7-9) and three columns of tiles (i.e., a first column including Tiles 1, 4 and 7; a second column 35 including Tiles 2, 5 and 8; and a third column including Tiles 3, 6 and 9). In this example, each tile is coupled to the other tiles in its row and is coupled to the other tiles in its column. For example, Tile 1 is coupled via port A to Tile 2, via port B to Tile 3, via port C to Tile 4, and via port D to Tile 7. In 40 certain exemplary embodiments, using this matrix configuration, switching or routing a packet of information from one network port to another network port can be performed using no more than two "hops," where a "hop" is a transfer from one tile to another tile. For example, to switch or route 45 a packet of information from Node 9 to Node 1, the switching system 100 may be configured for Tile 9 to transmit the packet via its port B to Tile 7, and Tile 7 may be configured to transmit the packet via its port D to Tile 1. Of course, there are other pathways within the switching 50 system 100 to switch or route a packet from Node 9 to Node 1, so different embodiments may employ different switching/routing logic. An exemplary bandwidth on-demand adaptive routing scheme for a crossbar switching system is described in U.S. Pat. No. 9,237,093 entitled BANDWIDTH ON-DEMAND ADAPTIVE ROUTING, which is hereby incorporated herein by reference in its entirety. It also should be noted that various alternative embodiments may include additional pathways within the switching system 100. For example, additional pathways may be included to form a 60 fully interconnected configuration in which every tile is coupled to every other tile; using such a configuration, switching or routing a packet of information from one network port to another network port can be performed using a single hop. The present invention is not limited to 65 any particular type or configuration of switching system, nor to any particular number of interconnected tiles.

6

FIG. 3 is a schematic diagram showing elements of a tile **310**, in accordance with various exemplary embodiments. In this example, each tile 310 includes a network port and a number of fabric ports interconnected via an internal switching system 311. In this example, each port is capable of receiving packets from and transmitting packets to a node external to the tile 310 (in which case the other tiles to which the tile 310 is coupled can be considered nodes with respect to the internal switching system 311). In this example, each port includes a queue circuit (referred to herein as a "queue") for temporarily storing packets received from the external node and an arbitration circuit (referred to herein as an "arbiter") configured to process packets received from the internal switching system 311 to be transmitted to the external node. Typically, the arbiter of a port may receive multiple packets from the internal switching system 311 (e.g., packets from two or more of the other ports), in which case the arbiter determines the order in which the packets are transmitted to the external node using a predetermined arbitration scheme. Some exemplary arbitration circuits and arbitration schemes are discussed below.

FIG. 4 is a schematic diagram of an arbiter 400, in accordance with various exemplary embodiments. From a "black box" perspective, the arbiter 400 receives packets from the internal switching system 311 via various input interfaces and outputs the packets over an output interface. When multiple packets are available to be output, the arbiter 400 determines the order in which the packets are output using a predetermined arbitration scheme.

FIG. 5 is a schematic diagram showing the elements of arbiter 400, in accordance with various exemplary embodiments. Among other things, the arbiter 400 includes an arbitration controller 402 and a switching circuit 404. When multiple packets are available to be output, the arbitration controller 402 determines the order in which the packets are output and controls the switching circuit 404 to output the packets in the determined order. The arbitration controller 402 and the switching circuit 404 can be separate devices or can be a single device that effectively performs both the order determination and the switching. The switching circuit 404 can include a physical switch or a logical switch.

The arbiter 400 can be configured to implement any of a wide variety of arbitration schemes. Two common classes of arbitration schemes include round-robin arbitration and agebased arbitration. In round-robin arbitration, the arbiter 400 typically determines the order for outputting packets on a round-robin basis, e.g., if multiple inputs are competing for bandwidth, then the arbiter 400 may output a number of packets from a first input, then a number of packets from a second input, and so on, stepping through the inputs in a round-robin fashion. In age-based arbitration, the arbiter 400 typically determines the order for outputting packets based on the ages of the packets, e.g., allowing older packets to be output before newer packets. In some embodiments, the arbiter 400 is configured to implement a combination of round-robin and age-based arbitration, although such implementations are often very complex or make significant comprises in order to satisfy timing requirements.

Age-Based Arbitration

In a typical switching system or other shared resource system, age-based arbitration can be implemented by the arbiter 400, specifically by comparing, in real time, the ages of packets available at multiple input interfaces and choosing the packet with the oldest age as the next packet to output. One possible issue with such age-based arbitration is that real-time comparison of packet ages by the arbiter 400 often has an adverse timing and/or latency impact on the

switching system. Another possible issue with such agebased arbitration is that one node with predominantly high packet ages can effectively "lock out" nodes with lower packet ages.

Therefore, in certain exemplary embodiments, the age 5 comparison is moved from the arbiter 400 to the queue circuit, which is configured to assign a high priority (HP) flag to a given packet if the packet age exceeds a predetermined threshold. The HP flag is associated with the packet (e.g., included in a flag field in a packet header or conveyed 10 "out-of-band" separately from the packet) and is used by each arbiter that subsequently processes the packet to give priority to the packet over packets without the HP flag. Among other things, this approach removes the real time age comparison from all the arbitration points and simplifies 15 timing and can improve latency.

In certain exemplary embodiments, the predetermined threshold is based on the ages of packets entering the switching system on the tile network ports (e.g., the average age). FIG. 6 is a schematic diagram showing a switching 20 system 600 with an age-based arbitration circuit, in accordance with various exemplary embodiments. Among other things, the switching system 600 includes a number of tiles **610** (only one tile **610** is shown for convenience) and an age threshold computer 620. The age threshold computer 620 25 receives packet age information from the tile network port queue circuits, computes the predetermined threshold, and distributes the predetermined threshold to all of the file network port queue circuits. In this regard, the tile network port queue circuits are configured to include an age tracker 30 circuit 612 that tracks packet age information for incoming network packets, transmits the packet age information to the age threshold computer 620, receives the predetermined threshold from the age threshold computer **620**, performs the age comparison on incoming network packets, and assigns 35 an HP flag to network packets having a packet age that exceeds the predetermined threshold. The arbiter 400 is configured to output packets based on the existence or absence of an HP flag in packets competing for bandwidth rather than performing an age comparison in real time, 40 thereby greatly simplifying the arbiter. The age threshold computer 620 may compute and distribute a new threshold from time to time, thereby allowing the switching system 600 to dynamically adjust based on the ages of packets.

In some exemplary embodiments, to insure that a given 45 source with high incoming packet ages does not lock out other sources at the arbitration points, the age tracker circuit 612 is further configured to assign HP status to certain incoming packets regardless of actual packet age (e.g., every Nth packet) in order to ensure that all nodes will occasion-50 ally get a chance to flow.

In certain alternative embodiments, the predetermined threshold is a programmable threshold that is distributed to the tile network port queue circuits. In this regard, the age threshold computer 620 can be eliminated from the switching system 600, and the age tracker 612 can be configured to apply the predetermined threshold to incoming network packets without having to track packet age information for incoming network packets and transmit packet age information to an age threshold computer. The programmable 60 threshold may be set once or may be updated from time to time, e.g., based on network congestion information.

FIG. 7 is a logic flow diagram for the age tracker 612, in accordance with various exemplary embodiments. In block 702, the age tracker 612 tracks packet ages. In block 704, the 65 age tracker 612 transmits packet age information to the age threshold computer 620. In block 706, the age tracker 612

8

receives the predetermined threshold from the age threshold computer 620. In block 708, the age tracker 612 receives an incoming packet. In block 710, the age tracker 612 compares the packet age to the predetermined threshold. In block 712, the age tracker 612 assigns an HP flag to the packet if the packet age exceeds the threshold. In block 714, the age tracker 612 optionally assigns an HP flag to the packet regardless of packet age.

Predictive Arbitration

In a typical switching system or other shared resource system, even seemingly equal bandwidth distribution among competing sources at a given arbitration point (e.g., using round-robin arbitration) can lead to unequal bandwidth distribution across the switching system.

For example, with reference to FIG. 2, imagine that Tile 2, Tile 8, and Tile 9 are simultaneously transmitting packets to Tile 1, with the packets from Tile 8 and Tile 9 being transferred through Tile 7 to Tile 1. In this case, Tile 9 port B transmits packets to Tile 7 port B and Tile 8 port A transmit packets to Tile 7 port A, and both the Tile 8 and Tile 9 data streams will need to share the Tile 7 port D connection to Tile 1. With round-robin Arbitration at Tile 7 port D, both Tile 8 and Tile 9 theoretically will get 50% of the bandwidth on the Tile 7 port D connection to Tile 1 port D (i.e., the arbiter at Tile 7 port D may alternate between the two requesting sources). Both Tile 8 and Tile 9 data streams arrive at Tile 1 on the same connection, i.e., Tile 1 port D. The Tile 2 data stream arrives at Tile 1 on port A. The round-robin arbiter on the Tile 1 network port will see two competing sources (i.e., port A and port D) and will divide the bandwidth evenly between those two sources. Thus, port A will get 50% of the Tile 1 network port bandwidth and port D will get 50% of the Tile 1 network port bandwidth. However, since Tile 1 port D is carrying two data streams (i.e., one from Tile 8 and one from Tile 9), the overall bandwidth for the Tile 8 and Tile 9 data streams effectively is reduced to one half of 50% or 25% each.

Therefore, in various exemplary embodiments, the arbiter at each fabric port is configured to provide a count of the number of active sources competing for bandwidth. For example, using the above scenario, the arbiter at Tile 8 port A would provide a count of 1 to Tile 7 to indicate that the packets received from Tile 8 port A are associated with a single source, and the arbiter at Tile 9 port B would provide a count of 1 to Tile 7 to indicate that the packets received from Tile 9 port B are associated with a single source. Therefore, Tile 7 port D would provide divide the bandwidth of Tile 7 port B equally between Tile 8 and Tile 9 and would provide a count of 2 to Tile 1 to indicate that two sources (i.e., Tile 8 and Tile 9) are competing for bandwidth. Furthermore, the arbiter at Tile 2 port A would provide a count of 1 to Tile 1 to indicate that the packets received from Tile 2 port A are associated with a single source. Then, the arbiter on the Tile 1 network port can determine the total number of sources competing for bandwidth (in this example, the total number of sources would be three) and can allocate the Tile 1 network port bandwidth based on the total number of sources. In this above example, there are three sources competing for Tile 1 network port bandwidth (two via Tile 1 port D and one via Tile 1 port A), so the arbiter on the Tile 1 network port generally would be configured to allocate <sup>2</sup>/<sub>3</sub> of the bandwidth to Tile 1 port D and ½ of the bandwidth to Tile 1 port A, for example, by outputting two packets from port D for every one packet output from port A. In this way, Tile 2, Tile 8, and Tile 9 each receives 1/3 of the Tile 1 network port bandwidth. Thus, by providing a count of the number of active sources associated

with a data stream, the arbiter at the receiving tile can distribute bandwidth more fairly among the competing sources.

It should be noted that in certain exemplary embodiments, one or more of the intermediate data streams (i.e., the data streams from Tile 2, Tile 8, and/or Tile 9 in the above example) may include packets from multiple sources. For example, assume that the data stream from Tile 9 to Tile 1 aggregates packets from Tile 6 and Node 9. Here, Tile 9 would split the bandwidth on the connection to Tile 7 10 equally between its two sources and would provide a count of 2 to Tile 7. Tile 7 would then divide the bandwidth on the connection to Tile 1 between three sources (e.g., ½ to Tile 9 and ½ to Tile 8) and would provide a count of 3 to Tile 1. Tile 1 would then divide the Tile 1 network port bandwidth 15 between four sources (e.g., ¾ to Tile 1 port D and ¼ to Tile 1 port A).

In certain exemplary embodiments, if the network port has packets for the outgoing connection to the destination (i.e., over one of the fabric ports), the network port is 20 considered to be associated with a single source for purposes of predictive arbitration as discussed herein, because the external node from which packets are received at the network port generally will not provide a count of the number of sources associated with the data stream.

FIG. 8 is a logic flow diagram for predictive arbitration by the arbiter of a port, in accordance with various exemplary embodiments, in accordance with various exemplary embodiments. In block 802, the arbiter starts with a count of the number of competing sources equal to zero. In block 30 **804**, the arbiter determines which port(s) have packets for the outgoing connection to the destination. In block 806, if the network port has packets for the outgoing connection, then the arbiter increments the count by one, since, in this particular exemplary embodiment, the network port is con- 35 sidered to be associated with a single source for purposes of predictive arbitration. In block 808, for each fabric port having packets for the outgoing connection, the arbiter increments the count by the number of sources associated with the port, which, in this particular exemplary embodi- 40 ment, may be received from the transmitting fabric port. In block 810, the arbiter outputs packets from ports having packets for the outgoing connection based on the number of sources associated with each port relative to the total number of competing sources (e.g., as indicated by the count of the 45 number of competing sources). In block 812, the arbiter preferably provides the number of competing sources to the destination if destination is another switching element (tile).

In order to support predictive arbitration as discussed herein, the queue circuit of each fabric port typically 50 includes special circuitry to receive a count of the number of competing sources from the transmitting fabric port and to provide the count for use by the arbiter associated with the outgoing connection.

FIG. 9 is a logic flow diagram for predictive arbitration by 55 the queue circuit of a port, in accordance with various exemplary embodiments. In block 902, the queue circuit receives a data stream including packets for the outgoing connection to the destination along with a count of the number of sources associated with the packets. In block 904, 60 the queue circuit provides the count for use by the arbiter associated with the outgoing connection, e.g., by storing the count in a computer-readable medium accessible by the arbiter for the outgoing connection.

Shared-Credit Arbitration

In a typical switching system or other shared resource system, shared resources at a destination (e.g., bandwidth on

**10**

a destination communication channel or buffers in a destination memory) can be accessed by multiple entities (referred to herein for convenience as "virtual channels" or "VCs"). Virtual channels can be separate physical channels to the destination (e.g., different source ports accessing a particular destination arbiter in a switching system such as of the type discussed with reference to FIG. 3) or multiple logical channels to the destination over a single physical channel (e.g., different virtual channels for different packet types or data streams). Thus, for example, multiple sources can access shared resources at the destination over separate physical/virtual channels, or a single source can access shared resources at the destination using multiple virtual channels over a single physical channel.

FIG. 16 is a schematic diagram showing multiple virtual channels between a source device and a destination device (arbiter) over a single physical channel, in accordance with various exemplary embodiments. In this example, there are five virtual channels between the source device and the arbiter. The virtual channels can be used for virtually any type of access, such as, for example, separate virtual channels for different applications, sockets, communication protocols, or packet types (e.g., requests vs. responses), to name but a few.

FIG. 11 is a schematic diagram showing some possible arrangements of virtual channels in the context of a tile of a switching system such as of the type shown in FIG. 3, in accordance with various exemplary embodiments. In this example, each port A-D has a separate physical channel to the arbiter of port N. From an arbitration perspective, the separate physical channels from ports A-D to the arbiter of port N may be considered separate virtual channels, with the queue circuits of ports A-D representing separate sources for such virtual channels. Thus, the arbiter of port N can arbitrate accesses by ports A-D to port N (e.g., using round-robin arbitration to cycle through ports A-D). Furthermore, in certain exemplary embodiments, each of the separate physical channels from ports A-D to the arbiter of port N can include multiple logical channels. From an arbitration perspective, the logical channels associated with each physical channel may be considered virtual channels, with the queue circuit of each port representing a common source for the virtual channels associated with that port. Thus, the arbiter of port N can arbitrate accesses by the logical channels of ports A-D to port N (e.g., using a form of "round robin" arbitration to cycle through ports A-D on a round-robin basis and, for each port, providing accesses to the logical channels on a round-robin basis). It also would be possible for a similar arrangement to exist for each of the other arbiters.

Accesses can be divided among the virtual channels in a variety of ways. For example, each virtual channel may be allotted a dedicated amount of resources from a pool of resources and/or multiple virtual channels may share a pool of resources. One way to divide access among the multiple virtual channels is to use a credit-based system in which each virtual channel is allotted a certain amount of credits and the source associated with a particular virtual channel (which manages the credits for the virtual channel) can access the shared resource only when the virtual channel has credits available. Each time a source associated with a particular virtual channel accesses the shared resource, it uses one of the virtual channel's credits, and when the destination frees the resource, the credit is returned by the destination to the source. When the virtual channel has no available credits, the source generally has to wait for resources to be freed and credits returned by the destination.

Some credit-based arbitration schemes include two types of resource pools, namely a dedicated pool for each virtual channel and a shared pool, and further include two types of credits, namely dedicated credits and shared credits that are allotted to the virtual channel s. Credit schemes utilizing 5 dedicated and shared credits often rely on the source(s) being fully aware of the various credit streams available at the destination shared resource. For example, in such credit schemes, the source associated with each virtual channel generally maintains a count of the number of dedicated 10 credits and a count of the number of shared credits available to the virtual channel, and then the source chooses which type of credit to use for a given destination access. This approach can significantly complicate the overall implementation of the source(s).