#### US010736549B1

# (12) United States Patent

Philippine et al.

# (54) ELECTRICALLY-ISOLATED AND MOISTURE-RESISTANT DESIGNS FOR WEARABLE DEVICES

(71) Applicant: Verily Life Sciences LLC, South San

Francisco, CA (US)

(72) Inventors: **Mandy Philippine**, San Carlos, CA

(US); Scott Matula, Alameda, CA (US); Johan Vanderhaegen, Cupertino, CA (US); Louis Jung, Foster City, CA (US); Nivi Arumugam, San Francisco,

CA (US)

(73) Assignee: Verily Life Sciences LLC, South San

Francisco, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 16/224,887

(22) Filed: Dec. 19, 2018

#### Related U.S. Application Data

(63) Continuation of application No. 15/964,227, filed on Apr. 27, 2018, now Pat. No. 10,182,750.

(Continued)

(51) Int. Cl. A61B 5/05

A61B 5/145

(2006.01) (2006.01)

(Continued)

(52) **U.S. Cl.**

CPC ...... A61B 5/14532 (2013.01); A61B 5/1486 (2013.01); A61B 5/14865 (2013.01);

(Continued)

## (10) Patent No.: US 10,736,549 B1

(45) **Date of Patent:** \*A

\*Aug. 11, 2020

#### (58) Field of Classification Search

CPC ...... A61B 2562/166; A61B 5/14532; A61B 5/1486; A61B 5/14865; A61B 5/157; A61B 5/6801

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

6,144,869 A 11/2000 Berner et al. 6,764,446 B2 7/2004 Wolinsky et al. (Continued)

#### OTHER PUBLICATIONS

Analog Devices (2012), Chapter 12: Printed Circuit Board (PCB) Design Issues, [Online]. Available: http://www.analog.com/library/analogdialogue/archives/43-09/edch%2012%20pc%20issues.pdf.

(Continued)

Primary Examiner — Yuriy Semenenko

(74) Attorney, Agent, or Firm — Kilpatrick Townsend & Stockton LLP

### (57) ABSTRACT

An example continuous glucose monitor includes a printed circuit board ("PCB") having first and second outer layers and an inner layer; a semiconductor package having a plurality of pins coupled to the first outer layer of the PCB; an electrical contact formed on the second outer layer of the PCB; a trace having a first portion disposed on the first outer layer, a second portion disposed on the inner layer, and a third portion disposed on the second outer layer, the trace having a first end coupled to a first pin of the plurality of pins and a second end coupled to the electrical contact; and an encapsulant disposed around a perimeter of the semiconductor package, the encapsulant covering the plurality of pins, the first portion of the sensor trace, the third portion of the sensor trace, wherein an upper surface of the semiconductor package remains exposed.

#### 13 Claims, 6 Drawing Sheets

# US 10,736,549 B1

Page 2

| Related U.S. Application Data |                                                                        |                        | 2005/0016844                                                     | A1*        | 1/2005 | Burke G01N 33/558<br>204/403.01 |

|-------------------------------|------------------------------------------------------------------------|------------------------|------------------------------------------------------------------|------------|--------|---------------------------------|

| (60                           | Provisional application No. 62/490,970, filed on Apr. 27, 2017.        |                        | 2007/0149897                                                     | <b>A</b> 1 | 6/2007 | Ghesquiere et al.               |

|                               |                                                                        |                        |                                                                  |            |        | Marcoux C07F 5/025              |

| (5                            | 1) Int. Cl.                                                            |                        | 2012/0092812                                                     | A1         | 4/2012 | Lewis et al.                    |

|                               | $A61B \ 5/00$ (2006.01)                                                |                        |                                                                  |            |        | Birtwhistle G06F 19/3481        |

|                               | $A61B \ 5/1486 $ (2006.01)                                             |                        |                                                                  |            |        | 726/26                          |

|                               | $A61B \ 5/157 \ (2006.01)$                                             |                        | 2014/0008110                                                     | A1*        | 1/2014 | Arnold H05K 3/462               |

|                               | $H05K\ 3/28$ (2006.01)                                                 |                        |                                                                  |            |        | 174/257                         |

| (5)                           | 2) U.S. Cl.                                                            | /1D 5//001             | 2015/0004756                                                     | A1*        | 1/2015 | Chi H01L 23/49816<br>438/127    |

|                               | CPC                                                                    |                        | 2015/0220109                                                     | A1*        | 8/2015 | von Badinski G01P 15/00         |

|                               |                                                                        |                        |                                                                  |            |        | 340/539.12                      |

|                               | 2302/100                                                               | ) (2013.01)            | 2016/0013148                                                     | A1*        | 1/2016 | Lin H01L 23/552<br>257/773      |

| (5)                           | (56) References Cited                                                  |                        | 2017/0188898                                                     | <b>A</b> 1 | 7/2017 | Jina et al.                     |

|                               | U.S. PATENT DOCUMENTS                                                  |                        | 2018/0075200                                                     |            |        | Davis et al.                    |

|                               |                                                                        |                        | 2018/0120892                                                     |            |        | von Badinski G06F 3/1423        |

|                               | 0 465 405 DOW 6/0040 TT 11                                             | 64D 5/4 4500           | 2018/0228416                                                     |            | 8/2018 |                                 |

|                               | 8,465,425 B2 * 6/2013 Heller Ac                                        | 61B 5/14532<br>600/365 | 2010, 0220 110                                                   | 1 1 1      | 0,2010 |                                 |

|                               | 8,579,853 B2 11/2013 Reggiardo et al.                                  |                        |                                                                  | OT.        | HER PU | BLICATIONS                      |

|                               | 9,243,276 B2 * 1/2016 Malecha G0                                       |                        |                                                                  |            |        |                                 |

|                               | 9,865,575 B2 * 1/2018 Chi                                              |                        | U.S. Appl. No. 15/964,227, "Notice of Allowance", dated Sep. 26, |            |        |                                 |

|                               | 9,980,669 B2 5/2018 Cole et al.<br>10,182,750 B1* 1/2019 Philippine Ac | 61B 5/1/1532           | 2018, 11 pages.                                                  |            |        |                                 |

| 2                             | 10,182,750 B1 * 1/2019 Philippine Ac<br>004/0167801 A1 * 8/2004 Say Ac |                        |                                                                  |            |        |                                 |

|                               | oo horoot iii o, 200 i buy iii                                         | 705/2                  | * cited by exa                                                   | miner      | •      |                                 |

|                               |                                                                        |                        |                                                                  |            |        |                                 |

FIG. 1H

FIG. 2

#### ELECTRICALLY-ISOLATED AND MOISTURE-RESISTANT DESIGNS FOR WEARABLE DEVICES

#### CROSS-REFERENCE TO RELATED APPLICATIONS

The present application is a continuation of U.S. patent application Ser. No. 15/964,227, filed Apr. 27, 2018, entitled "Electrically-Isolated And Moisture-Resistant Designs For 10 Wearable Devices," which claims priority to Provisional Application No. 62/490,970, filed on Apr. 27, 2017, and entitled "Electrically-Isolated And Moisture-Resistant are hereby incorporated by reference herein.

#### **FIELD**

The present application generally relates to wearable 20 devices, but more specifically relates to electrically-isolated and moisture-resistant designs for wearable devices.

#### BACKGROUND

A person with diabetes generally monitors her blood glucose levels so that she can properly administer insulin at the correct times and in the correct doses. To do so, she may periodically prick a finger to draw a small quantity of blood. The blood may be inserted into a blood glucose sensing 30 device, which measures blood glucose level and reports the value to the user. This form of blood glucose testing is frequently referred to as a "finger prick" test. An alternative to the finger prick test is to wear a continuous glucose monitor ("CGM"), which is applied to the user's body, often 35 on the user's abdomen. The CGM includes a sensor wire that is inserted into the wearer's skin and obtains glucose levels from the wearer's interstitial fluid. The CGM is able to then communicate the glucose level to the user via an interface device, such as the user's smartphone or an insulin pump.

#### **SUMMARY**

Various examples are described for electrically-isolated and moisture-resistant designs for wearable devices. One 45 example wearable device includes a printed circuit board ("PCB") having first and second outer layers and an inner layer, the inner layer disposed between the first and second outer layers; a semiconductor package having four corner portions and a plurality of pins, the semiconductor package 50 coupled to the first outer layer of the PCB via the plurality of pins; an electrical ground plane formed on the PCB and coupled to at least one pin at each of a first, second, and third of the four corner portions, and not coupled to any pins at a fourth corner portion; an electrical contact for a sensor wire 55 formed on the second outer layer of the PCB; a sensor trace having a first portion disposed on the first outer layer, a second portion disposed on the inner layer, and a third portion disposed on the second outer layer, the sensor trace having a first end coupled to a first pin of the plurality of pins 60 and a second end coupled to the electrical contact for the sensor wire, the first pin at the fourth corner of the semiconductor package; a plurality of guard rings disposed on the PCB, each guard ring encircling one of the portions of the sensor trace; and an encapsulant disposed around a 65 perimeter of the semiconductor package, the encapsulant covering (i) the plurality of pins, (ii) the first portion of the

sensor trace, (iii) the third portion of the sensor trace, wherein an upper surface of the semiconductor package remains exposed.

Another example example wearable device includes a <sup>5</sup> printed circuit board ("PCB") having first and second outer layers and an inner layer, the inner layer disposed between the first and second outer layers; a semiconductor package having four corner portions and a plurality of pins, the semiconductor package coupled to the first outer layer of the PCB via the plurality of pins; an electrical contact for a sensor wire formed on the second outer layer of the PCB; a sensor trace having a first portion disposed on the first outer layer, a second portion disposed on the inner layer, and a Designs For Wearable Devices," the entireties of each which 15 third portion disposed on the second outer layer, the sensor trace having a first end coupled to a first pin of the plurality of pins and a second end coupled to the electrical contact for the sensor wire, the first pin at a fourth corner portion of the semiconductor package; and an encapsulant disposed around a perimeter of the semiconductor package, the encapsulant covering (i) the plurality of pins, (ii) the first portion of the sensor trace, (iii) the third portion of the sensor trace, wherein an upper surface of the semiconductor package remains exposed.

> One example for providing a wearable biosensor includes forming a wearable biosensor electronics portion by: providing a plurality of PCB layers; affixing a semiconductor package to a first layer of the PCB layers, the semiconductor package having a plurality of pins; applying a first electrical trace to the first layer, the first electrical trace having a first end coupled to a pin of the semiconductor package and a second end coupled to a first via formed in the first layer; applying a guard ring to the first PCB layer, the guard rings encircling the first electrical trace, the pin, and the first via; applying a second electrical trace to a second PCB layer of the PCB layers, the second electrical trace having a first end coupled to a sensor wire and a second end coupled to a second via formed in the second PCB layer; applying a third electrical trace on a third PCB layer of the PCB layers, the third electrical trace having a first end coupled to the first via and a second end coupled to the second via; bonding the third PCB layer between the first and second PCB layers; affixing a sensor wire to a second PCB layer, the sensor wire having a first portion extending away from the second PCB layer; applying a first encapsulant over the pins of the semiconductor package and the first electrical trace, and not applying the encapsulant to an upper surface of the semiconductor package; and applying the encapsulant over the second electrical trace; disposing the wearable biosensor electronics portion in a first portion of a housing, the first portion defining a hole to receive the first portion of the sensor wire; sealing a second portion of the housing to the first portion of the housing to enclose the wearable biosensor electronics portion; and sealing the hole using the encapsulant.

> These illustrative examples are mentioned not to limit or define the scope of this disclosure, but rather to provide examples to aid understanding thereof. Illustrative examples are discussed in the Detailed Description, which provides further description. Advantages offered by various examples may be further understood by examining this specification.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, which are incorporated into and constitute a part of this specification, illustrate one or more certain examples and, together with the description of

the example, serve to explain the principles and implementations of the certain examples.

FIGS. 1A-1G show views of an example electronics portion of a CGM;

FIG. 1H-1I show views of an example housing for a 5 CGM;

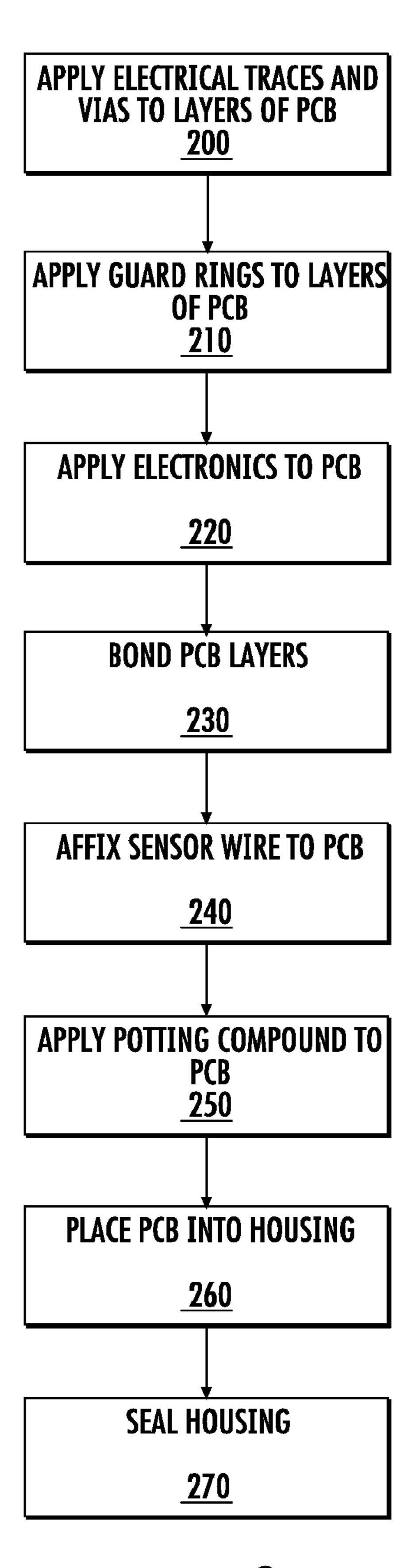

FIG. 2 shows an example method of providing a moisture-resistant CGM.

#### DETAILED DESCRIPTION

Examples are described herein in the context of electrically-isolated and moisture-resistant designs for wearable devices. Those of ordinary skill in the art will realize that the following description is illustrative only and is not intended to be in any way limiting. Reference will now be made in detail to implementations of examples as illustrated in the accompanying drawings. The same reference indicators will be used throughout the drawings and the following description to refer to the same or like items.

In the interest of clarity, not all of the routine features of the examples described herein are shown and described. It will, of course, be appreciated that in the development of any such actual implementation, numerous implementation-specific decisions must be made in order to achieve the developer's specific goals, such as compliance with application-and business-related constraints, and that these specific goals will vary from one implementation to another and from one developer to another.

According to one illustrative example, a CGM is designed 30 and manufactured to provide moisture resistance to the CGM's electronics and to provide electrical isolation for the CGM's sensor lead. In this example, the CGM is designed to have a low profile to provide a more comfortable, less bulky CGM to wear. Thus, the CGM is designed to have a 35 height of approximately 9 millimeters ("mm"), excluding the length of sensor wire that extends below the lower surface of the CGM's housing.

In addition, because the CGM is worn on the wearer's body for a number of days, and through the wearer's typical 40 routine, it may be exposed to a wide variety of environments, including immersion in water, soap, sweat, or other moisture sources. Thus, maintaining moisture protection for the electronics within the CGM is of particular importance, while also allowing for the low profile of the CGM. Further, 45 because the sensor electronics of the CGM are highly sensitive to extraneous electrical signals, preventing shorts due to moisture, as well as preventing leakage currents from other electronic components or traces is critical to the proper functioning of the device, properly isolating the sensor 50 electronics, while maintaining a low profile form factor, is another key feature of the design.

As mentioned above, this example CGM has a low-profile housing that defines the overall dimensions of the CGM, excluding the external portion of the sensor wire. The 55 housing itself defines an internal cavity in which the CGM's electronics are positioned. The electronics include an application-specific integrated circuit ("ASIC") package having a rectangular footprint, a wireless transceiver, and a sensor wire, all of which are affixed to a multi-layer printed circuit 60 board ("PCB"). The ASIC package encases custom circuitry to receive sensor signals, determine glucose levels, and provide glucose level data to the wireless transceiver. In addition, the sensor wire is physically and electrically connected to the PCB and is connected via an electrical trace to 65 the ASIC package, thereby enabling communication from the sensor to the ASIC.

4

To protect against moisture shorting pins on the ASIC package or the wireless transceiver, or from shorting other electrical connections or leads, a potting compound is applied around the perimeter of the ASIC package and wireless transceiver and overtop of the ASIC package's and transceiver package's electrical contacts, as well as the electrical trace 130a-c running from the sensor wire 140 to the ASIC package 120; however, potting compound is not applied to other portions of the CGM electronics. For 10 example, the potting compound is not applied to the upper surfaces of the semiconductor packages or other taller electronics features coupled to the PCB, as such a placement would increase the overall height of the device. By only applying the potting compound to these portions of the CGM electronics, the total amount of volume occupied by the CGM electronics and potting compound may be reduced, thereby enabling a CGM with the desired height of less than approximately 9 mm. Such a height may be desirable to allow the CGM to remain flush against the 20 wearer's skin and avoid unintentional contact with the wearer's limbs, clothing, or other objects.

In addition to providing moisture resistance via the potting compound, the sensor wire, which extends below a bottom surface of the CGM, is coupled to the lowest layer of the PCB, and coupled to an electrical trace, which runs from the lowest layer of the PCB to a via, where the electrical trace is routed onto an interior layer of the PCB, where it is protected from moisture by adjoining layers of the PCB. The via in this example is also filled with a potting compound to seal the via 132b running from the lowest layer to the interior layer. The electrical trace runs from the via 132b to a second via 132a located in close proximity to the contact pin on the ASIC package that accepts signals from the sensor, at which location the electrical trace traverses the second via 132a, also filled with a potting compound, to the upper surface of the PCB and connects to the ASIC package.

In addition to providing moisture resistance, electrical features are included to electrically-isolate the sensor wire from other portions of the CGM electronics to mitigate leakage current to the sensor wire, which may introduce error into signals provided by the sensor wire. The electrical features include a modified ground plane for the ASIC package and a guard ring encircling the electrical trace coupling the sensor wire to the ASIC package and the sensor wire electrical contacts themselves. In the case of a CGM, the signal provided by the sensor wire 140 is extremely small and highly susceptible to interference from leakage current. As will be discussed in more detail below, the sensor wire 140 may only provide a few nanoamps of current to indicate a glucose level. Thus, leakage current in the nanoamp range or greater can entirely overwhelm the signal provided by the sensor 140 itself.

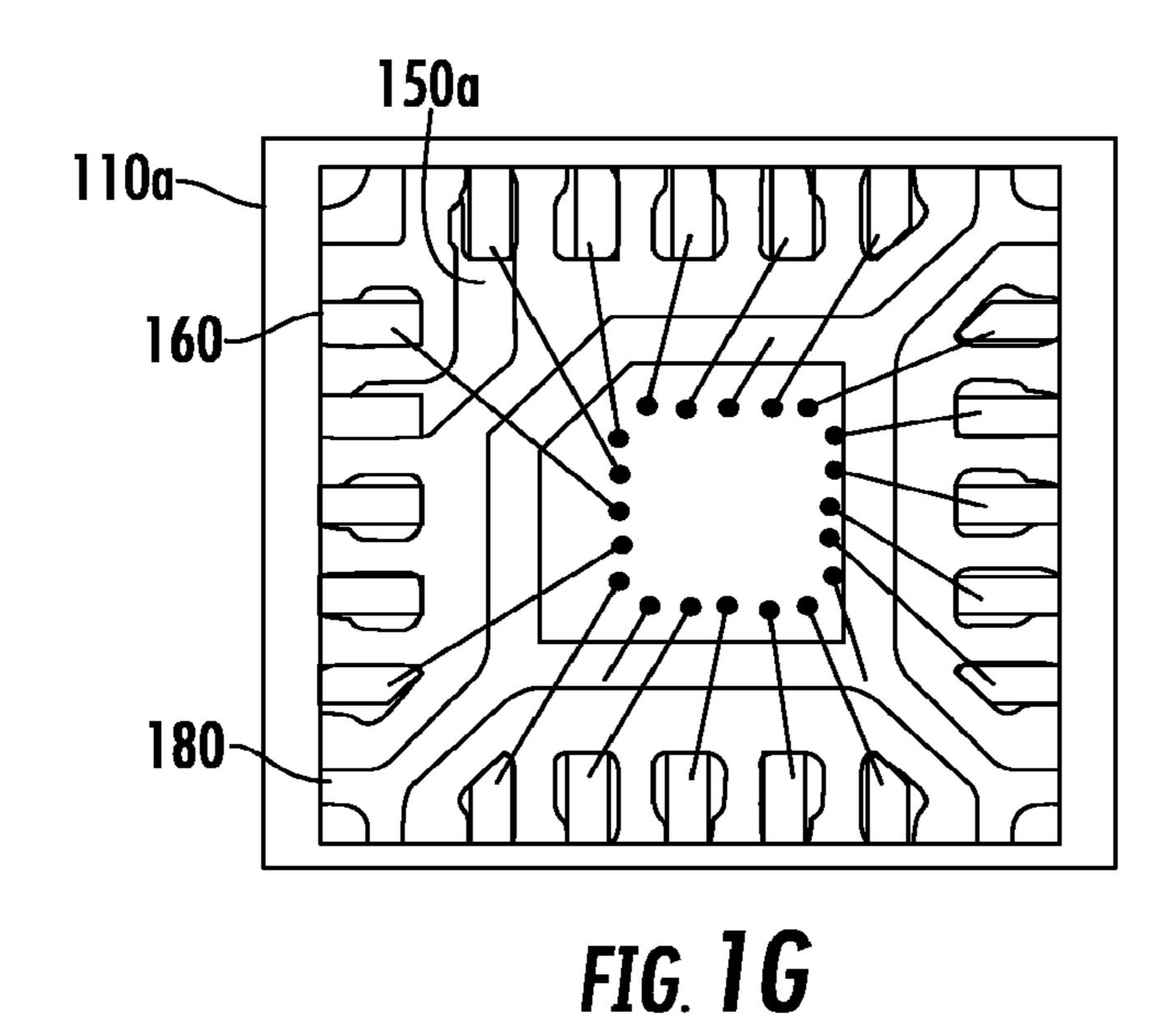

The ground plane 180 connections for the ASIC package are provided at three corner portions of the ASIC package, but not at the fourth. In addition, the ground plane trace on the PCB associated with the ASIC package 120 is shaped to provide a gap in the ground plane 180 adjacent to the fourth corner portion, where the sensor wire electrical trace 130a connects to the ASIC package 120. By providing space for a portion of the guard ring 150a, the guard ring 150a can entirely encircle and electrically isolate the electrical trace 130a from the ground plane 180 or other electrical traces or sources of electrical leakage on the PCB. The guard ring 150a also encircles the portion of the sensor wire electrical trace 130a on the upper layer 110a of the PCB. The portion of the sensor wire electrical trace 130b running along the interior layer 110b of the PCB is also encircled by a guard

ring 150b, and the portion of the sensor wire electrical trace 130c running along the lowest layer 110n of the PCB to the sensor wire connection itself is encircled by a guard ring 150c. Thus, the entire lengths of the different portions of the sensor wire electrical trace 130a-c are electrically isolated 5 by their respective guard rings.

Such features enable a low-profile CGM, while providing sufficient moisture resistance and an electrically-isolated sensor to reduce error in sensor readings. This illustrative example is given to introduce the reader to the general 10 subject matter discussed herein and the disclosure is not limited to this example. The following sections describe various additional non-limiting examples and examples of electrically-isolated and moisture-resistant designs for wearable devices.

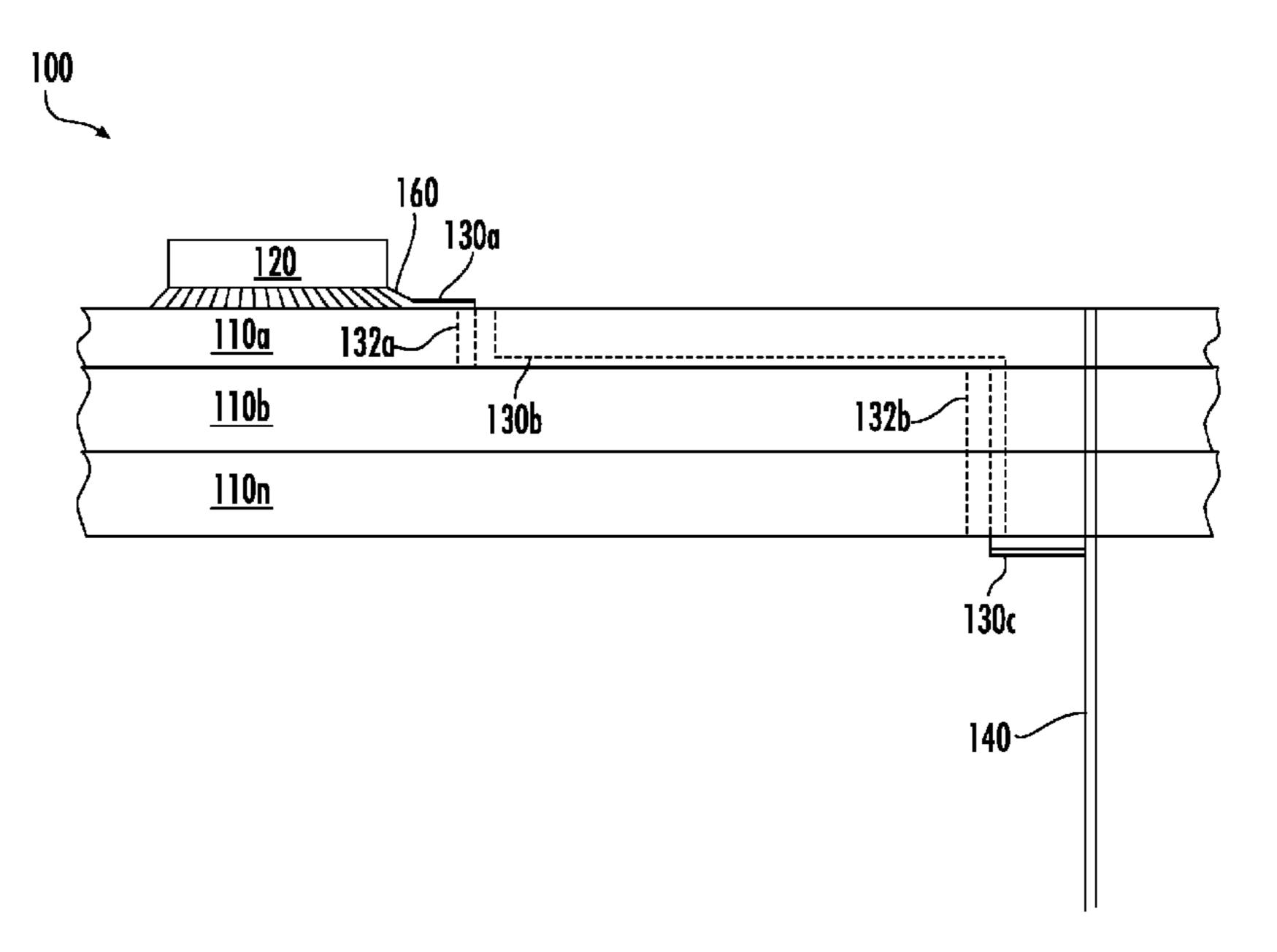

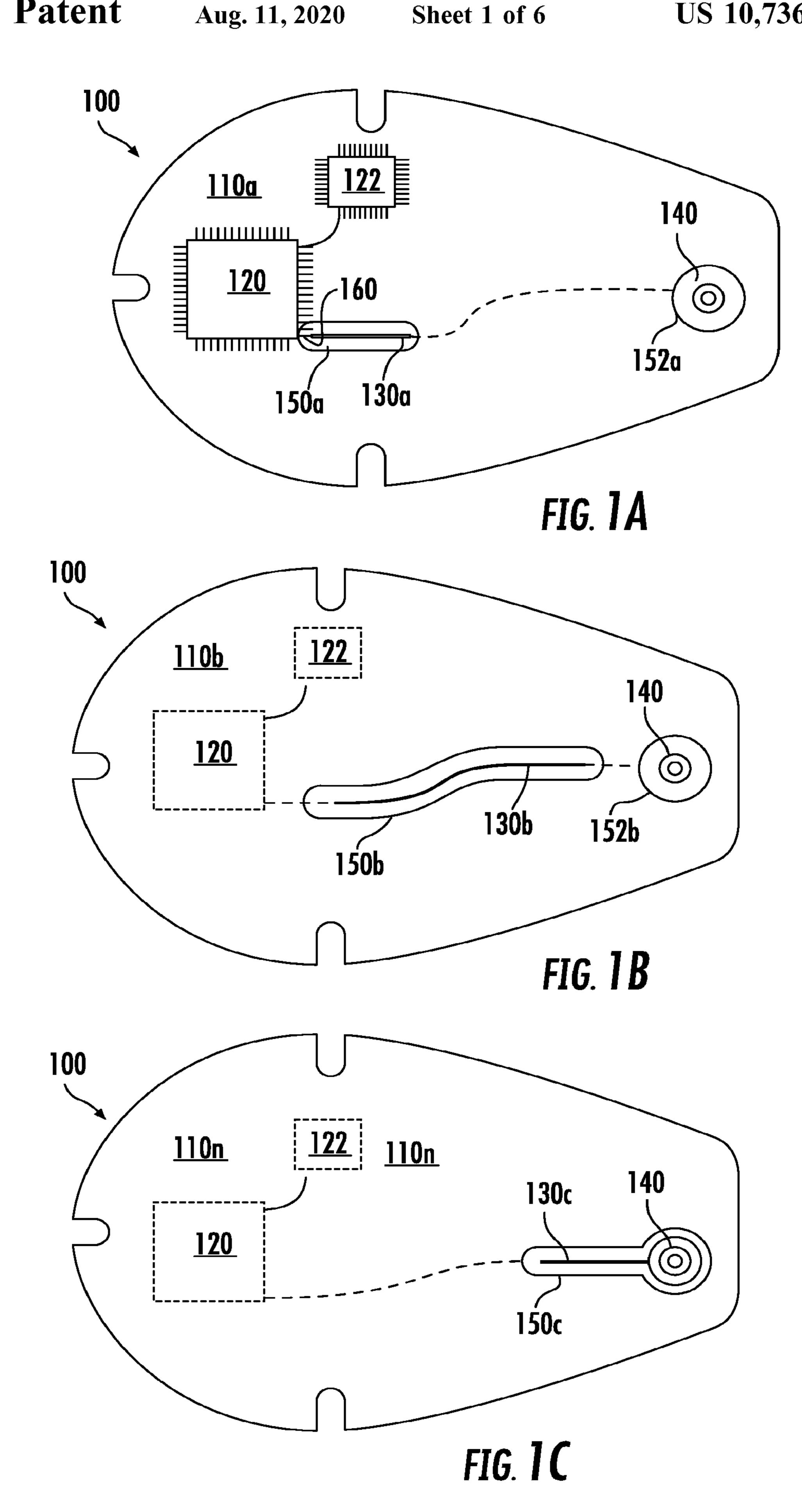

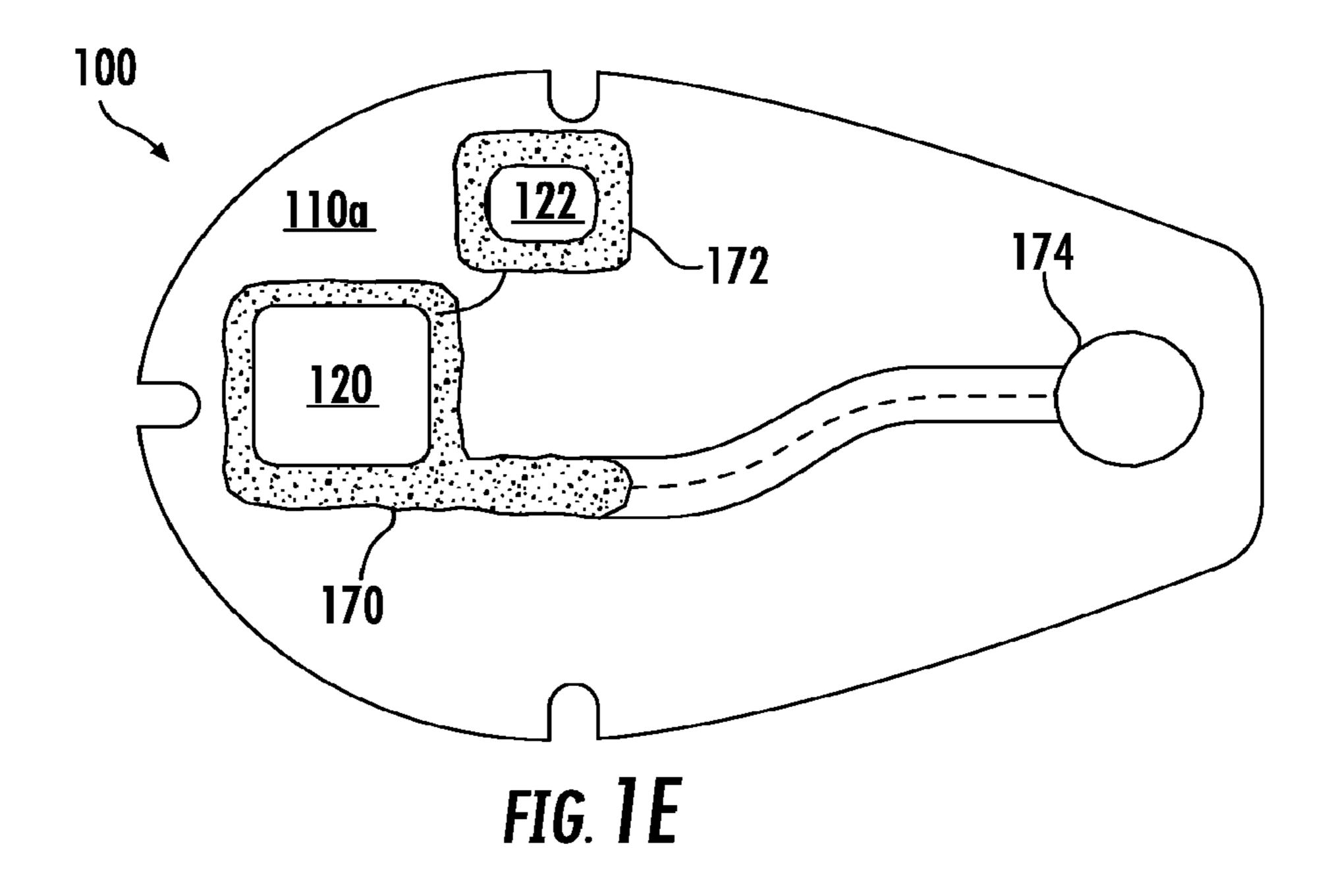

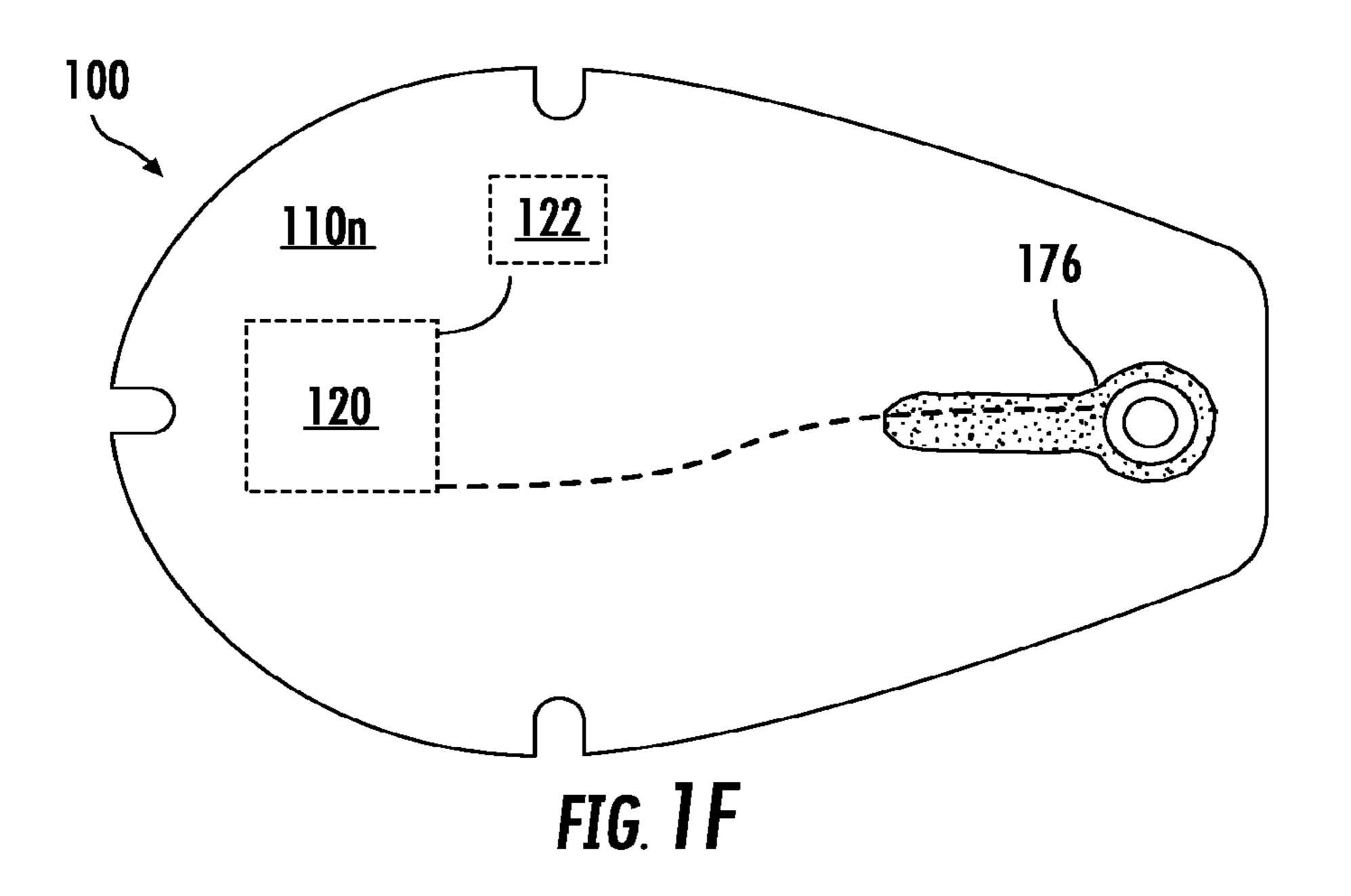

Referring now to FIGS. 1A-1F, FIGS. 1A-D show different views of an electronics portion of an example wearable device 100 having a moisture-resistant design, while FIGS. 1E-F shows the view of FIGS. 1A and 1C with a potting compound that is not shown in FIGS. 1A and 1C. In this 20 example, the wearable device 100 is a CGM (also referred to as CGM 100), but may be any other suitable wearable device. For example, other wearable devices may include biosensors, such as blood oxygen sensors, electrocardiogram sensors, blood flow or pressure sensors, etc. In this 25 example, the example CGM 100 is designed to have a low profile, e.g., less than approximately 9 mm. Thus, the height of electronics features constrains ways by which to prevent moisture damage to the electronics within the electronics portion of the CGM 100.

The electronics portion of the CGM 100 in this example includes a multi-layer PCB 110a-n to which are coupled a first semiconductor package 120; a second semiconductor package 122; a sensor wire 140; a sensor wire electrical trace 130a-c; and several guard rings 150a-c, 152a-b. It should be 35 appreciated that other components may be included as well, or other electrical traces or electronic components to enable communications between different components or to provide other functionality. A multi-layer PCB is employed in some examples as interior layers of the PCB can provide 40 moisture protection to electrical components, such as electrical traces, that are laid on such interior layers. For example, an electrical trace connecting a sensor wire to a semiconductor package that runs along an interior layer of the PCB may be protected from moisture by the other layers 45 of the PCB. However, a multi-layer PCB is not required according to different examples.

FIG. 1A shows a top or upper layer 110a of the PCB and the components attached to it, as well as hashed lines indicating other identified components, which are present or 50 coupled to other layers of the PCB. FIG. 1B shows an interior layer 110b of the PCB, while FIG. 1C shows the bottom or lowest layer 110n of the PCB. Layer 110n is referred to as the lowest or bottom layer because it is the layer that will be closest to a wearer's skin as the sensor wire 55 last contacts the PCB at the lowest layer before extending away from the bottom layer and out of the CGM's housing such that it can be inserted into a wearer's skin. While in this example, the PCB has three layers, any suitable number of N layers may be employed. In this example, to reduce the 60 overall height of the CGM 100, each layer 110a-n of the PCB has a thickness of approximately 0.020 inches (or 20 mils); however, PCB layers of any suitable thickness may be employed.

As can be seen in FIG. 1A, the semiconductor packages 65 120, 122 have a substantially rectangular shape with multiple pins that are coupled to the PCB. No requirement is

6

imposed on the shape or number of pins of any semiconductor package; thus, other shapes or sizes may be employed as well. In this example, the package refers to the physical package within which integrated circuits may be encased, and the specifics of the integrated circuits may vary according to application. In this example, the first semiconductor package 120 has an integrated circuit, which is an ASIC that includes circuitry to receive signals from the sensor wire, determine a glucose level based on those signals, and to transmit information to the wireless transceiver. The second semiconductor package 122 also has an integrated circuit, which is a wireless transceiver in this example.

In addition to the semiconductor packages 120, 122, a sensor wire 140 is coupled to the PCB and is electrically connected to the ASIC 120 via an electrical trace 130a-c. As discussed above, by running a significant portion of the electrical trace 130b along an interior layer 110b of the PCB, most of the length of the sensor wire electrical trace 130a-c can be shielded from moisture by the exterior layers 110a, 110n of the PCB.

Referring to FIG. 1D, the sensor wire 140 is coupled to each of the layers 110a-n of the PCB and extends away from the lowest layer 110n of the PCB, thereby enabling the sensor wire 140 to be inserted into a wearer's skin. And while in this example, the sensor wire 140 extends through each layer 110a-n of the PCB, other configurations may be employed in some examples. For example, the sensor wire 140 may extend through only some, or even one, of the PCB layers 110a-n. In some examples, a portion of the sensor wire 140 may be soldered, grasped, or otherwise coupled to the lowest layer 110n of the PCB and another portion may bend and extend away from that layer 110n, e.g., at a 90 degree angle.

In this example, the sensor wire 140 has two electrodes that are inserted into a wearer's skin to expose the electrodes to the wearer's interstitial fluid, from which glucose readings may be taken. In this example, the two electrodes are (1) a platinum or platinum-coated wire, and (2) a silver/silver-chloride (Ag/AgCl) material that covers a part of the wire. One end of the sensor wire 140, including a portion of the Ag/AgCl material, extends downward from the bottom, or lowest layer 110n, of the PCB and may be inserted into the wearer's skin, while the other end of the sensor wire 140 is attached to the PCB.

In this example, a portion of the sensor wire **140** that is inserted into the wearer's skin also has a glucose oxidase ("GOX") coating that will react to glucose present within the wearer's interstitial fluid. When the sensor wire **140** is inserted into the wearer's skin, the GOX reacts with glucose, which creates reaction products, such as hydrogen peroxide. When a voltage is applied to the electrodes, an electrical current is generated based on the amount of these reaction products generated by the glucose/GOX reaction. The electrical current is then transmitted to the ASIC within the first semiconductor package **120** via the electrical trace **130***a-c*. The ASIC determines the amount of glucose that is present based on the strength of the current.

Because the example CGM 100 may be worn by a wearer for an extended period of time, such as days or weeks, it will likely be exposed to a variety of different environments, including water or high humidity environments as a result of the user bathing, swimming, etc. To help prevent damage to the CGM electronics, they are entirely disposed within a sealed housing. In addition, the electronics are protected from moisture by other aspects of the design, including

routing electrical traces through interior portions of the PCB and using a potting compound on portions of the electronics and electrical traces.

For example, as can be seen in FIG. 1D, an electrical trace 130c couples to the sensor wire 140 on the lowest layer 110n = 5of the PCB, traverses a short distance, e.g., 1-5 mm, before traversing a via 132b to an interior layer 110b of the PCB. The electrical trace 130b runs along the interior layer 110bto a second via 132a, which it to the top layer 110a of the PCB and couples to a pin 160 on the ASIC package 120. By 10 routing the electrical trace 130b along an interior layer 110bof the PCB, that portion 130b of the electrical trace, plus the portions traversing the vias 132a-b, are protected from moisture that may enter the housing. Because the layers **110***a-n* of the PCB are bonded together and thus do not 15 admit water between them. In addition, the vias 132a-b may be sealed when they are defined within the PCB, or the vias 132a-b may be filled with a potting compound to prevent ingress of moisture. It should be appreciated that while the example electrical trace 130a-c is illustrated as coupling the 20 sensor wire 140 to the ASIC semiconductor package 120 without any intervening electronic components, in some examples, other electronic components may be coupled to the electrical trace 120a-c. Such as in one example, a resistor is coupled between the electrical trace 130a and the ASIC 25 semiconductor package 120, which may provide electrical protection to electronics within the semiconductor package.

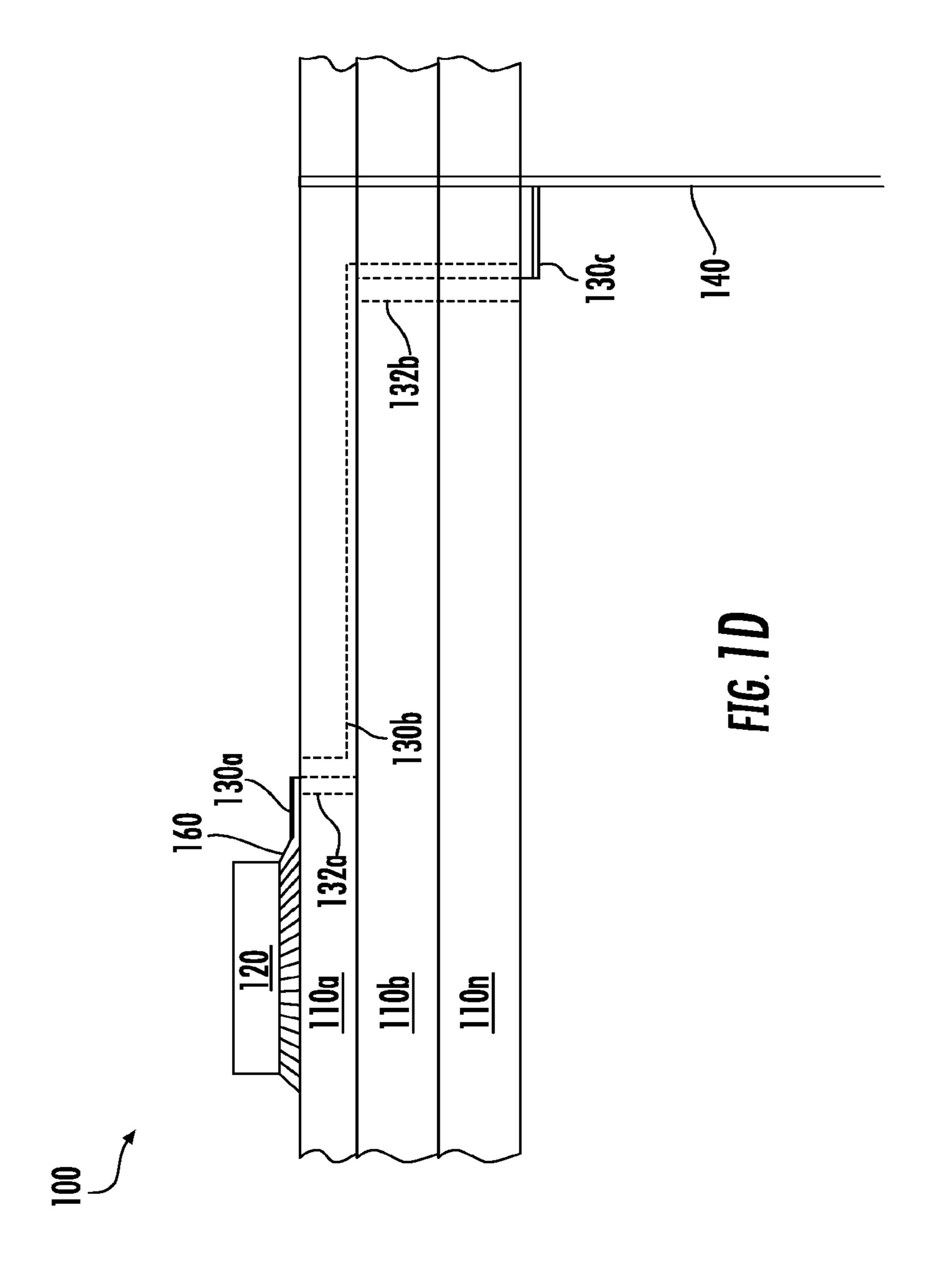

Referring now to FIGS. 1E-1F, portions of the electronics of FIGS. 1A-1D are shown protected by an encapsulant, such as a potting compound 170-176. Suitable encapsulants 30 may be applied as a liquid or a gel during a manufacturing process, and may be cured at an elevated temperature. Such encapsulants should have a glass transition temperature above expected operational temperatures, including other manufacturing temperatures, e.g., related to forming a housing or welding portions of a housing together. In addition, the encapsulant should not be moisture sensitive and high electrical resistivity, e.g., greater than 10<sup>13</sup> ohms per centimeter.

In this example, in addition to routing the electrical trace 40 130b along an interior layer 110b of the PCB, the portions of the electrical trace 130a and sensor wire 140 that are exposed on the top layer 110a, and the electrical trace 130con the lowest layer 110-*n* are encased by a potting compound 170-176, which prevents moisture from reaching the other- 45 wise exposed electrical traces 130a,c on the PCB. In examples where additional electronic components are provided along the route of the electrical trace 130a-c, e.g., the resistor discussed above, such components may also be encased in the potting compound 170 to ensure the exposed 50 conductive path between the sensor wire 140 and the ASIC semiconductor package 120 is entirely encased by the potting compound 170, including the guard rings 150a-c, **152***a-b*, which are discussed in more detail below. In addition, in this example, the electrical traces 130a, c are first 55 covered by a conformal coating, which may provide further moisture protection, and subsequently encased in a potting compound 170, 176; however, in some examples, a conformal coating is not employed.

It should be noted in this example that the sensor wire **140** 60 extends away from the lowest layer **110**n of the PCB to enable it to be inserted into a wearer's skin. Thus, a portion of the sensor wire **140** will also extend outside of the CGM's housing. Thus, the potting material **176** on the lowest layer is applied both to protect the exposed portions of the sensor 65 wire **140** within the housing, but also to seal a hole in the housing through which the sensor wire **140** extends. Thus,

8

the potting compound both encapsulates portions of the internal electronics of the CGM 100 but also serves as physical barrier by obstructing the hole traversed by the sensor wire 140. However, the potting material is not applied to the portions of the sensor wire 140 to be inserted into the wearer's skin.

In addition to encasing the electrical trace 130*a-c* in a potting compound, the pins of the semiconductor packages 120, 122 are also encased in the potting compound 170, 172. After the semiconductor packages 120, 122 have been coupled, e.g., soldered, to the top layer 110*a* of the PCB, the potting compound 170, 172 is applied around the perimeter of the semiconductor packages, thereby encasing the pins. However, the potting compound 170, 172 is not applied to the upper surface of the semiconductor packages. As discussed above, the CGM 100 is designed to achieve a low profile form factor. Applying a potting compound to the upper surface of the semiconductor packages 120, 122 would increase the respective heights of those components, potentially exceeding the desired profile, which in this example, again, is less than 9 mm.

In addition, as discussed above, the potting compound is only applied around the perimeter of the semiconductor packages 120, 122 and over the portions of the electrical trace 130a,c formed on the upper and lower layers 110a, 110n of the PCB and coupling the sensor wire 140 to the first electronics package. In some examples, the potting material may also be applied over one or more guard rings 150a-c, 152a-b. Thus, the potting compound does not add to the height of the tallest electronic components, e.g., semiconductor packages, affixed to the PCB, and does not affect the overall profile of the electronics portion of the CGM 100.

Suitable potting compounds according to this disclosure include materials having a glass transition temperature greater than 45 degrees Celsius, while having a cure temperature of less than 175 degrees Celsius. Such thermal characteristics may accommodate expected operating temperatures as well as temperatures that may be experienced during manufacture, e.g., resulting from contact with the wearer's skin or heat applied to weld portions of the housing together or to otherwise seal the CGM housing. In addition, suitable potting compounds have a resistivity of greater than 10<sup>13</sup> ohms per centimeter, which may provide protection from short circuits for components encased in a common portion of the potting compound. Viscosity characteristics of suitable potting compounds include viscosities of approximately 800 poise (P) or greater; however, potting compounds having a variable viscosity during dispensing may improve manufacturing processes. One example suitable potting compound is Loctite® Eccobond® EO1072, also referred to as Hysol® EO1072, for which a technical data sheet is appended to this disclosure.

In addition to providing moisture resistance, the CGM electronics in this example include features to electrically isolate the sensor wire and the electrical trace that connects the sensor wire to the ASIC semiconductor package 120 from potential sources of current leakage. In this example, the CGM 100 employs a sensor wire 140 that, when inserted in a wearer's interstitial fluid, may provide a sensor signal with a current in the range of single-digit or tens of nanoamps ("nA"). Leakage of current from other electrical traces, ground planes, or electronic components onto the sensor wire 140 or its electrical trace 130a-c may interfere with the current generated by the sensor wire electrodes and thus may impact the accuracy of sensor readings or render them unusable. In this example, to electrically isolate the sensor wire 140 and its electrical trace 130a-c, multiple

guard rings 150a-c, 152a-b are applied to the PCB and a physical configuration of a ground plane 180 corresponding to the ASIC semiconductor package 120 is shaped to help ensure the sensor wire and its electrical trace are protected from leakage current, as will be discussed in more detail 5 with respect to FIG. 1G below.

Referring again to FIG. 1A, a portion of the sensor wire's electrical trace 130a runs along the top layer 110a of the PCB before traversing a via 132a to an interior layer as discussed above. In this example, a guard ring 150a encircles the portion of the electrical trace 130a on the top layer 110a of the PCB. By encircling the portion of the electrical trace 110a, current leaking from components near 150a, and thus do not reach the electrical trace 130a. In addition, a guard ring 152a encircles the portion of the sensor wire 140 coupled to the top layer 110a of the PCB. Referring to FIG. 1B, the electrical trace 130b running along the interior layer 110b of the PCB is also encircled by a  $_{20}$ guard ring 150b formed on the interior layer 110b of the PCB. Similarly, a guard ring 152b encircles the portion of the sensor wire 140 coupled to the interior layer 110a of the PCB. It should be noted that if the PCB has more than three layers, guard rings may be formed on each of the interior 25 layers to which the sensor wire has a connection, not merely those on which a portion of the electrical trace runs. Further, referring to FIG. 1C, the portion of the electrical trace 130con the lowest layer 110c of the PCB is also encircled by a guard ring 150c as is the portion of the sensor wire 140 30 coupled to the lowest layer 110c. Thus, all portions of the sensor wire 140 coupled to the PCB layers, and the electrical trace 130a-c running from the sensor wire 140 to the ASIC semiconductor package 120 are encircled by guard rings 150a-c, 152a-b, thereby reducing the likelihood that leakage 35 currents may reach the sensor wire 140 or the electrical trace 130a-c and affect the sensor signals.

Referring now to FIG. 1G, FIG. 1G illustrates an example layout of a portion of the PCB corresponding to the ASIC semiconductor package 120. The layout defines multiple 40 contact pads for the ASIC semiconductor package's pins as well as a ground plane 180 that couples to pins on three of the four corner portions of the package **120**. However, the fourth corner portion lacks the corresponding ground plane conductor. Instead, a portion of the guard ring 150a couples 45 two contact pads and provides an electrical barrier between the pin 160 that connects to the sensor wire's electrical trace 130a and the ground plane 180. Thus, while the semiconductor package 120 is provided with a ground plane 180, the sensor wire electrical trace 130a and the pin 160 on the 50 PCB. ASIC semiconductor package 120 connected to the electrical trace 130a are encircled by a guard ring 150a, thereby shielding the electrical trace 130a and pin 160 from the ground plane 180.

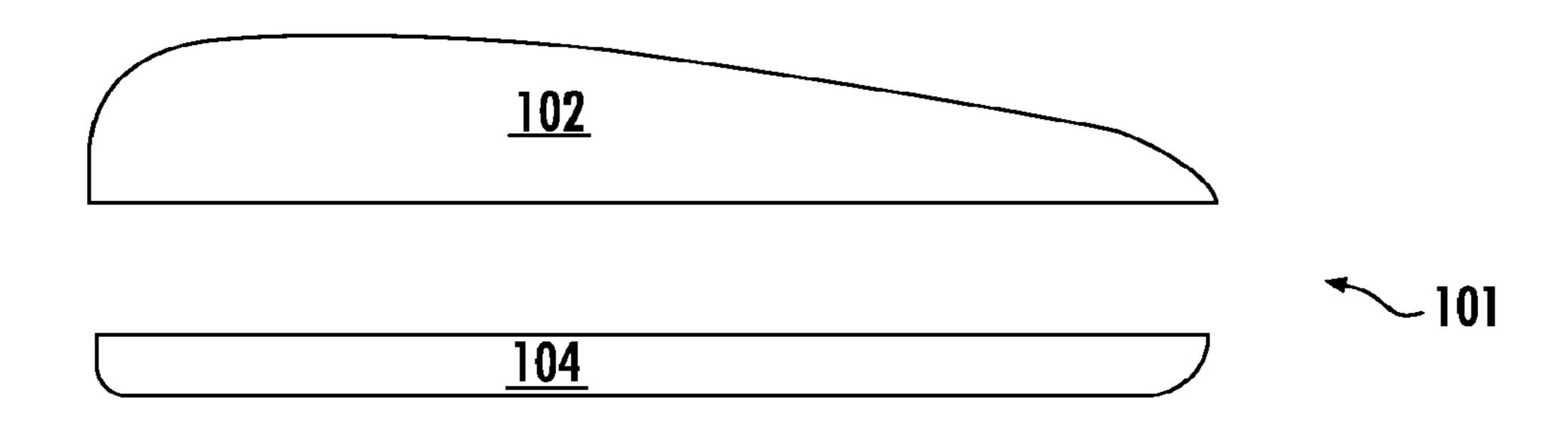

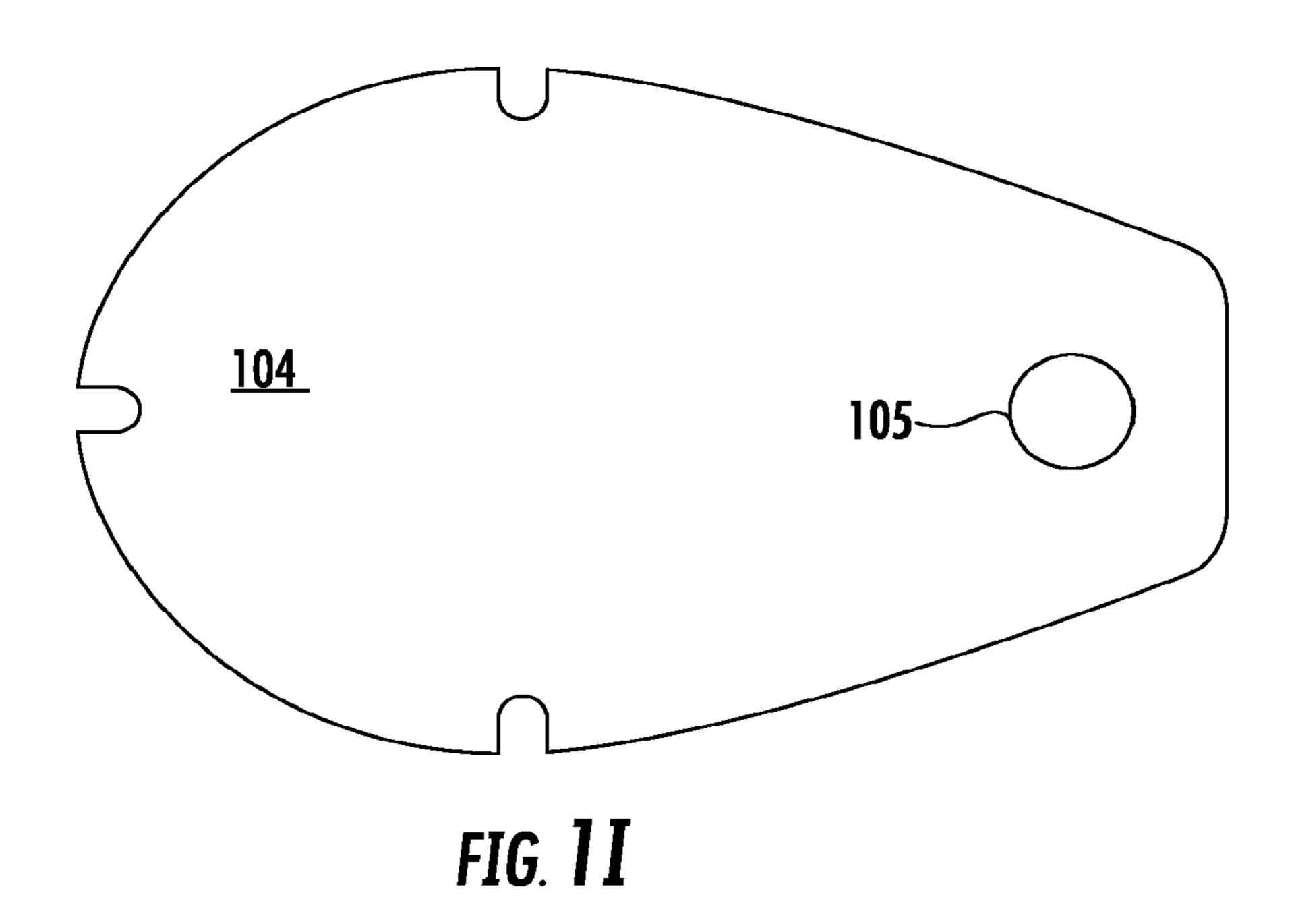

Referring now to FIGS. 1H-1I, FIGS. 1H-1I show an 55 applied or affixed to the layer 110b. example housing 101 for the CGM 100 shown in FIGS. 1A-F. The housing 101 has an upper portion 102 and a lower portion 104 that can be coupled together, such as by an adhesive (e.g., an epoxy or resin) or via heat welding, to form a waterproof seal between the housing portions. In 60 addition, the lower portion 104 of the housing defines a hole 105 through which the sensor wire 140 can pass. In this example, "lower" refers to the portion of the housing through which the sensor wire 140 passes. In addition, as discussed above, the hole 105 may be sealed with a potting 65 compound after the sensor wire 140 has been inserted through the hold 105.

Example CGMs incorporating one or more of the aforementioned features may provide improved resistance to moisture or high-humidity environments, and may enable more accurate sensor readings by shielding the sensor electronics both from moisture and from leakage currents.

Referring now to FIG. 2, FIG. 2 shows an example method for providing an electrically-isolated and moistureresistant design for a wearable device. Discussion of the method shown in FIG. 2 will be made with respect to the 10 example CGM 100 shown in FIG. 1; however, it should be appreciated that other example CGMs, or other types of electronic devices, may be provided according to examples methods according to this disclosure.

At block 200, electrical traces 130a-c are applied to the the electrical trace 130a may be absorbed by the guard ring 15 respective layers 110a-n of the PCB. In this example, the PCB will have three layers 110a-n, thus, before the layers 110a-n are bonded together, electrical trace 130a is applied to the first layer 110a, electrical trace 130b is applied to the second layer 110b, and electrical tracer 130c is applied to the third layer 110n. In addition, vias 132a-b are established in each of the layers 130a-c at locations corresponding to the ends of the respective traces 130a-c to provide a conductive path between layers 110a-n. While this example includes three PCB layers, any suitable number of layers, including 4 or more layers may be employed according to some examples.

At block 210, guard rings 150a-c, 152a-b are applied to one or more layers 110a-n of the PCB to encircle the electrical trace 130a-c corresponding to a sensor wire 140 on the respective layer. A guard ring in this example is formed by defining a trace entirely encircling an electrical trace on a respective layer, including any via through which the electrical trace runs. In some examples, the electrical trace may be applied to at least three layers of the PCB, and a guard ring may be applied to each of these layers and encircling the length of the electrical trace on the respective layer. In some examples, a guard ring may be omitted on one or more layers if no other electronic components or traces are routed or affixed to the layer.

At block 220, one or more electronic devices, such as semiconductor packages, resistors, capacitors, batteries, etc. are affixed to the appropriate layers of the PCB. For example, the semiconductor packages 120, 122 may be soldered to corresponding bonding pads on top layer 110a of the PCB. In some examples, a resistor may be affixed to the top layer 110a of the PCB to couple the sensor wire electrical trace 130a to a pin 160 on the ASIC semiconductor package 120. In still other examples, fewer, additional, or different electronic devices may be affixed to layers of the

At block 230, the layers 110a-n are bonded together to create the multi-layer PCB. In this example, layer 110b is bonded between layers 110a and 110n after any electrical traces, guard rings, vias, or electrical components are

At block 240, a potting compound is applied to at least one of the top or bottom layers 110a, n of the PCB. In this example, a potting compound 170 is applied around the perimeter of the ASIC semiconductor package 120 that encases each of its pins. In addition, the potting compound 170 is applied over-top of the sensor wire electrical tracer 130a and the associated guard ring 150a. Potting compound 172, 174 is also applied around the perimeter of the wireless transceiver semiconductor package 122 and over-top of the sensor wire 140 coupled to the top layer 110a of the PCB. Potting compound 176 in this example is also applied to the bottom layer 110n of the PCB to encase the portion of the

sensor wire electrical trace 130c and the guard ring 150c that encircles the electrical trace 130c and the sensor wire 140c. It should be appreciated that a potting compound may not be applied to the bottom layer 110n of the PCB if the electrical trace coupling the sensor wire 140c to the ASIC semiconductor package 120c couples to the sensor wire on an interior layer 110b of the PCB. In such an example, potting compound is not applied to the interior layer 110b of the PCB.

At block **250**, the sensor wire **140** is affixed to the PCB. In this example, the sensor wire **140** is inserted into a 10 preformed hole in the PCB and soldered into place. However, in some examples, the sensor wire **140** may be soldered or affixed to the PCB, e.g., by one or more clamps or other features that provide an interference or frictional coupling. In some examples the sensor wire **140** may be bonded to the 15 PCB using an adhesive, such as a non-conducting epoxy or resin.

At block 260, the PCB is disposed within a housing 101. In this example, the housing 101 is made of two housing portions, a lower portion 104 and an upper portion 102. The 20 PCB may be disposed in a lower portion 104 of the housing 101 to allow the sensor wire 140 to extend downward through a corresponding hole 105 in the lower portion 104 of the housing 101. The upper portion 102 of the housing 101 may then be placed over the PCB and into contact with 25 the lower portion 102 of the housing 101. And while, in this example, the housing 101 is made up of two portions 102, 104, other example housings may have more than two pieces, or may only have a single piece that entirely encases the PCB, or is open on one side, which may later be sealed, 30 such as at block 270.

At block 270, the housing 101 is sealed. For example, the upper and lower portions 102, 104 of the housing 101 may be sealed using an adhesive, such as an epoxy or resin. In some examples, the upper and lower portions 102, 104 of the 35 housing 101 may be heat welded together. In addition, a potting compound may be applied within the hole 105 in the lower portion 104 of the housing 101 after the sensor wire 140 has been inserted through it. The potting compound may provide a seal between the sensor wire 140 and the lower 40 portion 104 of the housing 101 to provide a barrier against contaminants, such as moisture or dirt from entering the housing 101.

While the method of FIG. 2 has been described as having certain steps, in some examples, only some of the steps may 45 be performed, or the steps may be performed in an order different than is described.

While some examples of methods and systems herein are described as having semiconductor packages that include circuitry. For example, a semiconductor package may 50 include a processor or processors. The processor comprises a computer-readable medium, such as a random access memory (RAM) coupled to the processor. The processor executes computer-executable program instructions stored in memory, such as executing one or more computer pro- 55 grams for editing an image. Such processors may comprise a microprocessor, a digital signal processor (DSP), an application-specific integrated circuit (ASIC), field programmable gate arrays (FPGAs), and state machines. Such processors may further comprise programmable electronic 60 devices such as PLCs, programmable interrupt controllers (PICs), programmable logic devices (PLDs), programmable read-only memories (PROMs), electronically programmable read-only memories (EPROMs or EEPROMs), or other similar devices.

Such processors may comprise, or may be in communication with, media, for example computer-readable storage

12

media, that may store instructions that, when executed by the processor, can cause the processor to perform the steps described herein as carried out, or assisted, by a processor. Examples of computer-readable media may include, but are not limited to, an electronic, optical, magnetic, or other storage device capable of providing a processor, such as the processor in a web server, with computer-readable instructions. Other examples of media comprise, but are not limited to, a floppy disk, CD-ROM, magnetic disk, memory chip, ROM, RAM, ASIC, configured processor, all optical media, all magnetic tape or other magnetic media, or any other medium from which a computer processor can read. The processor, and the processing, described may be in one or more structures, and may be dispersed through one or more structures. The processor may comprise code for carrying out one or more of the methods (or parts of methods) described herein.

The foregoing description of some examples has been presented only for the purpose of illustration and description and is not intended to be exhaustive or to limit the disclosure to the precise forms disclosed. Numerous modifications and adaptations thereof will be apparent to those skilled in the art without departing from the spirit and scope of the disclosure.

Reference herein to an example or implementation means that a particular feature, structure, operation, or other characteristic described in connection with the example may be included in at least one implementation of the disclosure. The disclosure is not restricted to the particular examples or implementations described as such. The appearance of the phrases "in one example," "in an example," "in one implementation," or "in an implementation," or variations of the same in various places in the specification does not necessarily refer to the same example or implementation. Any particular feature, structure, operation, or other characteristic described in this specification in relation to one example or implementation may be combined with other features, structures, operations, or other characteristics described in respect of any other example or implementation.

Use herein of the word "or" is intended to cover inclusive and exclusive OR conditions. In other words, A or B or C includes any or all of the following alternative combinations as appropriate for a particular usage: A alone; B alone; C alone; A and B only; A and C only; B and C only; and A and B and C.

That which is claimed is:

- 1. A wearable device comprising:

- a printed circuit board ("PCB") having first and second outer layers and an inner layer, the inner layer disposed between the first and second outer layers;

- a semiconductor package having a plurality of electrical conductors, the semiconductor package coupled to the first outer layer of the PCB using the plurality of electrical conductors;

- an electrical contact formed on the second outer layer of the PCB;

- a trace having a first portion disposed on the first outer layer, a second portion disposed on the inner layer, and a third portion disposed on the second outer layer, the trace having a first end coupled to a first electrical conductor of the plurality of electrical conductors and a second end coupled to the electrical contact; and

- an encapsulant disposed around a perimeter of the semiconductor package, the encapsulant covering (i) the plurality of electrical conductors, (ii) the first portion of the trace, (iii) the third portion of the trace, wherein an upper surface of the semiconductor package remains exposed.

- 2. The wearable device of claim 1, further comprising a sensor wire coupled to the second outer layer of the PCB and extending from the PCB, wherein the sensor wire is further coupled to the electrical contact.

- 3. The wearable device of claim 2, further comprising a housing defining a cavity and comprising a first housing portion and a second housing portion, the first housing portion coupled to the second housing portion to define the cavity, the PCB disposed within the housing and the sensor wire extending through the housing.

- 4. The wearable device of claim 3, wherein the first housing portion is heat welded to the second housing portion.

- 5. The wearable device of claim 2, wherein the sensor wire comprises first and second electrodes, the first electrode comprising a platinum or platinum-coated wire, and the second electrode comprising a silver/silver-chloride (Ag/AgCl) material.

- 6. The wearable device of claim 1, wherein the encapsulant has a glass transition temperature greater than 45 degrees Celsius and a cure temperature of less than 175 degrees Celsius.

- 7. The wearable device of claim 1, wherein the encapsulant has a glass transition temperature greater than an operating temperature range of the wearable device and a cure temperature substantially lower than a melting temperature of a housing material of the wearable device.

- 8. The wearable device of claim 1, wherein the encapsulant has a resistivity of at least  $10^{13}$  ohms per centimeter.

- 9. The wearable device of claim 1, wherein a total height of the PCB and the semiconductor package is less than 9 millimeters.

- 10. A wearable device comprising:

- a printed circuit board ("PCB") having first and second outer layers and an inner layer, the inner layer disposed between the first and second outer layers;

**14**

- a semiconductor package having a plurality of electrical conductors, the semiconductor package coupled to the first outer layer of the PCB using the plurality of electrical conductors;

- an electrical ground plane formed on the PCB and coupled to a subset of the plurality of electrical conductors and not coupled to any electrical conductors at a first corner portion of the semiconductor package;

- an electrical contact formed on the second outer layer of the PCB;

- a trace having a first portion disposed on the first outer layer, a second portion disposed on the inner layer, and a third portion disposed on the second outer layer, the trace having a first end coupled to a first electrical conductor of the plurality of electrical conductors and a second end coupled to the electrical contact, the first electrical conductor at the first corner portion of the semiconductor package; and

- a plurality of guard rings disposed on the PCB, each guard ring of the plurality of guard rings encircling a respective one of the portions of the trace.

- 11. The wearable device of claim 10, further comprising a sensor wire coupled to the second outer layer of the PCB and extending from the PCB, wherein the sensor wire is further coupled to the electrical contact.

- 12. The wearable device of claim 11, wherein the sensor wire comprises first and second electrodes, the first electrode comprising a platinum or platinum-coated wire, and the second electrode comprising a silver/silver-chloride (Ag/AgCl) material.

- 13. The wearable device of claim 11, further comprising a housing defining a cavity and comprising a first housing portion and a second housing portion, the first housing portion coupled to the second housing portion to define the cavity, the PCB disposed within the housing and the sensor wire extending through the housing.

\* \* \* \*