#### US010637479B2

## (12) United States Patent

#### Hamilton et al.

## (54) SUPERCONDUCTING CIRCUIT DEVICE AND APPLICATIONS OF SAME

(71) Applicant: AUBURN UNIVERSITY, Auburn, AL (US)

(72) Inventors: **Michael C. Hamilton**, Auburn, AL (US); **Uday S. Goteti**, Auburn, AL (US)

(73) Assignee: AUBURN UNIVERSITY, Auburn, AL (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 16/000,105

(22) Filed: Jun. 5, 2018

#### (65) Prior Publication Data

US 2018/0294815 A1 Oct. 11, 2018

#### Related U.S. Application Data

- (63) Continuation of application No. 15/617,727, filed on Jun. 8, 2017, now Pat. No. 9,998,122.

- (60) Provisional application No. 62/347,165, filed on Jun. 8, 2016.

- (51) Int. Cl.

H03K 19/195 (2006.01)

H03K 19/21 (2006.01)

H03K 3/38 (2006.01)

(52) **U.S. Cl.**CPC ...... *H03K 19/195* (2013.01); *H03K 3/38* (2013.01); *H03K 19/21* (2013.01)

(58) Field of Classification Search

CPC ......... H03K 3/38; H03K 19/21; H03K 19/195

See application file for complete search history.

### (10) Patent No.: US 10,637,479 B2

(45) Date of Patent: Apr. 28, 2020

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 3,281,609 A   | 10/1966 | Rowell                |  |  |

|---------------|---------|-----------------------|--|--|

| 5,334,884 A * | 8/1994  | Tesche H03B 15/003    |  |  |

|               |         | 324/248               |  |  |

| 9,390,951 B2* | 7/2016  | Freer B82Y 10/00      |  |  |

| 9,664,751 B1* | 5/2017  | Berggren G01R 33/0354 |  |  |

| (Continued)   |         |                       |  |  |

#### OTHER PUBLICATIONS

J.E. Mooij and Yu. V. Nazarov, Superconducting Nanowires as Quantum Phase-Slip Junctions, Feb. 12, 2006, https://www.nature.com/articles/nphys234; whole document (Year: 2006).\*

(Continued)

Primary Examiner — Alexander H Taningco

Assistant Examiner — Kurtis R Bahr

(74) Attorney, Agent, or Firm — Locke Lord LLP; Tim

Tingkang Xia, Esq.

#### (57) ABSTRACT

A superconducting circuit device includes one or more JJs and one or more QPSJs. The one or more QPSJs are adapted for receiving at least one input and responsively providing at least one output. Each QPSJ is configured such that when an input voltage of an input voltage pulse exceeds a critical value, a quantized charge of a Cooper electron pair tunnels across said QPSJ as an output, when the input voltage is less than the critical value, no quantized charge of the Cooper electron pair tunnels across said QPSJ as the output, wherein the presence and absence of the quantized charge that is realizable as a constant area of current pulses in the output form two logic states, and wherein the at least one QPSJ is biased with a bias voltage. The superconducting circuit device may include one or more JJs.

#### 26 Claims, 31 Drawing Sheets

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 9,998,122 B2    | 6/2018   | Hamilton et al.   |

|-----------------|----------|-------------------|

| 2008/0048902 A1 | * 2/2008 | Rylov H03M 1/1215 |

|                 |          | 341/155           |

| 2015/0111754 A1 | * 4/2015 | Harris G06N 10/00 |

|                 |          | 505/170           |

| 2017/0201224 A1 | * 7/2017 | Strong H01P 1/18  |

#### OTHER PUBLICATIONS

Ergul, et. al.; Quantum Phase Slips in one-dimensional Josephson Junction Chains, May 30, 2013; Cornell University;pp. 1 thru 12 arXiv.org (Year: 2013).\*

Josephson, Brian David. "Possible new effects in superconductive tunnelling." Physics letters 1.7 (1962): 251-253.

Anderson, Philip W., and John M. Rowell. "Probable observation of the Josephson superconducting tunneling effect." Physical Review Letters 10.6 (1963): 230.

Hamilton, Clark A., Charles J. Burroughs, and Samuel P. Benz. "Josephson voltage standard-a review." IEEE transactions on applied superconductivity 7.2 (1997): 3756-3761.

Anacker, Wilhelm. "Potential of superconductive Josephson tunneling technology for ultrahigh performance memories and processors." IEEE Transactions on Magnetics 5.4 (1969): 968-975.

Anacker, Wilhelm. "Josephson computer technology: an IBM research project." IBM Journal of Research and Development24.2 (1980): 107-112.

Likharev, Konstantin K., and Vasilii K. Semenov. "RSFQ logic/memory family: A new Josephson-junction technology for subterahertz-clock-frequency digital systems." IEEE Transactions on Applied Superconductivity 1.1 (1991): 3-28.

Holmes, D. Scott, Andrew L. Ripple, and Marc A. Manheimer. "Energy-efficient superconducting computing—Power budgets and requirements." IEEE Transactions on Applied Superconductivity 23.3 (2013): 1701610-1701610.

Tolpygo, Sérgey K. "Superconductor digital electronics: Scalability and energy efficiency issues." Low Temperature Physics 42.5 (2016): 361-379.

Langer, J. S. "JS Langer and V. Ambegaokar, Phys. Rev. 164, 498 (1967)." Phys. Rev. 164 (1967): 498.

Skocpol, W. J., M. R. Beasley, and M. Tinkham. "Phase-slip centers and nonequilibrium processes in superconducting tin microbridges." Journal of Low Temperature Physics 16.1-2 (1974): 145-167.

Giordano, N. "Evidence for macroscopic quantum tunneling in one-dimensional superconductors." Physical review letters61.18 (1988): 2137.

Mooij, J. E., and Yu V. Nazarov. "Superconducting nanowires as quantum phase-slip junctions." Nature Physics 2.3 (2006): 169. Mooij, J. E., and C. J. P. M. Harmans. "Phase-slip flux qubits." New Journal of Physics 7.1 (2005): 219.

Webster, C. H., et al. "Nbsi nanowire quantum phase-slip circuits: dc supercurrent blockade, microwave measurements, and thermal analysis." Physical Review B 87.14 (2013): 144510.

Hriscu, Alina Marina. "Theoretical proposals of quantum phase-slip devices." (2012).

Goteti, Uday S., and Michael C. Hamilton. "Charge-based superconducting digital logic family using quantum phase-slip junctions." IEEE Transactions on Applied Superconductivity 28.4 (2018): 1-4.

Goteti, Uday Sravan, and Michael C. Hamilton. "SPICE model implementation of quantum phase-slip junctions." Electronics Letters 51.13 (2015): 979-981.

Murphy, Andrew, Dmitri V. Averin, and Alexey Bezryadin. "Nanoscale superconducting memory based on the kinetic inductance of asymmetric nanowire loops." New Journal of Physics 19.6 (2017): 063015.

<sup>\*</sup> cited by examiner

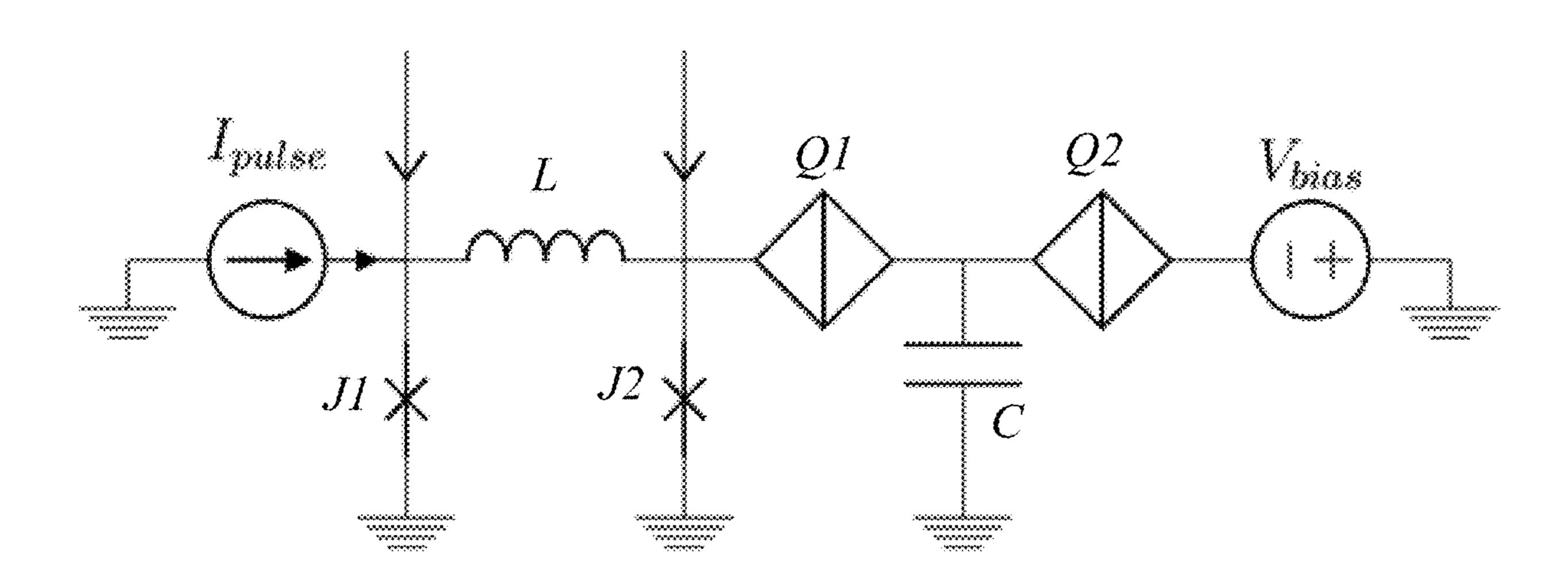

FIG. 1 (Prior Art)

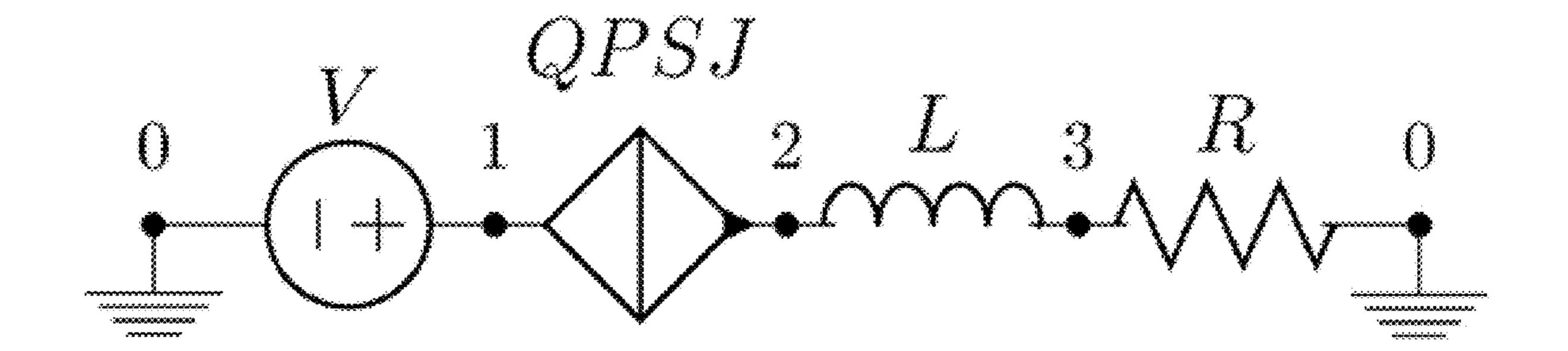

FIG. 2

FIG. 4

Length = 3.0  $\mu$ m

Thickness = 5nm

Thickness = 20nm

Thickness = 30nm

Thickness = 40nm

Thickness = 50nm

Thickness = 50nm

Thickness = 100nm

Thickness = 100nm

Thickness = 100nm

Width (nm)

FIG. 6

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 17

FIG. 18

FIG. 19

FIG. 25

FIG. 29

FIG. 31

Apr. 28, 2020

FIG. 33

FIG. 34

FIG. 35

FIG. 36

FIG. 37

FIG. 39

FIG. 41

FIG. 43

FIG. 44

FIG. 45

FIG. 46

FIG. 47

1

# SUPERCONDUCTING CIRCUIT DEVICE AND APPLICATIONS OF SAME

## CROSS-REFERENCE TO RELATED PATENT APPLICATIONS

This application is a continuation application of U.S. patent application Ser. No. 15/617,727, filed Jun. 8, 2017, now allowed, which itself claims priority to and the benefit of, pursuant to 35 U.S.C. § 119(e), U.S. Provisional Patent Application Ser. No. 62/347,165, filed Jun. 8, 2016, which are incorporated herein in their entireties by reference.

Some references, which may include patents, patent applications and various publications, are cited and discussed in the description of this invention. The citation and/or discus- 15 sion of such references is provided merely to clarify the description of the present invention and is not an admission that any such reference is "prior art" to the invention described herein. All references cited and discussed in this specification are incorporated herein by reference in their <sup>20</sup> entireties and to the same extent as if each reference was individually incorporated by reference. In terms of notation, hereinafter, "[n]" represents the nth reference cited in the reference list. For example, [30] represents the 30th reference cited in the reference list, namely, Uday S Goteti and <sup>25</sup> Michael C Hamilton, Spice model implementation of quantum phase-slip junctions, Electronics Letters, 51(13):979-981, 2015.

#### FIELD OF THE INVENTION

The present invention relates generally to superconducting quantum logic, and more particularly, to a superconducting circuit device comprising at least one of one or more Josephson junctions (JJs) and one or more quantum phase 35 slip junctions (QPSJs), and applications of the same.

#### BACKGROUND OF THE INVENTION

The background description provided herein is for the 40 purpose of generally presenting the context of the present invention. The subject matter discussed in the background of the invention section should not be assumed to be prior art merely as a result of its mention in the background of the invention section. Similarly, a problem mentioned in the 45 background of the invention section or associated with the subject matter of the background of the invention section should not be assumed to have been previously recognized in the prior art. The subject matter in the background of the invention section merely represents different approaches, 50 which in and of themselves may also be inventions. Work of the presently named inventors, to the extent it is described in the background of the invention section, as well as aspects of the description that may not otherwise qualify as prior art at the time of filing, are neither expressly nor impliedly 55 admitted as prior art against the present invention.

Superconducting electronics, primarily involving Josephson junctions and related devices have been crucial in several analog and digital electronic applications, as well as in quantum computing. With the report of Josephson junctions (JJ), it was quickly realized that these devices can be used advantageously as significantly fast switches and logic devices compared to conventional CMOS based logic [1-3]. A voltage-state type logic was pursued in earlier developments at IBM, for example, which used zero-voltage of JJs 65 during its superconducting state as logical '0' and corresponding non-zero voltage of its normal state as logical '1'

2

[4]. This logic family found difficulty competing with CMOS logic due to several disadvantages including poor choice of superconducting materials, and mainly, the use of under-damped Josephson junctions that latch into the voltage state, once switched [5], although several improvements were suggested [6, 7]. Some of the drawbacks of a voltage-state logic family were addressed using single flux quantum (SFQ) logic, which employs over-damped JJs, was introduced in 1985 [8] and was experimentally demonstrated in 1987 [9]. Later, several improvements were suggested for circuits in this logic family [10-12].

Rapid single-flux-quantum (RSFQ) logic family is known to perform arithmetic and logic operations at compellingly high clock speeds (a few hundred GHz) [13, 14] using significantly lower energy compared to existing CMOS technologies [15-17]. The basic logic elements of this technology employ superconducting loops, broken with JJs, that store flux quanta as its basic logic element. The state of the element can be measured as voltage pulses with quantized area [5]. However, RSFQ logic has disadvantages in having static power dissipation and in requiring relatively large DC current biases to supply current to all the junctions, which, in-turn, introduce difficulties in design. These two disadvantages were overcome by other related technologies that use the same quantized flux logic but with improved biasing techniques such as low voltage RSFQ [17, 18], energyefficient RSFQ (ERSFQ/eSFQ) [15, 16, 19], reciprocal quantum logic (RQL) [20, 21] and adiabatic quantum flux parametron (AQFP) [22, 23].

Quantum phase-slip is a phenomenon in superconducting systems where the phase difference between two connected superconducting regions changes by  $2\pi$  with the suppression of the superconducting order parameter to zero. This occurs with quantum tunneling of vortices or fluxons across a narrow superconducting line, which is a dual to macroscopic quantum tunneling of charges across the insulating barrier in Josephson junction structures [25]. These effects have been studied extensively for quasi-one-dimensional nanowires, with thermally induced phase slips observed near the superconducting transition temperatures of the nano-wire and quantum phase-slips at significantly lower temperatures [37-44]. Qubits based on coherent quantum phase-slips were proposed [43] and coherent phase-slip events were observed [42].

QPSJ-based structures may serve as a potential circuit element in applications in superconducting electronics, quantum information processing and as a current standard. However, demonstrating a QPSJ with proper DC and RF operation has been relatively challenging to implement practically [44]. There has been no platform to identify potential applications of a QPSJ in electronic circuits.

Therefore, a heretofore unaddressed need exists in the art to address the aforementioned deficiencies and inadequacies.

#### SUMMARY OF THE INVENTION

In one aspect, the present invention relates to a superconducting circuit device comprising one or more JJs and one or more QPSJs.

In one embodiment, the one or more QPSJs are adapted for receiving at least one input and responsively providing at least one output, each QPSJ being configured such that when an input voltage of an input voltage pulse exceeds a critical value, a quantized charge of a Cooper electron pair tunnels across said QPSJ as an output, when the input voltage is less than the critical value, no quantized charge of the Cooper

electron pair tunnels across said QPSJ as the output, wherein the presence and absence of the quantized charge that is realizable as a constant area of current pulses in the output form two logic states, and wherein the at least one QPSJ is biased with a bias voltage.

In one embodiment, the bias voltage is about 50-95% of the critical voltage, the input voltage is at least about 110% of the critical voltage for quantized charge tunneling.

In one embodiment, each QPSJ is characterizable as a compact circuit model, wherein the compact circuit model 10 comprises a voltage source, a phase-slip junction, an inductor representing an inductance of a nano-wire of the phaseslip junction, and a non-linear resistor having different values of resistance in different phases of operation and showing normal to superconductor transition as a function of 15 the voltage across the phase-slip junction, coupling to each other in series.

In one embodiment, the critical voltage, the inductance, and the resistance are determined by material properties and physical dimensions of the QPSJ.

In one embodiment, the one or more QPSJs comprise two QPSJs, wherein a node connecting two QPSJs and a capacitor defines a charge island.

In one embodiment, when the quantized charge of the Cooper electron pair tunnels across one of the two QPSJs, 25 the quantized charge of the Cooper electron pair is stored in the charge island, otherwise no quantized charge of the Cooper electron pair is stored in the charge island, thereby forming a basic logic element having the two logic states.

In one embodiment, the one or more QPSJs forms a QPSJ 30 transmission line, wherein the one or more QPSJs comprise a plurality of QPSJs connected to one another in series, wherein each node connecting two adjacent QPSJs and a capacitor defines a charge island.

electron pair is stored in a charge island or forced to hop to its immediately next charge island, by design of or tuning a capacitance of the charge island, along with the junction parameters, thereby transferring the quantized charge of the Cooper electron pair along the QPSJ transmission line.

In one embodiment, amplification or attenuation of the current pulse amplitude is obtained by using the QPSJs of different critical voltages and different capacitor values.

In one embodiment, the one or more QPSJs forms a QPSJ pulse splitter, wherein the one or more QPSJs comprise three 45 QPSJs, where the first QPSJ has a first terminal connected to an input voltage source defining an input node, and a second terminal connected to a first capacitor; the second QPSJ has a first terminal connected to the second terminal of the first QPSJ, and a second terminal connected to a 50 second capacitor and a first bias voltage source defining a first output node; and the third QPSJ has a first terminal connected to the second terminal of the first QPSJ, and a second terminal connected to a third capacitor and a second bias voltage source defining a second output node. In 55 operation, an input pulse at the input node is split into two pulses output from the first and second output nodes respectively.

In one embodiment, the one or more QPSJs forms a QPSJ buffer, wherein the one or more QPSJs comprise three 60 QPSJs, wherein the first QPSJ has a first terminal connected to an input voltage source or a first bias voltage source defining a first node, and a second terminal connected to a first capacitor defining a second node; the second QPSJ has a first terminal connected to the second terminal of the first 65 QPSJ defining a third node, and a second terminal connected to a second capacitor and the first bias voltage source or the

input voltage source defining a fourth node; and the third QPSJ has a first terminal connected to the third node, and a second terminal connected to a second bias voltage source. In operation, an input pulse from the first node through the first QPSJ switches to the third QPSJ, before it switches to the second QPSJ so as to prevent a signal flow in a direction from the first node to the fourth node, or when current arrives from an opposite direction, the first QPSJ switches before the third QPSJ, allowing the signal through.

In one embodiment, the one or more QPSJs forms a QPSJ confluence buffer, wherein the one or more QPSJs comprise four QPSJs, wherein the first QPSJ has a first terminal connected to a first input voltage source, and a second terminal connected to a first capacitor defining node 3; the second QPSJ has a first terminal connected to a second input voltage source, and a second terminal connected to a second capacitor defining node 6, wherein both nodes 3 and 6 are connected to node 7; the third QPSJ has a first terminal 20 connected to node 7, and a second terminal connected to a first bias voltage source; and the fourth QPSJ has a first terminal connected to node 7, and a second terminal connected to a third capacitor and the second bias voltage source at node 8, wherein in operation, input pulses from either the first or second input voltage sources result in an output pulse from node 8, but do not result in output from the other input.

In one embodiment, the one or more QPSJs forms a QPSJ based OR gate, wherein the one or more QPSJs comprise six QPSJs, wherein the first to fourth QPSJs define the confluence buffer and the fifth and sixth QPSJs define an island, wherein the confluence buffer is connected to the island in series such that a first terminal of the fifth QPSJ is connected to the output terminal of the confluence buffer and a second terminal of the sixth QPSJ is connected to a clock signal of In one embodiment, the quantized charge of the Cooper 35 a third input voltage source that is connected to a second bias voltage source.

> In one embodiment, the one or more QPSJs forms a QPSJ based AND gate, wherein the one or more QPSJs comprise five QPSJs, wherein the first to fourth QPSJs define the 40 confluence buffer and the fifth QPSJ has a first terminal connected to the output terminal of the confluence buffer and a second terminal connected to a second bias voltage source, and the output terminal of the confluence buffer is connected to a clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, the one or more QPSJs forms a QPSJ based XOR gate, wherein the one or more QPSJs comprise four QPSJs, wherein the first to fourth QPSJs define the confluence buffer and the output terminal of the confluence buffer is connected to a clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, the one or more QPSJs forms an RS flip-flop or a D flip-flop, wherein the one or more QPSJs comprise two QPSJs, wherein the first QPSJ has a first terminal connected to a bias voltage source at node 2 that in turn is connected to a first input voltage source connected to node 1, a second terminal connected node 3 that in turn is connected to a capacitor; and the second QPSJ has a first terminal connected to node 3, and a second terminal connected to node 4 that is in turn connected to the second input voltage source.

In one embodiment, the one or more QPSJs forms the RS flip-flop, wherein in operation, a SET input signal at node 1 induces a quantized charge of the Cooper electron pair to the island of node 3, and a RESET input signal at node 4 induces a current pulse opposite to that induced by the SET input signal so as to reset the charge on the island.

5

In one embodiment, the one or more QPSJs forms the D flip-flop, wherein in operation, a SET input signal at node 1 induces a quantized charge of the Cooper electron pair to the island of node 3, and a RESET input signal at node 4 is a clock signal that switches the first QPSJ and induces a quantized charge of the Cooper electron pair on the island, and with the next clock pulse, the charge flows through an output terminal to perform a function of the D flip-flop.

In one embodiment, the one or more QPSJs forms a T flip-flop, wherein the one or more QPSJs comprise two QPSJs, wherein the first QPSJ has a first terminal connected to a bias voltage source at node 3 that in turn is connected to an input voltage source at node 2, the input voltage source connected to node 1, a second terminal connected node 4 that in turn is connected to a capacitor; and the second QPSJ has a first terminal connected to node 4, and a second terminal connected to node 2. In operation, a single clock signal of the input voltage source is input at node 1, and at each clock pulse, the current pulse toggles from ON to OFF and vice versa, indicating the presence and absence of a quantized charge of the Cooper electron pair on the island 20 with each clock pulse.

In one embodiment, each of the one or more JJs is configured such that when an input current through said JJ exceeds a critical value, a single flux quantum pulse tunnels across said JJ as an output, when the input current is less than the critical value, no single flux quantum pulse tunnels across said JJ as the output, wherein the presence and absence of the single flux quantum pulse in the output form two logic states.

In one embodiment, the one or more QPSJs comprise two QPSJs defining a QPSJ island with a capacitor, and the one or more JJs comprises two JJs defining a JJ loop with a inductor, and the QPSJ island and the JJ loop is connected in series to perform a bridge operation between flux and charge.

In one embodiment, the one or more QPSJs further <sup>35</sup> comprises a third QPSJ having a first terminal connected to a node between the QPSJ island and the JJ loop, and a second terminal connected to a bias voltage source, wherein in operation, a voltage pulse is induced through the third QPSJ that enables or disables the output pulse.

40

In one embodiment, the superconducting circuit device further comprises at least one complementary quantum logic (CQL) cell, each CQL cell comprising at least one QPSJ, and at least one JJ coupled with the at least one QPSJ to perform one or more logic operations.

In one embodiment, the CQL cell comprises two QPSJs defining a QPSJ island with a capacitor, and two JJs defining a JJ loop with a inductor, and the QPSJ island and the JJ loop is connected in series to perform a bridge operation between flux and charge.

In one embodiment, the CQL cell further comprises a third QPSJ having a first terminal connected to a node between the QPSJ island and the JJ loop, and a second terminal connected to a bias voltage source, wherein in operation, a voltage pulse is induced through the third QPSJ 55 that enables or disables the output pulse.

These and other aspects of the present invention will become apparent from the following description of the preferred embodiment taken in conjunction with the following drawings, although variations and modifications therein 60 may be affected without departing from the spirit and scope of the novel concepts of the disclosure.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings illustrate one or more embodiments of the present invention and, together with the

6

written description, serve to explain the principles of the invention. Wherever possible, the same reference numbers are used throughout the drawings to refer to the same or like elements of an embodiment.

FIG. 1 shows a compact circuit model for a QPSJ implemented in a SPICE model.

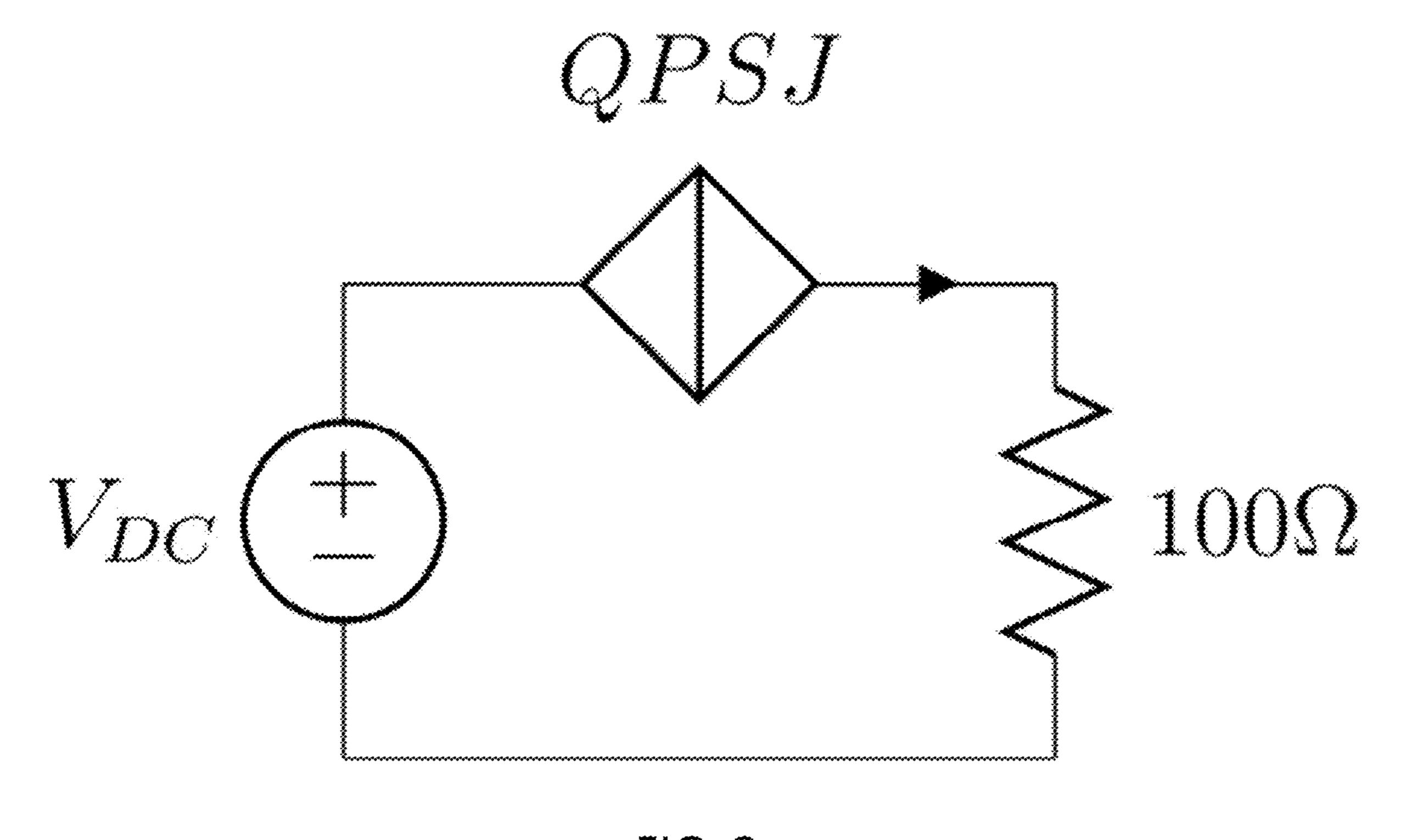

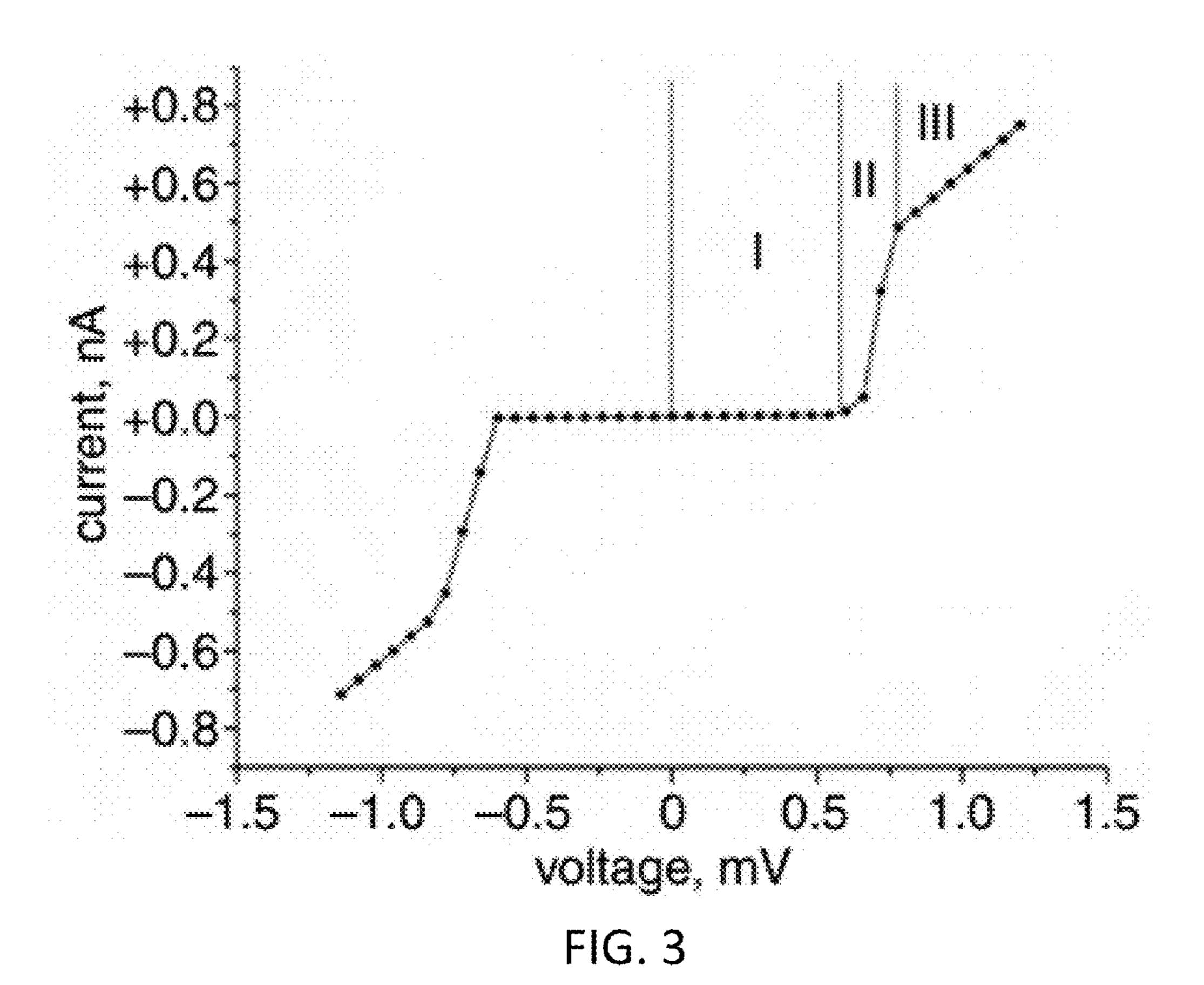

FIG. 2 shows a QPSJ circuit for simulation with piecewise linear function for voltage V from -1.2 mV to 1.2 mV in 4 ns and series resistor  $R=100\Omega$ , according to one embodiment of the present invention.

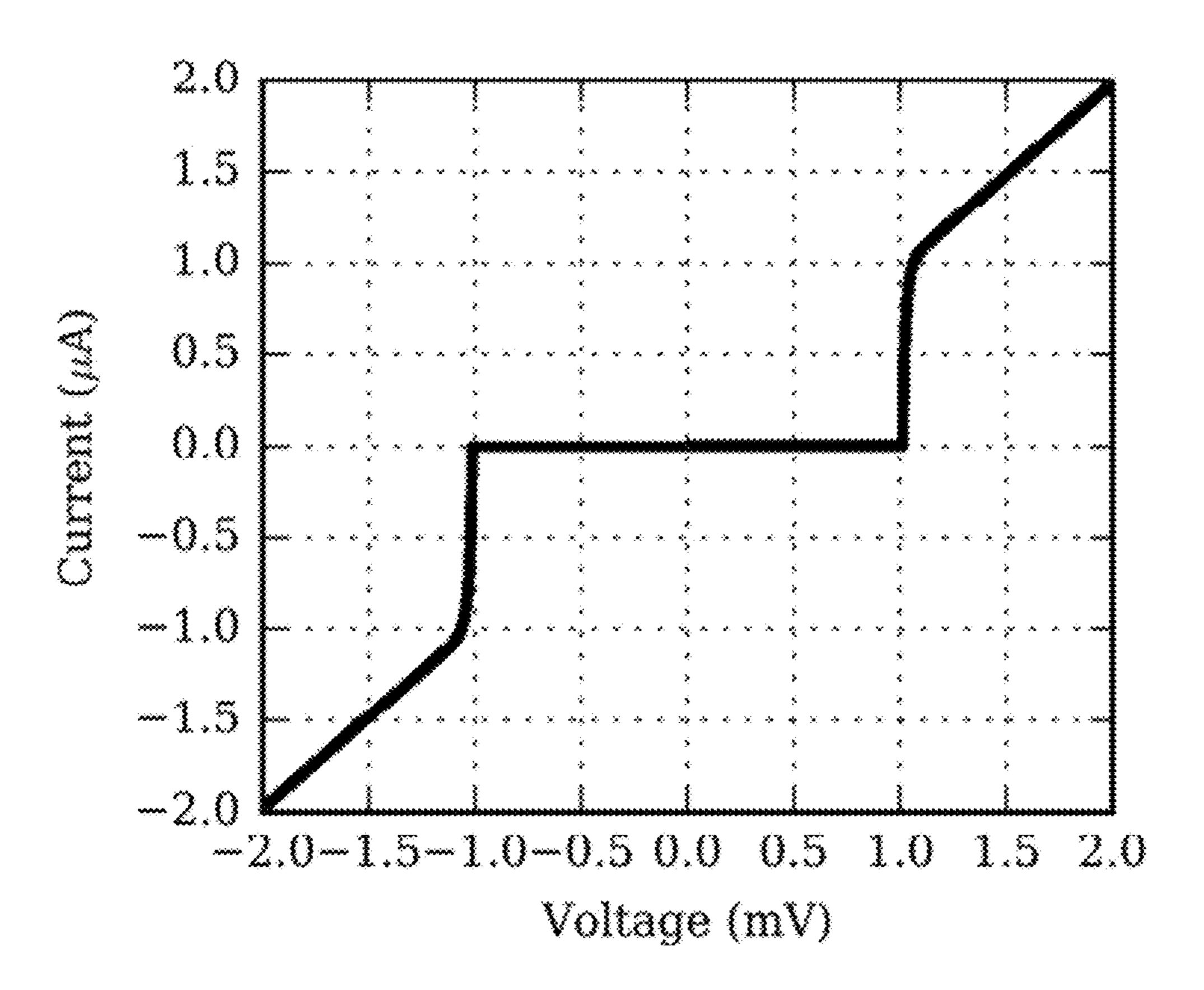

FIG. 3 shows current-voltage (I-V) characteristics of the QPSJ circuit shown in FIG. 2, according to one embodiment of the present invention, which is simulated in JSPICE using relevant model parameters.

FIG. 4 shows I-V characteristics of the compact circuit model of the QPSJ shown in FIG. 1 with  $V_C$ =1 mV, L=20 nH and R=1 k $\Omega$ , according to one embodiment of the present invention.

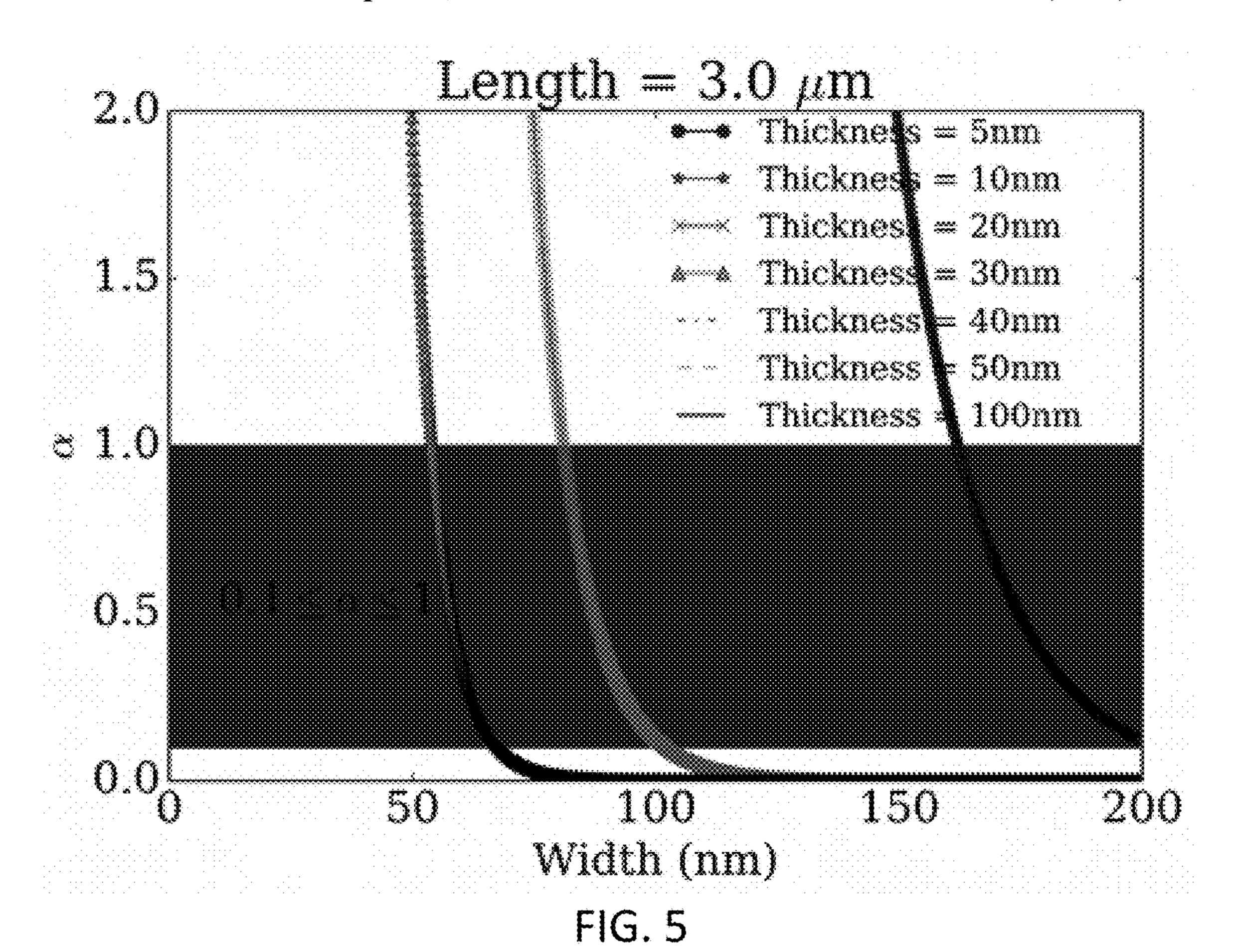

FIG. 5 shows design parameter evaluation for InOx, where the shaded region shows design parameter combinations satisfying conditions for forming a QPSJ, according to one embodiment of the present invention.

FIG. 6 shows design parameter evaluation for NbN, where the shaded region shows design parameter combinations satisfying conditions for forming a QPSJ, according to one embodiment of the present invention.

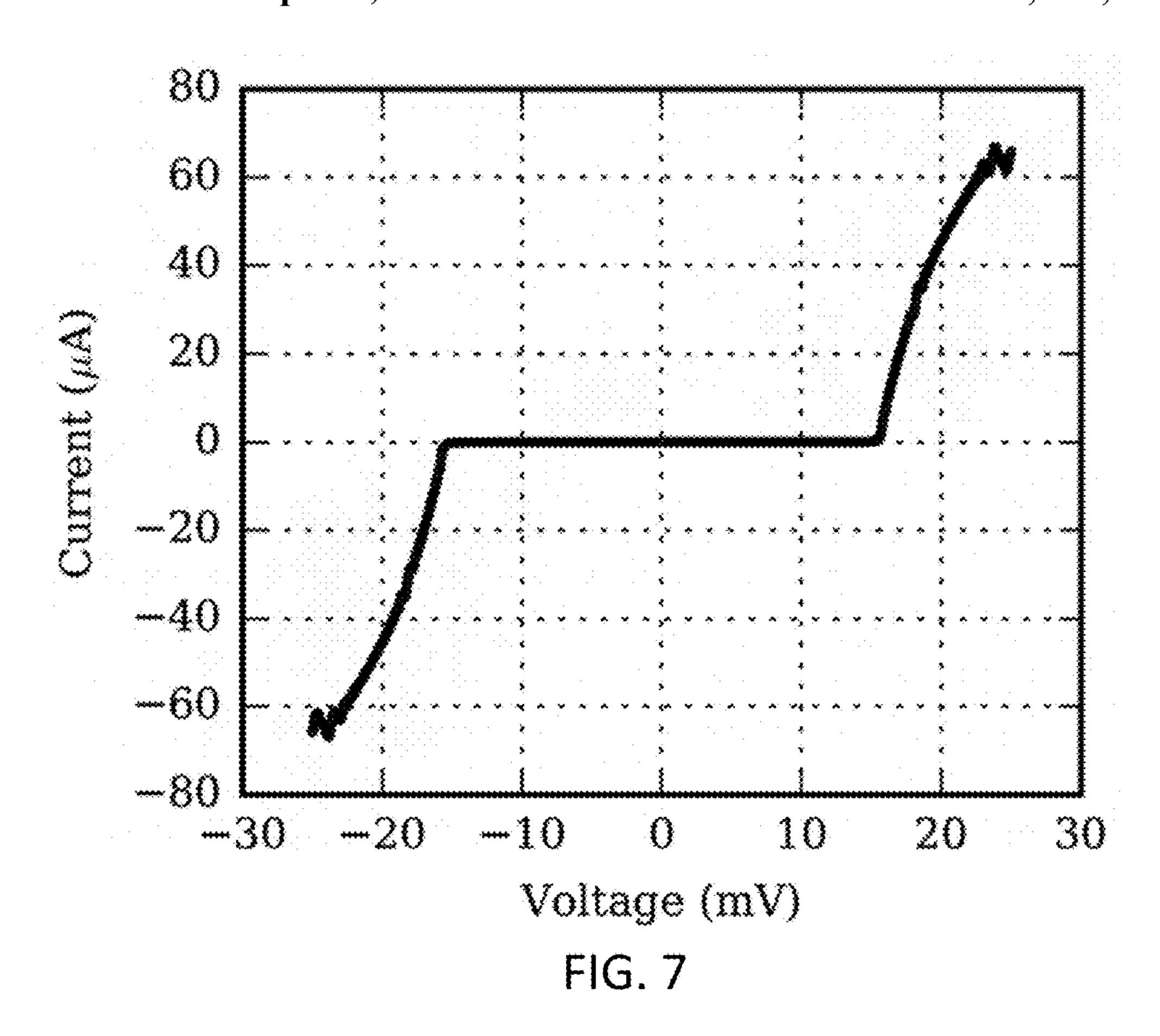

FIG. 7 shows I-V characteristics of InOx based QPSJ simulated in WRSPICE with  $V_c$ =14.7 mV, R=300 k $\Omega$ , L=2.8 nH, according to one embodiment of the present invention.

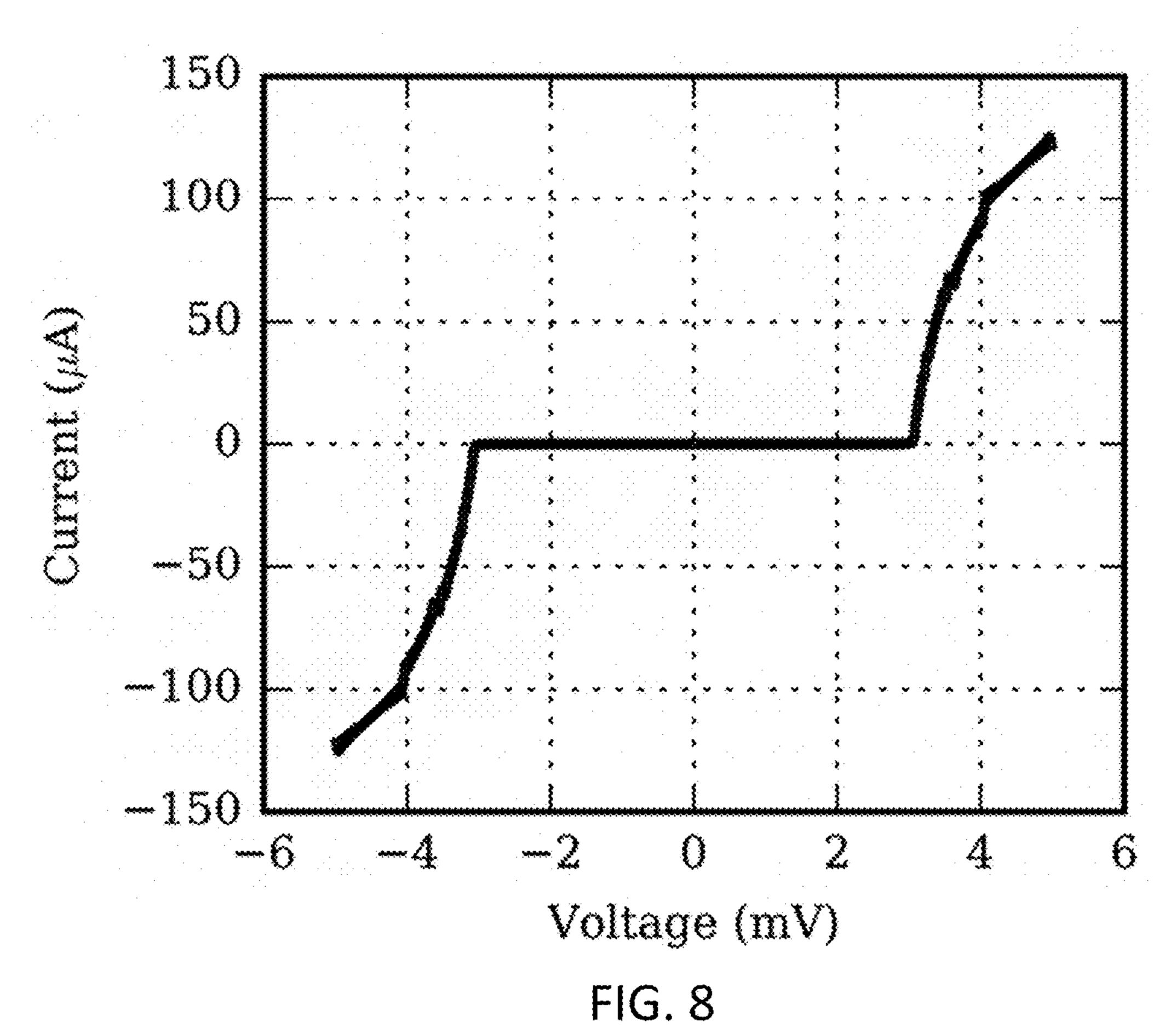

FIG. 8 shows I-V characteristics of NbN based QPSJ simulated in WRSPICE with  $V_c$ =2.94 mV, R=37.2 k $\Omega$ , L=14.24 nH, according to one embodiment of the present invention.

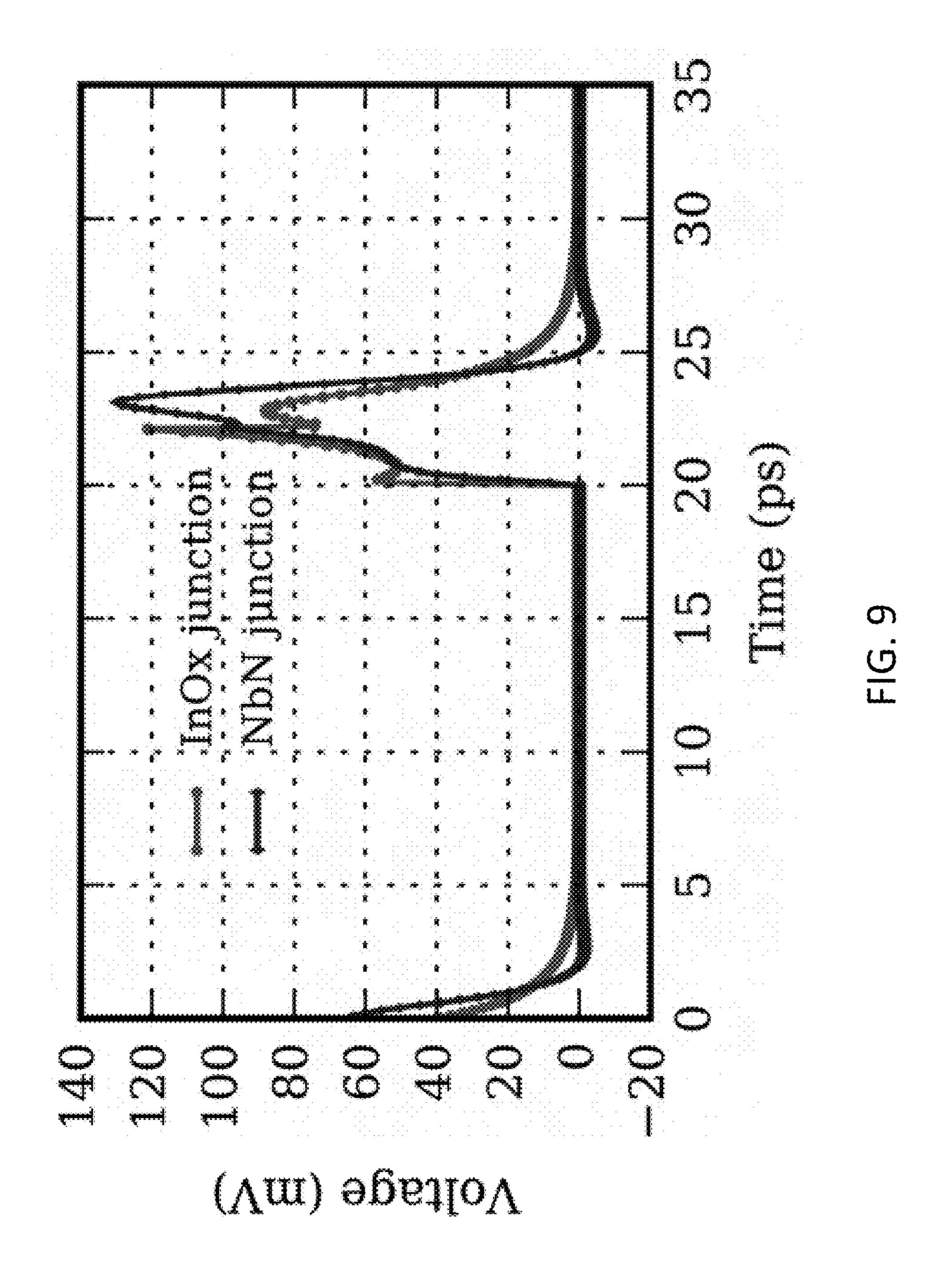

FIG. 9 shows switching characteristics of a QPSJ according to one embodiment of the present invention, which demonstrates a quantized-area current pulse (with a value=2e) for charge-based logic for two material systems.

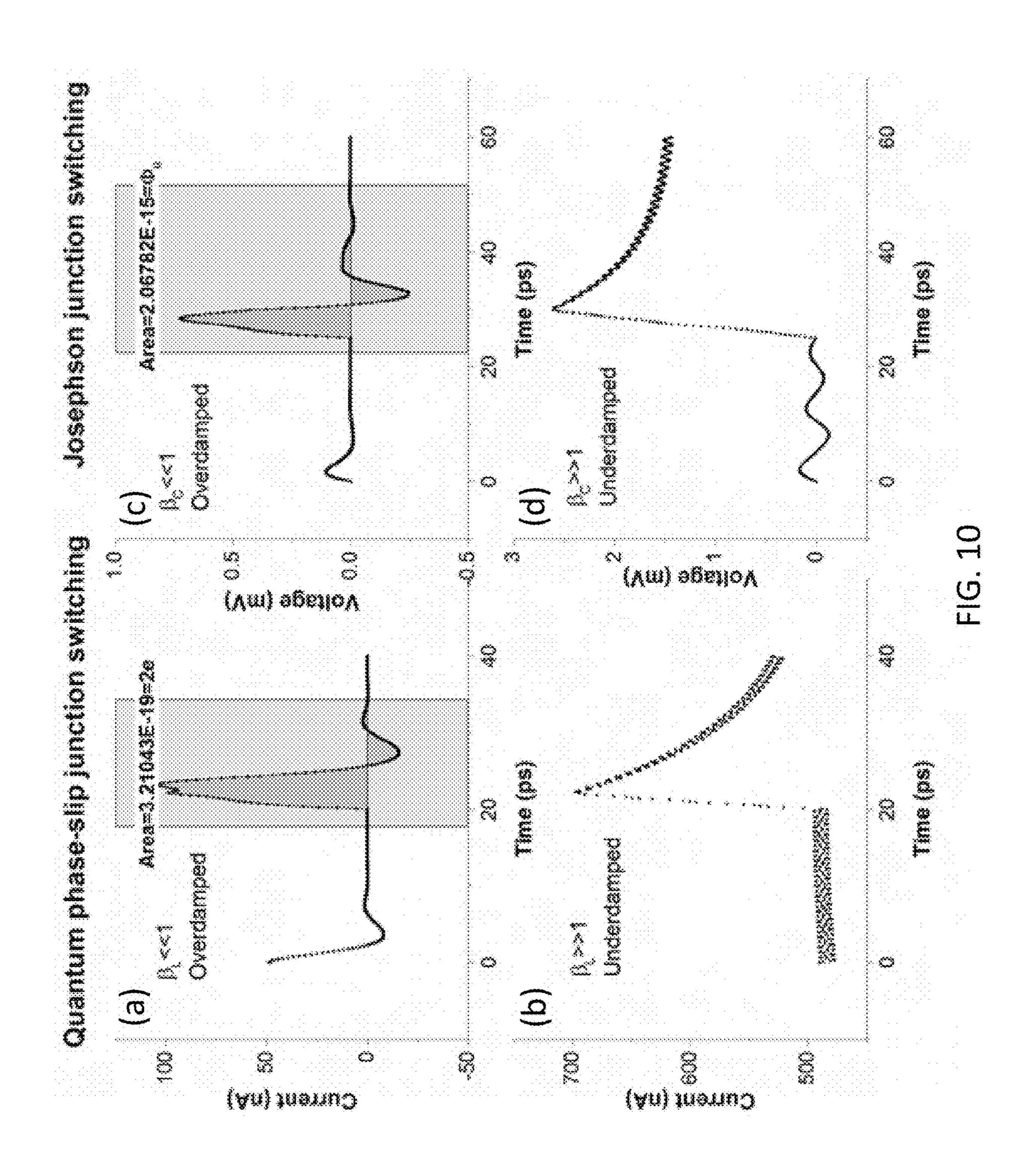

FIG. 10 shows switching dynamics of QPSJ (a) and (b), and of JJ (c) and (d).

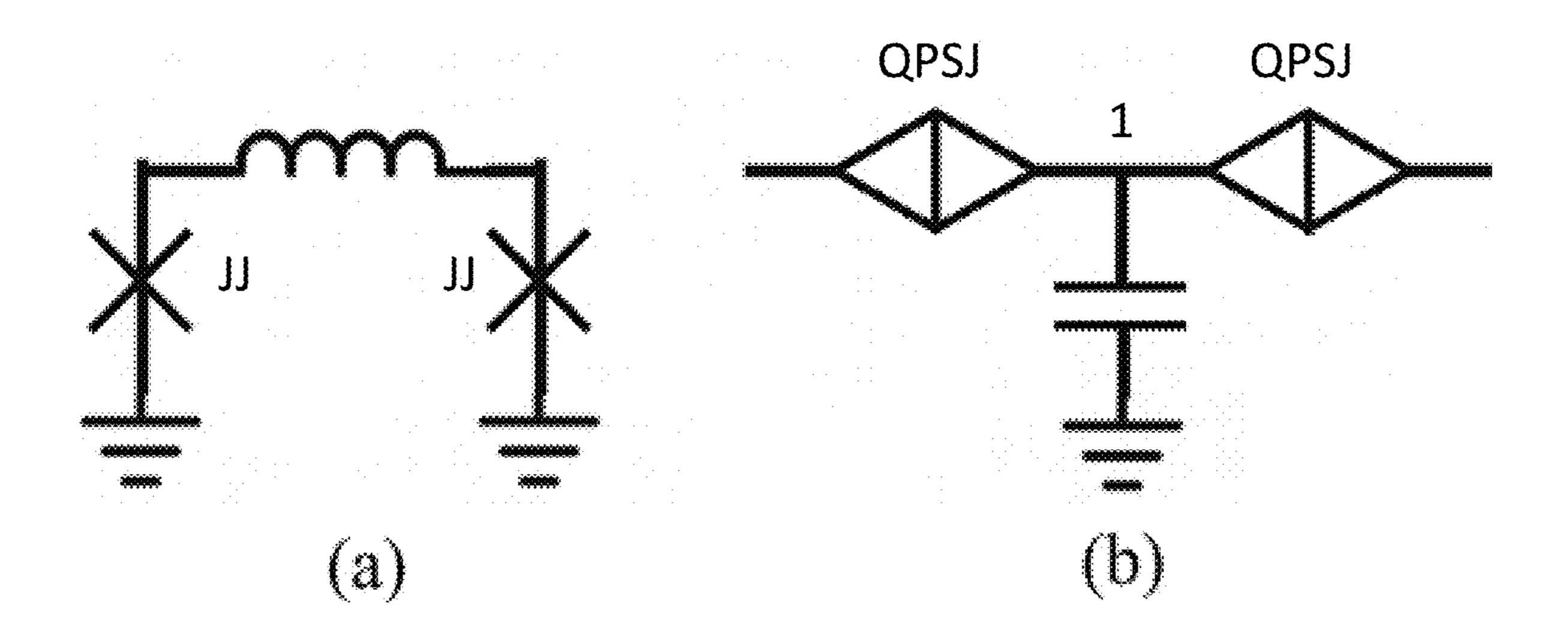

FIG. 11 shows rapid single-flux-quantum (RSFQ) and QPSJ based logic: (a) loop storing flux  $\Phi_0$  in RSFQ based logic, (b) and (c) island storing charge 2e in QPSJ based logic according to one embodiment of the present invention.

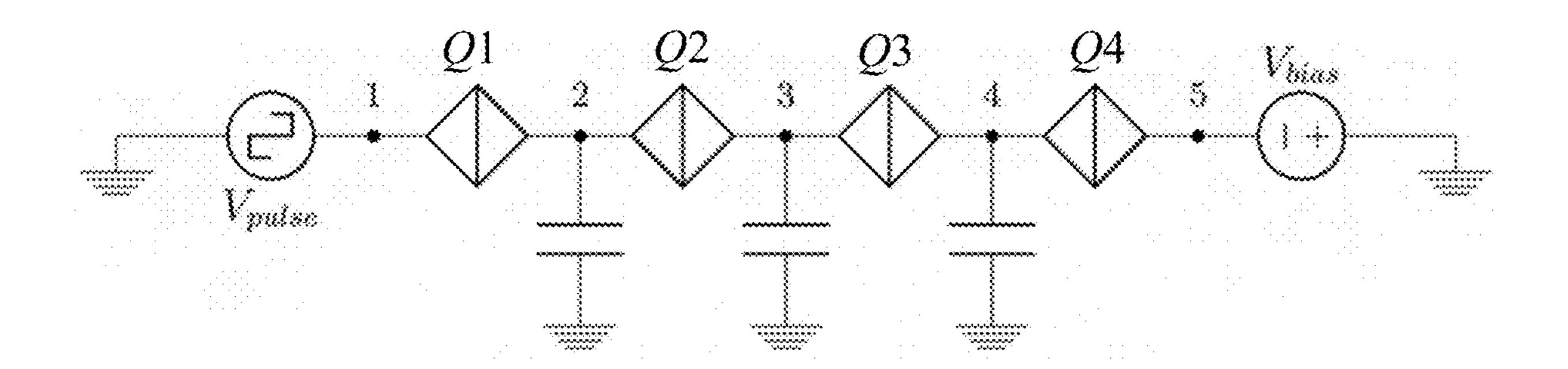

FIG. 12 shows a QPSJ transmission line comprising a pluarity of QPSJs with a DC voltage bias of  $4\times0.7V_C$  and pulse input signal according to one embodiment of the present invention, where  $V_C$  is the critical voltage of each of the junctions. Hereinafter, a QPSJ may be denoted by a capital letter "Q" in the disclosure.

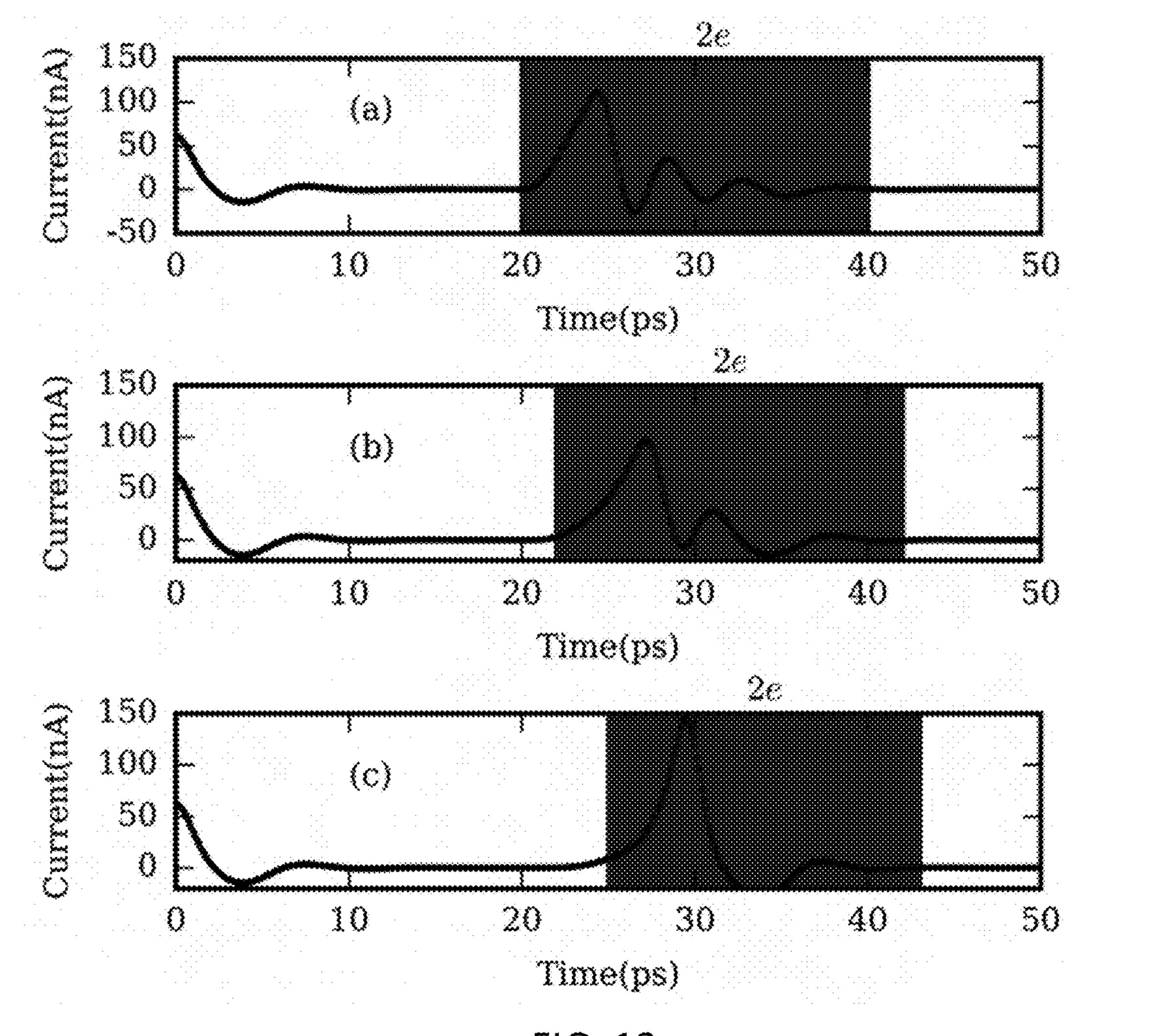

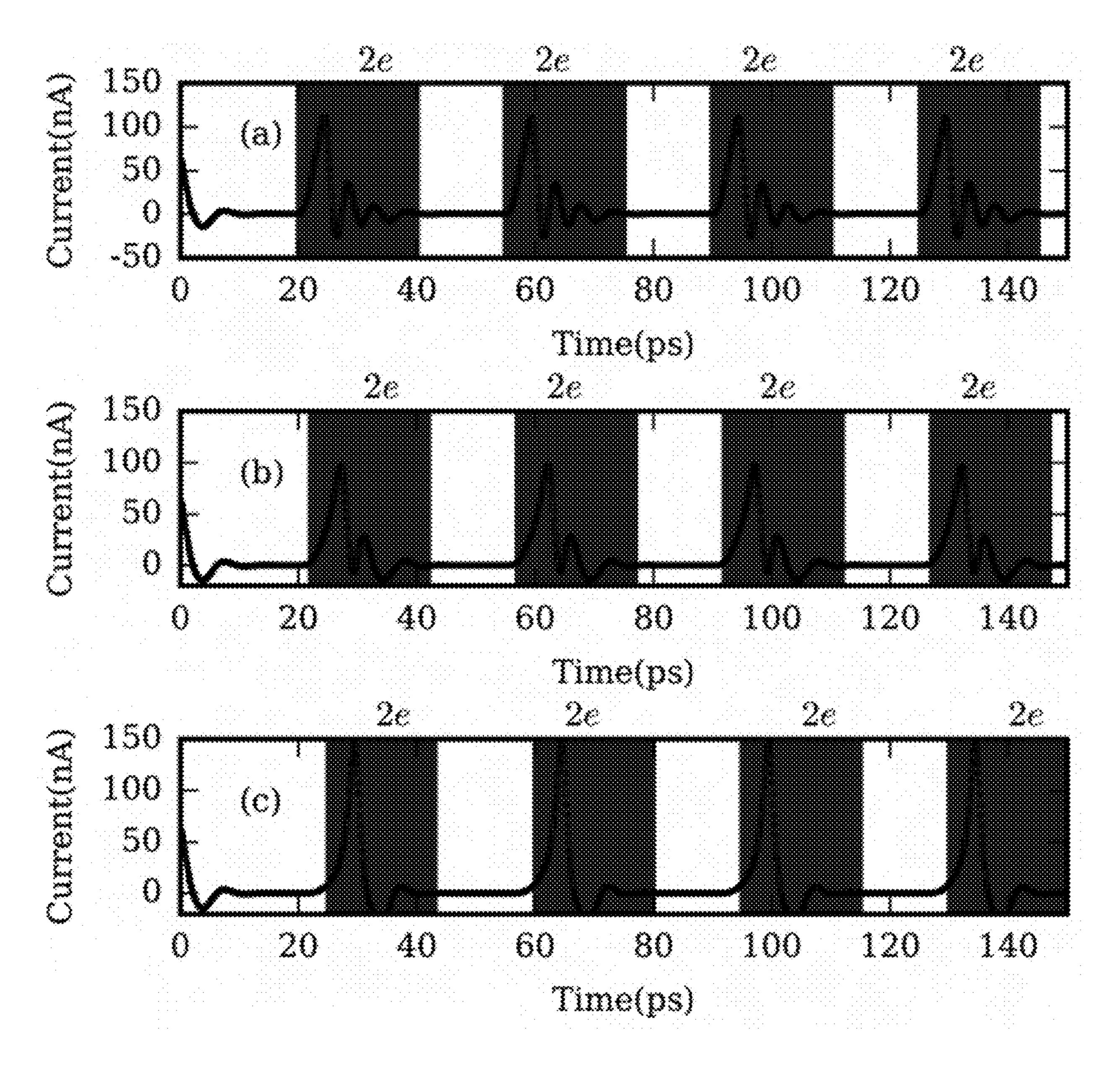

FIG. 13 shows simulation results of the QPSJ transmission line illustrating charge 2e traveling across islands according to one embodiment of the present invention: (a) current at node 1, (b) current at node 2, and (c) current at node 3. The QPSJ transmission line is shown in FIG. 12.

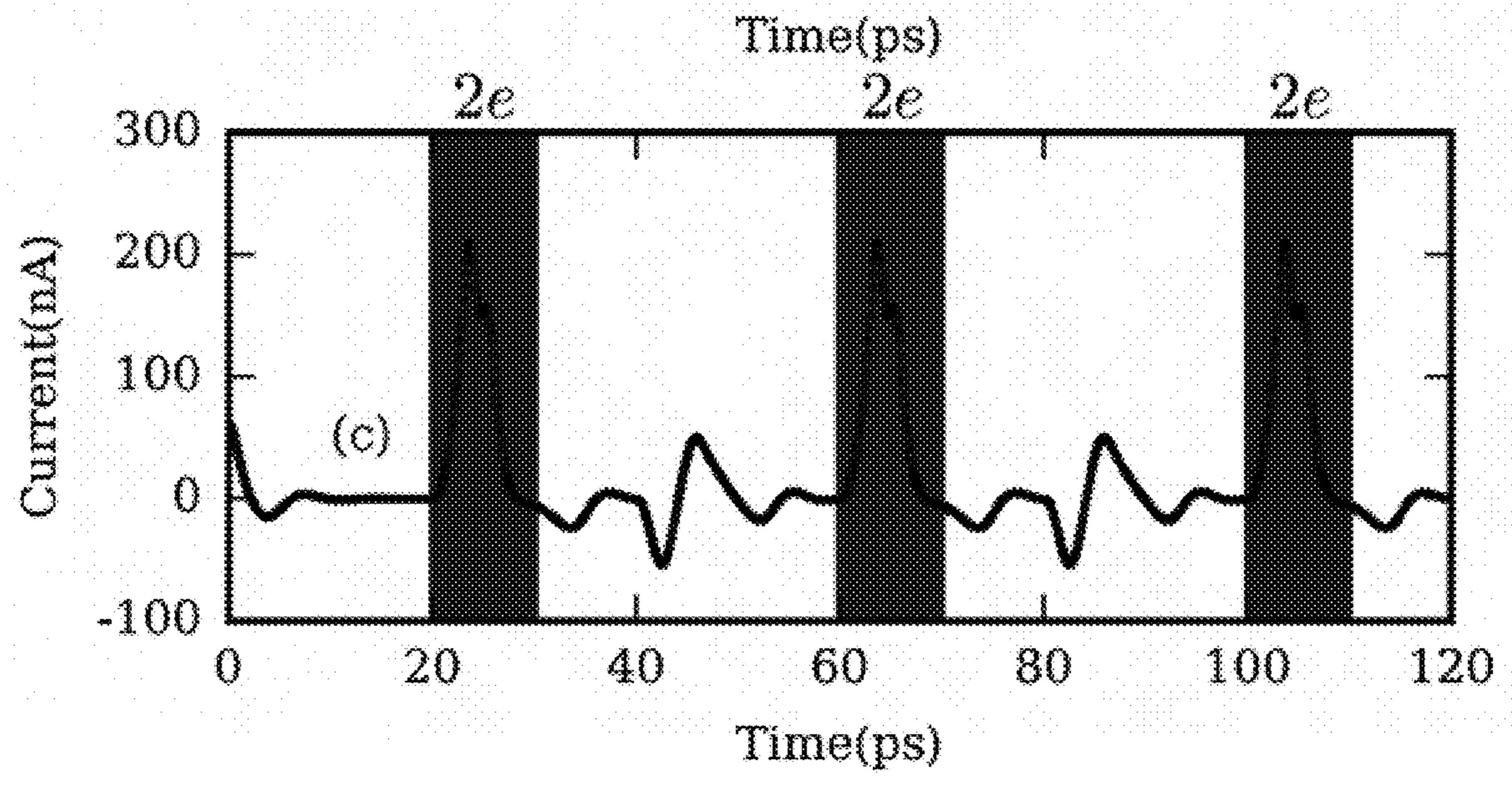

FIG. 14 shows simulation results of the QPSJ transmission line with multiple pulses according to one embodiment of the present invention: (a) current at node 1, (b) current at node 2, and (c) current at node 3. The QPSJ transmission line is shown in FIG. 12.

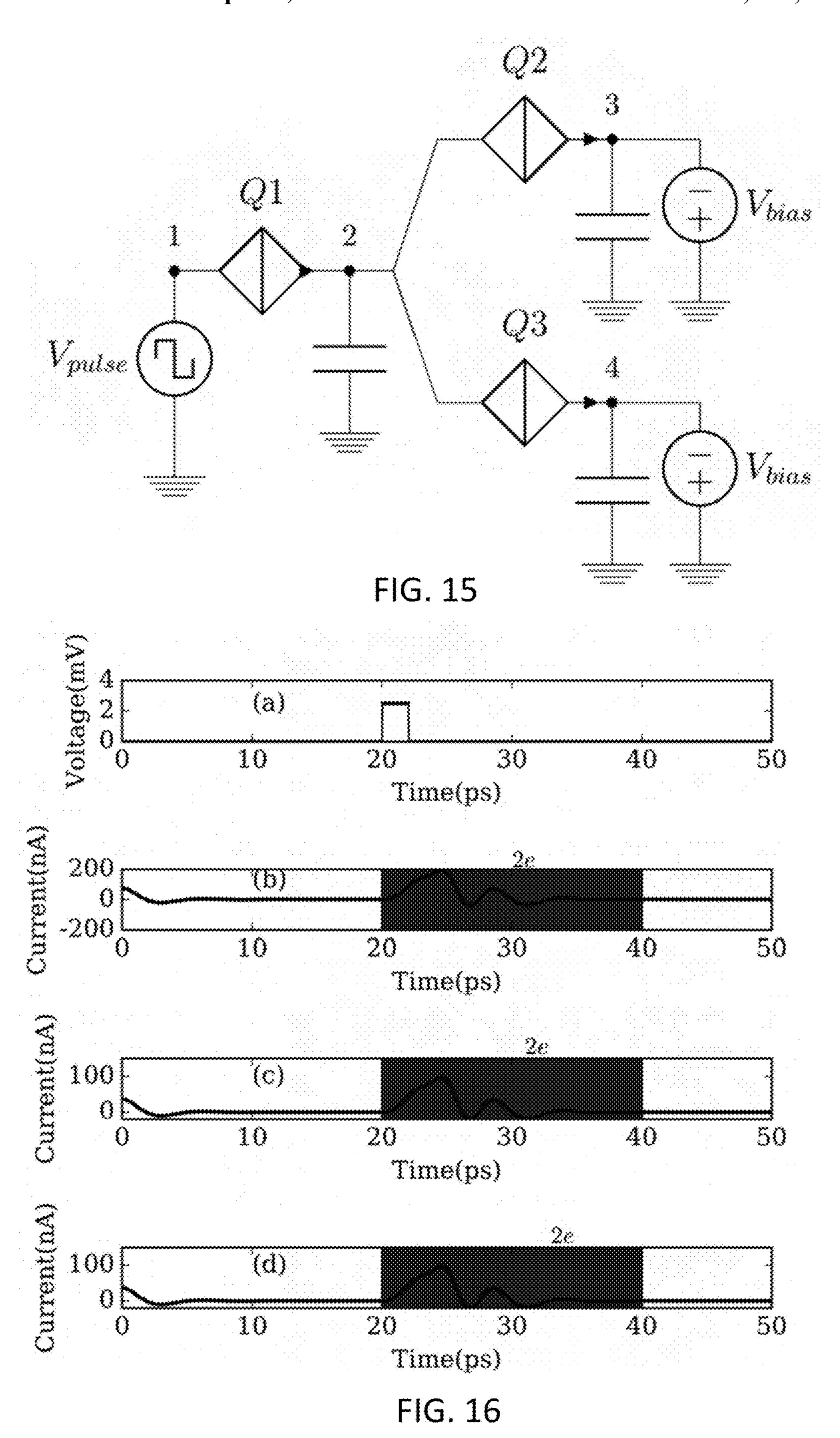

FIG. 15 shows a pulse splitter according to one embodiment of the present invention, where the critical voltage of Q1 is 0.7 Vc, and the critical voltages of Q2 and Q3 are Vc.

FIG. 16 shows simulation result of the pulse splitter circuit shown in FIG. 15 according to one embodiment of

the present invention: (a) total input voltage signal at node 1, (b) current at node 1, (c) current at node 3, and (d) current at node 4.

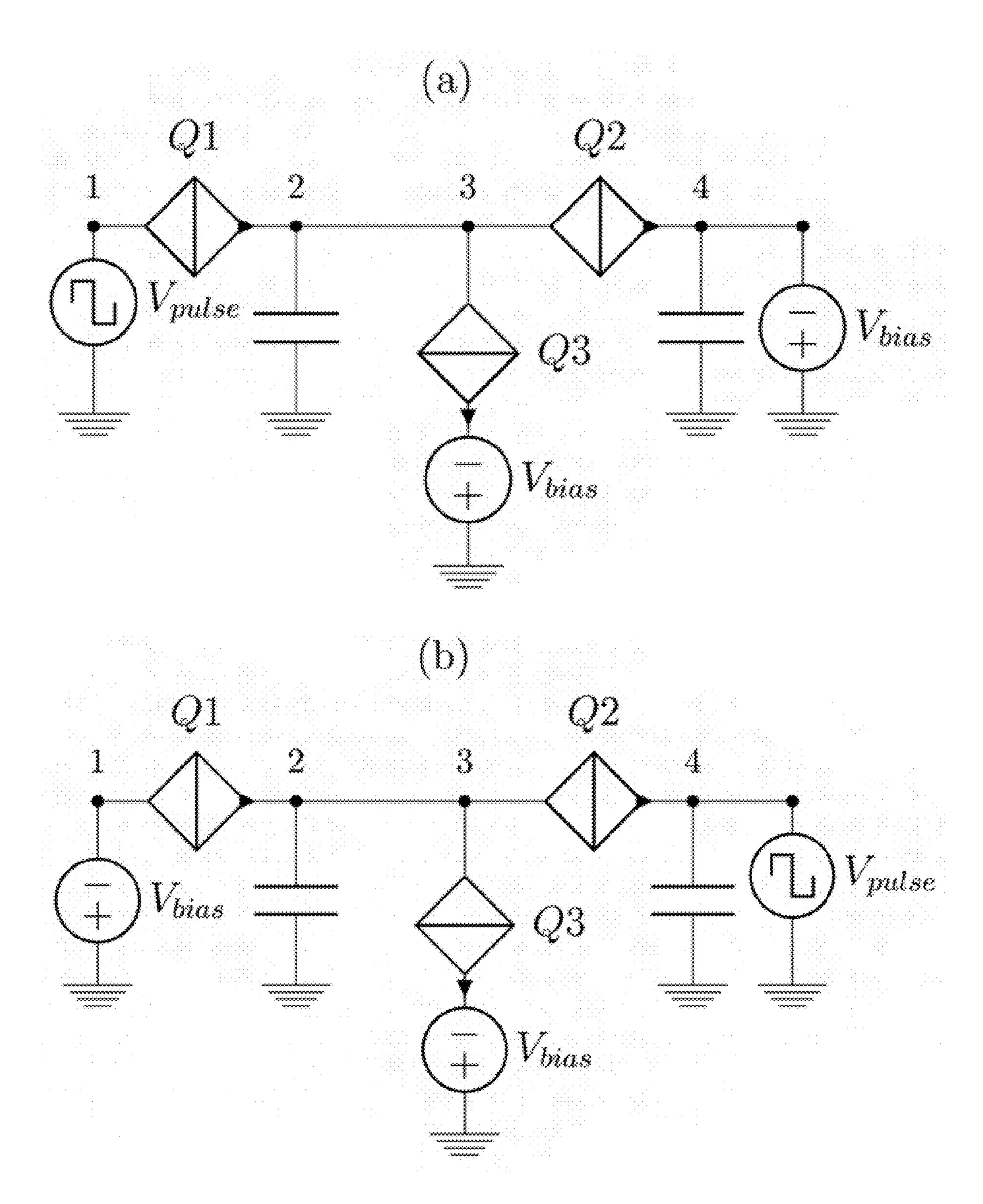

FIG. 17 shows two buffer circuits (a) and (b) showing current flow situations in both directions according to embodiments of the present invention, where the critical voltage of Q1=0.7 Vc, the critical voltage of Q2 is Vc, and the critical voltage of Q3 is 1.4 Vc.

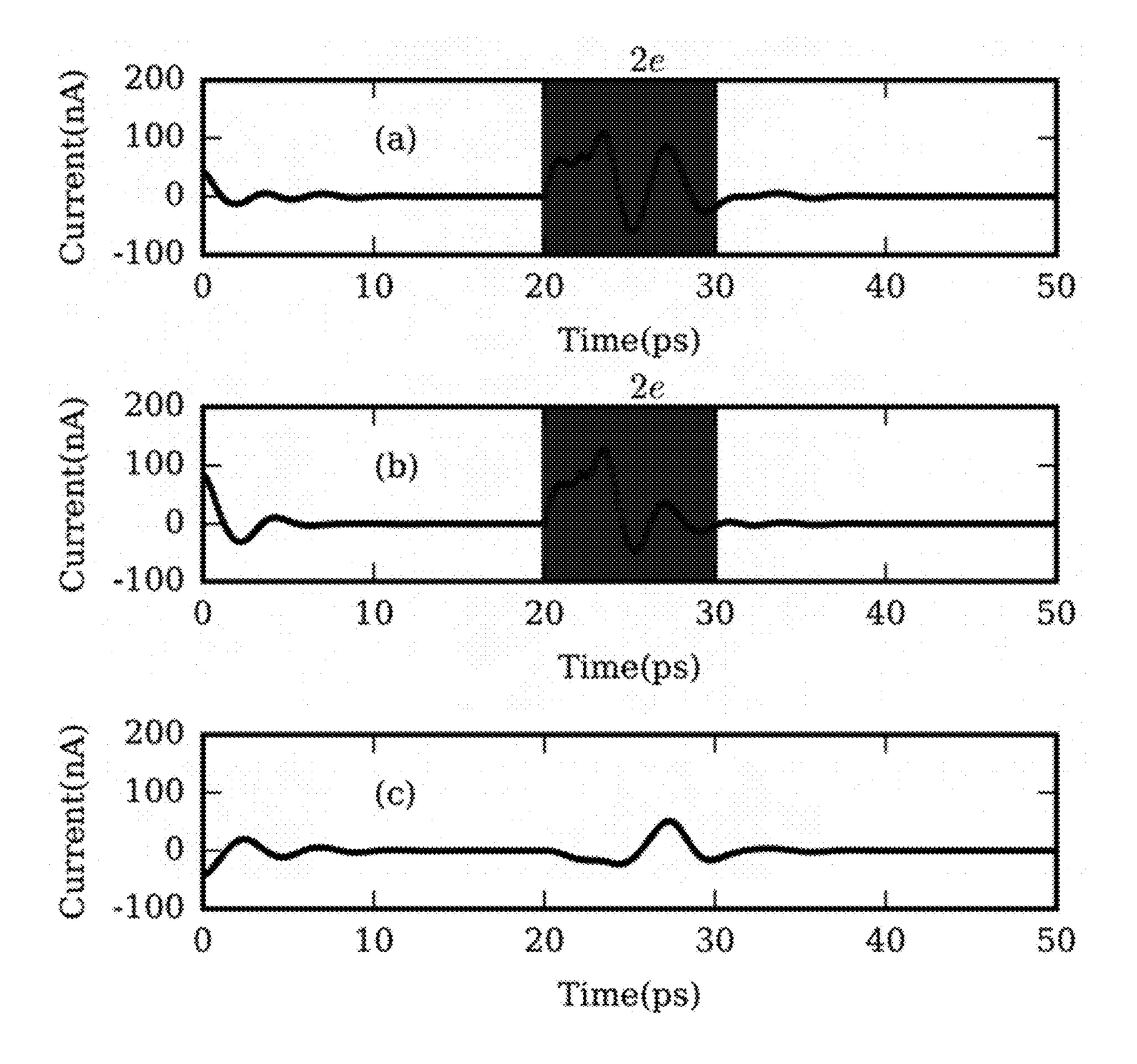

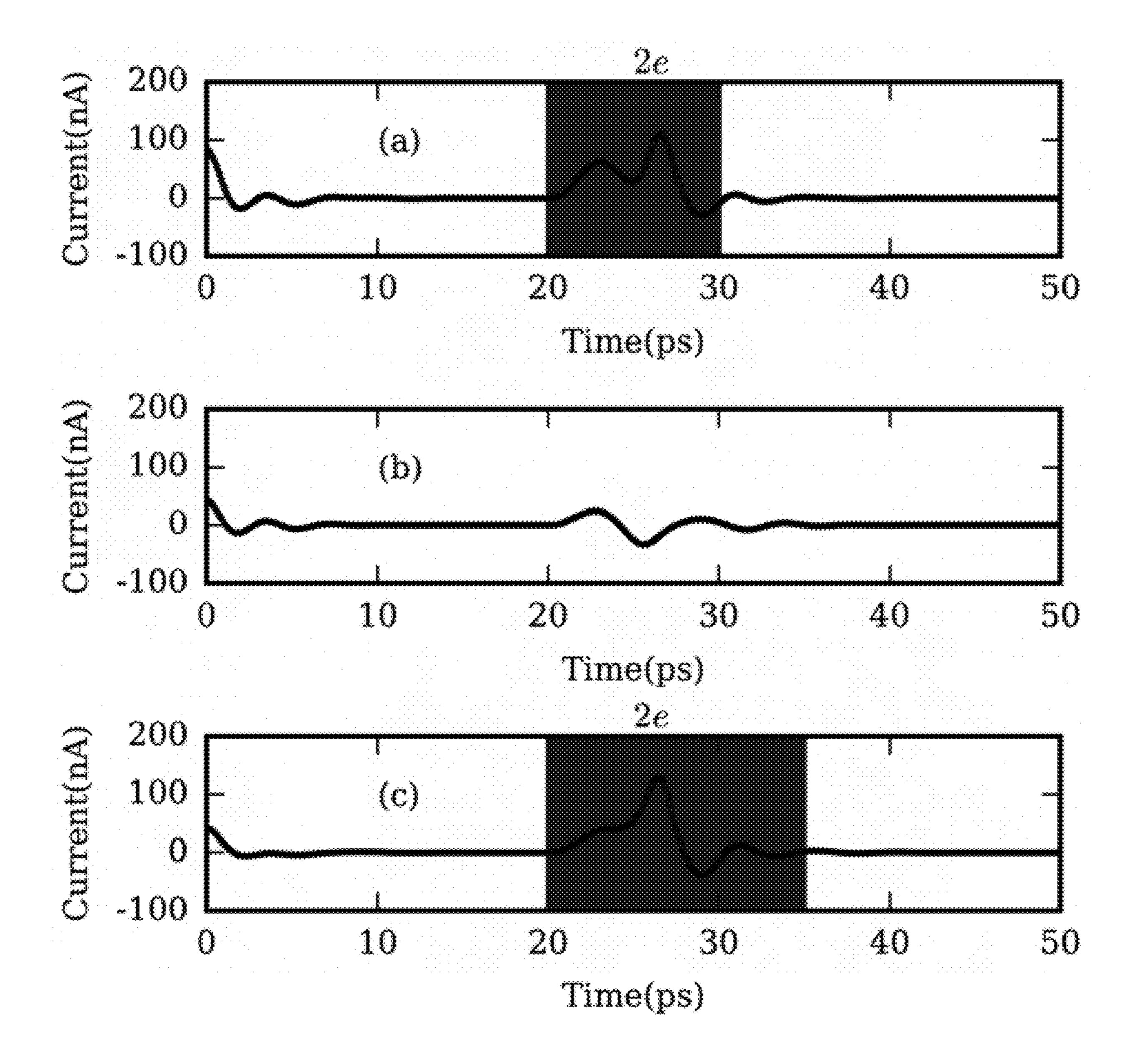

FIG. 18 shows simulation results of the buffer circuit shown in FIG. 17(a) according to one embodiment of the present invention: (a) signal at node 1, (b) signal through Q3, and (c) signal at node 4.

FIG. **19** shows simulation results of the buffer circuit shown in FIG. **17**(*b*) according to one embodiment of the present invention: (a) signal at node 1, (b) signal through Q**3**, and (c) signal at node 4.

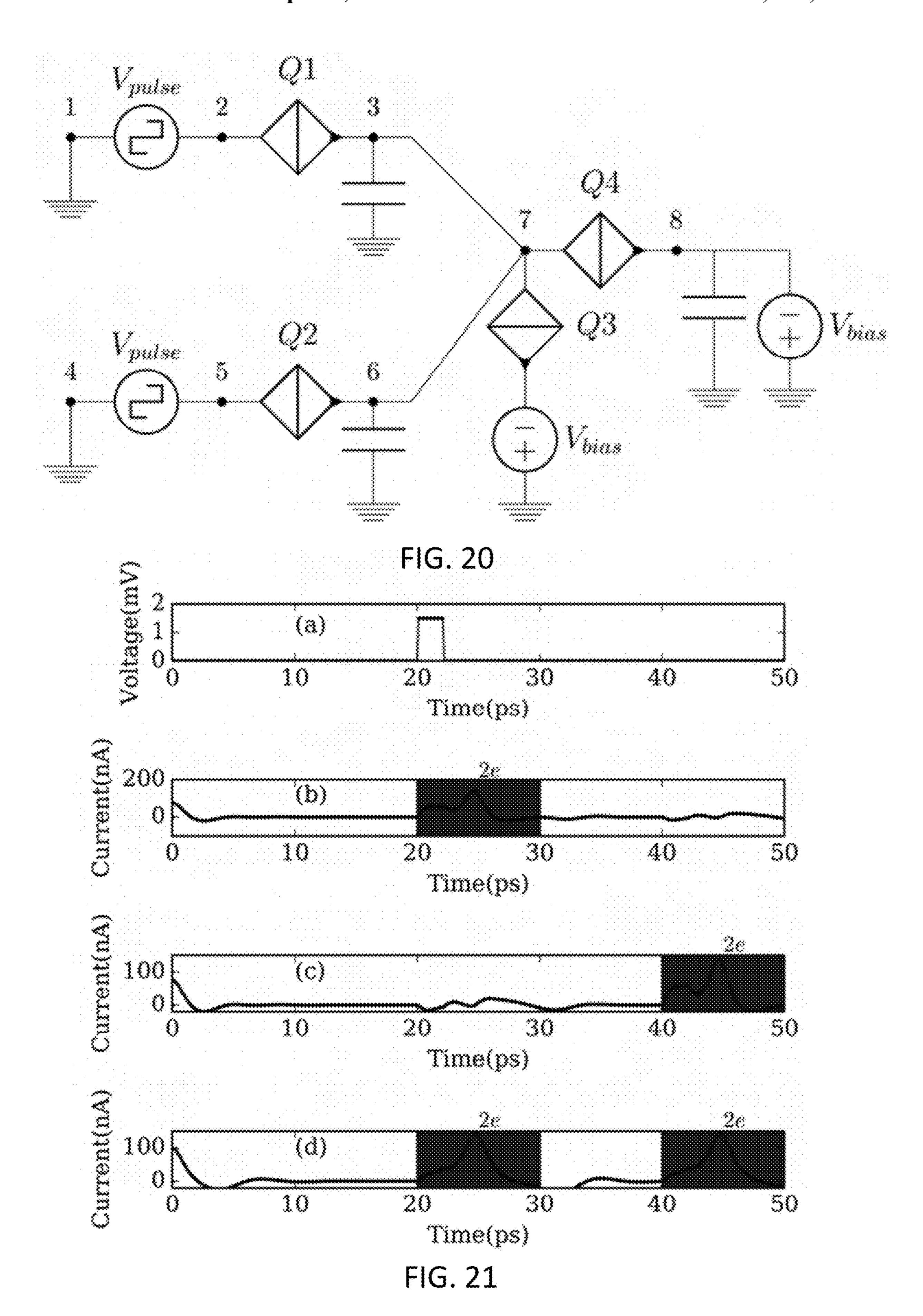

FIG. 20 shows a QPSJ merger according to one embodiment of the present invention, where the critical voltages of Q1 and Q2 are 1.4 Vc, the critical voltages of Q3 is Vc, and 20 the critical voltages of Q4 is 0.7 Vc.

FIG. 21 shows simulation results of the QPSJ merger shown in FIG. 20 according to one embodiment of the present invention: (a) total input voltage signal at node 1, (b) current pulse at node 3, (c) current pulse at node 6, and (d) 25 output signal at node 8.

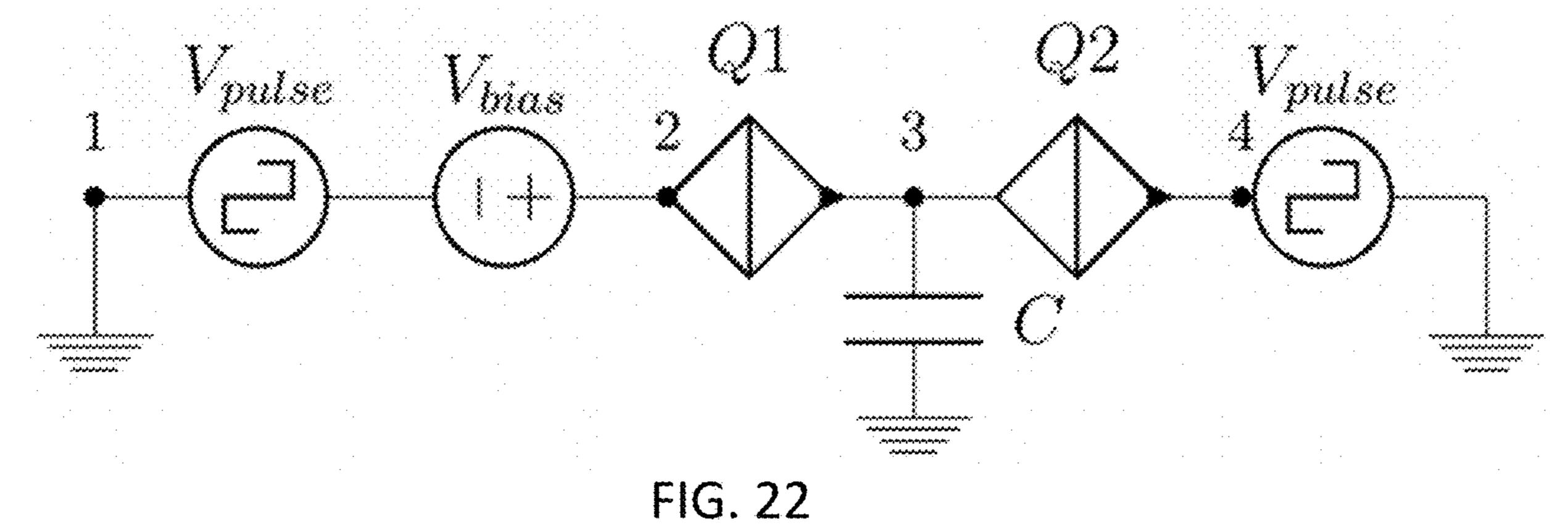

FIG. 22 shows an RS flip-flop using QPSJs forming an island with a capacitor according to one embodiment of the present invention, where the critical voltages of Q1 and Q2 are  $V_C$ , and  $C=1.5V_C/2e$ .

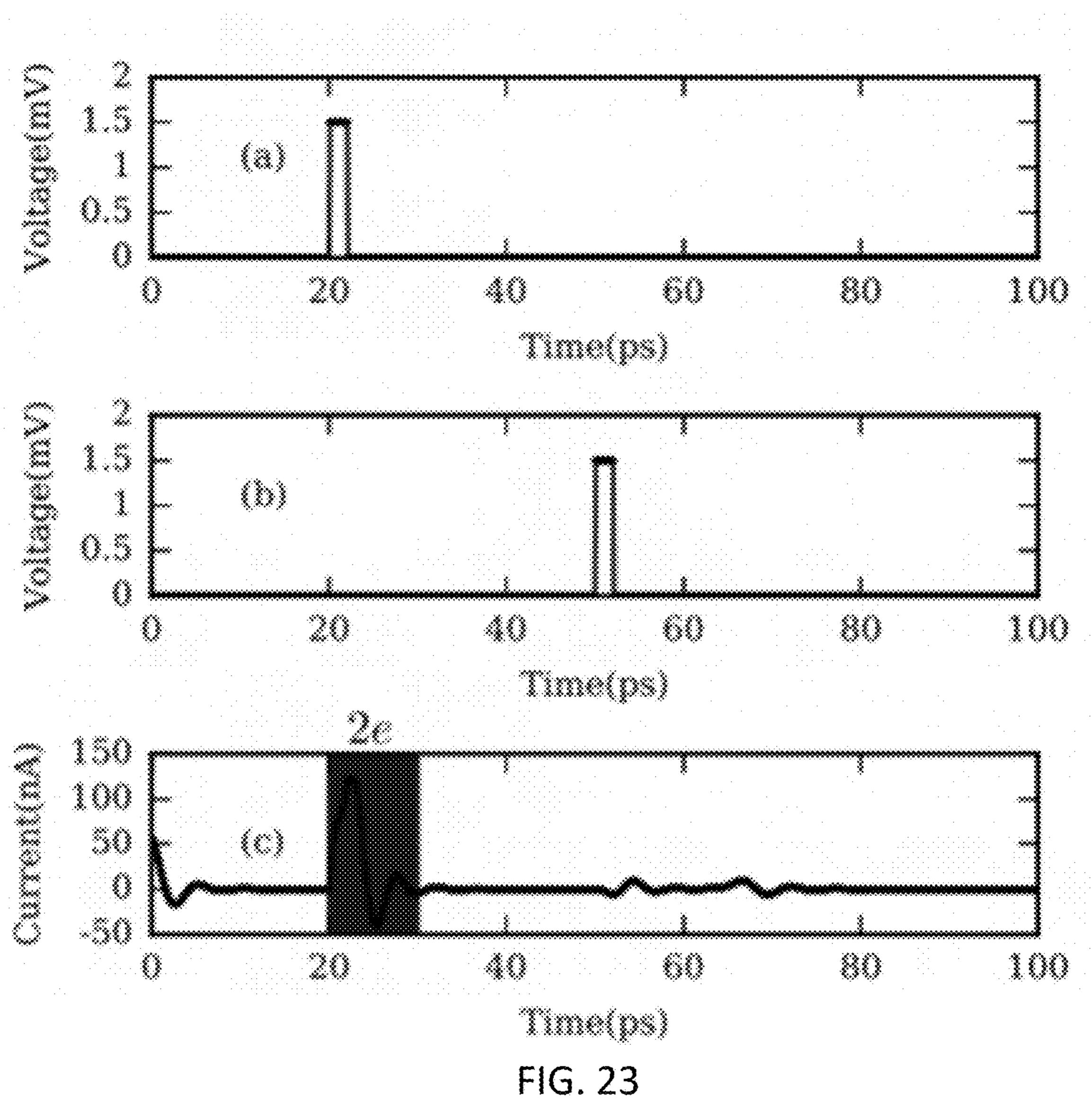

FIG. 23 shows simulation results for RS flip-flop circuit shown in FIG. 22 according to one embodiment of the present invention: (a) input voltage pulse at SET, i.e., node 1, (b) input voltage pulse at RESET, i.e., node 4, and (c) output current pulse at node 4.

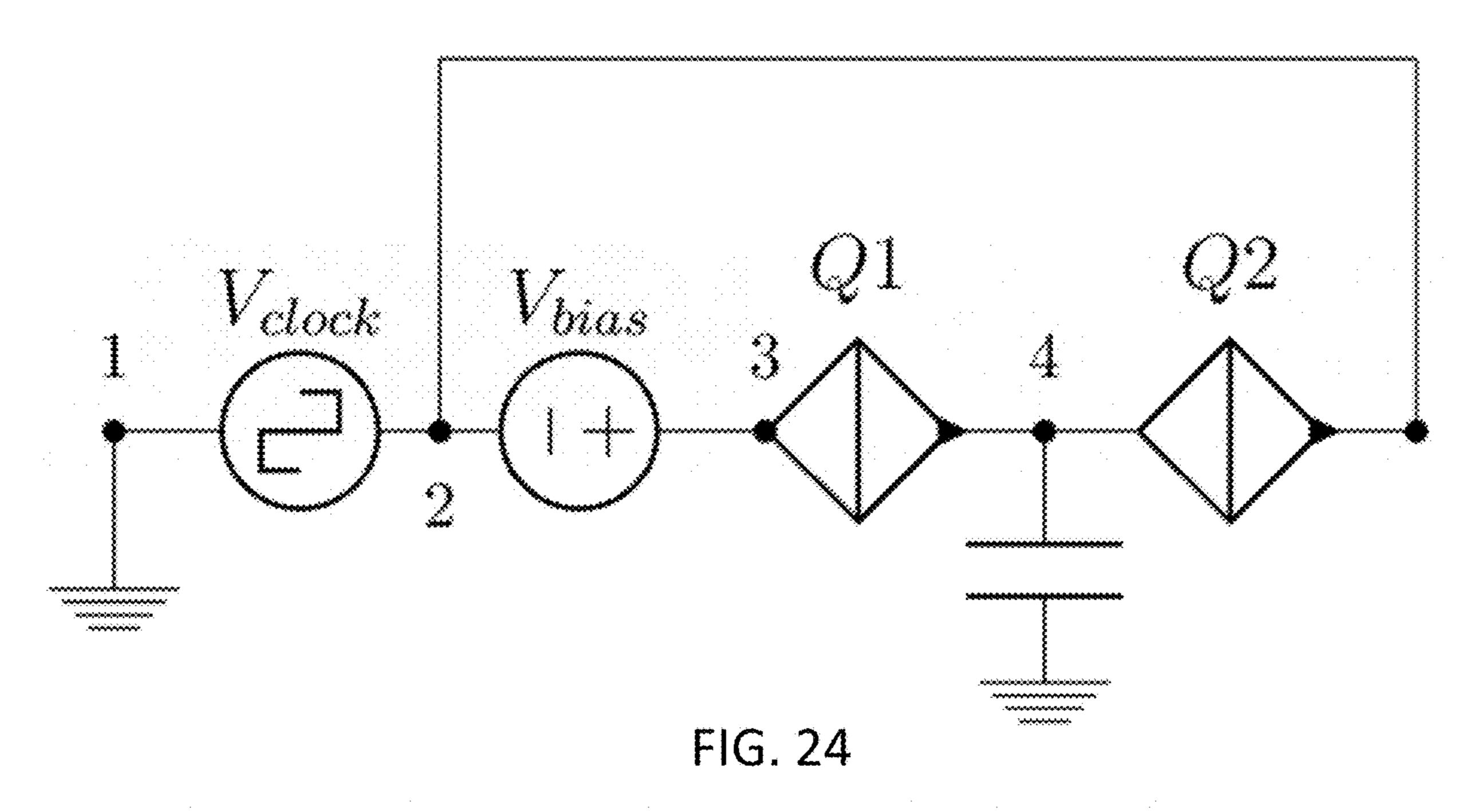

FIG. 24 shows a T flip-flop circuit obtained from QPSJ island and clock input according to one embodiment of the present invention, where the critical voltages of Q1 and Q2 is  $V_C$ , and  $C=1.5V_C/2e$ .

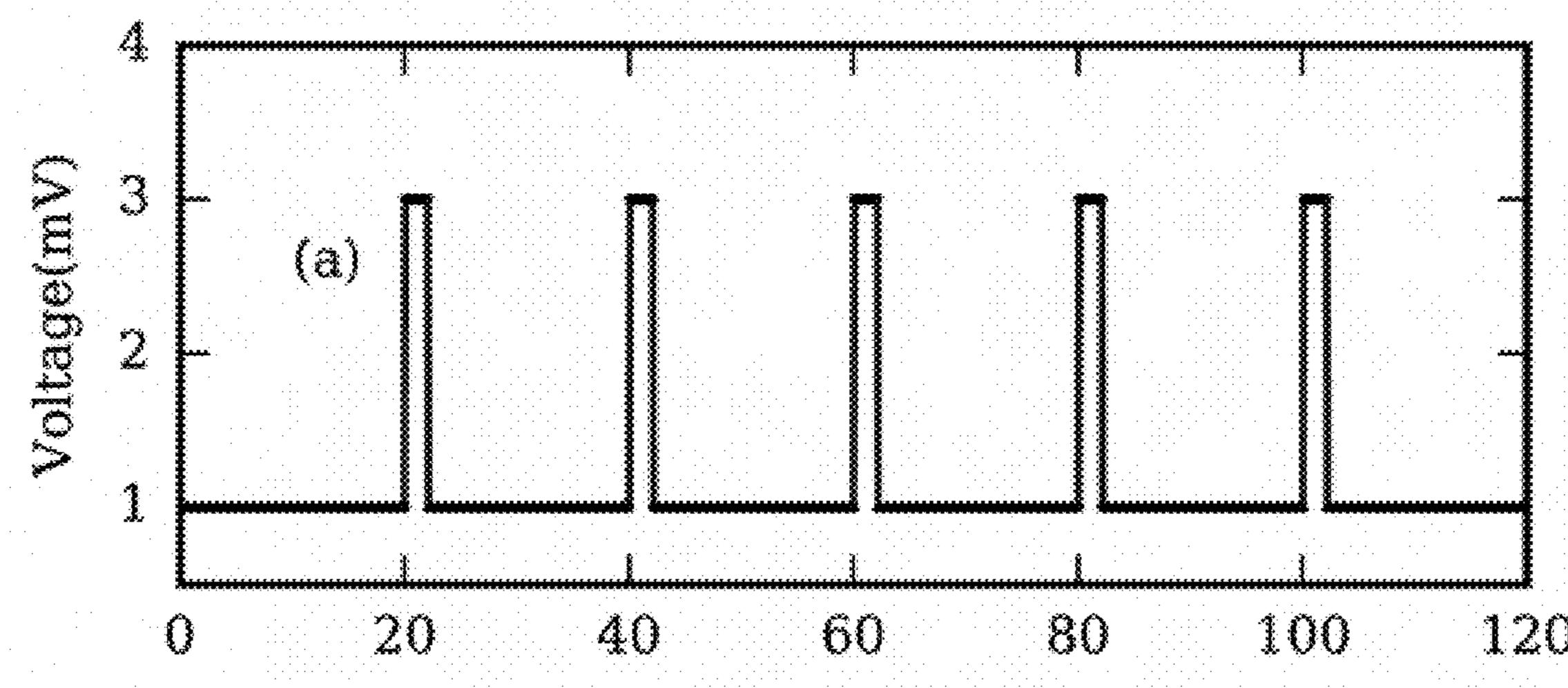

FIG. 25 shows simulation results for the T flip-flop shown 40 in FIG. 24 according to one embodiment of the present invention: (a) clock signal input at node 1, and (b) output current signal coming out of node 2.

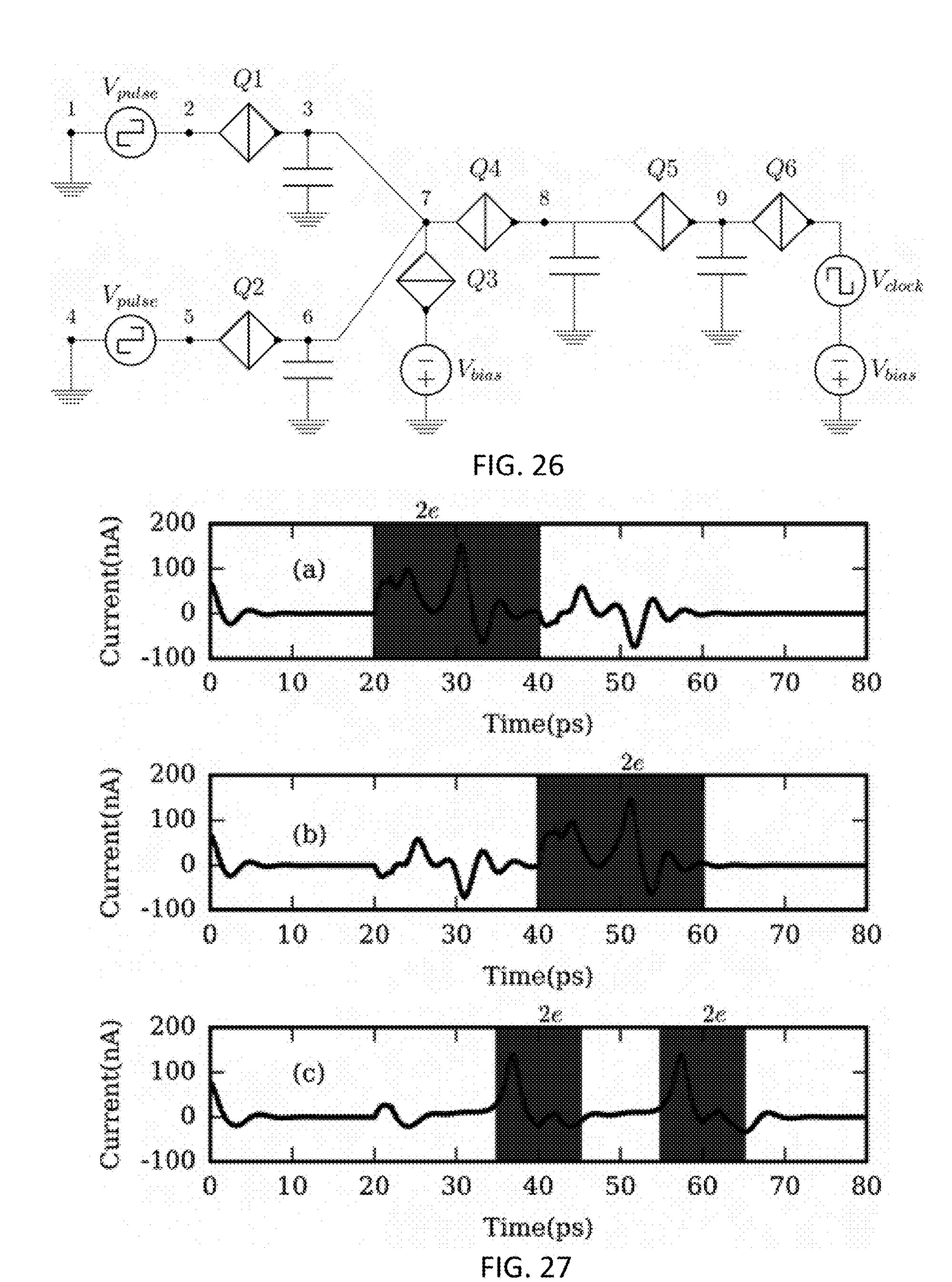

FIG. 26 shows a QPSJ based OR gate formed by combining a confluence buffer and an RS flip-flop according to 45 one embodiment of the present invention.

FIG. 27 shows simulation results of the OR gate implemented using QPSJs shown in FIG. 26 according to one embodiment of the present invention: (a) input current pulse at node 1, (b) input current pulse at node 2, and (c) output 50 current pulse at node 9.

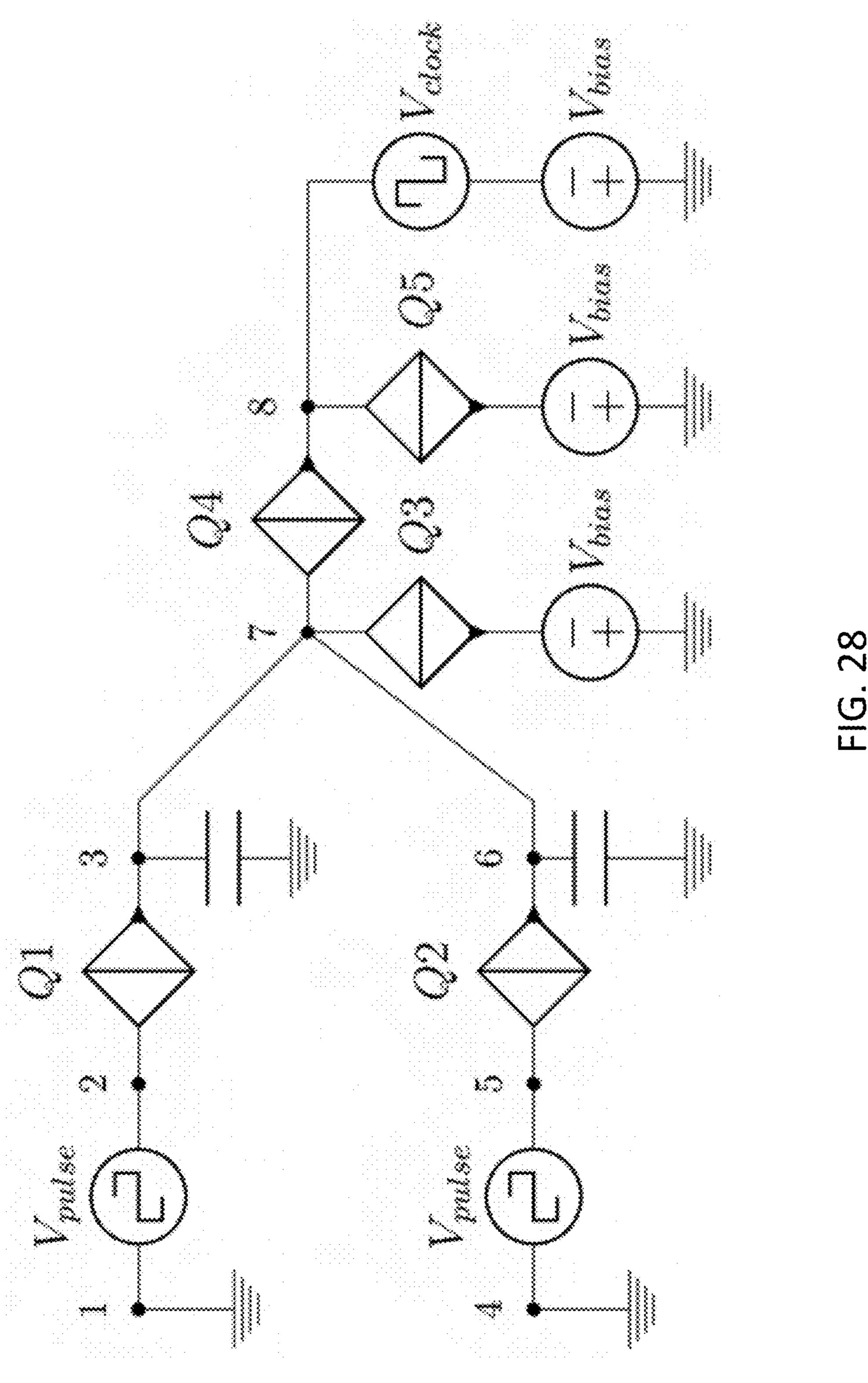

FIG. 28 shows an AND gate circuit implemented by replacing the RS flip-flop in the OR gate with a buffer circuit according to one embodiment of the present invention.

FIG. 29 shows simulation results of the AND gate implemented using QPSJs shown in FIG. 28 according to one embodiment of the present invention: (a) input current pulse at node 1, (b) input current pulse at node 2, and (c) output current pulse at node 8.

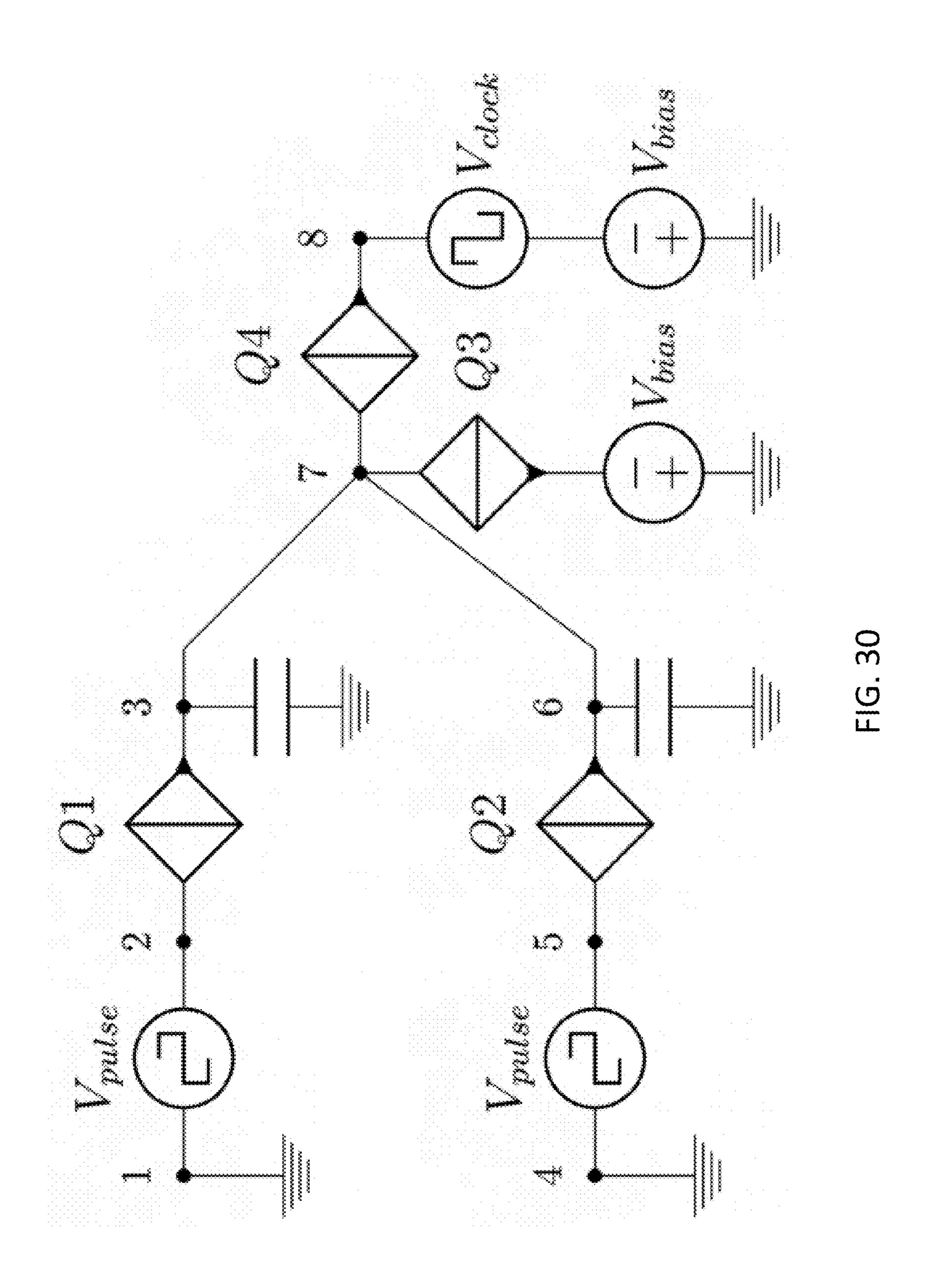

FIG. 30 shows an XOR gate circuit implemented by 60 removing the buffer circuit in the AND gate according to one embodiment of the present invention.

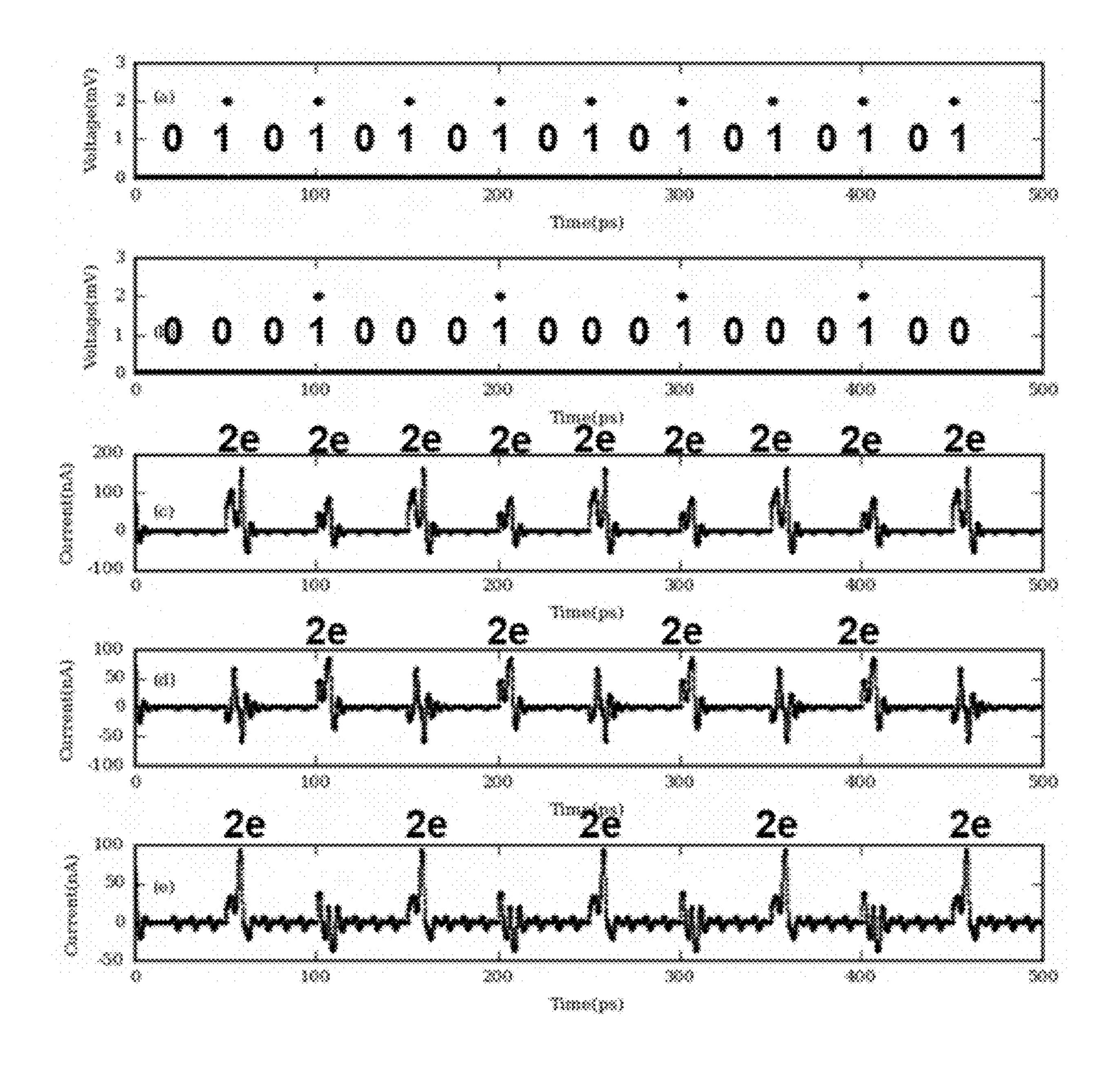

FIG. 31 shows simulation results of XOR gate implemented using QPSJs shown in FIG. 30 according to one embodiment of the present invention: (a) input current pulse 65 at node 1, (b) input current pulse at node 2, and (c) output current pulse at node 8.

8

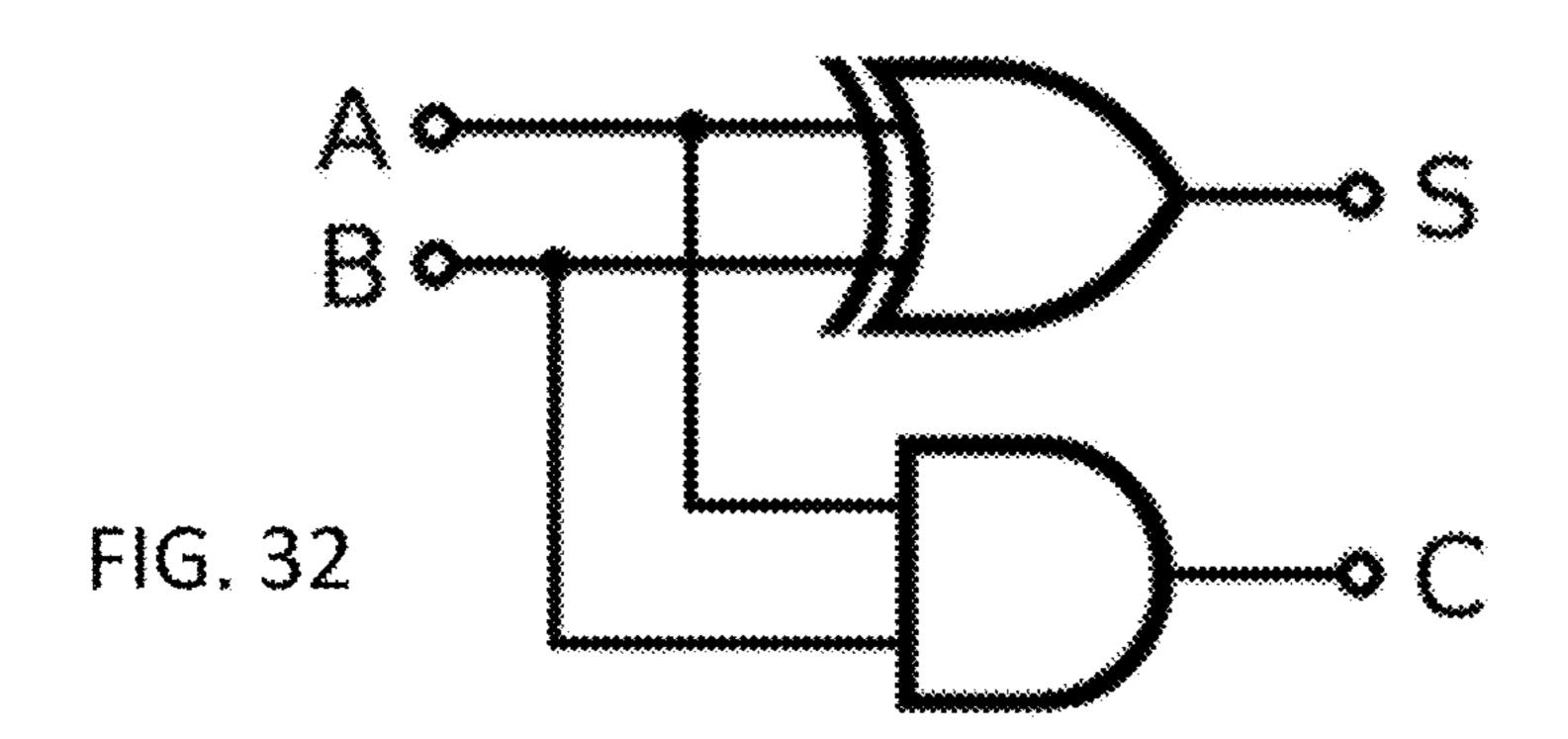

FIG. 32 shows a half-adder circuit according to one embodiment of the present invention.

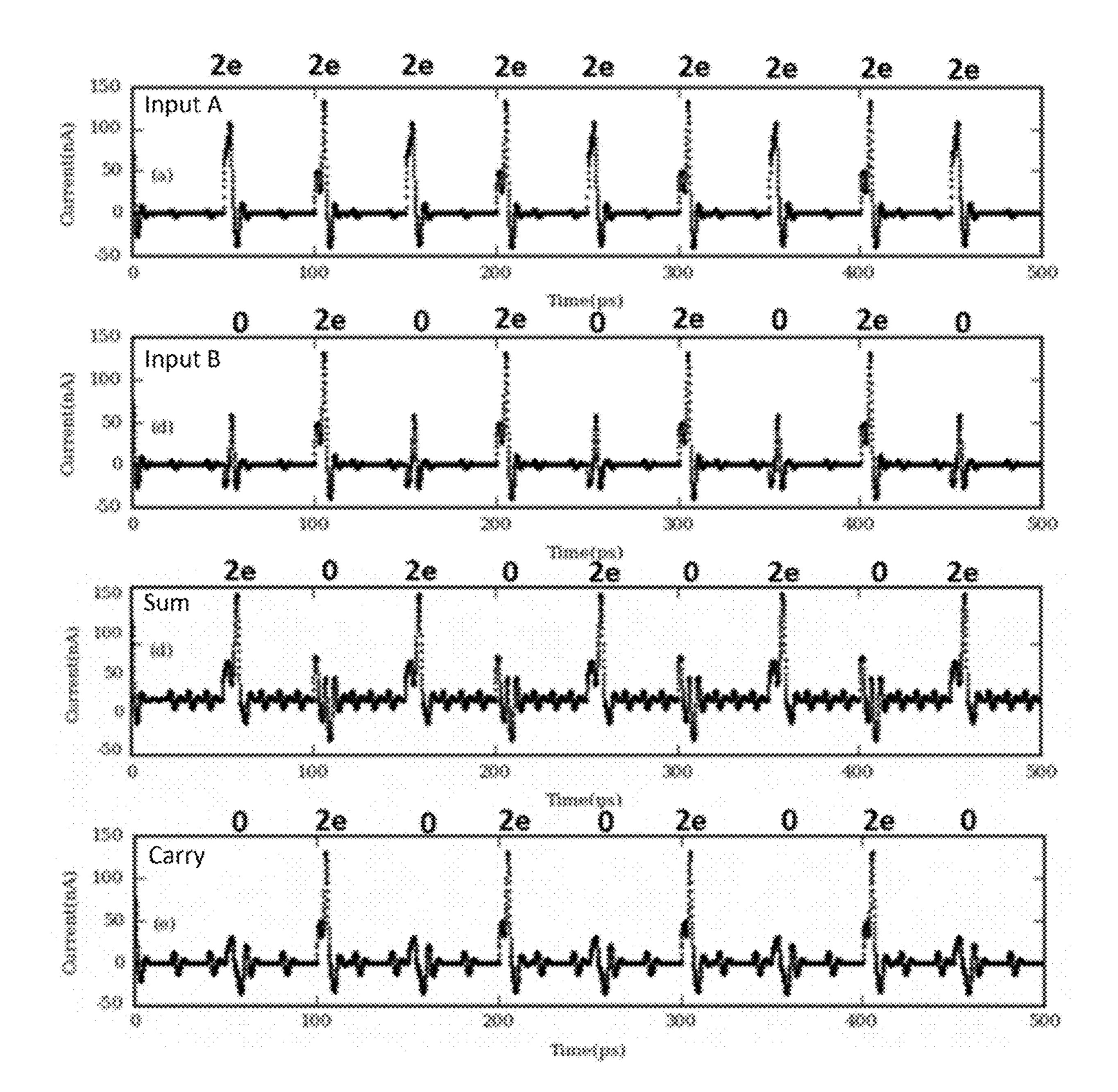

FIG. 33 shows simulation results of the half-adder using the XOR and AND gates shown in FIG. 32 according to one embodiment of the present invention, (a) input A, (b) input B, (c) sum (node S), and (d) carry (node C).

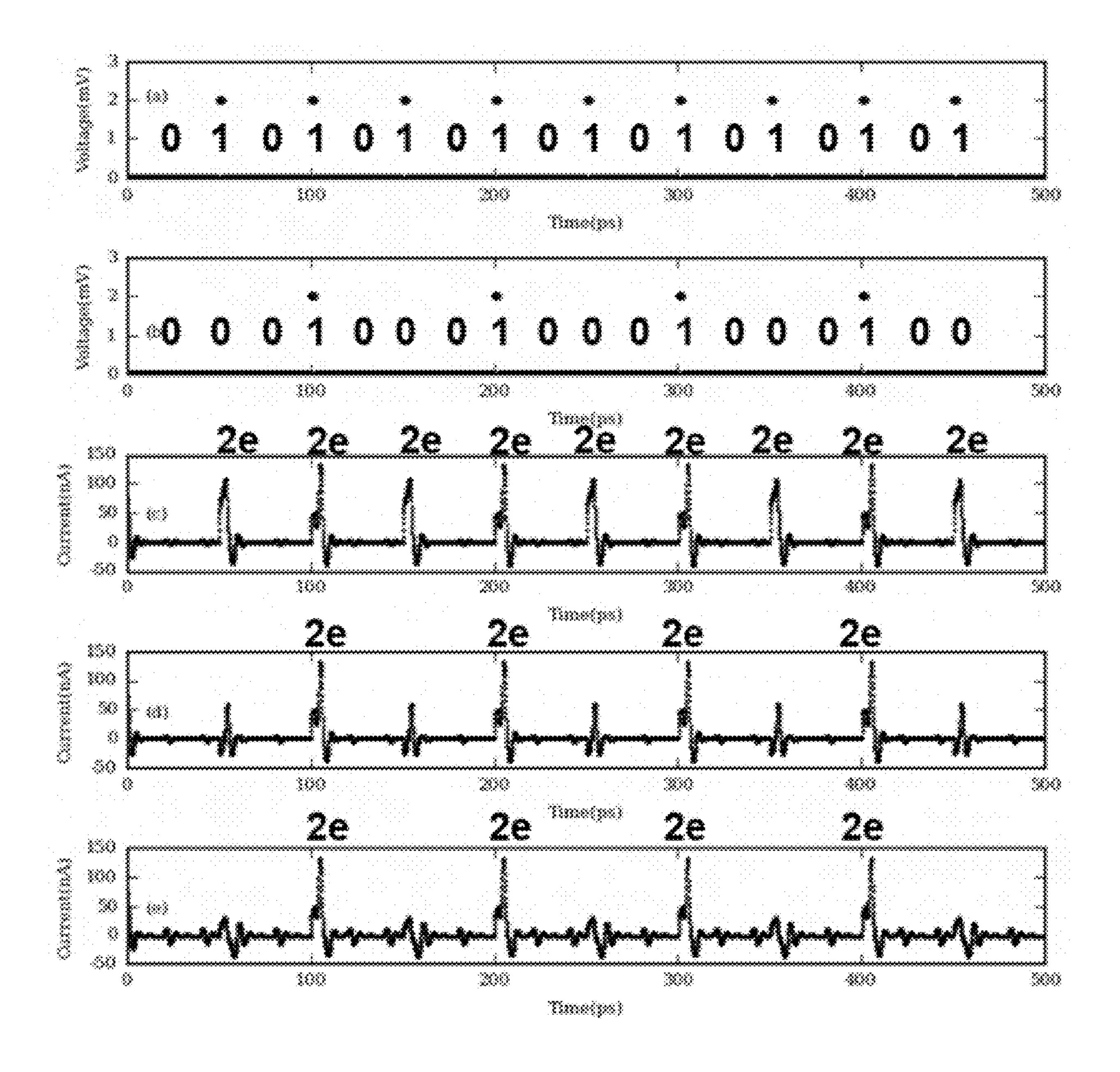

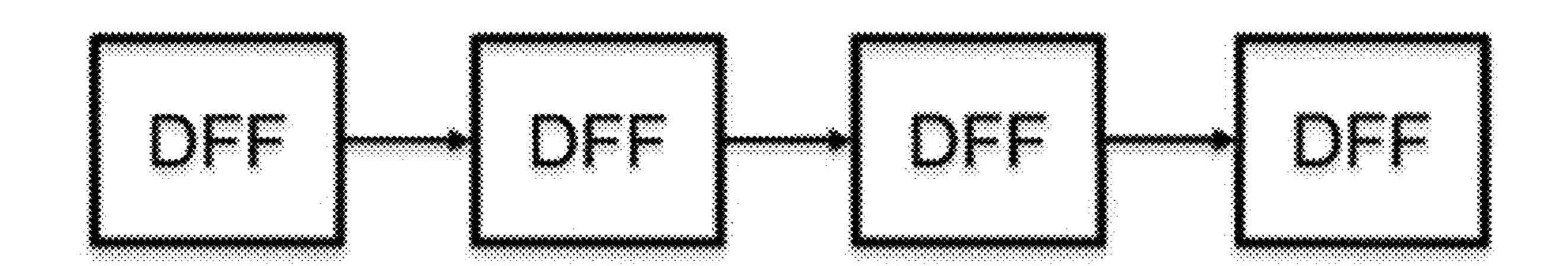

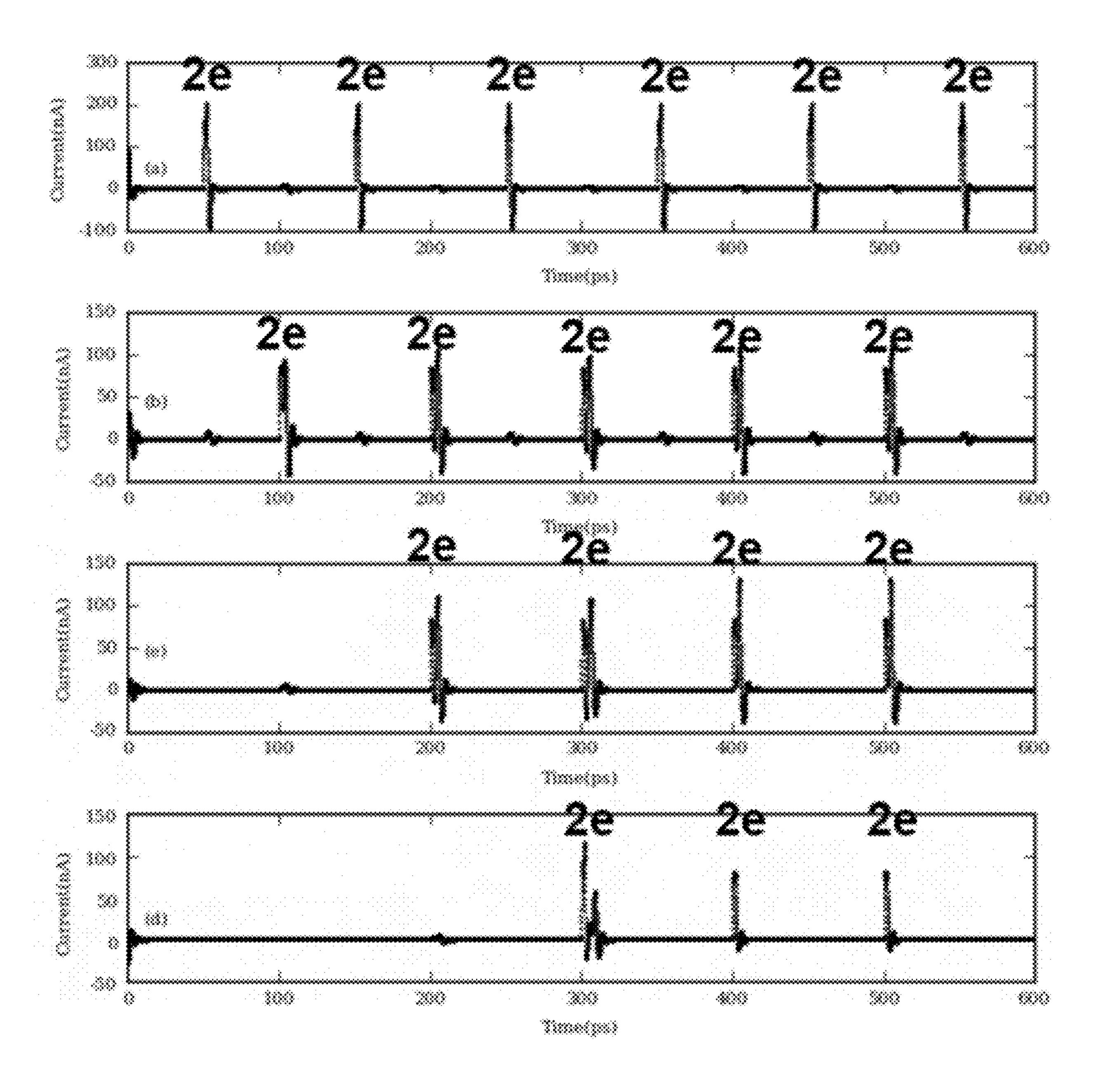

FIG. 34 shows a 4-stage shift register using the D flip-flops according to one embodiment of the present invention.

FIG. 35 shows simulation results of shift register shown in FIG. 34 according to one embodiment of the present invention: (a) input data pulses, (b) output after stage 1, (c) output after stage 2, and (d) output after stage 3.

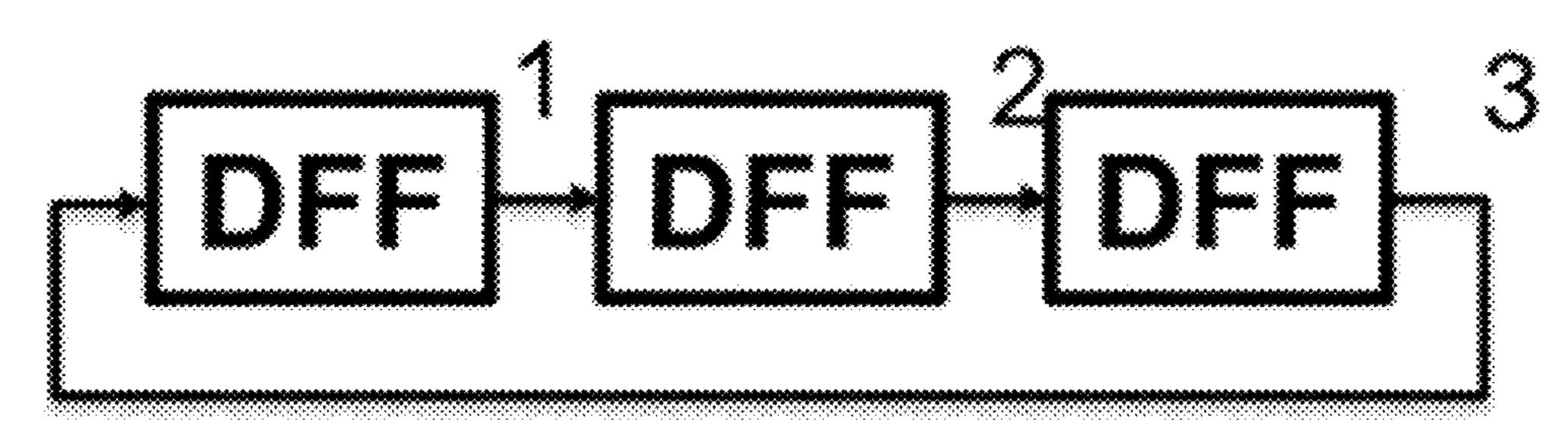

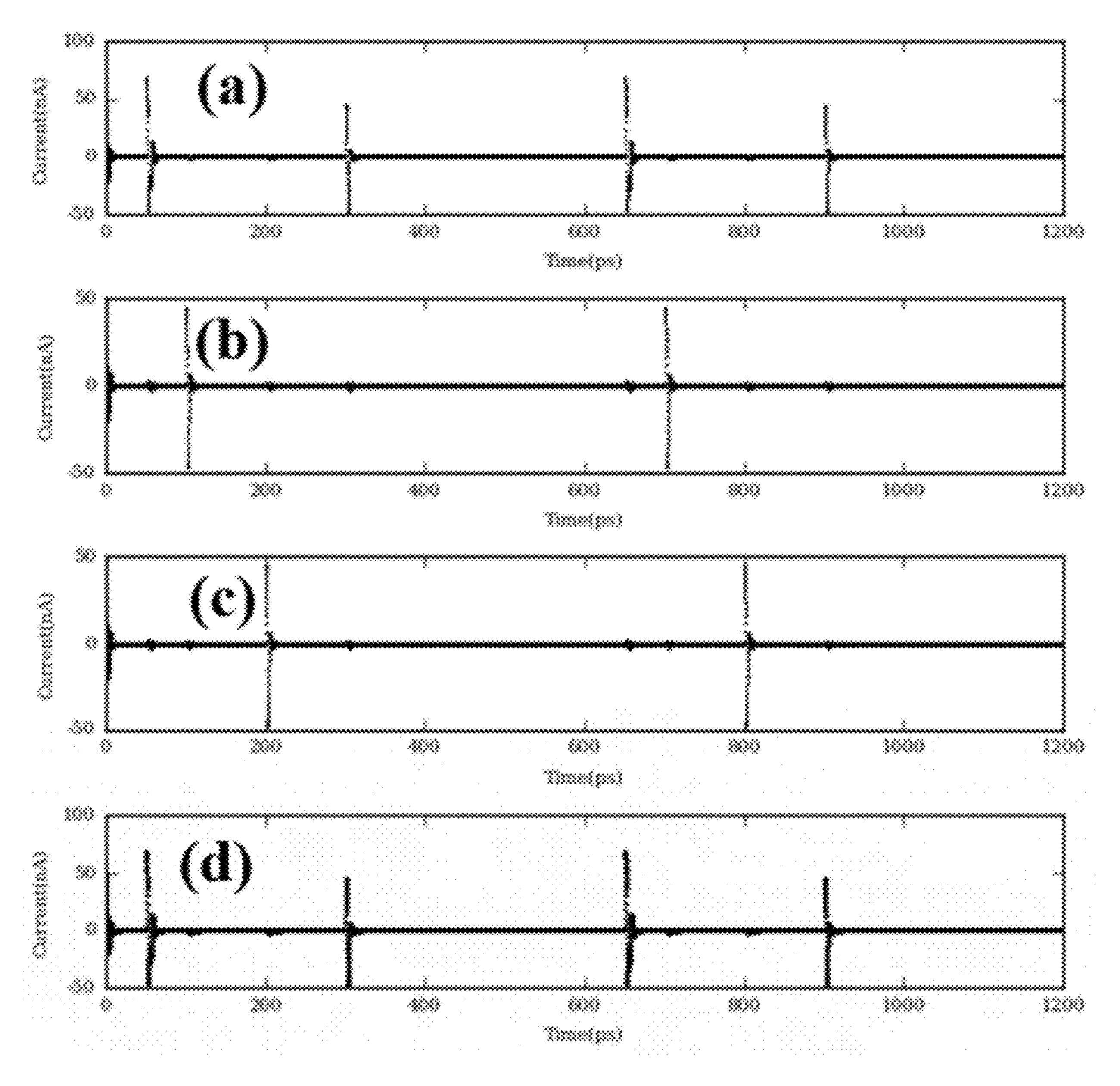

FIG. 36 shows a ring counter using D flip-flops according to one embodiment of the present invention.

FIG. 37 shows simulation results of the ring counter shown in FIG. 36 according to one embodiment of the present invention: (a) output after stage 1, (b) output after stage 2, (c) output after stage 3, and (d) output after stage 4.

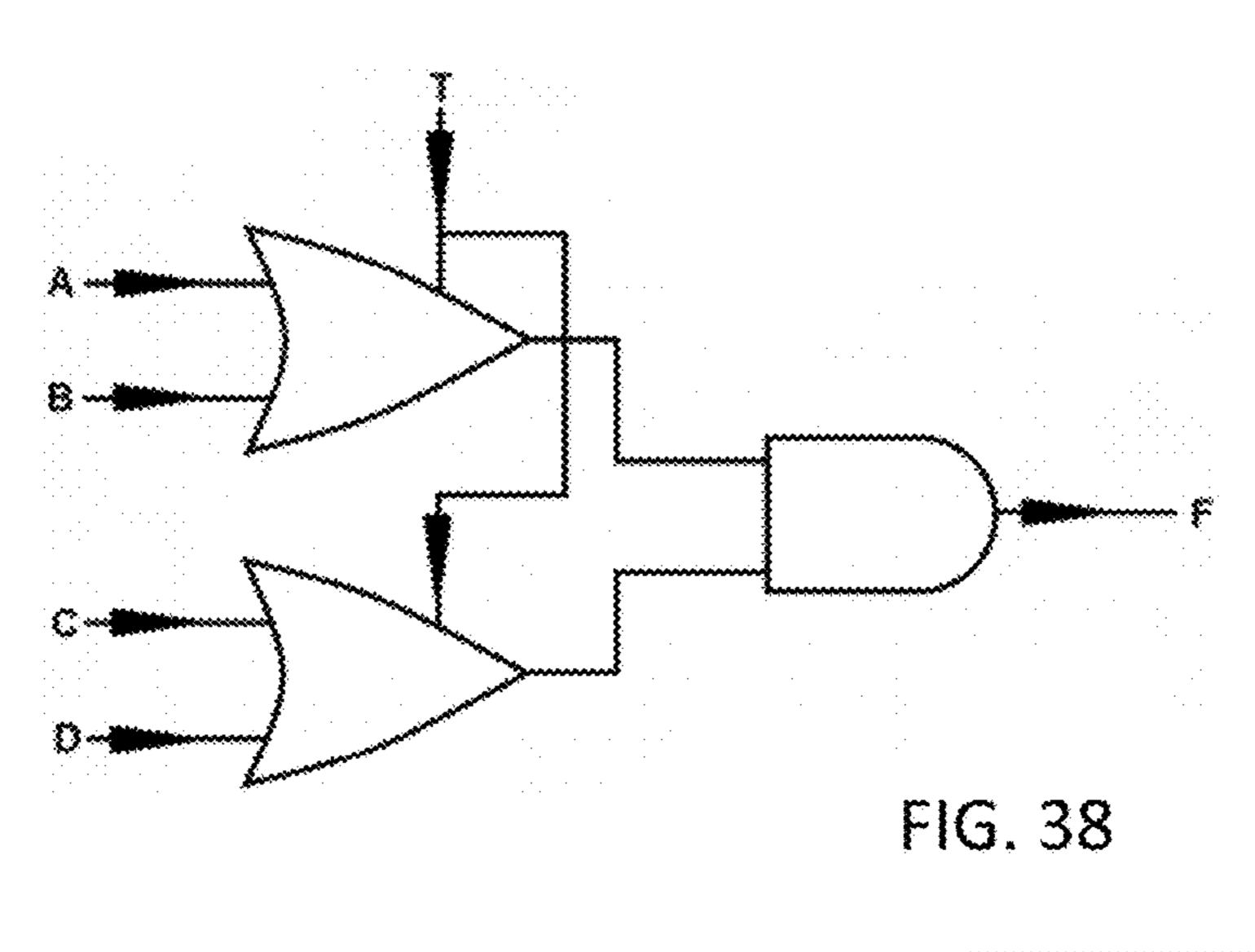

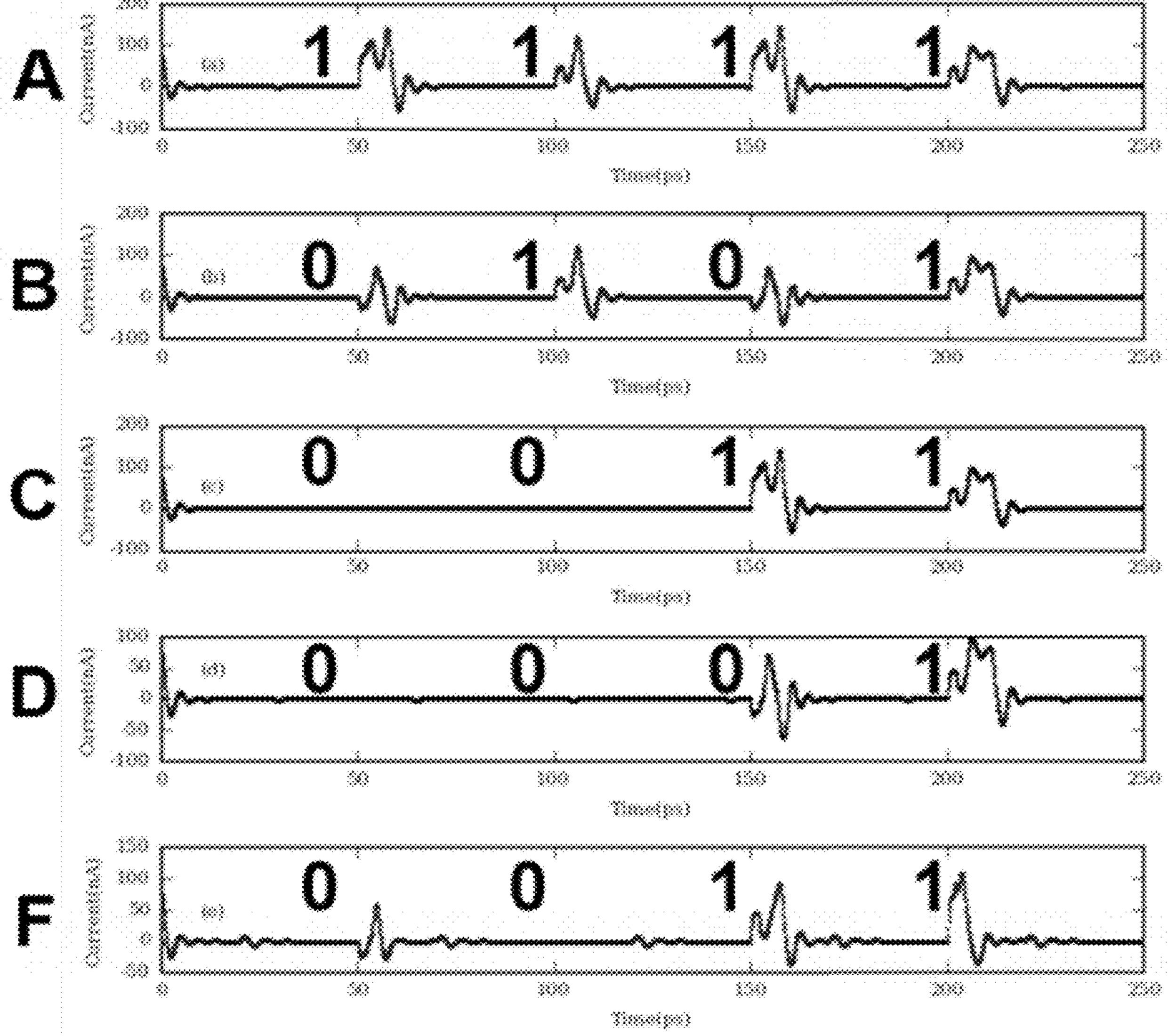

FIG. 38 shows an OR-AND logic circuit according to one embodiment of the present invention.

FIG. 39 shows simulation results of the OR-AND gate shown in FIG. 38 according to one embodiment of the present invention: (a) input A, (b) input B, (c) input C, (d) input D, and (e) output F.

FIG. 40 shows a block diagram of a QPSJ based ring oscillator according to one embodiment of the present invention.

FIG. 41 shows simulation results of the ring oscillator shown in FIG. 40 according to one embodiment of the present invention.

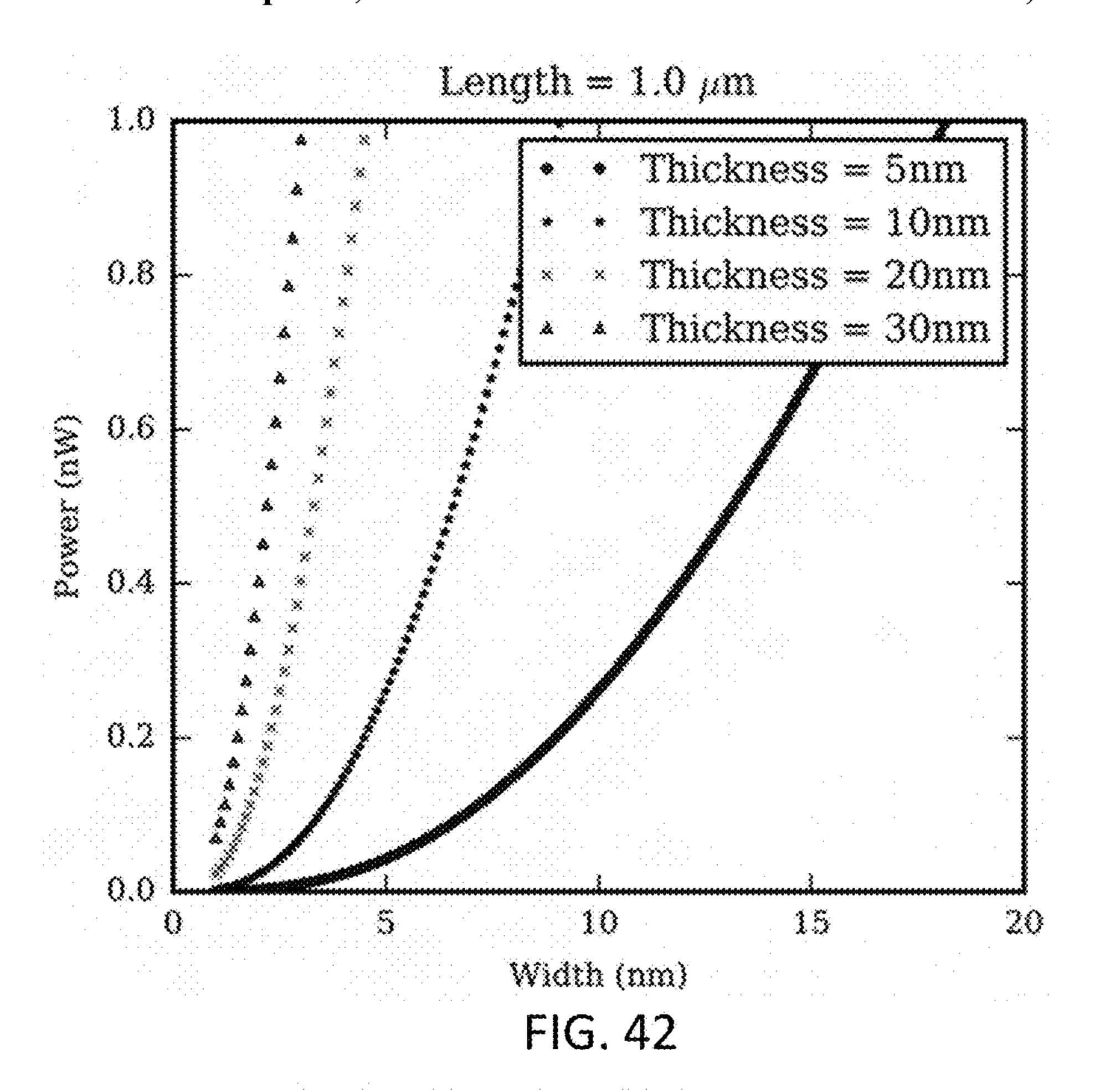

FIG. **42** shows power dissipated per switching event in an InOx QPSJ for a nano-wire of length 1 μm according to one embodiment of the present invention.

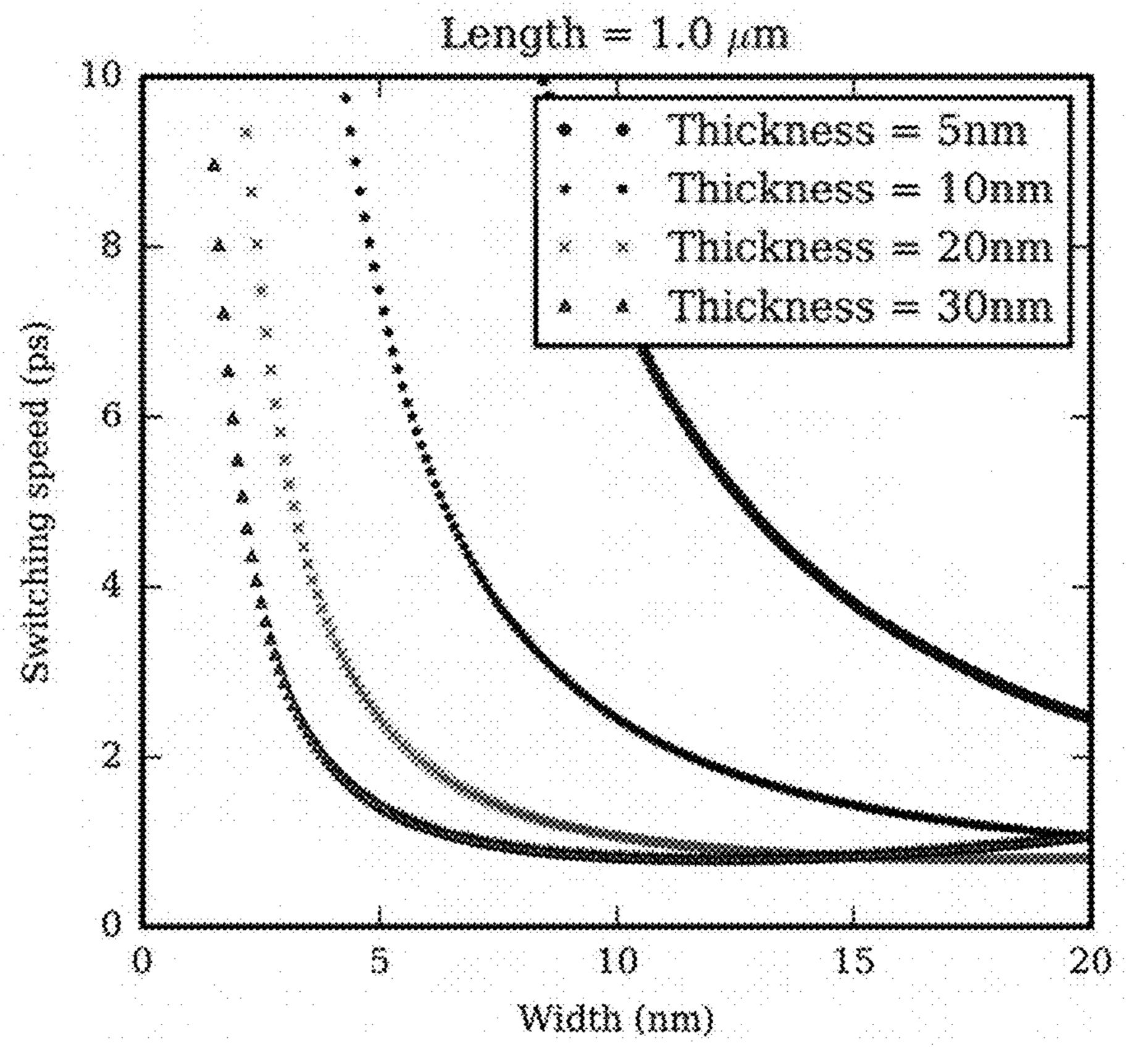

FIG. **43** shows switching speed in an InOx QPSJ for a nano-wire of length 1 μm according to one embodiment of the present invention.

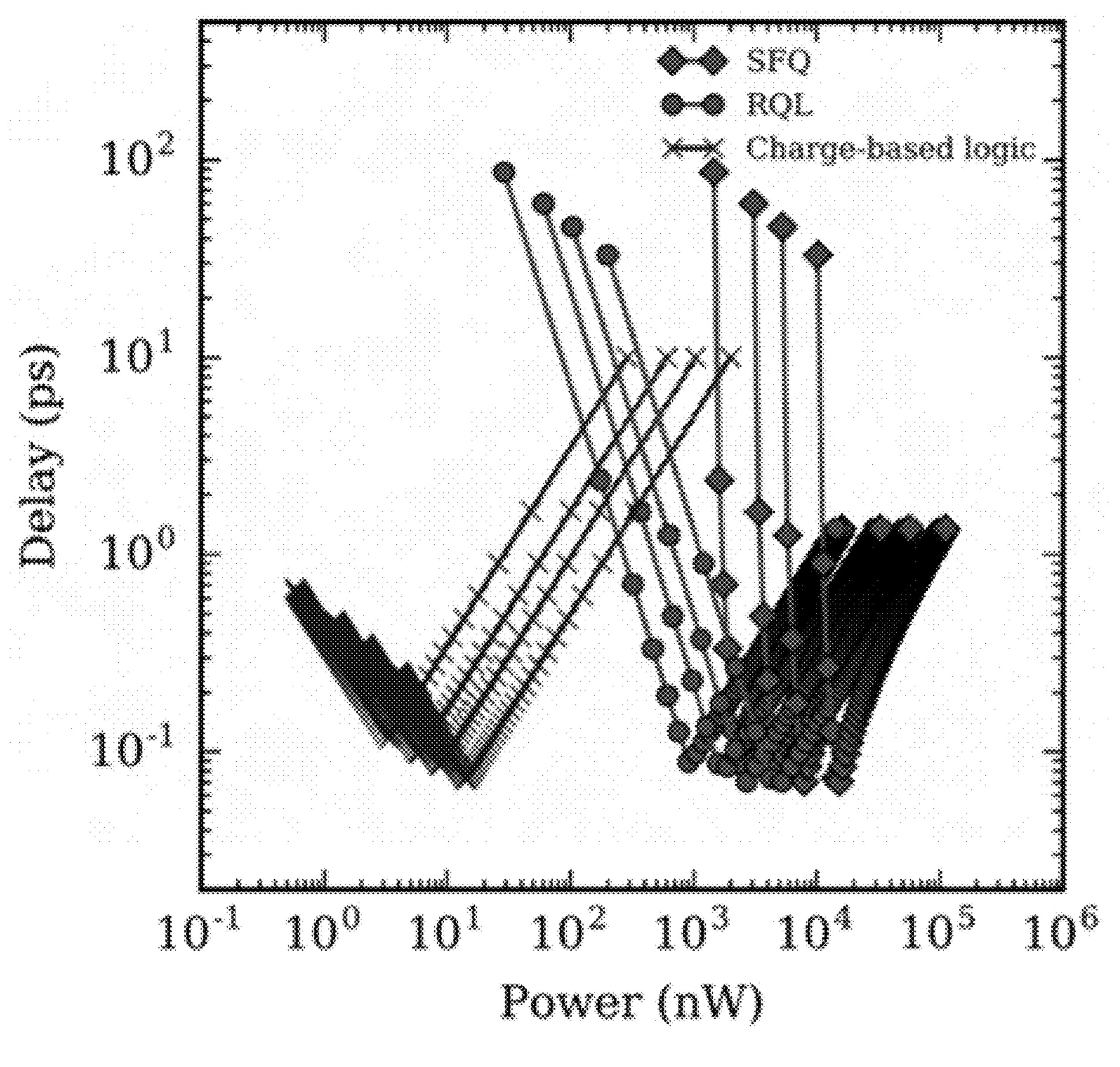

FIG. 44 shows power and switching delay comparison between QPSJ, single flux quantum and reciprocal quantum logic circuits according to one embodiment of the present invention.

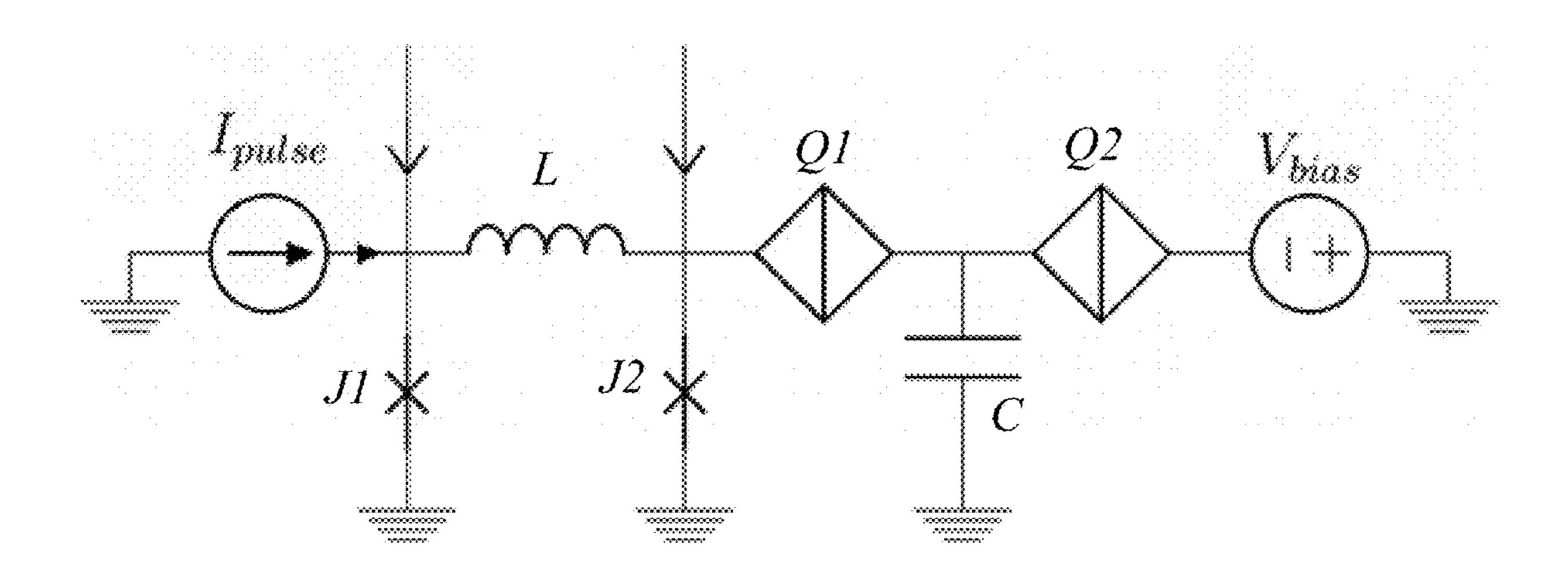

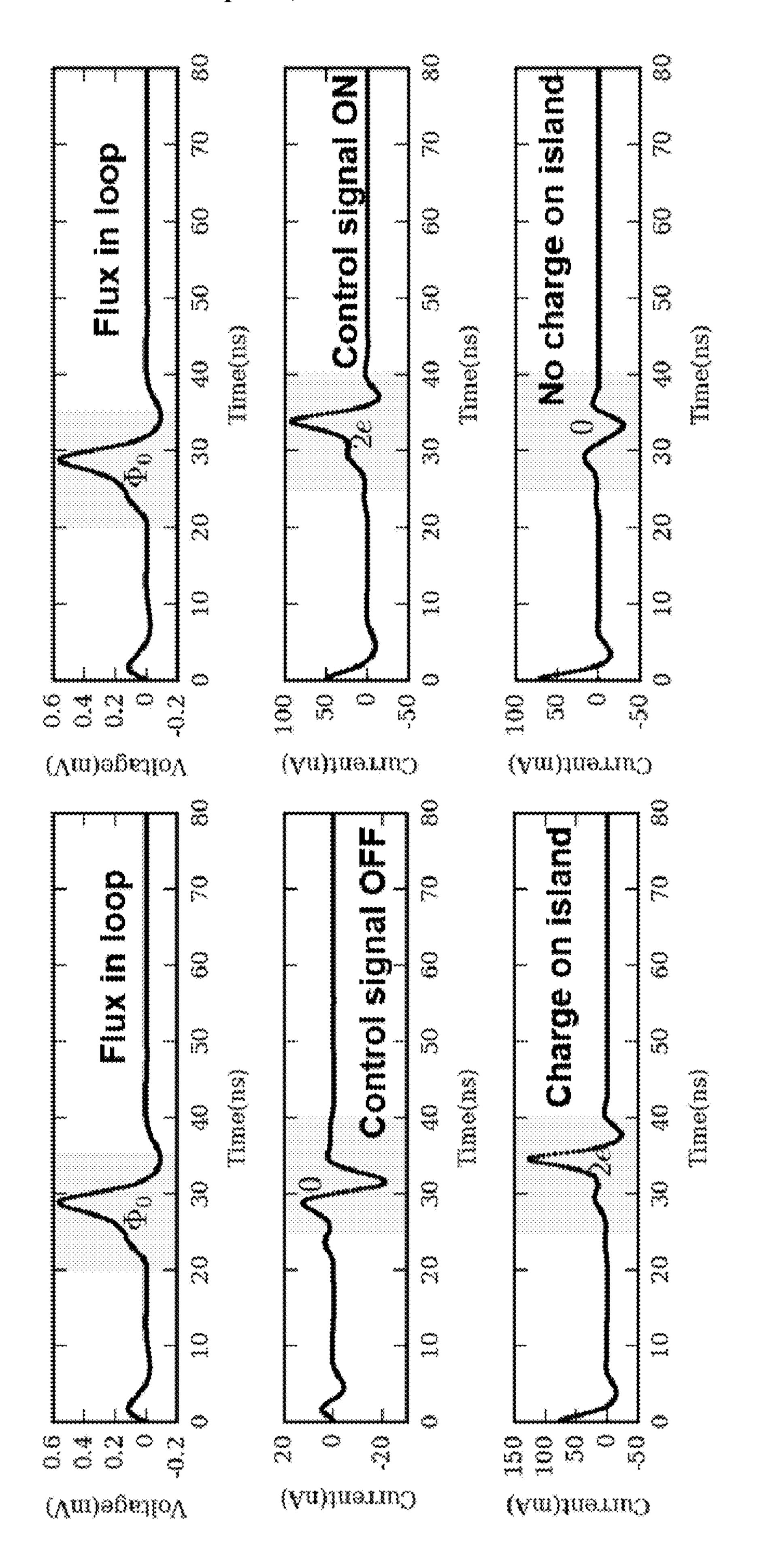

FIG. **45** shows a circuit of single-flux-quantum loop and quantized charge island in series facilitating flux-charge conversion according to one embodiment of the present invention.

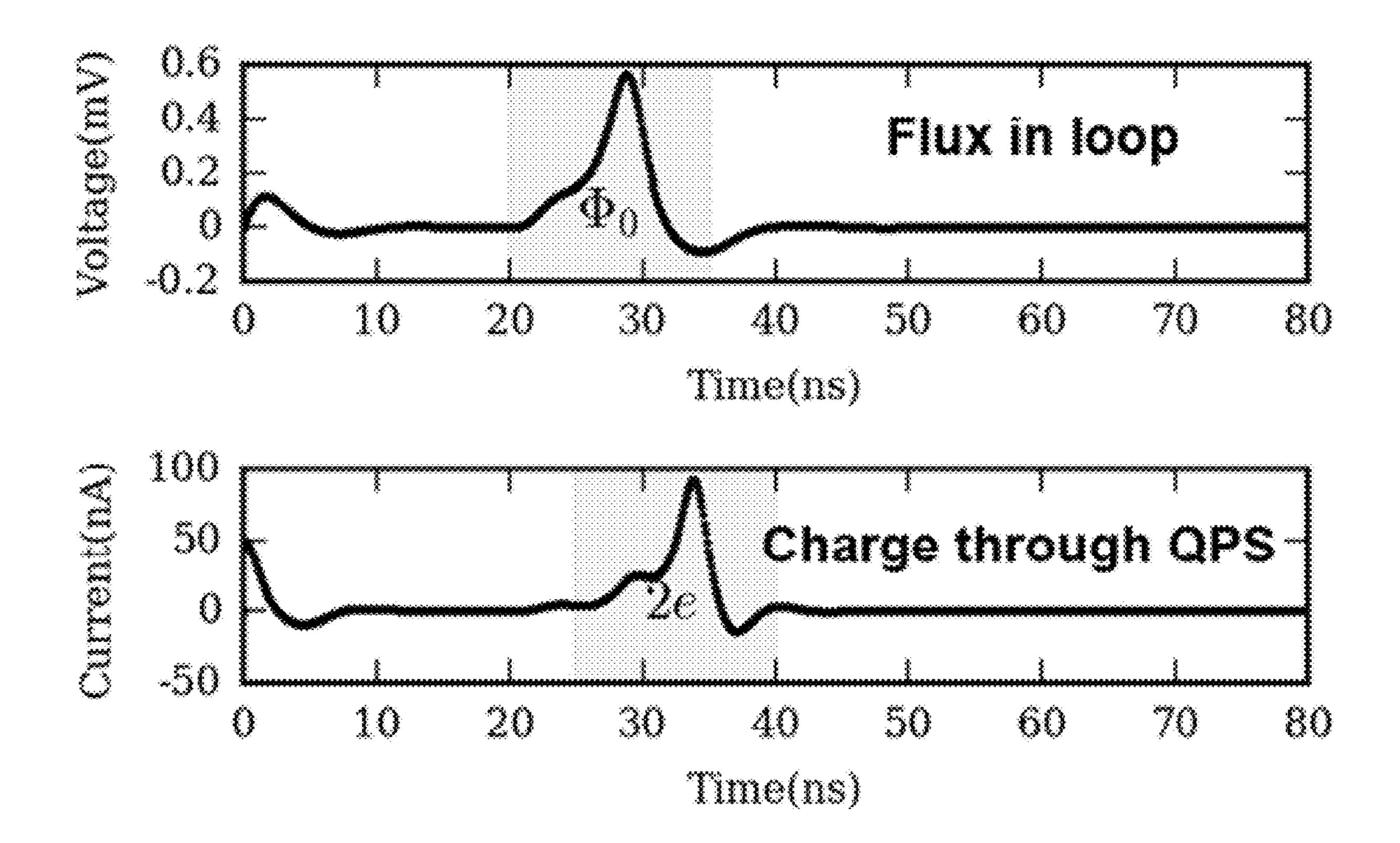

FIG. **46** shows simulation of the circuit shown in FIG. **45** demonstrating flux-charge conversion according to one embodiment of the present invention.

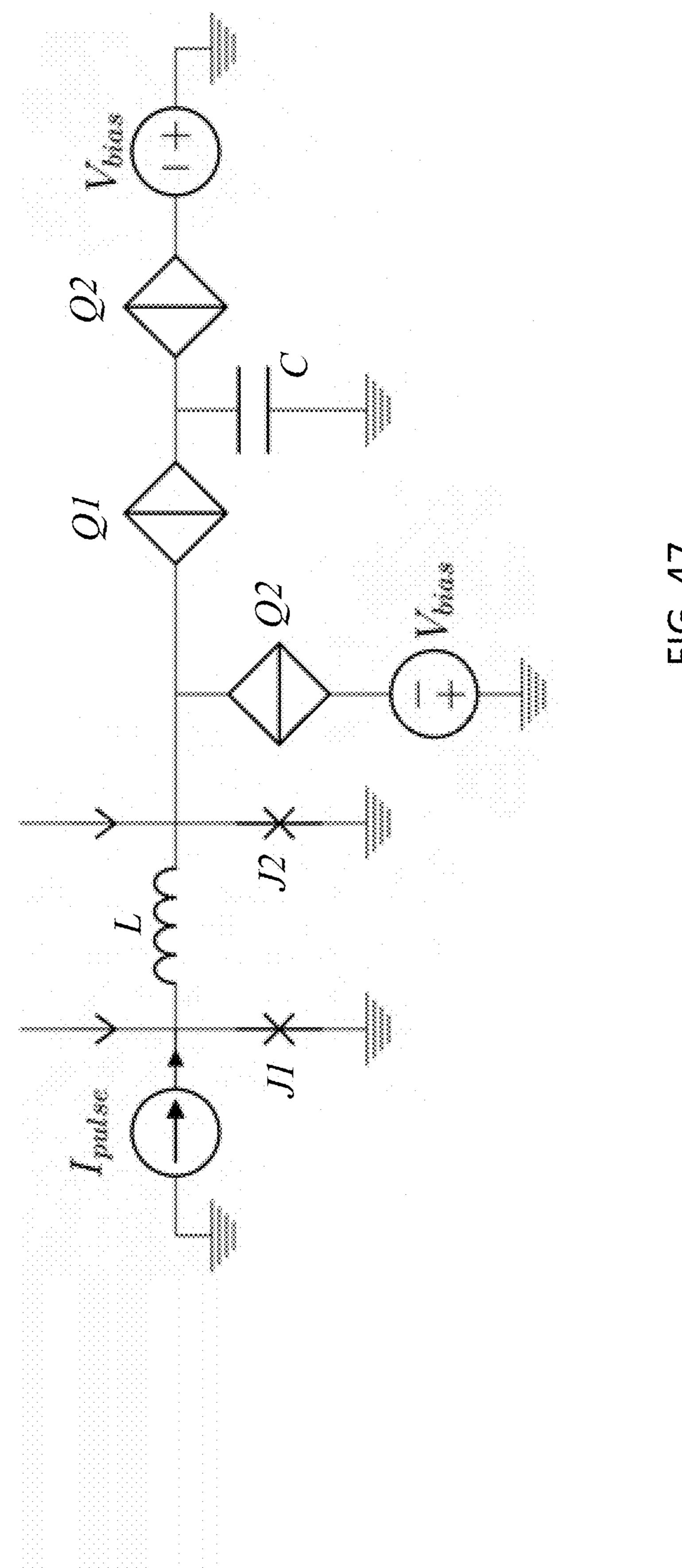

FIG. 47 shows a control/buffer circuit using flux-charge elements enabling logic operation in complementary quantum logic (CQL) according to one embodiment of the present invention.

FIG. 48 shows output signal generation enabled by control signal at the control/buffer circuit shown in FIG. 47 according to one embodiment of the present invention.

# DETAILED DESCRIPTION OF THE INVENTION

The present invention will now be described more fully hereinafter with reference to the accompanying drawings, in which exemplary embodiments of the present invention are shown. The present invention may, however, be embodied in many different forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the

invention to those skilled in the art. Like reference numerals refer to like elements throughout.

The terms used in this specification generally have their ordinary meanings in the art, within the context of the invention, and in the specific context where each term is 5 used. Certain terms that are used to describe the invention are discussed below, or elsewhere in the specification, to provide additional guidance to the practitioner regarding the description of the invention. For convenience, certain terms may be highlighted, for example using italics and/or quota- 10 tion marks. The use of highlighting and/or capital letters has no influence on the scope and meaning of a term; the scope and meaning of a term are the same, in the same context, whether or not it is highlighted and/or in capital letters. It will be appreciated that the same thing can be said in more 15 thereof. than one way. Consequently, alternative language and synonyms may be used for any one or more of the terms discussed herein, nor is any special significance to be placed upon whether or not a term is elaborated or discussed herein. Synonyms for certain terms are provided. A recital of one or 20 more synonyms does not exclude the use of other synonyms. The use of examples anywhere in this specification, including examples of any terms discussed herein, is illustrative only and in no way limits the scope and meaning of the invention or of any exemplified term. Likewise, the inven- 25 tion is not limited to various embodiments given in this specification.

The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of the invention. As used herein, the singular forms 30 "a," "an," and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise.

It will be understood that when an element is referred to as being "on," "attached" to, "connected" to, "coupled" with, "contacting," etc., another element, it can be directly 35 on, attached to, connected to, coupled with or contacting the other element or intervening elements may also be present. In contrast, when an element is referred to as being, for example, "directly on," "directly attached" to, "directly connected" to, "directly coupled" with or "directly contacting" another element, there are no intervening elements present. It will also be appreciated by those of skill in the art that references to a structure or feature that is disposed "adjacent" to another feature may have portions that overlap or underlie the adjacent feature.

It will be understood that, although the terms first, second, third, etc. may be used herein to describe various elements, components, regions, layers and/or sections, these elements, components, regions, layers and/or sections should not be limited by these terms. These terms are only used to distinguish one element, component, region, layer or section from another element, component, region, layer or section. Thus, a first element, component, region, layer or section discussed below can be termed a second element, component, region, layer or section without departing from the teachings of the present invention.

Furthermore, relative terms, such as "lower" or "bottom" and "upper" or "top," may be used herein to describe one element's relationship to another element as illustrated in the figures. It will be understood that relative terms are intended 60 to encompass different orientations of the device in addition to the orientation shown in the figures. For example, if the device in one of the figures is turned over, elements described as being on the "lower" side of other elements would then be oriented on the "upper" sides of the other 65 elements. The exemplary term "lower" can, therefore, encompass both an orientation of lower and upper, depend-

10

ing on the particular orientation of the figure. Similarly, if the device in one of the figures is turned over, elements described as "below" or "beneath" other elements would then be oriented "above" the other elements. The exemplary terms "below" or "beneath" can, therefore, encompass both an orientation of above and below.

It will be further understood that the terms "comprise(s)" and/or "comprising," or "include(s)" and/or "including" or "has (have)" and/or "having" or "contain(s)" and/or "containing" when used in this specification specify the presence of stated features, regions, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, regions, integers, steps, operations, elements, components, and/or groups thereof.

Unless otherwise defined, all terms (including technical and scientific terms) used herein have the same meaning as commonly understood by one of ordinary skill in the art to which the present invention belongs. It will be further understood that terms, such as those defined in commonly used dictionaries, should be interpreted as having a meaning that is consistent with their meaning in the context of the relevant art and the present disclosure, and will not be interpreted in an idealized or overly formal sense unless expressly so defined herein.

As used herein, "around," "about," "substantially" or "approximately" shall generally mean within 20 percent, preferably within 10 percent, and more preferably within 5 percent of a given value or range. Numerical quantities given herein are approximate, meaning that the terms "around," "about," "substantially" or "approximately" can be inferred if not expressly stated.

As used herein, the terms "capacitor" and "capacitance" are interchangeable in the disclosure, and may refer to a real, pysical component, a parasitic capacitor, or just a property of the lines connecting the QPSJs.

As used herein, the phrase at least one of A, B, and C should be construed to mean a logical (A or B or C), using a non-exclusive logical OR. It should be understood that one or more steps within a method may be executed in different order (or concurrently) without altering the principles of the present disclosure. As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items.

The description is now made as to the embodiments of the invention in conjunction with the accompanying drawings. Although various exemplary embodiments of the present invention disclosed herein may be described in the context of superconducting quantum logic that have significant advantages primarily in energy consumption and ease of fabrication/design, it should be appreciated that aspects of the present invention disclosed herein are not limited to being used in connection with one particular type of charged-based logic using quantum phase-slip junctions (QPSJs) and complementary quantum logic (CQL) using QPSJs and Josephson junctions (JJs) and may be practiced in connection with other types of charged-based logic and CQL or other types of logic devices using charged-based logic and CQL without departing from the scope of the present invention disclosed herein.

In one aspect of the invention, the superconducting logic cell includes at least one QPSJ for receiving at least one input and responsively providing at least one output, each QPSJ being configured such that when an input voltage of an input voltage pulse exceeds a critical value, a quantized charge of a Cooper electron pair tunnels across said QPSJ as an output, when the input voltage is less than the critical

value, no quantized charge of the Cooper electron pair tunnels across said QPSJ as the output, where the presence and absence of the quantized charge in the output form two logic states, and the at least one QPSJ is biased with a bias voltage. In one embodiment, the bias voltage is about 5 70-80% of the critical voltage, the input voltage is at least about 150% of the critical voltage for quantized charge tunneling. It should be appreciated by those having ordinary skill in the art that other ranges of the bias voltage and the input voltage can also be utilized to practice the invention. 10

Referring to FIG. 1, each QPSJ is characterizable as a compact circuit model for SPICE implementation. The compact circuit model comprises a voltage source V, a QPSJ element, an inductor L representing an inductance of a nano-wire of the QPSJ, and a non-linear resistor R having 15 different values of resistance in different phases of operation and showing normal to superconductor transition as a function of the voltage across the QPSJ, coupling to each other in series.

As discussed below, the critical voltage, the inductance, 20 and the resistance are determined by material properties and physical dimensions of the QPSJ.

In one embodiment, the at least one QPSJ comprises two QPSJs, where a node connecting two QPSJs and a capacitor defines a charge island, as shown in FIGS. 11(b) and 11(c). 25 In one embodiment the capacitor may be a real, pysical component. In another embodiment, the capacitor may be a parasitic capacitor, or just a property of the lines connecting the QPSJs. When the quantized charge of the Cooper electron pair tunnels across one of the two QPSJs, the quantized charge of the Cooper electron pair is stored in the charge island, otherwise no quantized charge of the Cooper electron pair is stored in the charge island, thereby forming a basic logic element having the two logic states.

As shown in FIG. 12, in this exemplary embodiment, the superconducting logic cell is a QPSJ transmission line, where the at least one QPSJ comprises four QPSJs connected to one another in series, where each node connecting two adjacent QPSJs and a capacitor defines a charge island. According to the invention, the quantized charge of the 40 Cooper electron pair is stored in a change island or forced to hop to its immediately next charge island, by proper design or tuning of a capacitance of the charge island, along with the junction parameters, thereby transferring the quantized charge of the Cooper electron pair along the QPSJ transmission line. In certain embodiments, amplification or attenuation of the current pulse amplitude is obtained by using the QPSJs of different critical voltages and different capacitor values.

In one embodiment, as shown in FIG. 15, the superconducting logic cell is a QPSJ pulse splitter that comprises three QPSJs, where the first QPSJ has a first terminal connected to an input voltage source defining an input node, and a second terminal connected to a first capacitor; the second QPSJ has a first terminal connected to the second 55 terminal of the first QPSJ, and a second terminal connected to a second capacitor and a first bias voltage source defining a first output node; and the third QPSJ has a first terminal connected to the second terminal of the first QPSJ, and a second terminal connected to a third capacitor and a second bias voltage source defining a second output node. In operation, an input pulse at the input node is split into two pulses output from the first and second output nodes respectively.

In one embodiment, as shown in FIG. 15, the superconducting logic cell is a QPSJ buffer including three QPSJs, where the first QPSJ has a first terminal connected to an

12

input voltage source or a first bias voltage source defining a first node, and a second terminal connected to a first capacitor defining a second node; the second QPSJ has a first terminal connected to the second terminal of the first QPSJ defining a third node, and a second terminal connected to a second capacitor and the first bias voltage source or the input voltage source defining a fourth node; and the third QPSJ has a first terminal connected to the third node, and a second terminal connected to a second bias voltage source. In operation, an input pulse from the first node through the first QPSJ switches to the third QPSJ, before it switches to the second QPSJ so as to prevent a signal flow in a direction from the first node to the fourth node, or when current arrives from an opposite direction, the first QPSJ switches before the third QPSJ, allowing the signal through.

In one embodiment, as shown in FIG. 20, the superconducting logic cell is a QPSJ confluence buffer having four QPSJs, where the first QPSJ has a first terminal connected to a first input voltage source, and a second terminal connected to a first capacitor defining node 3; the second QPSJ has a first terminal connected to a second input voltage source, and a second terminal connected to a second capacitor defining node 6, where both nodes 3 and 6 are connected to node 7; the third QPSJ has a first terminal connected to node 7, and a second terminal connected to a first bias voltage source; and the fourth QPSJ has a first terminal connected to node 7, and a second terminal connected to a third capacitor and the second bias voltage source at node 8. In operation, input pulses from either the first or second input voltage sources result in an output pulse from node 8, but do not result in output from the other input.

In one embodiment, as shown in FIG. 22, the superconducting logic cell is a QPSJ transmission line, here the at least one QPSJ comprises four QPSJs concreted to one another in series, where each node connecting to adjacent QPSJs and a capacitor defines a charge island. Excording to the invention, the quantized charge of the approximately next charge island, by proper design.

In one embodiment, as shown in FIG. 22, the superconducting logic cell is an RS flip-flop or a D flip-flop comprising two QPSJs, where the first QPSJ has a first terminal connected to a bias voltage source at node 2 that in turn is connected to a capacitor; and the second QPSJ has a first terminal connected to node 3, and a second terminal connected to node 4 that is in turn connected to the second input voltage source.

In one embodiment, the superconducting logic cell is the RS flip-flop. In operation, a SET input signal at node 1 induces a quantized charge of the Cooper electron pair to the island of node 3, and a RESET input signal at node 4 induces a current pulse opposite to that induced by the SET input signal so as to reset the charge on the island.

In one embodiment, the superconducting logic cell is the D flip-flop. In operation, a SET input signal at node 1 induces a quantized charge of the Cooper electron pair to the island of node 3, and a RESET input signal at node 4 is a clock signal that switches the first QPSJ and induces a quantized charge of the Cooper electron pair on the island, and with the next clock pulse, the charge flows through an output terminal to perform a function of the D flip-flop.

In one embodiment, as shown in FIG. 24, the superconducting logic cell is a T flip-flop comprising two QPSJs, where the first QPSJ has a first terminal connected to a bias voltage source at node 3 that in turn is connected to an input voltage source at node 2, the input voltage source connected to node 1, a second terminal connected node 4 that in turn is connected to a capacitor; and the second QPSJ has a first terminal connected to node 4, and a second terminal connected to node 2. In operation, a single clock signal of the input voltage source is input at node 1, and at each clock pulse, the current pulse toggles from ON to OFF and vice

versa, indicating the presence and absence of a quantized charge of the Cooper electron pair on the island with each clock pulse.

In one embodiment, as shown in FIG. **26**, the superconducting logic cell is a QPSJ based OR gate comprising six 5 QPSJs, where the first to fourth QPSJs define a confluence buffer and the fifth and sixth QPSJs define an island, where the confluence buffer is connected to the island in series such that a first terminal of the fifth QPSJ is connected to the output terminal of the confluence buffer and a second 10 terminal of the sixth QPSJ is connected to a clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, as shown in FIG. 28, the superconducting logic cell is a QPSJ based AND gate comprising five 15 QPSJs, where the first to fourth QPSJs define the confluence buffer and the fifth QPSJ has a first terminal connected to the output terminal of the confluence buffer and a second terminal connected to a second bias voltage source, and the output terminal of the confluence buffer is connected to a 20 clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, as shown in FIG. 30, the superconducting logic cell is a QPSJ based XOR gate comprising four QPSJs, where the first to fourth QPSJs define the confluence 25 buffer and the output terminal of the confluence buffer is connected to a clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, the superconducting logic cell further includes at least one JJ coupled with the at least one QPSJ 30 to perform one or more logic operations, where each JJ is configured such that when an input current through said JJ exceeds a critical value, a single flux quantum pulse tunnels across said JJ as an output, when the input current is less than the critical value, no single flux quantum pulse tunnels 35 across said JJ as the output, where the presence and absence of the single flux quantum pulse in the output form two logic states.

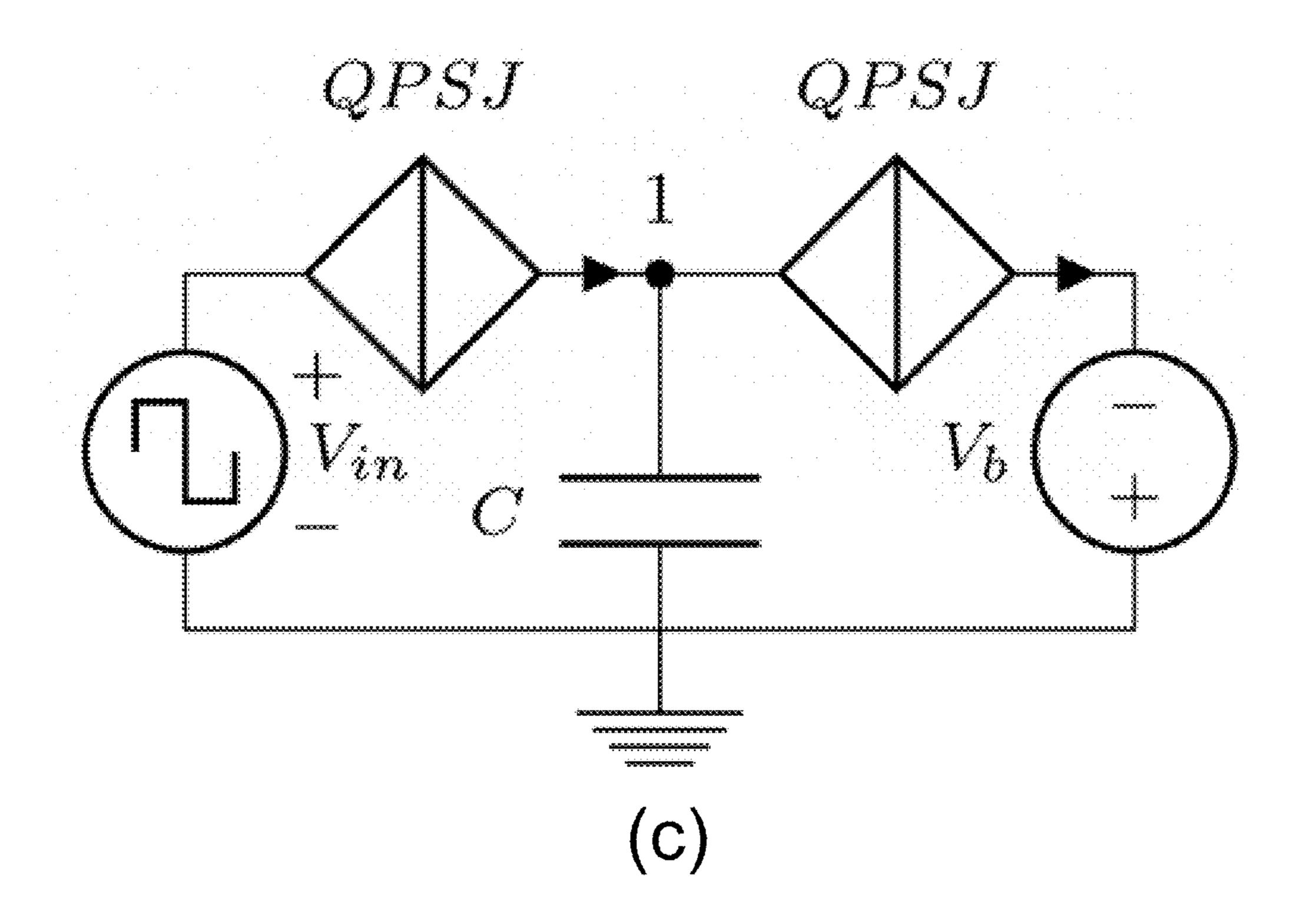

In one embodiment, as shown in FIG. **45**, the at least one QPSJ comprises two QPSJs defining a QPSJ island with a 40 capacitor, and the at least one JJ comprises two JJs defining a JJ loop with a inductor, and the QPSJ island and the JJ loop is connected in series to perform a bridge operation between flux and charge.

In one embodiment, as shown in FIG. 47, the at least one 45 QPSJ further comprises a third QPSJ having a first terminal connected to a node between the QPSJ island and the JJ loop, and a second terminal connected to a bias voltage source, where in operation, a voltage pulse is induced through the third QPSJ that enables or disables the output 50 pulse.

In another aspect, the present invention relates to a superconducting circuit device. In one embodiment, superconducting circuit device includes at least one superconducting logic cell, each superconducting logic cell comprising at least one QPSJ for receiving at least one input and responsively providing at least one output, each QPSJ being configured such that when an input voltage of an input voltage pulse exceeds a critical value, a quantized charge of a Cooper electron pair tunnels across said QPSJ as an output, when the input voltage is less than the critical value, no quantized charge of the Cooper electron pair tunnels across said QPSJ as the output, where the presence and absence of the quantized charge in the output form two logic states, and the at least one QPSJ is biased with a bias voltage.

In some embodiments, the at least one superconducting logic cell comprises a charge island, a QPSJ transmission

**14**

line, a QPSJ pulse splitter, a QPSJ buffer, a QPSJ confluence buffer, a QPSJ based OR gate, a QPSJ based AND gate, a QPSJ based XOR gate, an RS flip-flop, a D flip-flop, a T flip-flop, NOR, NAND, etc., or any combination thereof. It should be appreciated by those having ordinary skill in the art that the gates/circuits can also be extended to perform logic with greater than two inputs, and to more complex processes according to embodiments of the invention.

As shown in FIGS. 11(b) and 11(c), the charge island is defined by a node connecting two QPSJs and a capacitor.

In one embodiment, the QPSJ transmission line comprises a plurality of QPSJs, e.g., 4 QPSJs shown in FIG. 12, connected to one another in series, where each node connecting two adjacent QPSJs and a capacitor defines the charge island. In one embodiment the capacitor may be a real, pysical component. In another embodiment, the capacitor may be a parasitic capacitor, or just a property of the lines connecting the QPSJs.

In one embodiment, as shown in FIG. 15, the QPSJ pulse splitter comprises three QPSJs, where the first QPSJ has a first terminal connected to an input voltage source defining an input node, and a second terminal connected to a first capacitor; the second QPSJ has a first terminal connected to the second terminal of the first QPSJ, and a second terminal connected to a second capacitor and a first bias voltage source defining a first output node; and the third QPSJ has a first terminal connected to the second terminal of the first QPSJ, and a second terminal connected to a third capacitor and a second bias voltage source defining a second output node. In operation, an input pulse at the input node is split into two pulses output from the first and second output nodes respectively.

In one embodiment, as shown in FIGS. 17 (a) and (b), the QPSJ buffer comprises three QPSJs, where the first QPSJ has a first terminal connected to an input voltage source or a first bias voltage source defining a first node, and a second terminal connected to a first capacitor defining a second node; the second QPSJ has a first terminal connected to the second terminal of the first QPSJ defining a third node, and a second terminal connected to a second capacitor and the first bias voltage source or the input voltage source defining a fourth node; and the third QPSJ has a first terminal connected to the third node, and a second terminal connected to a second bias voltage source. In operation, an input pulse from the first node through the first QPSJ switches to the third QPSJ, before it switches to the second QPSJ so as to prevent a signal flow in a direction from the first node to the fourth node, or when current arrives from an opposite direction, the first QPSJ switches before the third QPSJ, allowing the signal through.

In one embodiment, as shown in FIG. 20, the QPSJ confluence buffer comprises four QPSJs, where the first QPSJ has a first terminal connected to a first input voltage source, and a second terminal connected to a first capacitor defining node 3; the second QPSJ has a first terminal connected to a second input voltage source, and a second terminal connected to a second capacitor defining node 6, where both nodes 3 and 6 are connected to node 7; the third QPSJ has a first terminal connected to node 7, and a second terminal connected to a first bias voltage source; and the fourth QPSJ has a first terminal connected to node 7, and a second terminal connected to a third capacitor and the second bias voltage source at node 8. In operation, input pulses from either the first or second input voltage sources result in an output pulse from node 8, but do not result in output from the other input.

In one embodiment, as shown in FIG. 26, the QPSJ based OR gate comprises six QPSJs, where the first to fourth QPSJs define the confluence buffer and the fifth and sixth QPSJs define an island, where the confluence buffer is connected to the island in series such that a first terminal of the fifth QPSJ is connected to the output terminal of the confluence buffer and a second terminal of the sixth QPSJ is connected to a clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, as shown in FIG. 28, the QPSJ based AND gate comprises five QPSJs, where the first to fourth QPSJs define the confluence buffer and the fifth QPSJ has a first terminal connected to the output terminal of the confluence buffer and a second terminal connected to a second bias voltage source, and the output terminal of the confluence buffer is connected to a clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, as shown in FIG. **30**, the QPSJ based 20 XOR gate comprises four QPSJs, where the first to fourth QPSJs define the confluence buffer and the output terminal of the confluence buffer is connected to a clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, as shown in FIG. 22, the RS flip-flop or the D flip-flop comprises two QPSJs, where the first QPSJ has a first terminal connected to a bias voltage source at node 2 that in turn is connected to a first input voltage source connected to node 1, a second terminal connected node 3 that in turn is connected to a capacitor; and the second QPSJ has a first terminal connected to node 3, and a second terminal connected to node 4 that is in turn connected to the second input voltage source.

In one embodiment, in operation, a SET input signal at node 1 induces a quantized charge of the Cooper electron pair to the island of node 3, and a RESET input signal at node 4 induces a charge opposite to that induced by the SET input signal so as to reset the charge on the island.

In one embodiment, in operation, a SET input signal at node 1 induces a quantized charge of the Cooper electron pair to the island of node 3, and a RESET input signal at node 4 is a clock signal that switches the first QPSJ and induces a quantized charge of the Cooper electron pair on 45 the island, and with the next clock pulse, the charge flows through an output terminal to perform a function of the D flip-flop.

In one embodiment, as shown in FIG. **24**, the T flip-flop comprises two QPSJs, where the first QPSJ has a first 50 terminal connected to a bias voltage source at node 3 that in turn is connected to an input voltage source at node 2, the input voltage source connected to node 1, a second terminal connected node 4 that in turn is connected to a capacitor; and the second QPSJ has a first terminal connected to node 4, 55 and a second terminal connected to node 2. In operation, a single clock signal of the input voltage source is input at node 1, and at each clock pulse, the current pulse toggles from ON to OFF and vice versa, indicating the presence and absence of a quantized charge of the Cooper electron pair on 60 the island with each clock pulse.

In one embodiment, as shown in FIG. 32, the superconducting circuit device is a QPSJ based half-adder comprising the AND and XOR gates along with splitters to split the input pulses to both the XOR and AND gates.

In one embodiment, as shown in FIG. 34, the superconducting circuit device is a QPSJ based shift register com-

**16**

prising a plurality of stages connected in series, each stage comprising the D flip-flop and having a different but identical clock input.

In one embodiment, as shown in FIG. 36, the superconducting circuit device is a QPSJ based ring counter comprising a plurality of stages connected to one another in a ring.

In one embodiment, as shown in FIG. 38, the superconducting circuit device is a QPSJ based OR-AND circuit.

In one embodiment, as shown in FIG. **40**, the superconducting circuit device is a QPSJ based ring oscillator comprising two QPSJ transmission lines, a confluence buffer and a pulse splitter, where the confluence buffer is connected to the first QPSJ transmission lines that in turn is connected to the pulse splitter, the pulse splitter is connected to the second QPSJ transmission lines that in turn is connected to the confluence buffer.

In one embodiment, the superconducting circuit device further includes at least one CQL cell, each CQL cell comprising at least one QPSJ, and at least one JJ coupled with the at least one QPSJ to perform one or more logic operations, where each JJ is configured such that when an input current through said JJ exceeds a critical value, a single flux quantum pulse tunnels across said JJ as an output, when the input current is less than the critical value, no single flux quantum pulse tunnels across said JJ as the output, where the presence and absence of the single flux quantum pulse in the output form two logic states.

In one embodiment, as shown in FIG. **45**, the CQL cell comprises two QPSJs defining a QPSJ island with a capacitor, and two JJs defining a JJ loop with a inductor, and the QPSJ island and the JJ loop is connected in series to perform a bridge operation between flux and charge.

In one embodiment, as shown in FIG. 47, the CQL cell further comprises a third QPSJ having a first terminal connected to a node between the QPSJ island and the JJ loop, and a second terminal connected to a bias voltage source, where in operation, a voltage pulse is induced through the third QPSJ that enables or disables the output pulse.

In yet another aspect, the invention relates to a superconducting circuit device comprising at least one of one or more JJs and one or more QPSJs.

In one embodiment, the one or more QPSJs are adapted for receiving at least one input and responsively providing at least one output, each QPSJ being configured such that when an input voltage of an input voltage pulse exceeds a critical value, a quantized charge of a Cooper electron pair tunnels across said QPSJ as an output, when the input voltage is less than the critical value, no quantized charge of the Cooper electron pair tunnels across said QPSJ as the output, wherein the presence and absence of the quantized charge that is realizable as a constant area of current pulses in the output form two logic states, and wherein the at least one QPSJ is biased with a bias voltage.

In one embodiment, the bias voltage is about 50-95% of the critical voltage, the input voltage is at least about 110% of the critical voltage for quantized charge tunneling.

In one embodiment, each QPSJ is characterizable as a compact circuit model, wherein the compact circuit model comprises a voltage source, a phase-slip junction, an inductor representing an inductance of a nano-wire of the phase-slip junction, and a non-linear resistor having different values of resistance in different phases of operation and showing normal to superconductor transition as a function of the voltage across the phase-slip junction, coupling to each other in series.

In one embodiment, the critical voltage, the inductance, and the resistance are determined by material properties and physical dimensions of the QPSJ.

In one embodiment, the one or more QPSJs comprise two QPSJs, wherein a node connecting two QPSJs and a capacitor defines a charge island.

In one embodiment, when the quantized charge of the Cooper electron pair tunnels across one of the two QPSJs, the quantized charge of the Cooper electron pair is stored in the charge island, otherwise no quantized charge of the 10 Cooper electron pair is stored in the charge island, thereby forming a basic logic element having the two logic states.

In one embodiment, the one or more QPSJs forms a QPSJ transmission line, wherein the one or more QPSJs comprise a plurality of QPSJs connected to one another in series, 15 wherein each node connecting two adjacent QPSJs and a capacitor defines a charge island.

In one embodiment, the quantized charge of the Cooper electron pair is stored in a charge island or forced to hop to its immediately next charge island, by design of or tuning a 20 capacitance of the charge island, along with the junction parameters, thereby transferring the quantized charge of the Cooper electron pair along the QPSJ transmission line.

In one embodiment, amplification or attenuation of the current pulse amplitude is obtained by using the QPSJs of 25 different critical voltages and different capacitor values.

In one embodiment, the one or more QPSJs forms a QPSJ pulse splitter, wherein the one or more QPSJs comprise three QPSJs, where the first QPSJ has a first terminal connected to an input voltage source defining an input node, and a 30 second terminal connected to a first capacitor; the second QPSJ has a first terminal connected to the second terminal of the first QPSJ, and a second terminal connected to a second capacitor and a first bias voltage source defining a connected to the second terminal of the first QPSJ, and a second terminal connected to a third capacitor and a second bias voltage source defining a second output node. In operation, an input pulse at the input node is split into two pulses output from the first and second output nodes respec- 40 tively.

In one embodiment, the one or more QPSJs forms a QPSJ buffer, wherein the one or more QPSJs comprise three QPSJs, wherein the first QPSJ has a first terminal connected to an input voltage source or a first bias voltage source 45 defining a first node, and a second terminal connected to a first capacitor defining a second node; the second QPSJ has a first terminal connected to the second terminal of the first QPSJ defining a third node, and a second terminal connected to a second capacitor and the first bias voltage source or the 50 input voltage source defining a fourth node; and the third QPSJ has a first terminal connected to the third node, and a second terminal connected to a second bias voltage source. In operation, an input pulse from the first node through the first QPSJ switches to the third QPSJ, before it switches to 55 the second QPSJ so as to prevent a signal flow in a direction from the first node to the fourth node, or when current arrives from an opposite direction, the first QPSJ switches before the third QPSJ, allowing the signal through.

In one embodiment, the one or more QPSJs forms a QPSJ 60 confluence buffer, wherein the one or more QPSJs comprise four QPSJs, wherein the first QPSJ has a first terminal connected to a first input voltage source, and a second terminal connected to a first capacitor defining node 3; the second QPSJ has a first terminal connected to a second input 65 voltage source, and a second terminal connected to a second capacitor defining node 6, wherein both nodes 3 and 6 are

**18**

connected to node 7; the third QPSJ has a first terminal connected to node 7, and a second terminal connected to a first bias voltage source; and the fourth QPSJ has a first terminal connected to node 7, and a second terminal connected to a third capacitor and the second bias voltage source at node 8, wherein in operation, input pulses from either the first or second input voltage sources result in an output pulse from node 8, but do not result in output from the other input.

In one embodiment, the one or more QPSJs forms a QPSJ based OR gate, wherein the one or more QPSJs comprise six QPSJs, wherein the first to fourth QPSJs define the confluence buffer and the fifth and sixth QPSJs define an island, wherein the confluence buffer is connected to the island in series such that a first terminal of the fifth QPSJ is connected to the output terminal of the confluence buffer and a second terminal of the sixth QPSJ is connected to a clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, the one or more QPSJs forms a QPSJ based AND gate, wherein the one or more QPSJs comprise five QPSJs, wherein the first to fourth QPSJs define the confluence buffer and the fifth QPSJ has a first terminal connected to the output terminal of the confluence buffer and a second terminal connected to a second bias voltage source, and the output terminal of the confluence buffer is connected to a clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, the one or more QPSJs forms a QPSJ based XOR gate, wherein the one or more QPSJs comprise four QPSJs, wherein the first to fourth QPSJs define the confluence buffer and the output terminal of the confluence buffer is connected to a clock signal of a third input voltage source that is connected to a second bias voltage source.

In one embodiment, the one or more QPSJs forms an RS first output node; and the third QPSJ has a first terminal 35 flip-flop or a D flip-flop, wherein the one or more QPSJs comprise two QPSJs, wherein the first QPSJ has a first terminal connected to a bias voltage source at node 2 that in turn is connected to a first input voltage source connected to node 1, a second terminal connected node 3 that in turn is connected to a capacitor; and the second QPSJ has a first terminal connected to node 3, and a second terminal connected to node 4 that is in turn connected to the second input voltage source.

> In one embodiment, the one or more QPSJs forms the RS flip-flop, wherein in operation, a SET input signal at node 1 induces a quantized charge of the Cooper electron pair to the island of node 3, and a RESET input signal at node 4 induces a current pulse opposite to that induced by the SET input signal so as to reset the charge on the island.

> In one embodiment, the one or more QPSJs forms the D flip-flop, wherein in operation, a SET input signal at node 1 induces a quantized charge of the Cooper electron pair to the island of node 3, and a RESET input signal at node 4 is a clock signal that switches the first QPSJ and induces a quantized charge of the Cooper electron pair on the island, and with the next clock pulse, the charge flows through an output terminal to perform a function of the D flip-flop.

> In one embodiment, the one or more QPSJs forms a T flip-flop, wherein the one or more QPSJs comprise two QPSJs, wherein the first QPSJ has a first terminal connected to a bias voltage source at node 3 that in turn is connected to an input voltage source at node 2, the input voltage source connected to node 1, a second terminal connected node 4 that in turn is connected to a capacitor; and the second QPSJ has a first terminal connected to node 4, and a second terminal connected to node 2. In operation, a single clock signal of the input voltage source is input at node 1, and at

each clock pulse, the current pulse toggles from ON to OFF and vice versa, indicating the presence and absence of a quantized charge of the Cooper electron pair on the island with each clock pulse.

In one embodiment, each of the one or more JJs is 5 configured such that when an input current through said JJ exceeds a critical value, a single flux quantum pulse tunnels across said JJ as an output, when the input current is less than the critical value, no single flux quantum pulse tunnels across said JJ as the output, wherein the presence and 10 absence of the single flux quantum pulse in the output form two logic states.

In one embodiment, the one or more QPSJs comprise two QPSJs defining a QPSJ island with a capacitor, and the one or more JJs comprises two JJs defining a JJ loop with a 15 inductor, and the QPSJ island and the JJ loop is connected in series to perform a bridge operation between flux and charge.

In one embodiment, the one or more QPSJs further comprises a third QPSJ having a first terminal connected to <sup>20</sup> a node between the QPSJ island and the JJ loop, and a second terminal connected to a bias voltage source, wherein in operation, a voltage pulse is induced through the third QPSJ that enables or disables the output pulse.

In one embodiment, the superconducting circuit device <sup>25</sup> further comprises at least one complementary quantum logic (CQL) cell, each CQL cell comprising at least one QPSJ, and at least one JJ coupled with the at least one QPSJ to perform one or more logic operations.

In one embodiment, the CQL cell comprises two QPSJs <sup>30</sup> defining a QPSJ island with a capacitor, and two JJs defining a JJ loop with a inductor, and the QPSJ island and the JJ loop is connected in series to perform a bridge operation between flux and charge.

In one embodiment, the CQL cell further comprises a 35 third QPSJ having a first terminal connected to a node between the QPSJ island and the JJ loop, and a second terminal connected to a bias voltage source, wherein in operation, a voltage pulse is induced through the third QPSJ that enables or disables the output pulse.

Without intent to limit the scope of the invention, exemplary methods and their related results according to the embodiments of the present invention are given below. Note that titles or subtitles may be used in the examples for convenience of a reader, which in no way should limit the 45 scope of the invention. Moreover, certain theories are proposed and disclosed herein; however, in no way they, whether they are right or wrong, should limit the scope of the invention so long as the invention is practiced according to the invention without regard for any particular theory or 50 scheme of action.

#### Spice Model Implementation of QPSJ

In one aspect, the present invention relates to implementions of a dual to a resistively and capacitively shunted junction (RCSJ) based JJ SPICE model to model a QPSJ in JSPICE for exploration and demonstration of circuit operations of QPSJ devices. By means of a SPICE model developed for quantum phase-slip junctions, switching of the 60 island to produce quantized-charge pulses with quantized area of 2e as that of the charge of a Cooper pair in a superconductor is demonstrated. The mode of operation of a QPSJ is established, based on a range of device parameters. Compact Model of QPSJ

Quantum phase-slip is a superconducting phenomenon where the phase difference across a nano-wire changes by  $2\pi$

**20**

with the suppression of superconducting order parameter to zero, that is, a temporary decay of superconductivity in a continuous superconducting nanowire. This event occurring at a point in the nano-wire introduces a Coulomb blockade, i.e., blockade of current/electric charge through the wire essentially behaving like an insulator. The phase-slip event is caused by a quantum unit of magnetic flux tunneling across the nanowire through the insulating substrate/layer on which the device is fabricated. This was observed as a resistance tail below superconducting transition in experiments [24, 27, 45]. This phenomenon has been identified as a dual process to Josephson tunneling. While a charge tunnels between two superconducting regions across an insulating barrier in a Josephson junction (JJ), inducing a flux quantum in the corresponding loop, a QPSJ can be viewed as flux tunneling across a superconducting nanowire (barrier for flux) creating a voltage drop at the ends of the wire. The duality between Josephson tunneling and quantum phase-slip can be characterized by the charge-flux relationship in Maxwell's equations. Therefore, a dualdevice to a JJ, called a QPSJ, can be established. Accordingly, an I-V relationship of a QPSJ can be obtained by replacing phase by charge, current term by voltage term and capacitance term by inductance term [25]. The two equations that describe a QPSJ are therefore given by:

$$V = V_C \sin(q) + L\frac{dI}{dt} + RI \tag{1}$$

where

$$I = \frac{2e}{2\pi} \frac{dq}{dt} \tag{2}$$

Here, V is the voltage across the junction,  $V_C$  is the critical voltage of the QPSJ, L is the geometric inductance of the QPSJ, I is the current through the junction, R is the normal resistance of the QPSJ, and q is the charge equivalent in the QPSJ normalized to the charge of a Cooper pair (2e) and the term

$\frac{1}{2\pi}$

to represent q as a phase corresponding to charge. Therefore, the relation of q to charge 2e is equivalent to relation of superconducting phase  $\phi$  and flux quantum  $\Phi_0$ , with e being charge of an electron. In practical implementation, the various parameters of the junction can be varied by varying the physical dimensions and material of the junction.