US010546748B2

# (12) United States Patent Yu et al.

### (54) TIN OXIDE FILMS IN SEMICONDUCTOR DEVICE MANUFACTURING

(71) Applicant: Lam Research Corporation, Fremont, CA (US)

(72) Inventors: Jengyi Yu, San Ramon, CA (US);

Samantha Tan, Fremont, CA (US); Yu

Jiang, San Jose, CA (US); Hui-Jung

Wu, Pleasanton, CA (US); Richard

Wise, Los Gatos, CA (US); Yang Pan,

Los Altos, CA (US); Nader Shamma, Cupertino, CA (US); Boris Volosskiy,

San Jose, CA (US)

(73) Assignee: Lam Research Corporation, Fremont,

CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/894,635

(22) Filed: **Feb. 12, 2018**

(65) Prior Publication Data

US 2018/0240667 A1 Aug. 23, 2018

#### Related U.S. Application Data

- (60) Provisional application No. 62/479,709, filed on Mar. 31, 2017, provisional application No. 62/460,573, filed on Feb. 17, 2017.

- (51) Int. Cl.

H01L 21/311 (2006.01)

H01L 21/033 (2006.01)

(Continued)

- (52) **U.S. Cl.**CPC ..... *H01L 21/0332* (2013.01); *H01L 21/0262* (2013.01); *H01L 21/0274* (2013.01); (Continued)

### (10) Patent No.: US 10,546,748 B2

(45) **Date of Patent:** Jan. 28, 2020

#### (58) Field of Classification Search

CPC ..... H04W 40/22; H04W 76/30; H04W 88/04; H01J 2237/186; H01J 2237/3321; (Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,708,766 A 11/1987 Hynecek 4,778,562 A 10/1988 Chang (Continued)

#### FOREIGN PATENT DOCUMENTS

KR 10-2017-0141673 A 12/2017

#### OTHER PUBLICATIONS

Office Action, dated Feb. 9, 2017, issued in U.S. Appl. No. 15/195,348. (Continued)

Primary Examiner — Lan Vinh (74) Attorney, Agent, or Firm — Weaver Austin Villeneuve & Sampson LLP

#### (57) ABSTRACT

Tin oxide films are used as spacers and hardmasks in semiconductor device manufacturing. In one method, tin oxide layer is formed conformally over sidewalls and horizontal surfaces of protruding features on a substrate. A passivation layer is then formed over tin oxide on the sidewalls, and tin oxide is then removed from the horizontal surfaces of the protruding features without being removed at the sidewalls of the protruding features. The material of the protruding features is then removed while leaving the tin oxide that resided at the sidewalls of the protruding features, thereby forming tin oxide spacers. Hydrogen-based and chlorine-based dry etch chemistries are used to selectively etch tin oxide in a presence of a variety of materials. In another method a patterned tin oxide hardmask layer is formed on a substrate by forming a patterned layer over an unpatterned tin oxide and transferring the pattern to the tin oxide.

#### 20 Claims, 20 Drawing Sheets

| (51)                                               | Int. Cl.                                                              |                                           |                                                                                                                                    | 2013/0161625 A1*                                                                                                                  | 6/2013                                                              | Ku H01L 27/1288                               |  |

|----------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------|--|

|                                                    | H01L 21/027                                                           |                                           | (2006.01)                                                                                                                          | 2012/0200071 41*                                                                                                                  | 11/2012                                                             | D-X/11: HOLL 21/0272                          |  |

|                                                    | H01L 21/67                                                            |                                           | (2006.01)                                                                                                                          | 2013/03098/1 A1*                                                                                                                  | 11/2013                                                             | DeVilliers H01L 21/0273<br>438/703            |  |

|                                                    | H01L 21/02                                                            |                                           | (2006.01)                                                                                                                          | 2014/0308812 A1*                                                                                                                  | 10/2014                                                             | Arghavani H01L 21/7688                        |  |

|                                                    | H01L 21/3065                                                          |                                           | (2006.01)                                                                                                                          |                                                                                                                                   |                                                                     | 438/675                                       |  |

|                                                    | H01L 21/3213                                                          |                                           | (2006.01)                                                                                                                          | 2015/0243661 A1*                                                                                                                  | 8/2015                                                              | Matsumoto H01L 21/823814                      |  |

|                                                    | H01L 21/465                                                           |                                           | (2006.01)                                                                                                                          | 2015/02/7220 4.1                                                                                                                  | 0/2015                                                              | D1                                            |  |

|                                                    | H01L 21/467                                                           |                                           | (2006.01)                                                                                                                          | 2015/0247238 A1<br>2015/0287612 A1                                                                                                |                                                                     | Pasquale et al.<br>Luere et al.               |  |

|                                                    | H01J 37/32                                                            |                                           | (2006.01)                                                                                                                          | 2015/026/012 A1*                                                                                                                  |                                                                     | Cantone H01L 21/823431                        |  |

|                                                    | H01L 21/683                                                           |                                           | (2006.01)                                                                                                                          |                                                                                                                                   |                                                                     | 438/702                                       |  |

|                                                    | H01L 21/68                                                            |                                           | (2006.01)                                                                                                                          | 2016/0203982 A1*                                                                                                                  | 7/2016                                                              | Lin H01L 21/3081                              |  |

| (52)                                               | U.S. Cl.                                                              |                                           |                                                                                                                                    | 2016/0314985 A1                                                                                                                   | 10/2016                                                             | Vana et al                                    |  |

|                                                    |                                                                       | 21/0217                                   | 75 (2013.01); <i>H01L 21/02565</i>                                                                                                 | 2016/0314983 A1<br>2016/0336178 A1                                                                                                |                                                                     | Yang et al.<br>Swaminathan et al.             |  |

|                                                    |                                                                       |                                           | 1L 21/0337 (2013.01); H01L                                                                                                         | 2018/0012759 A1                                                                                                                   |                                                                     | Smith et al.                                  |  |

|                                                    | `                                                                     | , ,                                       | ); <i>H01L 21/31116</i> (2013.01);                                                                                                 | 2018/0233398 A1                                                                                                                   | 8/2018                                                              | van Cleemput et al.                           |  |

|                                                    | H01L 21/31122 (2013.01); H01L 21/31138                                |                                           |                                                                                                                                    |                                                                                                                                   |                                                                     |                                               |  |

|                                                    | (2013.01); <i>H01L 21/31144</i> (2013.01); <i>H01L</i>                |                                           |                                                                                                                                    | OTHER PUBLICATIONS                                                                                                                |                                                                     |                                               |  |

|                                                    | `                                                                     | <b>86</b> (2013.01); <b>H01L</b> 21/32137 | Notice of Allowance, dated Jun. 26, 2017, issued in U.S. Appl. No.                                                                 |                                                                                                                                   |                                                                     |                                               |  |

|                                                    |                                                                       | <i>L 21/32139</i> (2013.01); <i>H01L</i>  | 15/195,348.                                                                                                                        |                                                                                                                                   |                                                                     |                                               |  |

|                                                    | 21/46.                                                                | 01); <i>H01L 21/467</i> (2013.01);        | Choi, WS., (Dec. 25, 2009) "The Fabrication of Tin Oxide Films                                                                     |                                                                                                                                   |                                                                     |                                               |  |

|                                                    | H01L 21/67069 (2013.01); H01L 21/67167                                |                                           |                                                                                                                                    | by Atomic Layer Deposition using Tetrakis(Ethylmethylamino) Tin                                                                   |                                                                     |                                               |  |

|                                                    | (2013.01); <b>H01L 21/6720</b> 7 (2013.01); H01J                      |                                           |                                                                                                                                    | Precursor," Transactions on Electrical and Electronic Materials,                                                                  |                                                                     |                                               |  |

|                                                    | <i>37/3211</i> (2013.01); <i>H01J 37/32651</i> (2013.01);             |                                           |                                                                                                                                    | 10(6):200-202.<br>Du, X. et al., (Jul./Aug. 2005) "In situ examination oftin oxide                                                |                                                                     |                                               |  |

|                                                    | H01J 2237/186 (2013.01); H01J 2237/334                                |                                           |                                                                                                                                    | atomic layer deposition using quartz crystal microbalance and                                                                     |                                                                     |                                               |  |

|                                                    | (2013.01); H01J 2237/3321 (2013.01); H01L                             |                                           |                                                                                                                                    | Fourier transform infrared techniques," J. Vac. Sci. Technol. A,                                                                  |                                                                     |                                               |  |

| 21/0228 (2013.01); H01L 21/02205 (2013.01);        |                                                                       |                                           | 23(4):581-588.                                                                                                                     | VO) 44 A 1                                                                                                                        | ' T                                                                 |                                               |  |

|                                                    | H0                                                                    |                                           | 02274 (2013.01); H01L 21/68                                                                                                        |                                                                                                                                   |                                                                     | ic Layer Deposition of Indium Tin             |  |

| (2013.01); H01L 21/6833 (2013.01)                  |                                                                       |                                           |                                                                                                                                    | Oxide Thin Films Using Nonhalogenated Precursors," <i>J. Phys. Chem. C</i> , 112(6):1938-1945.                                    |                                                                     |                                               |  |

| (58)                                               |                                                                       |                                           |                                                                                                                                    |                                                                                                                                   | Elam, J.W., et al, (Mar./Apr. 2008) "Atomic layer deposition of tin |                                               |  |

|                                                    | CPC                                                                   |                                           |                                                                                                                                    | oxide films using tetrakis(dimethylamino) tin," J. Vac. Sci. Technol.                                                             |                                                                     |                                               |  |

|                                                    | 37/32651; H01L 21/02175; H01L 21/02274; H01L                          |                                           |                                                                                                                                    | A, 26(2):244-252.                                                                                                                 |                                                                     |                                               |  |

|                                                    | 21/02203, 1101L 21/02274, 1101L 21/02575; H01L 21/0274; H01L 21/0332; |                                           |                                                                                                                                    | Heo, J., et al., (2010) "Low Temperature Atomic Layer Deposition of Tin Oxide," <i>Chemistry of Materials</i> , 22(17):4964-4973. |                                                                     |                                               |  |

|                                                    | H01L 21/02365, 1101L 21/0274, 1101L 21/0332,                          |                                           |                                                                                                                                    | Heo, J., et al., (2012) "Atomic layer deposition oftin oxide with                                                                 |                                                                     |                                               |  |

| 21/31144; H01L 21/467; H01L 21/67069               |                                                                       |                                           |                                                                                                                                    |                                                                                                                                   | nitric oxide as an oxidant gas," J. Mater. Chem., 22:4599-4602.     |                                               |  |

| USPC 216/67, 72, 75; 438/706, 710, 714, 722,       |                                                                       |                                           |                                                                                                                                    | Kwon, K.H., et al., (Mar./Apr. 2010) "Etch mechanism of In <sub>2</sub> O <sub>3</sub> and                                        |                                                                     |                                               |  |

| 438/723, 758                                       |                                                                       |                                           |                                                                                                                                    | $SnO_2$ thin films in HBr-based inductively coupled plasmas," J. Vac.                                                             |                                                                     |                                               |  |

| See application file for complete search history.  |                                                                       |                                           |                                                                                                                                    | Sci. Technol. A 28(2):226-231. Li. V. et al. (2012) "Tip Oxide with Centrelled Membelsey and                                      |                                                                     |                                               |  |

| are application into for complete scarcin mistory. |                                                                       |                                           | Li, X., et al., (2012) "Tin Oxide with Controlled Morphology and Crystallinity by Atomic Layer Deposition onto Graphene Nanosheets |                                                                                                                                   |                                                                     |                                               |  |

| (56)                                               |                                                                       |                                           |                                                                                                                                    | for Enhanced Lithium Storage," Advanced Function Materials,                                                                       |                                                                     |                                               |  |

|                                                    |                                                                       |                                           |                                                                                                                                    | 22:1647-1654.                                                                                                                     | U                                                                   |                                               |  |

| U.S. PATENT DOCUMENTS                              |                                                                       |                                           | Mohri et al., (Oct. 1990) "Plasma Etching of ITO Thin Films Using                                                                  |                                                                                                                                   |                                                                     |                                               |  |

|                                                    | 5,286,337 A                                                           | 2/1994                                    | Tsou                                                                                                                               | · <del>-</del>                                                                                                                    | ire," <i>Japa</i>                                                   | nese Journal of Applied Physics,              |  |

|                                                    | / /                                                                   |                                           | Saia et al.                                                                                                                        | 29(10):L1932-L1935. Mullings M N et al                                                                                            | (Nov /D                                                             | ec. 2013) "Tin oxide atomic layer             |  |

|                                                    | , ,                                                                   | 3/1997                                    |                                                                                                                                    | <del>-</del>                                                                                                                      | •                                                                   | ylamino)tin and water," J. Vac. Sci.          |  |

|                                                    | , ,                                                                   |                                           | Holland et al.<br>Chen H01L 21/32136                                                                                               | Technol. A, 31(6):061                                                                                                             | -                                                                   | •                                             |  |

|                                                    | 0,050,070 11                                                          | 3/ 2000                                   | 216/67                                                                                                                             |                                                                                                                                   |                                                                     | (a) "Silicon Processing for the VLSI          |  |

|                                                    | 6,368,978 B1                                                          | 4/2002                                    | Kumar et al.                                                                                                                       | · · · · · · · · · · · · · · · · · · ·                                                                                             | Op /                                                                | 1, Lattice Press, pp. 545-547.                |  |

|                                                    |                                                                       |                                           | Chiang et al.                                                                                                                      |                                                                                                                                   |                                                                     | re-Etched SnO <sub>2</sub> Glasses Applied to |  |

|                                                    | •                                                                     |                                           | Chiang et al.<br>Fleischer et al.                                                                                                  | 2014, Article ID 9076                                                                                                             |                                                                     | " Journal of Nanomaterials, vol.              |  |

|                                                    | / /                                                                   |                                           | Greer et al.                                                                                                                       | •                                                                                                                                 |                                                                     | d Feb. 9, 2018, Cleemput et al.               |  |

|                                                    | 8,435,608 B1                                                          | 5/2013                                    | Subramonium et al.                                                                                                                 | 11                                                                                                                                |                                                                     | d Written Opinion dated Jun. 27,              |  |

|                                                    | / /                                                                   |                                           | Park et al.                                                                                                                        | 2018 issued in Applic                                                                                                             | -                                                                   | <u>.</u>                                      |  |

|                                                    | 8,969,110 B2*                                                         | 3/2013                                    | Choi H01L 51/56<br>438/26                                                                                                          |                                                                                                                                   | -                                                                   | d Written Opinion dated May 17,               |  |

|                                                    | 9,437,443 B2                                                          | 9/2016                                    | Brink et al.                                                                                                                       | 11                                                                                                                                |                                                                     | PCT/US2019/015559.                            |  |

|                                                    | 9,824,893 B1 1                                                        |                                           | Smith et al.                                                                                                                       | 15/893,458.                                                                                                                       | uea sep                                                             | 13, 2019, issued in U.S. Appl. No.            |  |

|                                                    |                                                                       | 4/2006                                    | Li et al.<br>Hsiung et al                                                                                                          | ,                                                                                                                                 | arv Repor                                                           | rt on Patentability dated Aug. 29,            |  |

| /1 11 17                                           | 1/1/14AIIX AI                                                         | 77 71 H H7                                | 1 I STITUTO PL 31                                                                                                                  |                                                                                                                                   |                                                                     |                                               |  |

<sup>\*</sup> cited by examiner

2006/0148118 A1

2006/0270209 A1

2010/0120247 A1

7/2006 Hsiung et al. 11/2006 Mitsui et al.

5/2010 Park

2011/0198627 A1 8/2011 Maindron et al.

International Preliminary Report on Patentability dated Aug. 29,

2019 issued in Application No. PCT/US2018/018019.

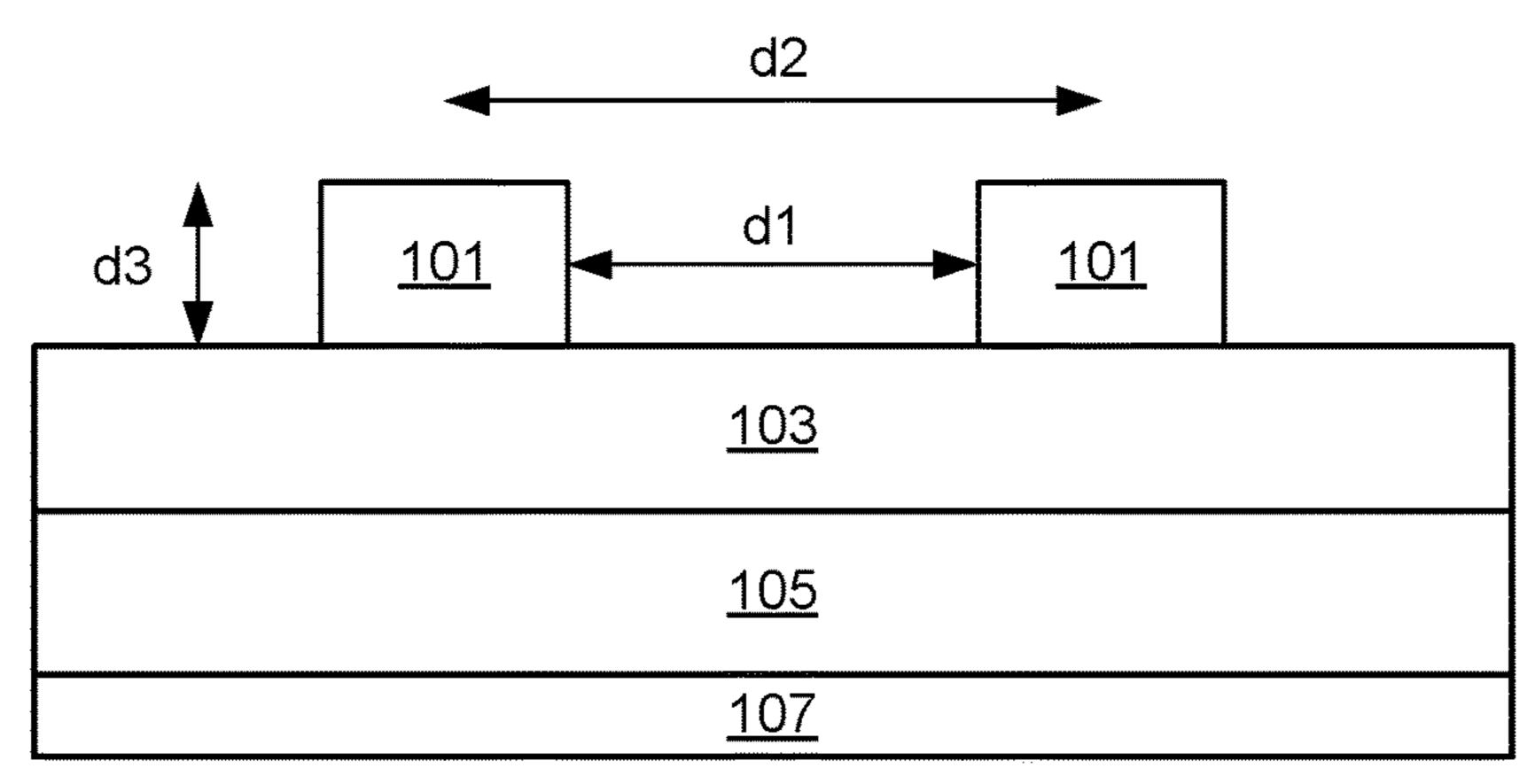

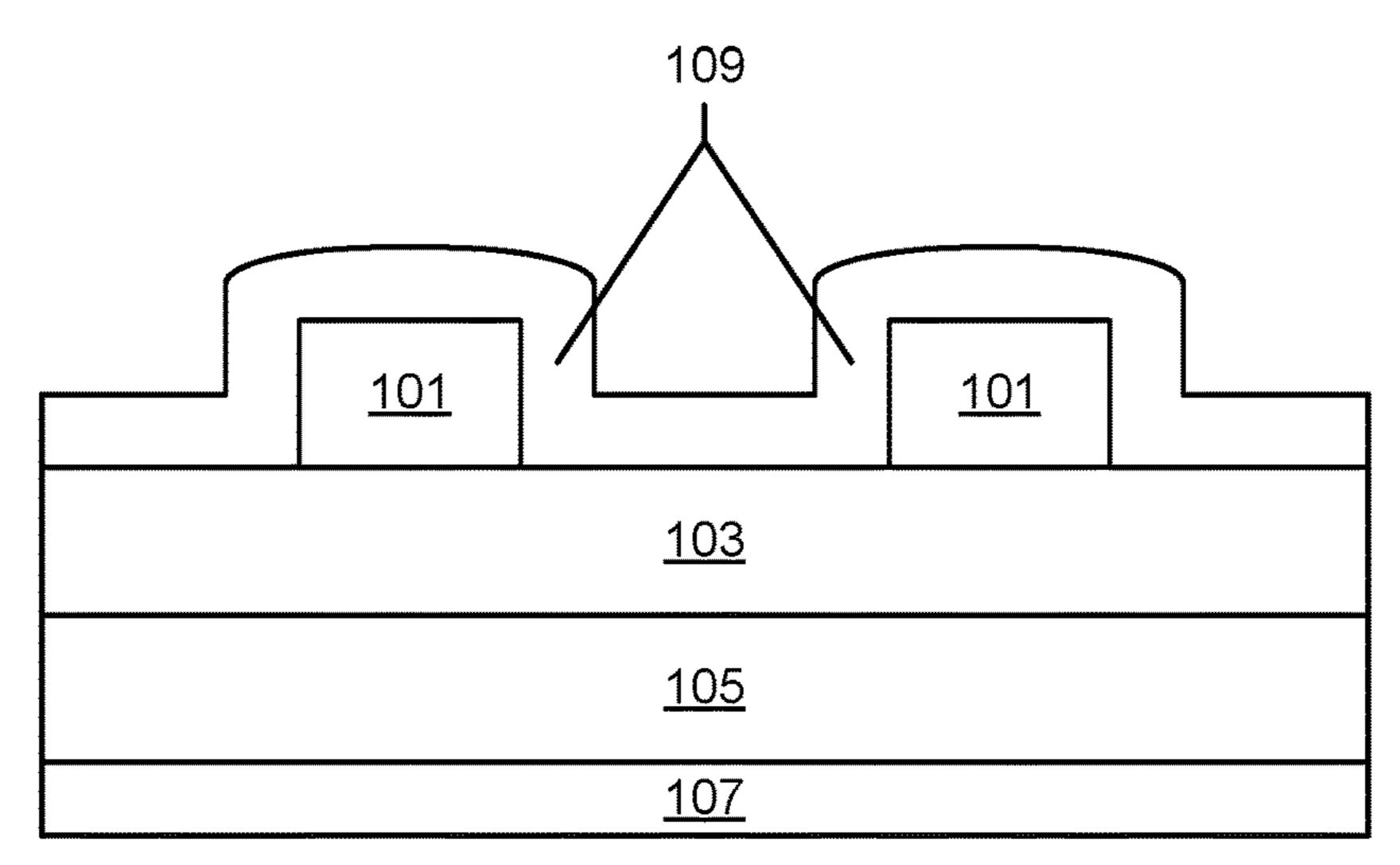

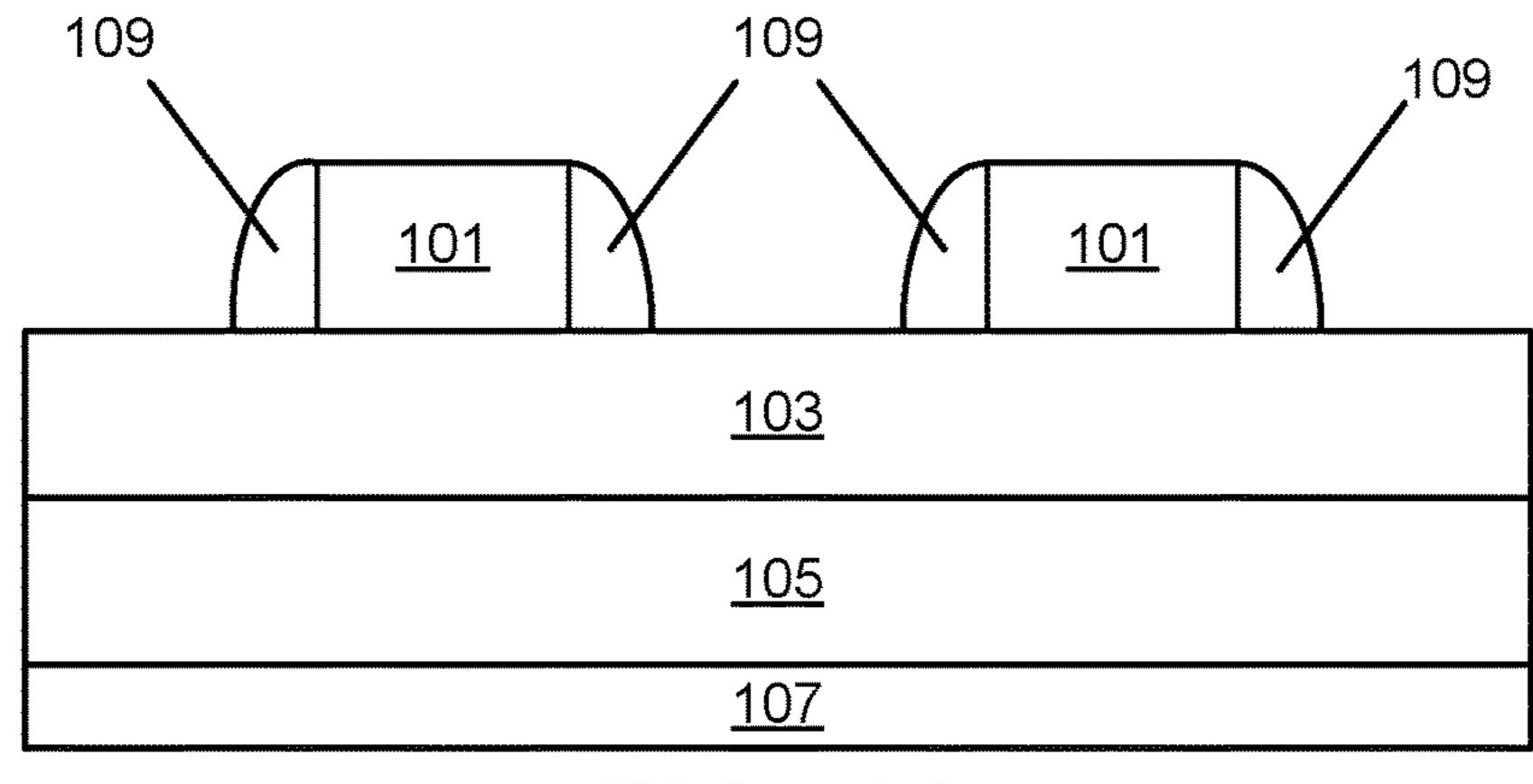

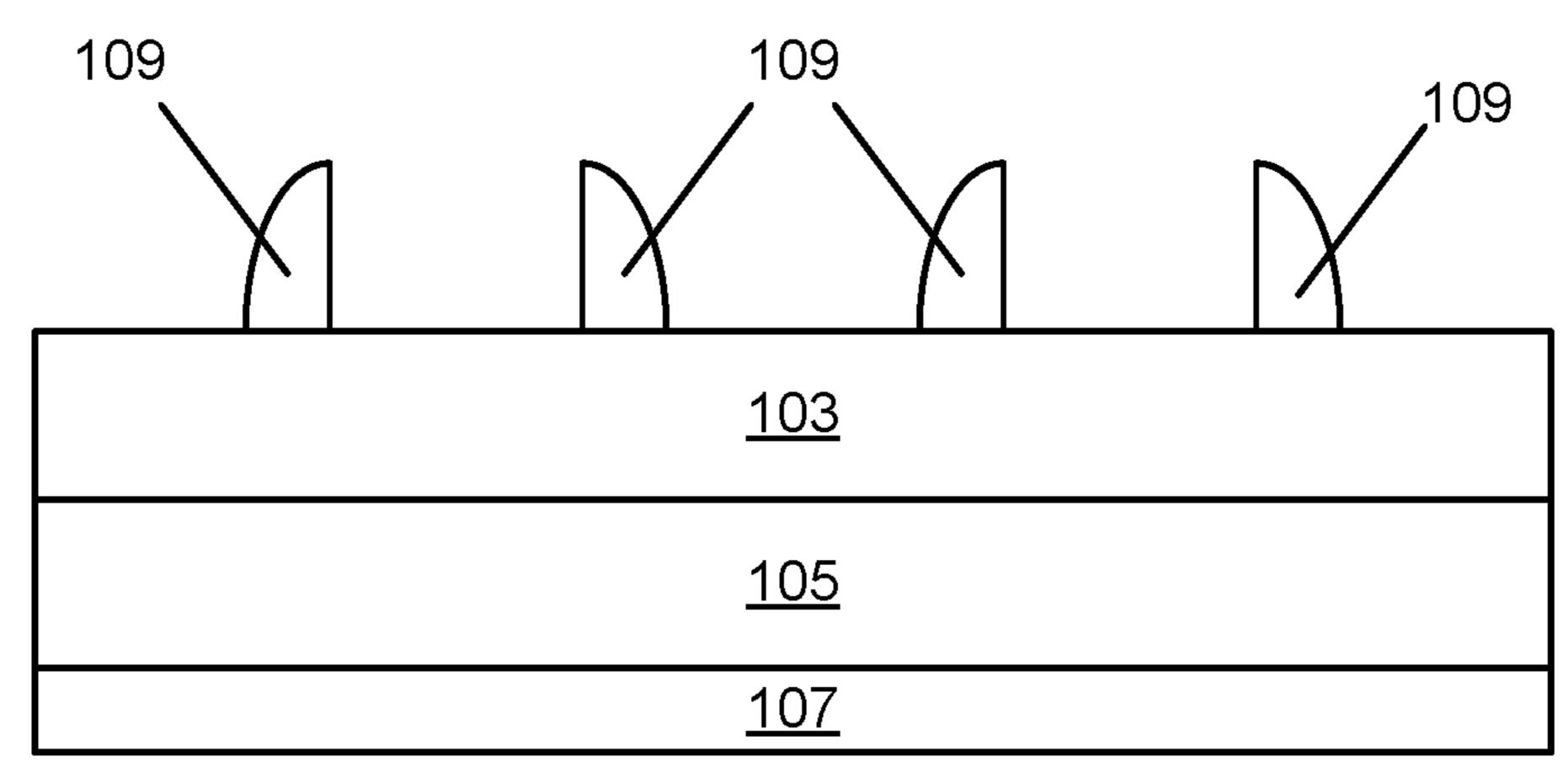

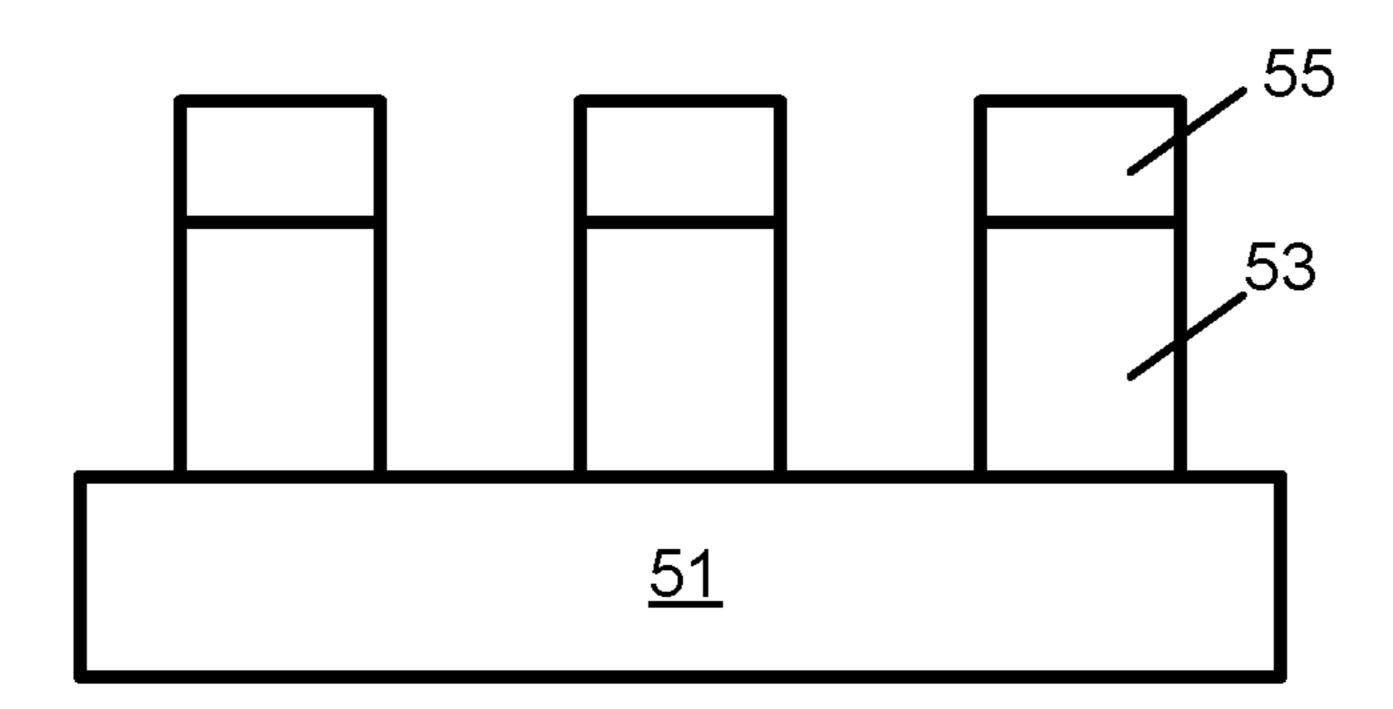

FIG. 1A

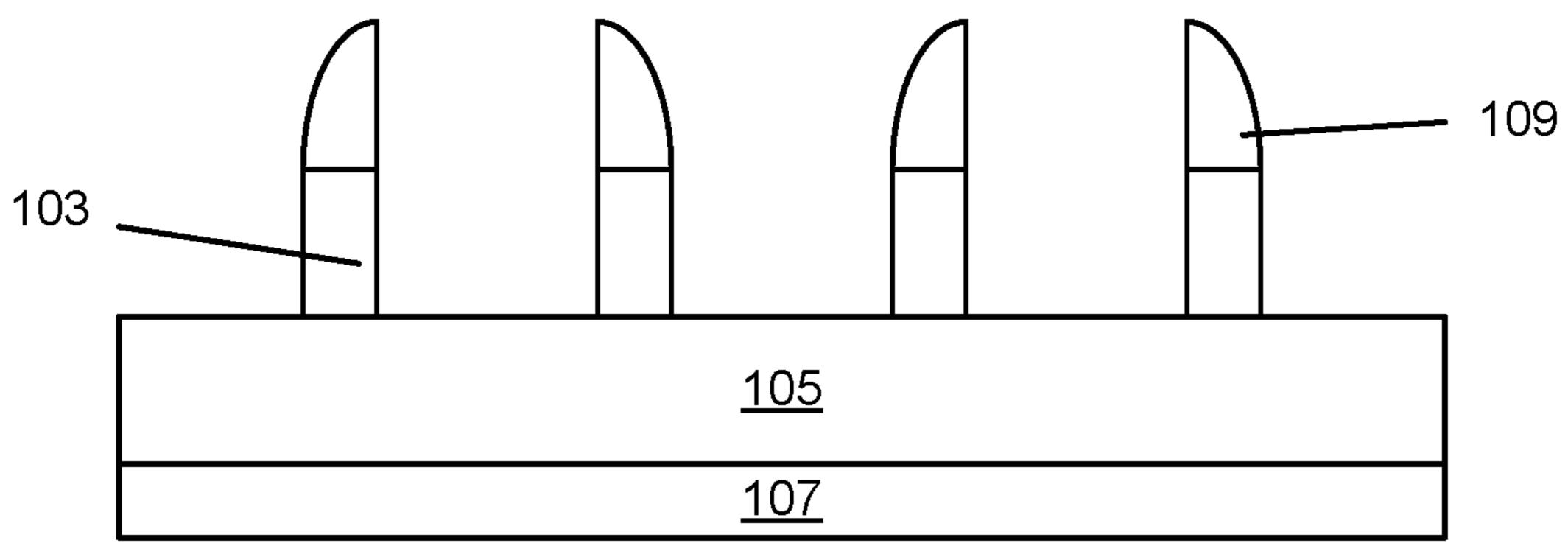

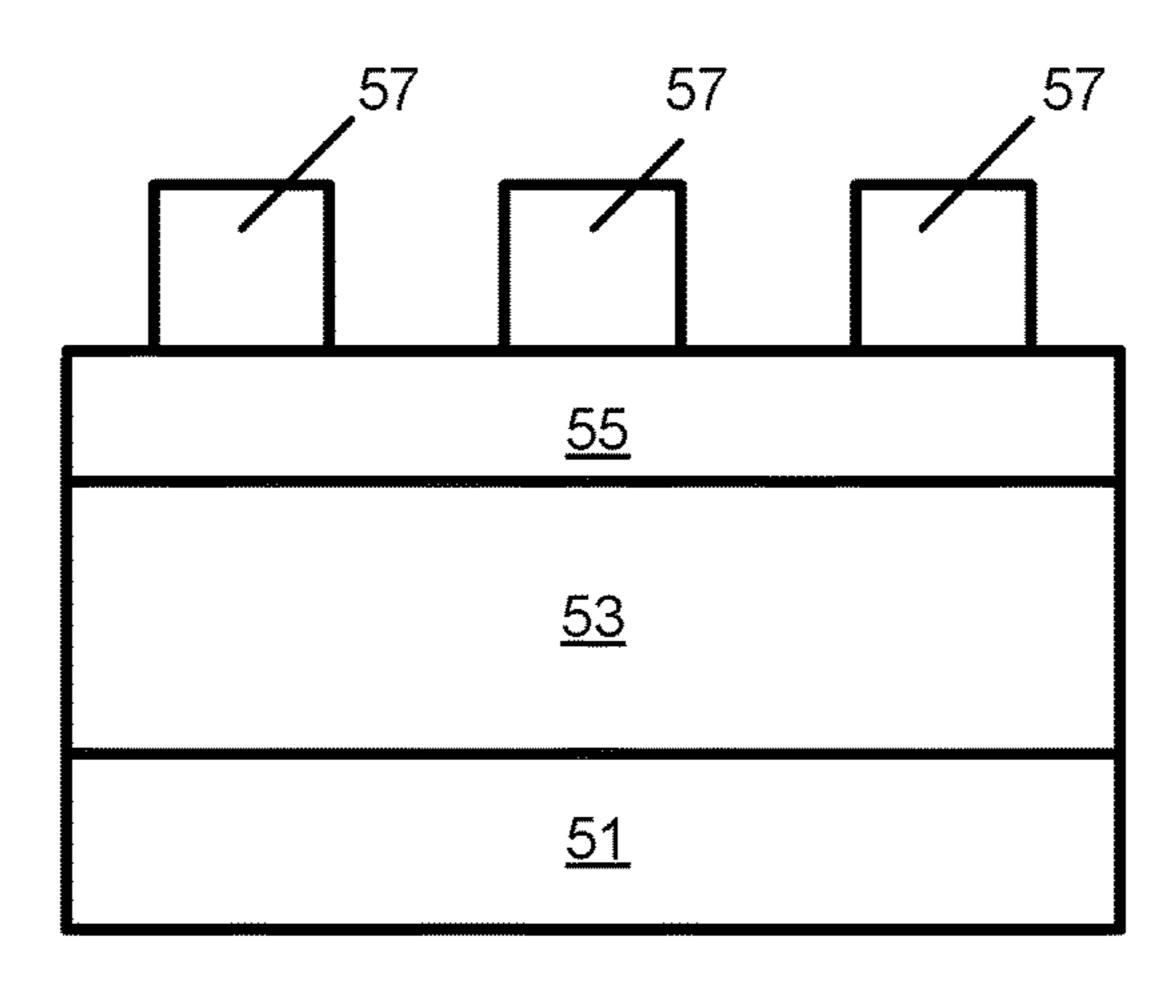

FIG. 1B

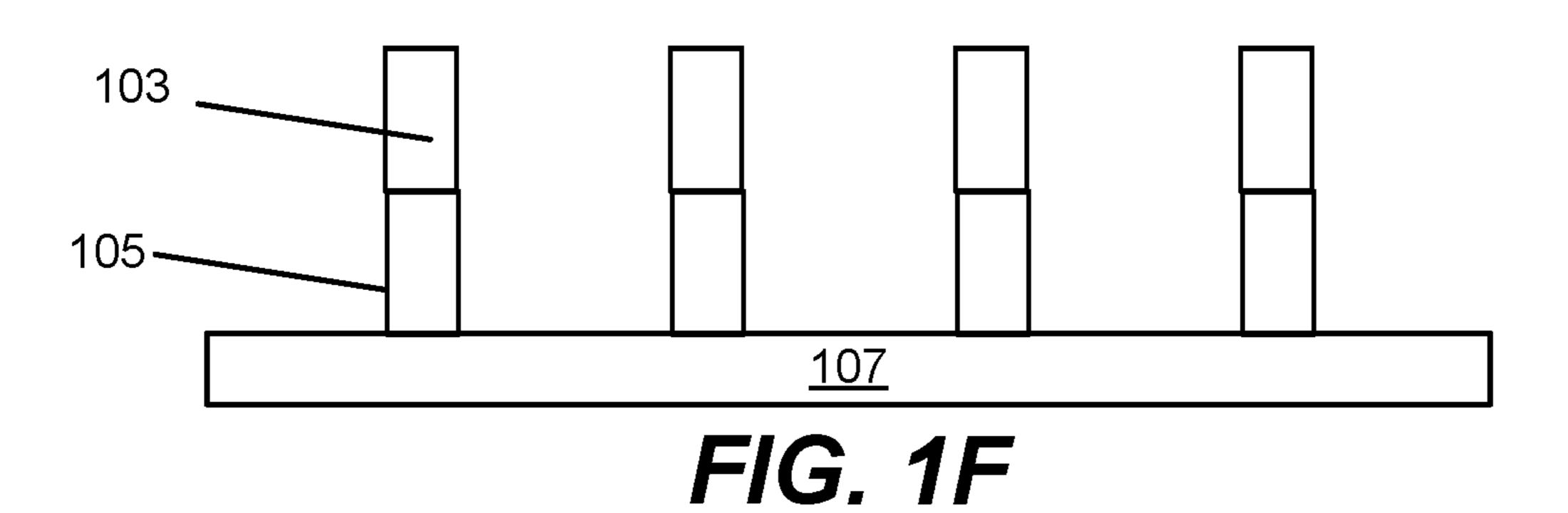

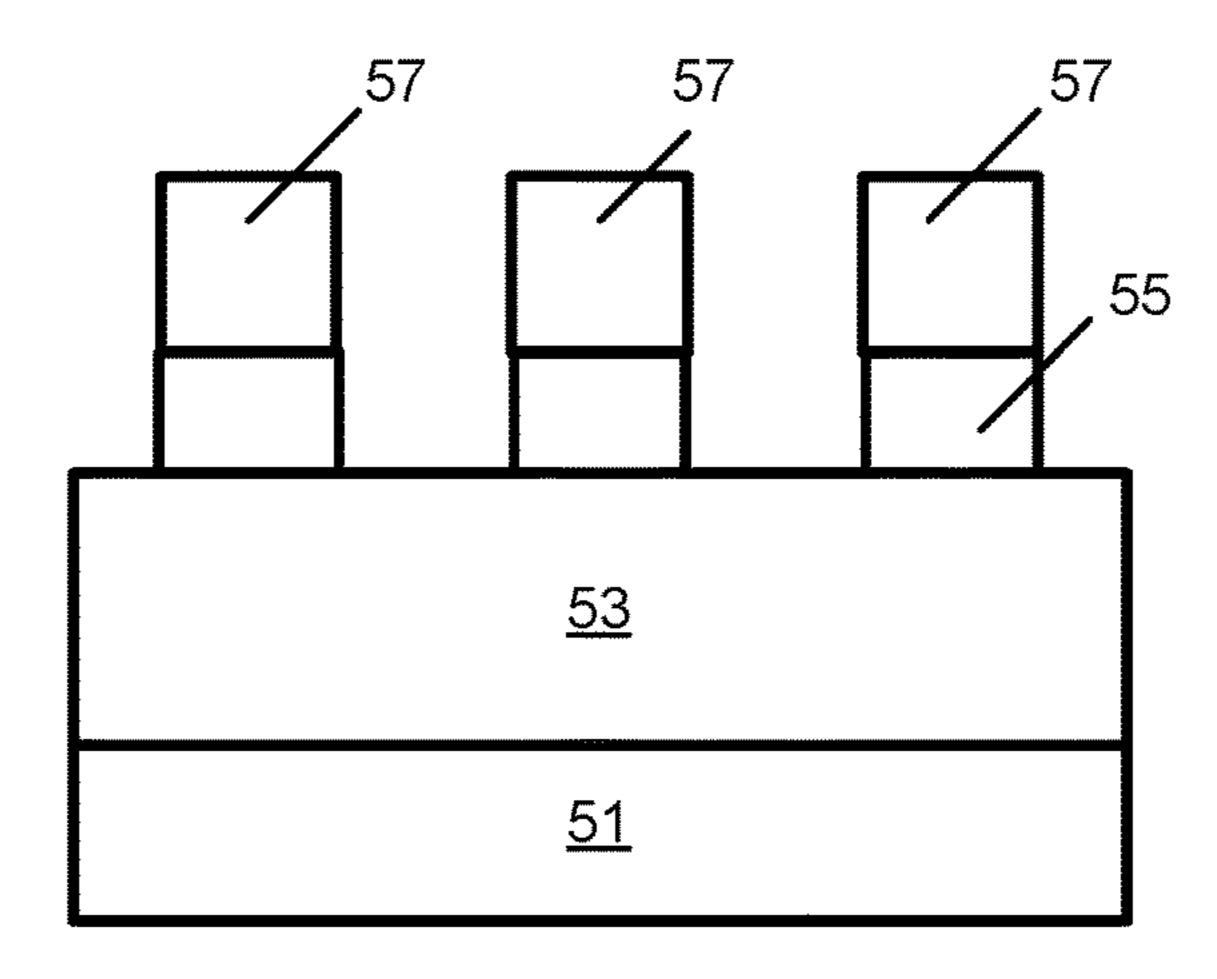

FIG. 1C

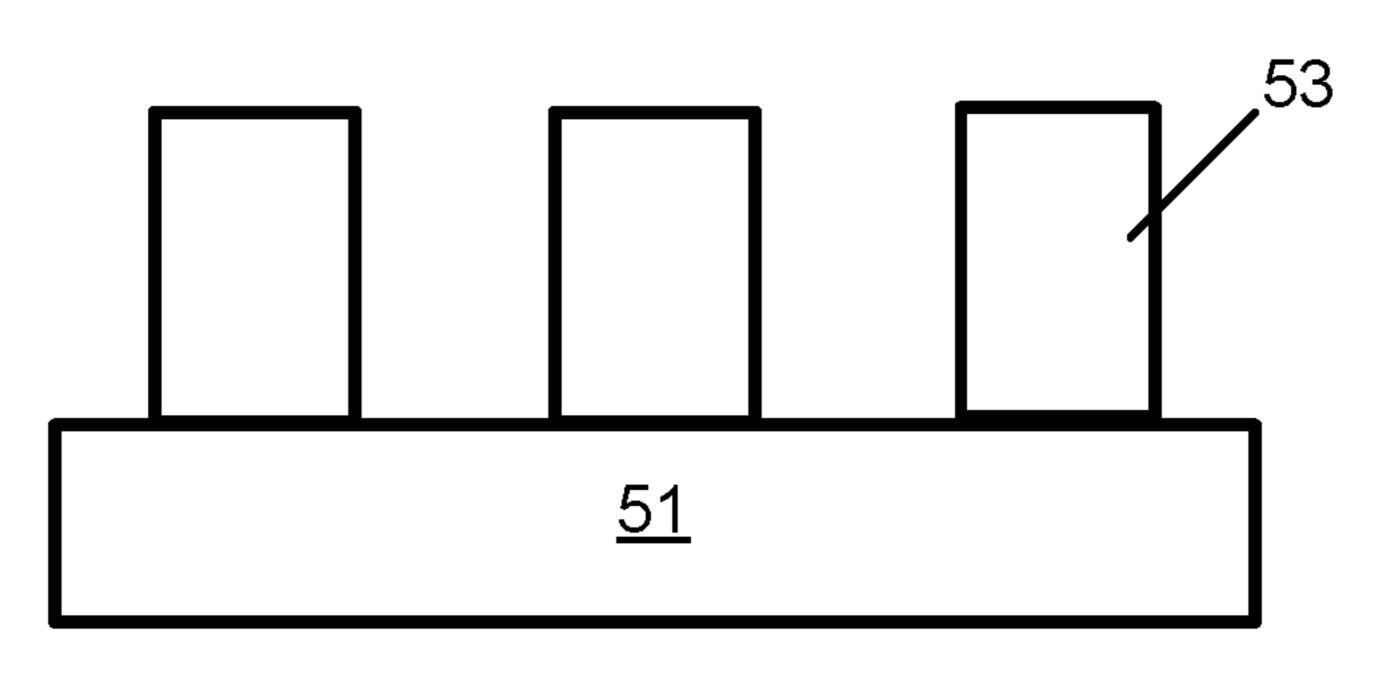

FIG. 1D

FIG. 1E

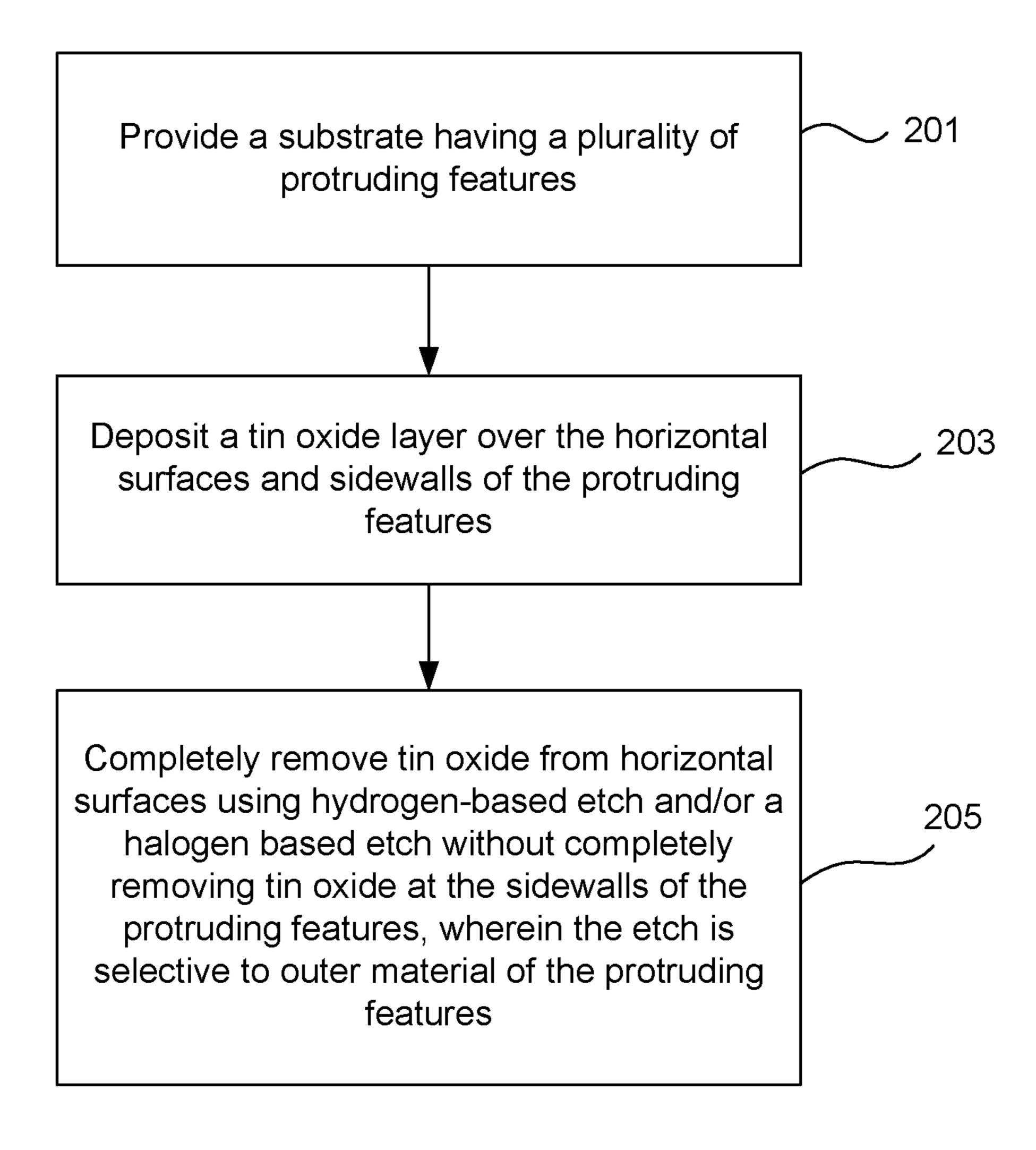

Fig. 2

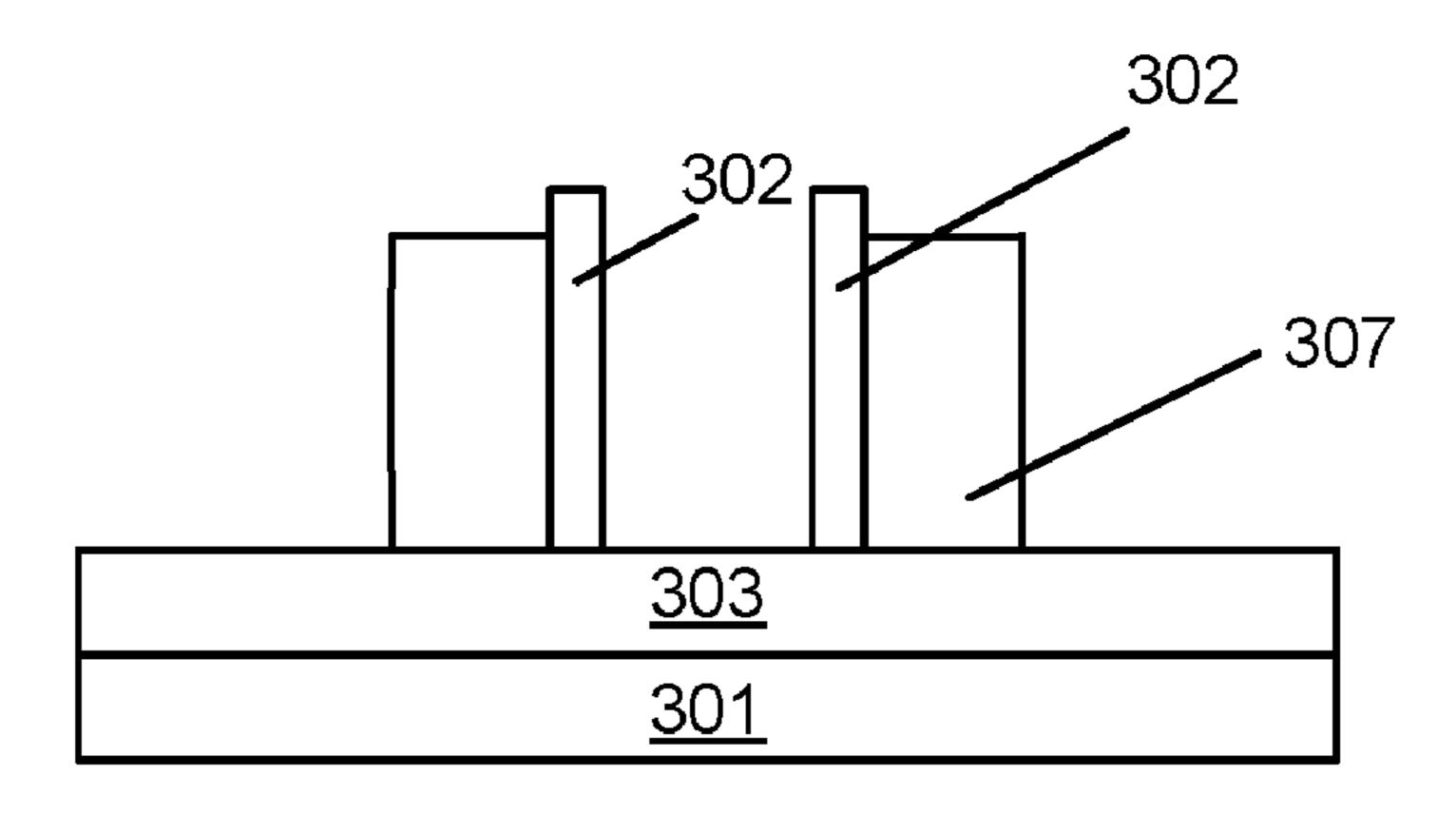

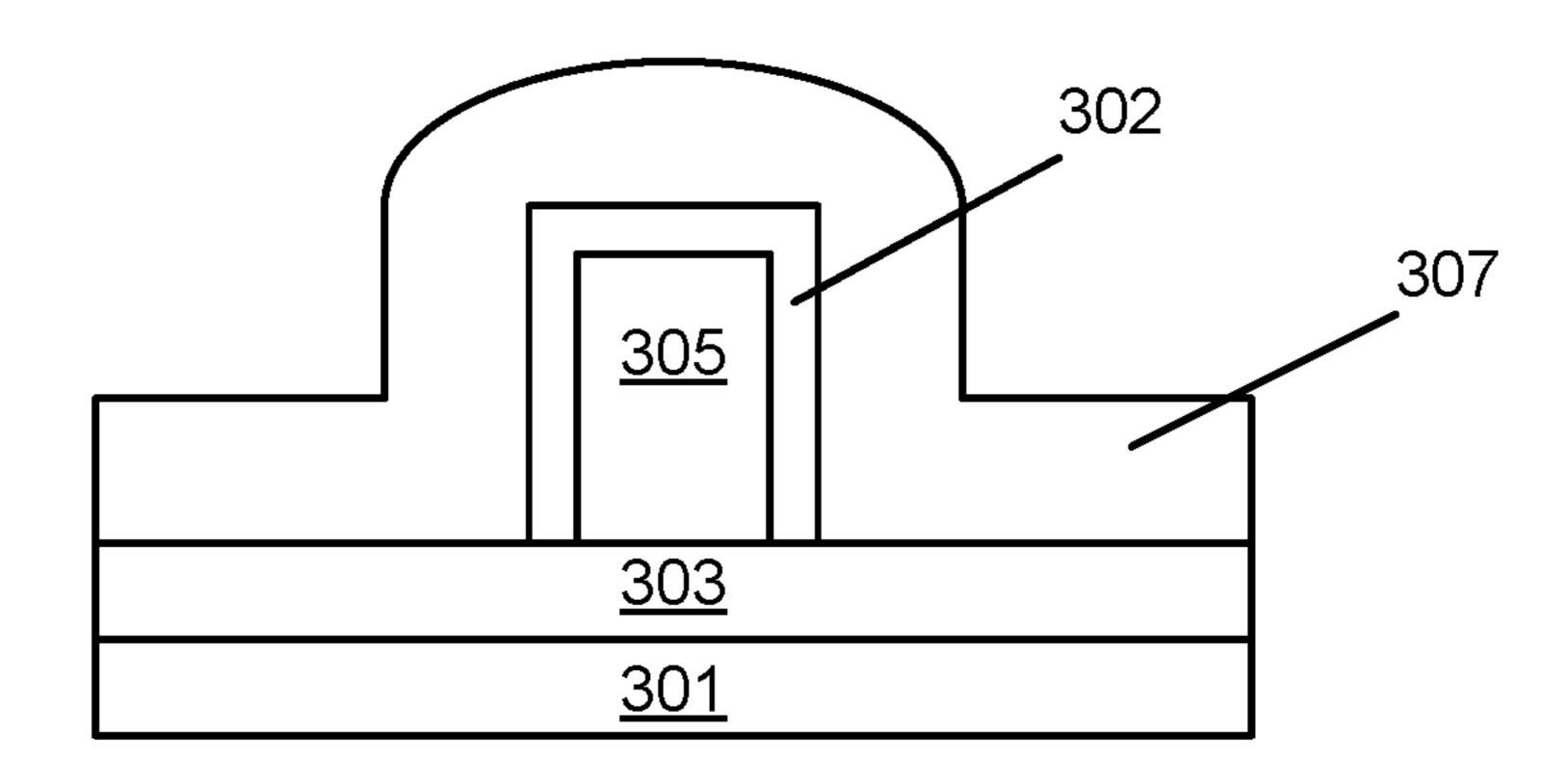

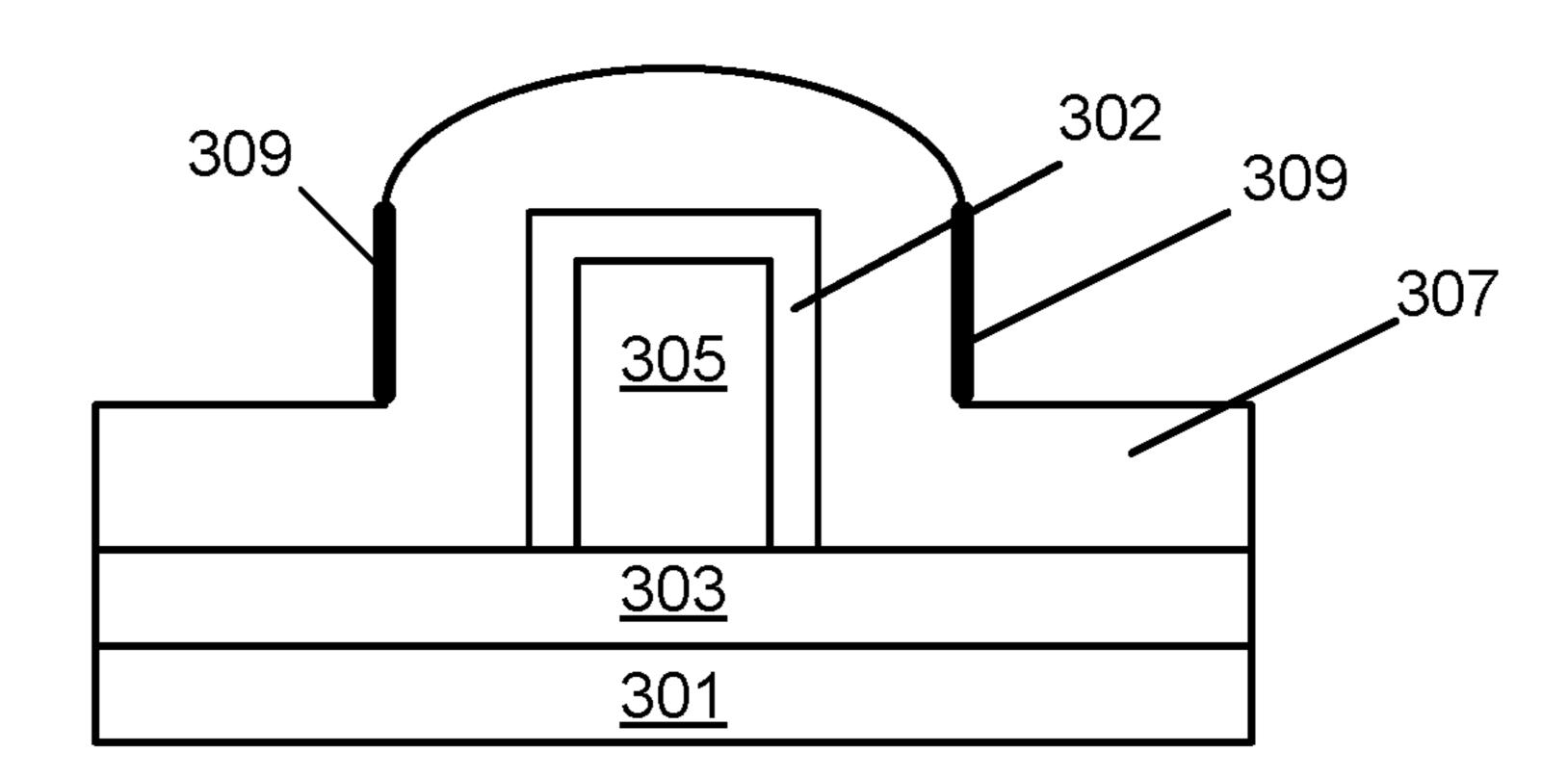

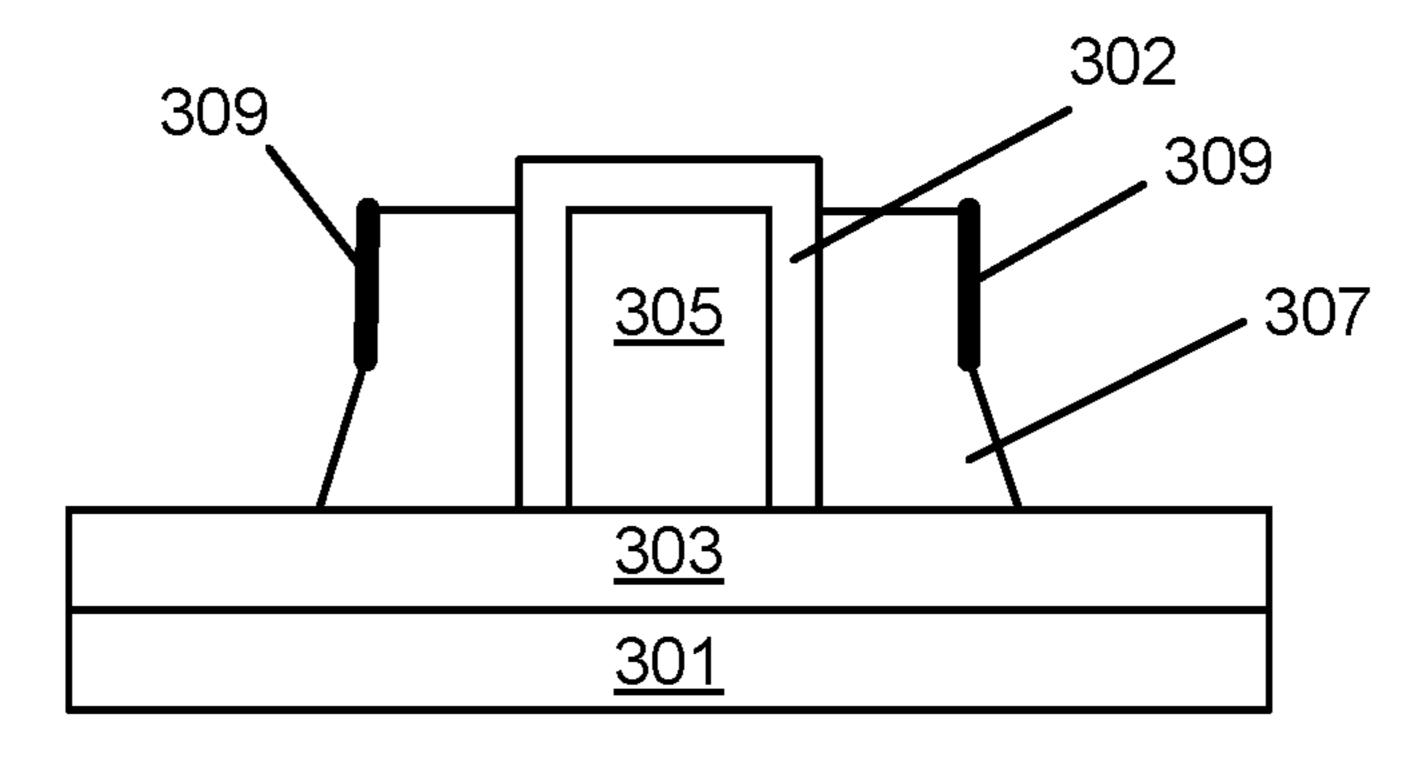

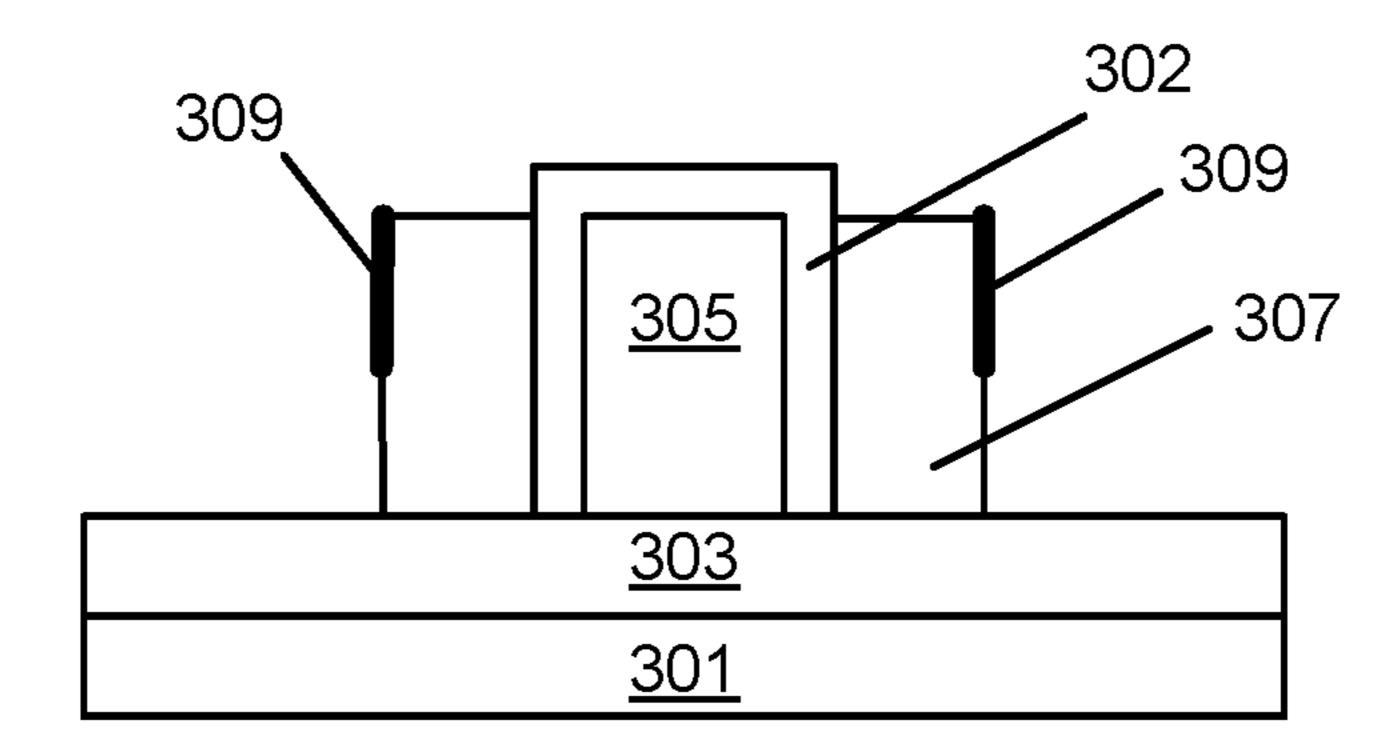

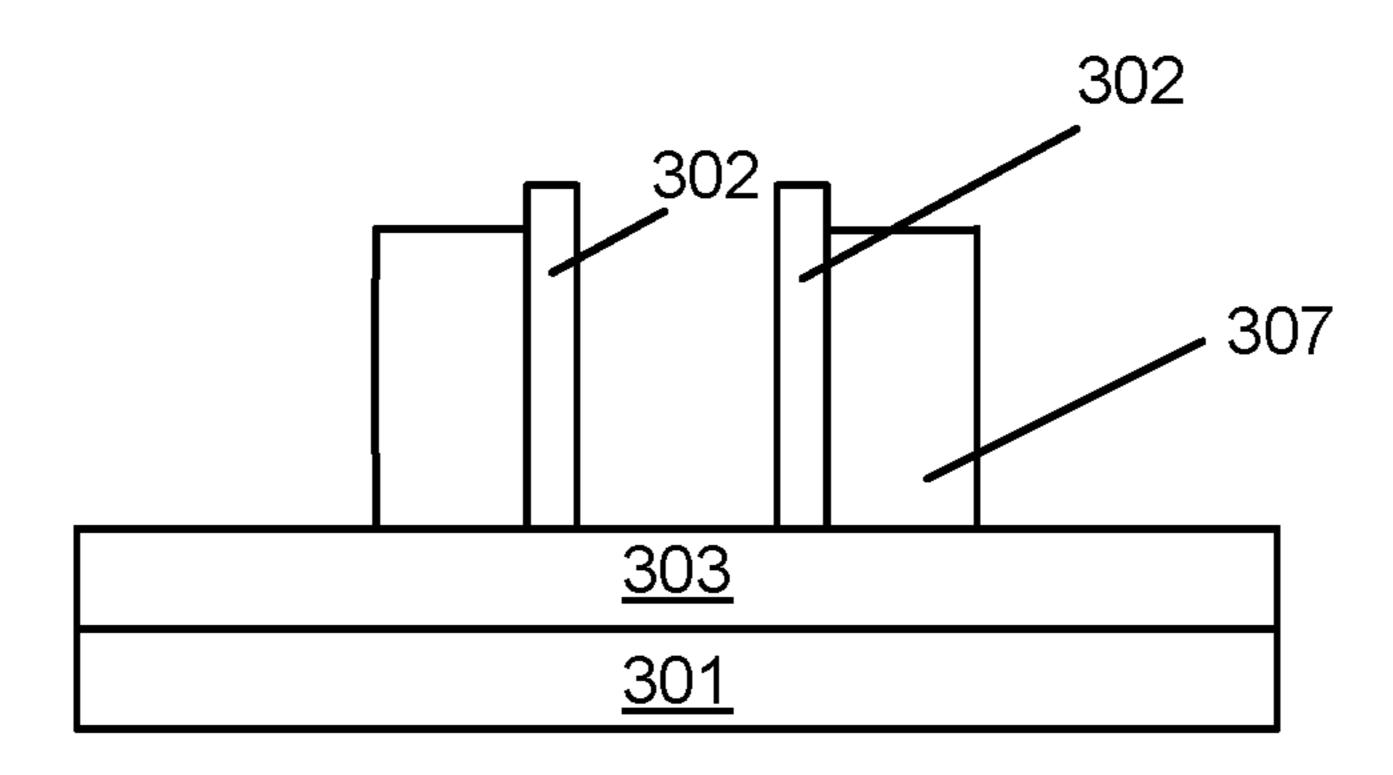

FIG. 3A

FIG. 3B

FIG. 3C

FIG. 3D

FIG. 3E

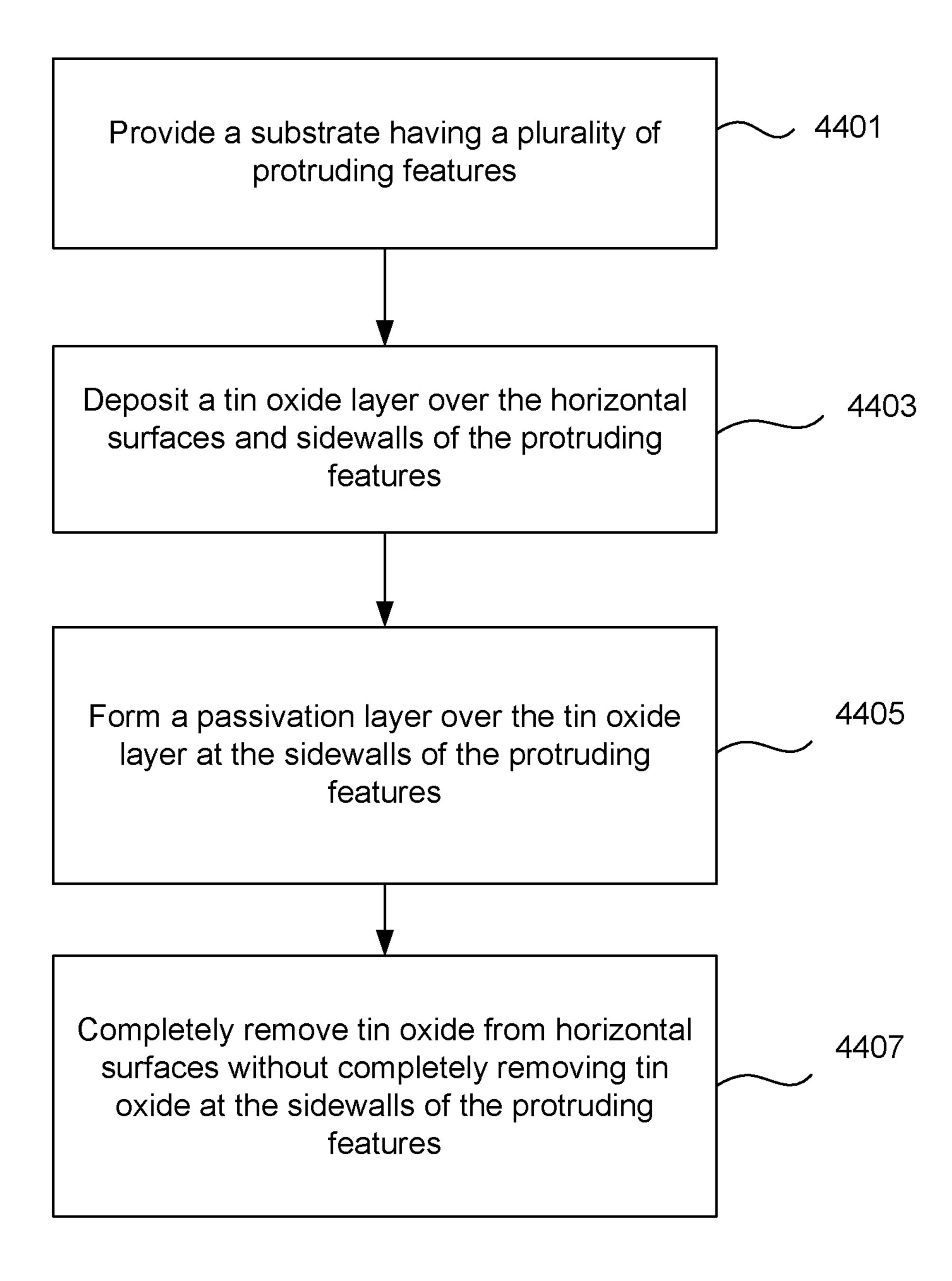

Fig. 4

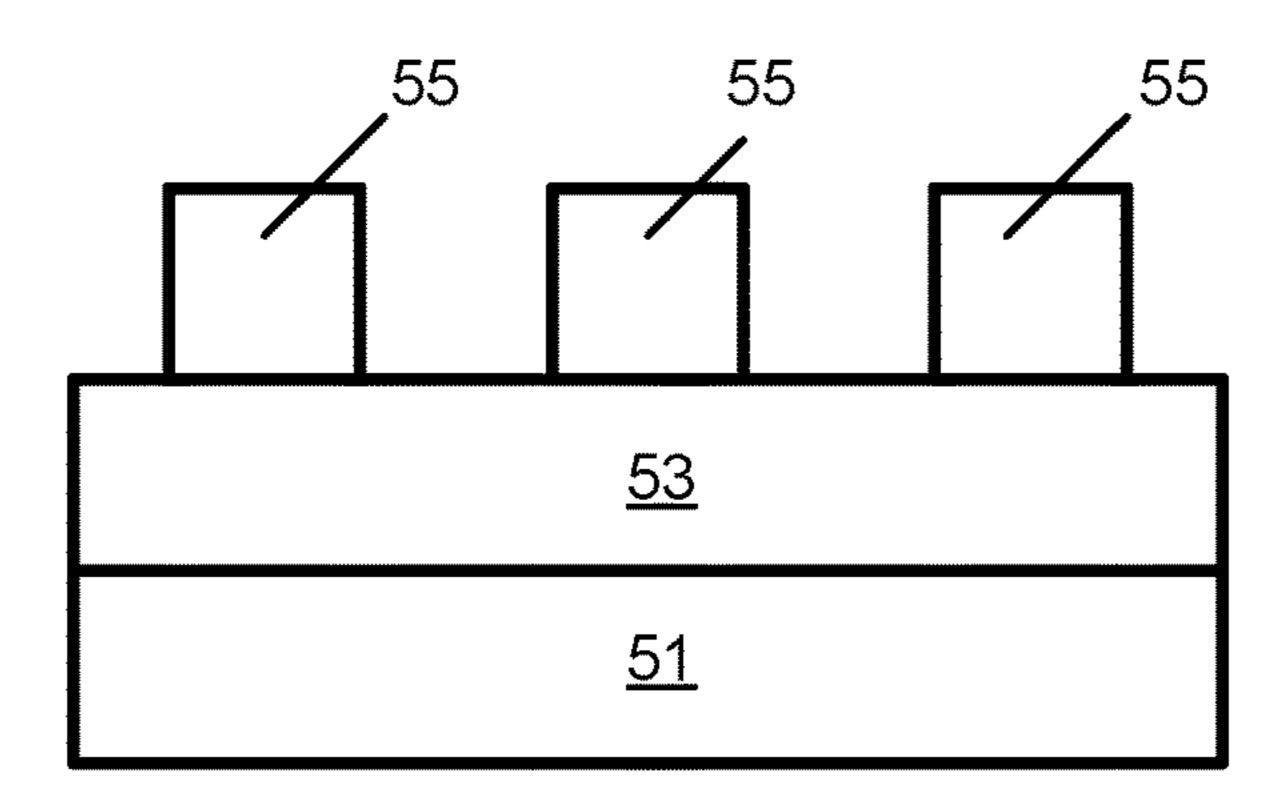

Fig. 5A

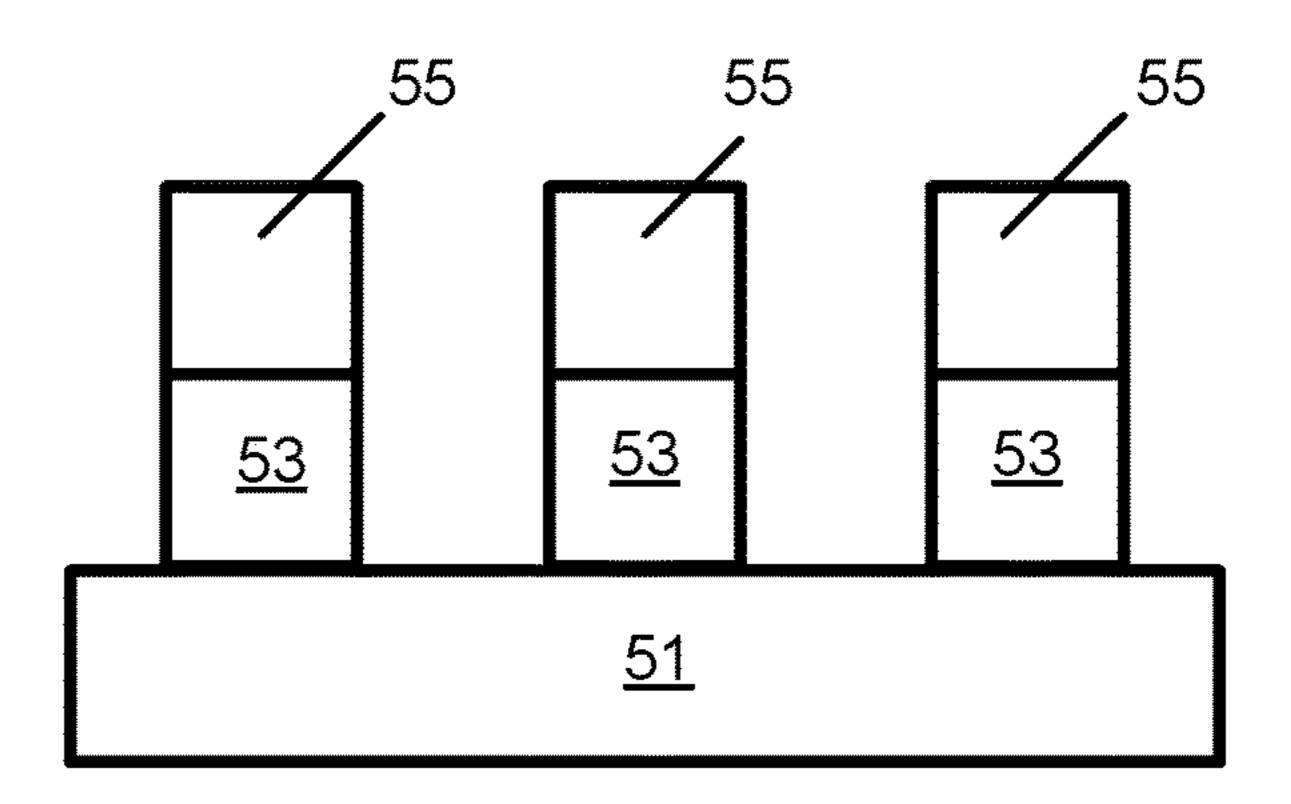

Fig. 5B

Fig. 5C

Fig. 5D

Fig. 5E

Fig. 5F

Fig. 5G

Fig. 5H

Fig. 51

Fig. 5J

Fig. 5K

Fig. 5L

Fig. 5M

Fig. 5N

Fig. 50

Fig. 6

Fig. 7A

Fig. 7B

Fig. 7C

Fig. 8

Fig. 9A

Fig. 9B

Fig. 9C

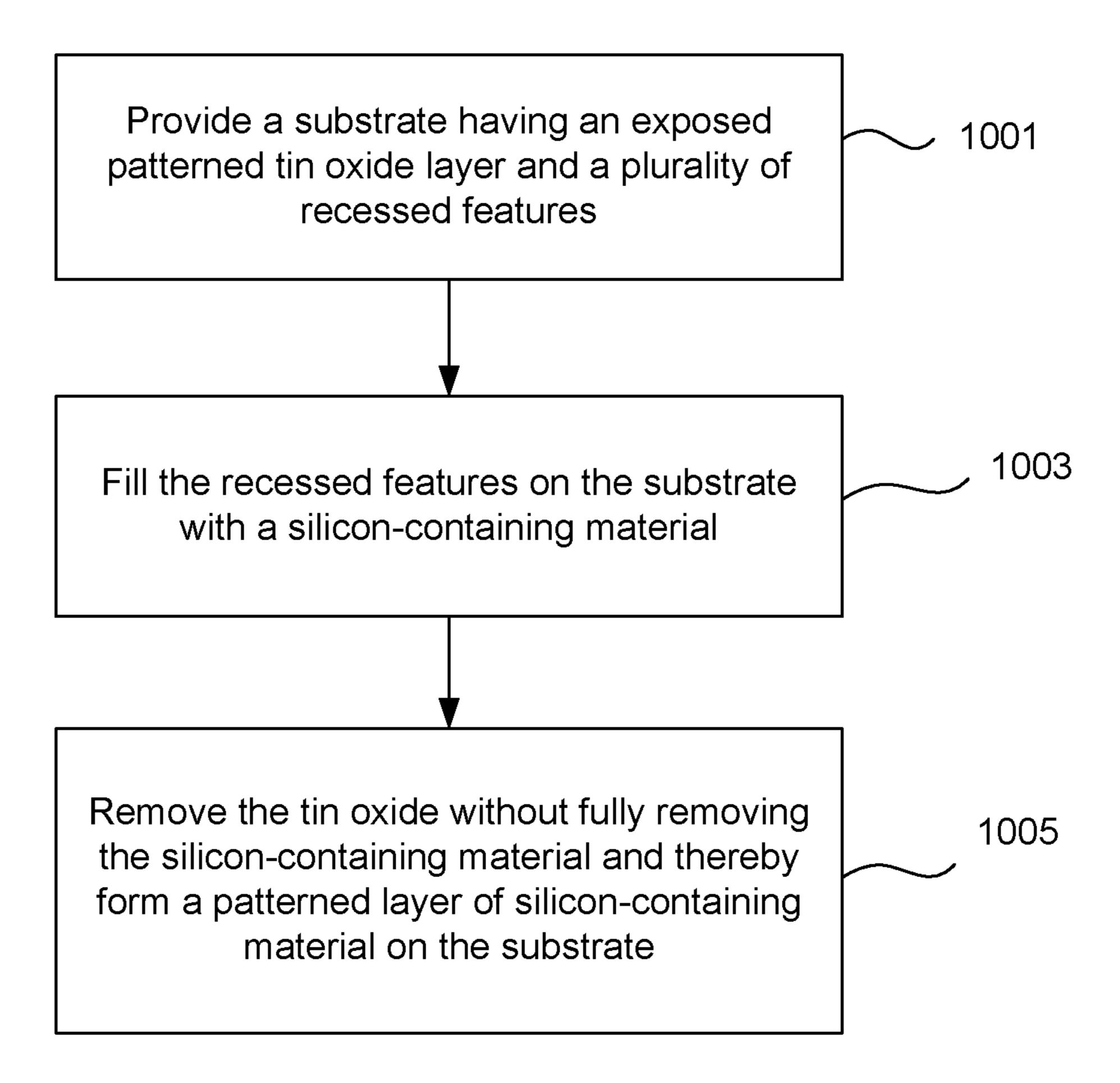

Fig. 10

FIG. 12

## TIN OXIDE FILMS IN SEMICONDUCTOR DEVICE MANUFACTURING

### CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims the benefit of U.S. Provisional Patent Application No. 62/460,573, filed on Feb. 17, 2017, titled "Tin Oxide Films in Semiconductor Device Manufacturing" naming Tan et al. as inventors, and of U.S. Provisional Patent Application No. 62/479,709, filed on Mar. 31, 2017, titled "Tin Oxide Films in Semiconductor Device Manufacturing" naming Tan et al. as inventors which are herein incorporated by reference in their entirety.

#### FIELD OF THE INVENTION

This invention pertains to methods of semiconductor device manufacturing. Specifically, embodiments of this invention pertain to methods of using tin oxide films in <sup>20</sup> semiconductor processing.

#### BACKGROUND

In integrated circuit (IC) fabrication, deposition and etching techniques are used for forming patterns of materials, such as for forming metal lines embedded in dielectric layers. Some patterning schemes involve the use of spacers that enable precise patterning and formation of small-scale features. Spacers are formed on a substrate, such that they are separated by defined distances (typically determined by previous patterning), and are used as masks for patterning of underlying layers. The materials of spacers and of surrounding layers are selected to have appropriate etch selectivity that would enable both formation of spacers, and patterning of underlying layers. After the patterning is completed, the spacers are removed by etching, and are not part of the final fabricated semiconductor device.

Spacers are used for patterning in a variety of applications, including formation of dynamic random-access 40 memory (DRAM), patterning fins in fin field effect transistors (finFETs), and in back end of line (BEOL) processing.

#### **SUMMARY**

In one aspect, a method of processing a semiconductor substrate is provided. In some embodiments the method includes: (a) providing a semiconductor substrate having a plurality of protruding features, the protruding features having horizontal surfaces and sidewalls; (b) forming a tin 50 oxide layer on the horizontal surfaces and the sidewalls of the protruding features (e.g., conformally depositing tin oxide to a thickness of between about 5-30 nm); (c) forming a passivation layer over the tin oxide layer at the sidewalls of the protruding features; and (d) after the passivation layer 55 is formed, etching and removing tin oxide from the horizontal surfaces of the protruding features and thereby exposing a material of the protruding features, without removing tin oxide residing at the sidewalls of the protruding features. In some embodiments the passivation layer has a thickness 60 of 1-5 nm. In some embodiments the material of the protruding features exposed in (d) is selected from the group consisting of a silicon-containing material (e.g., silicon oxide or another silicon-containing compound), a carboncontaining material (e.g., amorphous carbon or photoresist), 65 and a metal oxide (e.g., titanium oxide). In some embodiments, the semiconductor substrate provided in (a) includes

2

a material selected from the group consisting of silicon oxide, titanium oxide, zirconium oxide, and tungsten oxide between the protruding features.

In some embodiments, the step of etching and removing tin oxide from horizontal surfaces of the protruding features includes etching the tin oxide using a hydrogen-based etch chemistry that results in a formation of a tin hydride. For example, such etching may include contacting the semiconductor substrate with a plasma-activated hydrogen-containing reactant selected from the group consisting of H<sub>2</sub>, HBr, NH<sub>3</sub>, H<sub>2</sub>O, a hydrocarbon, and combinations thereof.

In some embodiments, the step of etching and removing tin oxide from horizontal surfaces of the protruding features includes using a chlorine-based etch chemistry that comprises exposing the semiconductor substrate to a plasma-activated chlorine-containing reactant selected from the group consisting of  $Cl_2$ ,  $BCl_3$ , and combinations thereof In some embodiments, the step of etching and removing tin oxide from horizontal surfaces of the protruding features includes etching tin oxide using a chlorine-based etch chemistry followed by etching the tin oxide using a hydrogen-based etch chemistry. For example this step may include etching the tin oxide layer using a plasma formed in a gas comprising  $Cl_2$  and  $BCl_3$ , followed by etching the tin oxide layer with a plasma formed in an  $H_2$ -containing gas.

In one implementation, the material of the protruding features exposed in during the tin oxide etch is selected from the group consisting of SiO<sub>2</sub>, SiN, SiOC, SiC, SiCN, SiCNO, and SiOC, and the tin oxide etching includes using a hydrogen-based etch chemistry that results in a formation of a tin hydride. In one embodiment, the protruding features silicon protruding features covered with silicon oxide and removing the tin oxide layer from the horizontal surfaces of the protrusions includes etching tin oxide using a hydrogen-based etch chemistry that results in a formation of a tin hydride, and exposing the underlying silicon oxide material.

In another embodiment the protruding features are carbon protruding features or photoresist protruding features. In another embodiment the protruding features are metal oxide protruding features selected from the group consisting of tantalum oxide (TaO), titanium oxide (TiO), tungsten oxide (WO), zirconium oxide (ZrO), and hafnium oxide (HfO).

In some embodiments forming the passivation layer over the tin oxide layer at the sidewalls of the protruding features 45 includes depositing a passivation material over both the horizontal surfaces and the sidewalls of the protruding features, followed by removal of the passivation material from the horizontal surfaces of the protruding features. In one implementation, forming the passivation layer over the tin oxide layer at the sidewalls of the protruding features includes depositing a silicon-containing passivation material over both the horizontal surfaces and the sidewalls of the protruding features, followed by removal of the siliconcontaining passivation material from the horizontal surfaces of the protruding features using a fluorocarbon-based etch chemistry. In another implementation, forming the passivation layer over the tin oxide layer at the sidewalls of the protruding features includes depositing a carbon-containing passivation material over both the horizontal surfaces and the sidewalls of the protruding features, followed by removal of the carbon-containing passivation material from the horizontal surfaces.

In some embodiments forming the passivation layer over the tin oxide layer at the sidewalls of the protruding features includes converting an outer portion of the tin oxide layer to a tin-containing passivation material selected from the group consisting of tin nitride (SnN), tin bromide (SnBr), and tin

fluoride (SnF). In one example forming the passivation layer over the tin oxide layer at the sidewalls of the protruding features includes converting an outer portion of the tin oxide layer to tin nitride by contacting the substrate with a nitrogen-containing reactant in a plasma.

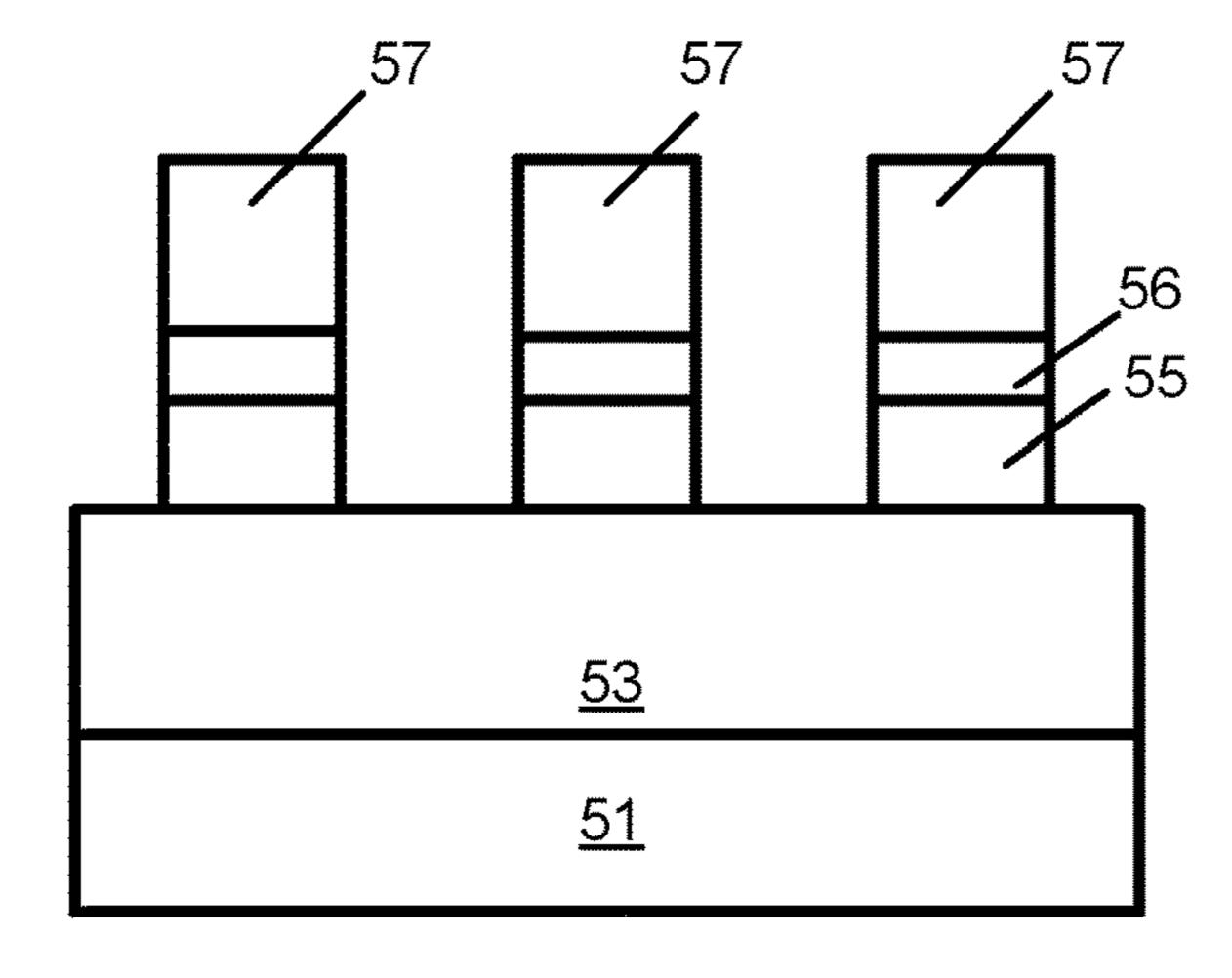

After the tin oxide layer is removed from the horizontal surfaces, the process may follow by removing the protruding features without completely removing the tin oxide layer that resided at the sidewalls of the protruding features, thereby forming tin oxide spacers.

The method may also include: applying photoresist to the substrate; exposing the photoresist to light; patterning the photoresist and transferring the pattern to the substrate; and selectively removing the photoresist from the substrate.

substrate is provided, wherein the semiconductor substrate includes a plurality of spacers, wherein each spacer includes a layer of tin oxide and a layer of a passivation material.

In another aspect, a system for processing a semiconductor substrate is provided. In one embodiment the system 20 includes: one or more deposition chambers; one or more etch chambers; and a system controller comprising program instructions for: (i) causing a deposition of a tin oxide layer over horizontal surfaces and sidewalls of a plurality of protruding features on the semiconductor substrate; (ii) 25 causing a formation of a passivation layer on the tin oxide layer at the sidewalls of the protruding features, and (ii) causing a removal of the tin oxide layer from horizontal surfaces of the protruding features, without causing a removal of the tin oxide layer over the sidewalls of the 30 protruding features.

In another aspect methods for processing a semiconductor substrate using tin oxide hardmasks are provided. In one embodiment a method for processing a semiconductor substrate includes: forming a patterned tin oxide hardmask layer 35 on the semiconductor substrate by forming a patterned layer over an unpatterned tin oxide hardmask layer and transferring the pattern to the tin oxide hardmask layer; and processing the semiconductor substrate in a presence of the tin oxide hardmask layer.

In one implementation processing the semiconductor substrate includes etching an exposed material that is not covered by the patterned tin oxide hardmask. In one embodiment, the exposed material that is not covered by the patterned tin oxide hardmask is a silicon-containing material 45 and the etching includes exposing the substrate to a fluorinebased etch chemistry (e.g., fluorocarbon-based etch chemistry). In another embodiment, the exposed material that is not covered by the patterned tin oxide hardmask is a carbon-containing material and the etching includes expos- 50 ing the substrate to an oxygen-based etch chemistry.

In another aspect, a method for processing a semiconductor substrate, is provided, where the method includes: (a) providing a semiconductor substrate having an exposed patterned ashable layer, wherein the patterned ashable layer comprises a plurality of recessed features with an exposed target material located at the bottom of each recessed feature; (b) filling the recessed features with tin oxide and forming a tin oxide overburden over the ashable layer; (c) removing the tin oxide overburden to expose the underlying 60 ashable material; and (d) removing the ashable material to expose an underlying target layer without fully removing tin oxide. In one embodiment the ashable material is a carboncontaining material (e.g., carbon), and (d) includes removing the ashable material using an oxygen-based etch chemistry. 65

In another aspect, a method for processing a semiconductor substrate is provided, where the method includes: (a)

providing a semiconductor substrate having a patterned tin oxide layer, wherein the patterned tin oxide layer comprises a plurality of recessed features; (b) filling the recessed features with a silicon-containing material, wherein the silicon-containing material is silicon or silicon-containing compound, and forming an overburden of the silicon-containing material over the tin oxide layer; (c) removing the overburden to expose the underlying tin oxide; and (d) removing the tin oxide without fully removing the silicon-10 containing material. In one implementation removing the tin oxide without fully removing the silicon-containing material includes etching tin oxide using a hydrogen-based etch chemistry (e.g. plasma formed in  $H_2$ ).

In another aspect, a method of processing a semiconduc-In another aspect a partially fabricated semiconductor 15 tor substrate includes: (a) providing a semiconductor substrate having a plurality of protruding features; (b) depositing a tin oxide layer over horizontal surfaces and sidewalls of the protruding features; and (c) etching and removing tin oxide from the horizontal surfaces of the protruding features, without completely removing tin oxide residing at the sidewalls of the protruding features, wherein the etching includes exposing the semiconductor substrate to a hydrogen-based etch chemistry to convert tin oxide to a tin hydride.

> In another aspect a method of processing a semiconductor substrate includes: (a) providing a semiconductor substrate having a plurality of protruding features; (b) depositing a tin oxide layer over horizontal surfaces and sidewalls of the protruding features; and (c) etching and completely removing tin oxide from the horizontal surfaces of the protruding features, without completely removing tin oxide residing at the sidewalls of the protruding features, wherein the etching comprises exposing the semiconductor substrate to a chlorine-based etch chemistry to convert tin oxide to a tin chloride.

In another aspect a method of processing a semiconductor substrate includes: (a) providing a substrate having a tin oxide layer, an exposed layer of patterned photoresist over the tin oxide layer, and a layer of an underlying material 40 below the tin oxide layer, wherein the tin oxide is exposed at locations that are not covered by the patterned photoresist; and (b) selectively etching the tin oxide in a presence of photoresist, and exposing the underlying material, wherein the etching is selective to both photoresist and the underlying material. In some embodiments, selectively etching the tin oxide includes exposing the substrate to a hydrogenbased plasma etch chemistry with a carbon-containing additive resulting in a formation of a carbon-containing polymer on the semiconductor substrate during the etch. In one implementation selectively etching the tin oxide comprises exposing the semiconductor substrate to a plasma formed in a process gas comprising H<sub>2</sub> and a hydrocarbon. In some embodiments, this tin oxide etch chemistry provides an etch selectivity of at least 100 to photoresist, and of at least 10 to the underlying material. In some embodiments the underlying material is selected from the group consisting of silicon (Si), a silicon-containing compound, and a carbon-containing material. In one implementation the underlying material is amorphous silicon, and the method further includes selectively etching amorphous silicon exposed in (b) in a presence of tin oxide. In another implementation the underlying material comprises tungsten (W) and carbon (C), and the method further includes selectively etching the underlying material exposed in (b) in a presence of tin oxide. In some embodiments, after selective etching of tin oxide the method further includes: (c) selectively etching the exposed underlying material in a presence of tin oxide; and (d) removing

the tin oxide from the semiconductor substrate by exposing the semiconductor substrate to a plasma formed in a process gas consisting essentially of H<sub>2</sub>.

In other aspects, selective etching methods are provided. In one aspect a method of processing a semiconductor substrate includes: (a) providing a semiconductor substrate having an exposed layer of tin oxide; (b) selectively etching the tin oxide in a presence of a material selected from the group consisting of photoresist, silicon (Si), carbon, and a carbon-containing material, by exposing the semiconductor substrate to a plasma formed in a process gas comprising H<sub>2</sub> and a hydrocarbon.

In another aspect, a method of processing a semiconductor substrate includes: (a) providing a semiconductor substrate having an exposed layer of tin oxide; (b) selectively etching the tin oxide in a presence of a material selected from the group consisting of silicon (Si), carbon, a carbon-containing material, metal, metal oxide and a metal nitride, using a hydrogen-based etch.

In another aspect, a method of processing a semiconductor substrate includes: (a) providing a semiconductor substrate having an exposed layer of tin oxide; and (b) selectively etching the tin oxide in a presence of a material selected from the group consisting of silicon (Si), a siliconcontaining compound, photoresist, carbon (C), a carbon-containing material, metal, metal oxide and a metal nitride, by exposing the semiconductor substrate to a plasma formed in a process gas comprising a hydrogen-containing reactant selected from the coup consisting of HBr, a hydrocarbon, 30 NH<sub>3</sub>, and H<sub>2</sub>O, to form a tin hydride during the etching.

In another aspect, a method of processing a semiconductor substrate includes: (a) providing a semiconductor substrate having an exposed layer of a material selected from the group consisting of titanium oxide, and a tungstencontaining material; and (b) selectively etching the tin oxide in a presence of the material selected from the group consisting of titanium oxide and the tungsten-containing material.

In another aspect an apparatus is provided, where the 40 apparatus includes a process chamber and a controller having program instructions for causing any of the methods provided herein.

In another aspect, a semiconductor device is provided, wherein the semiconductor device includes a tin oxide layer 45 and a plurality of other materials in any configuration described herein.

These and other aspects of implementations of the subject matter described in this specification are set forth in the accompanying drawings and the description below.

#### BRIEF DESCRIPTION OF THE DRAWINGS

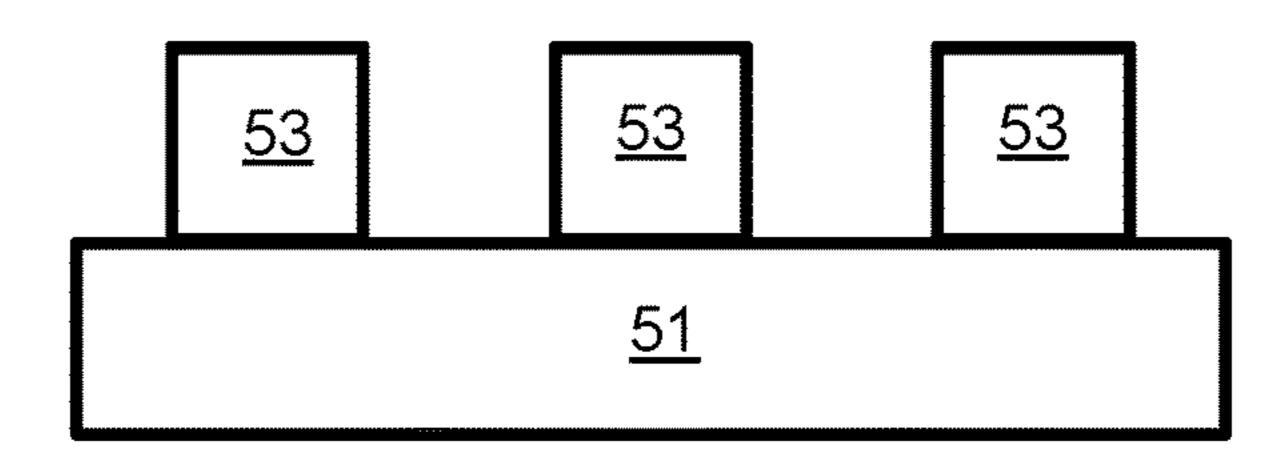

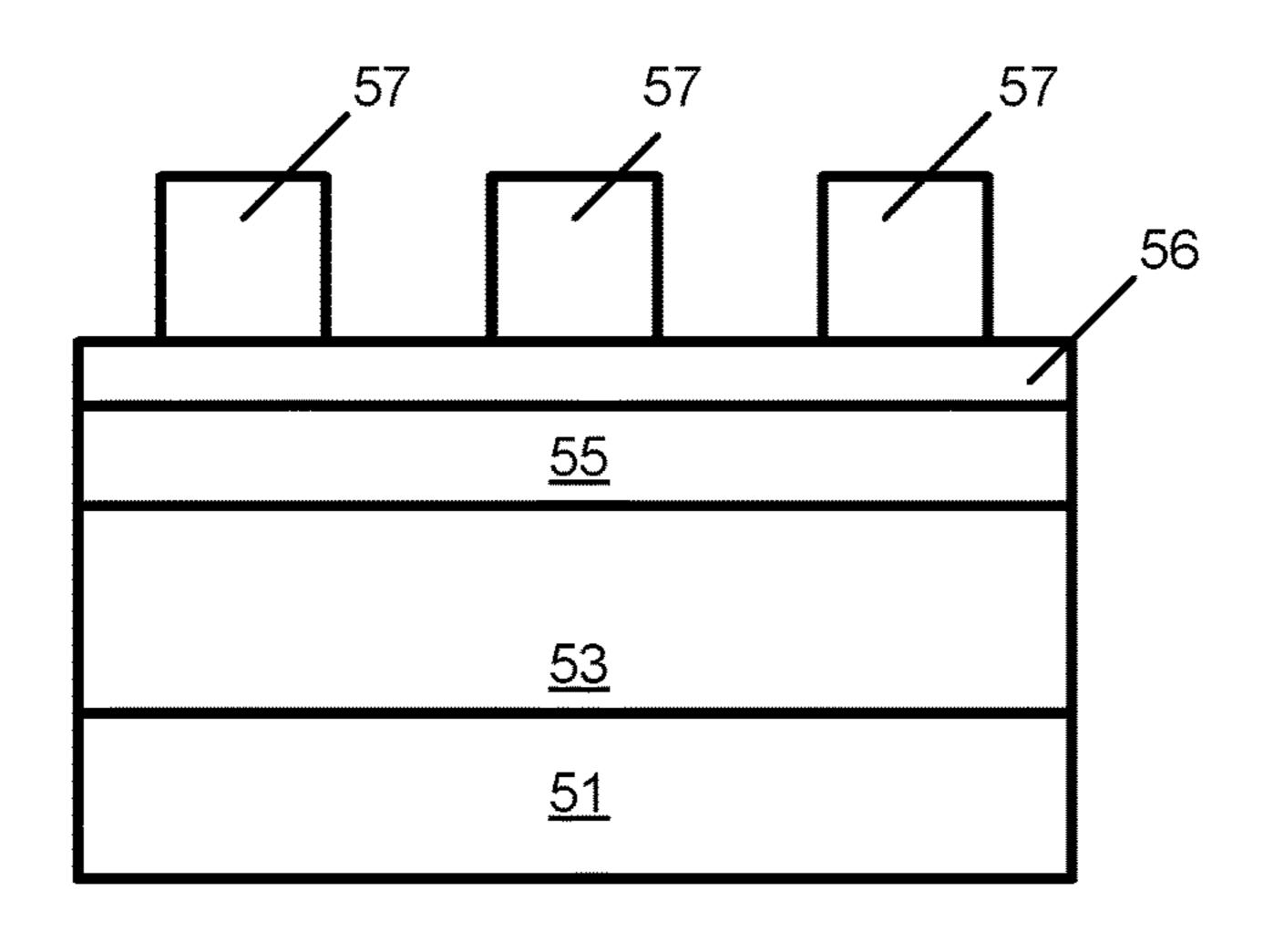

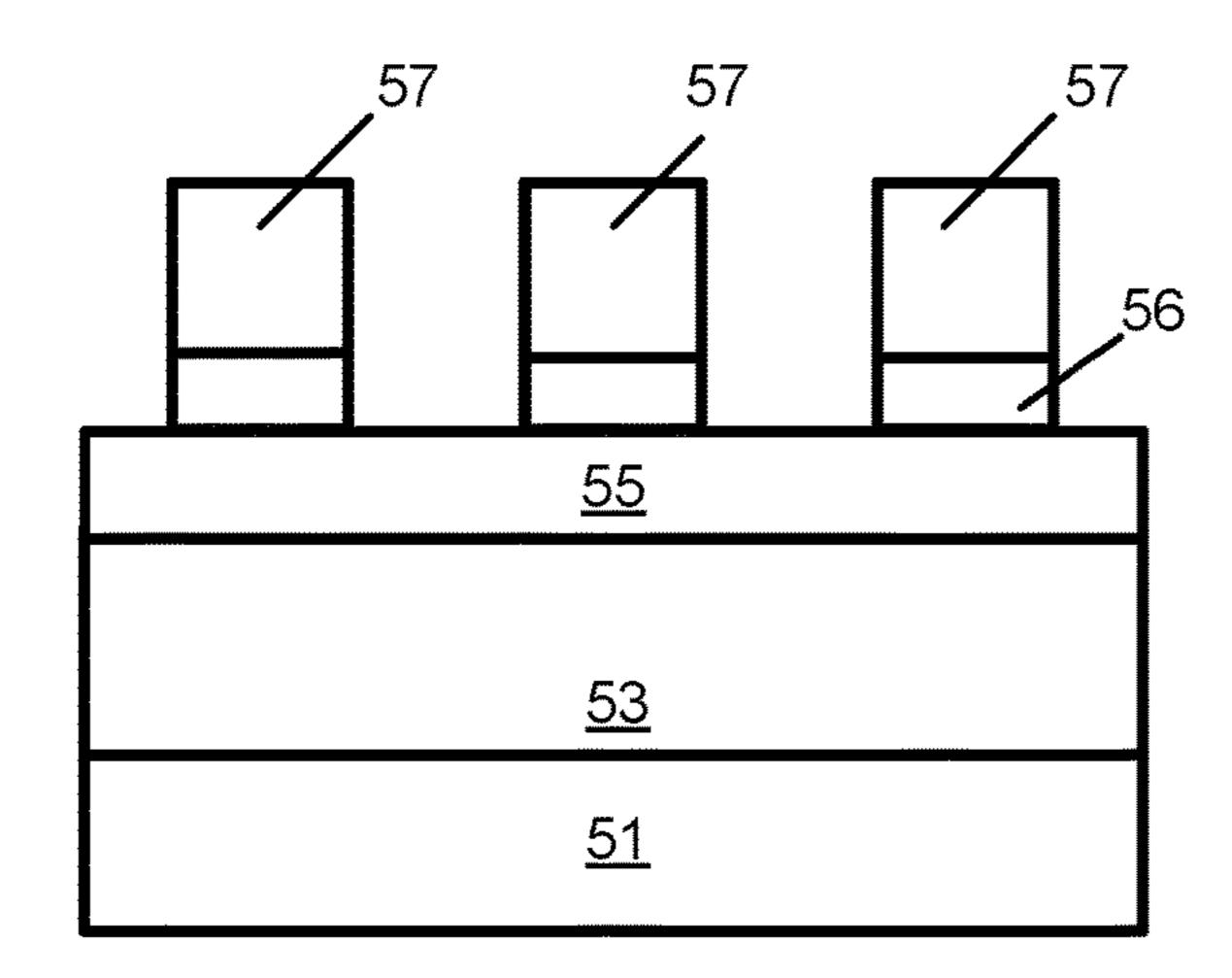

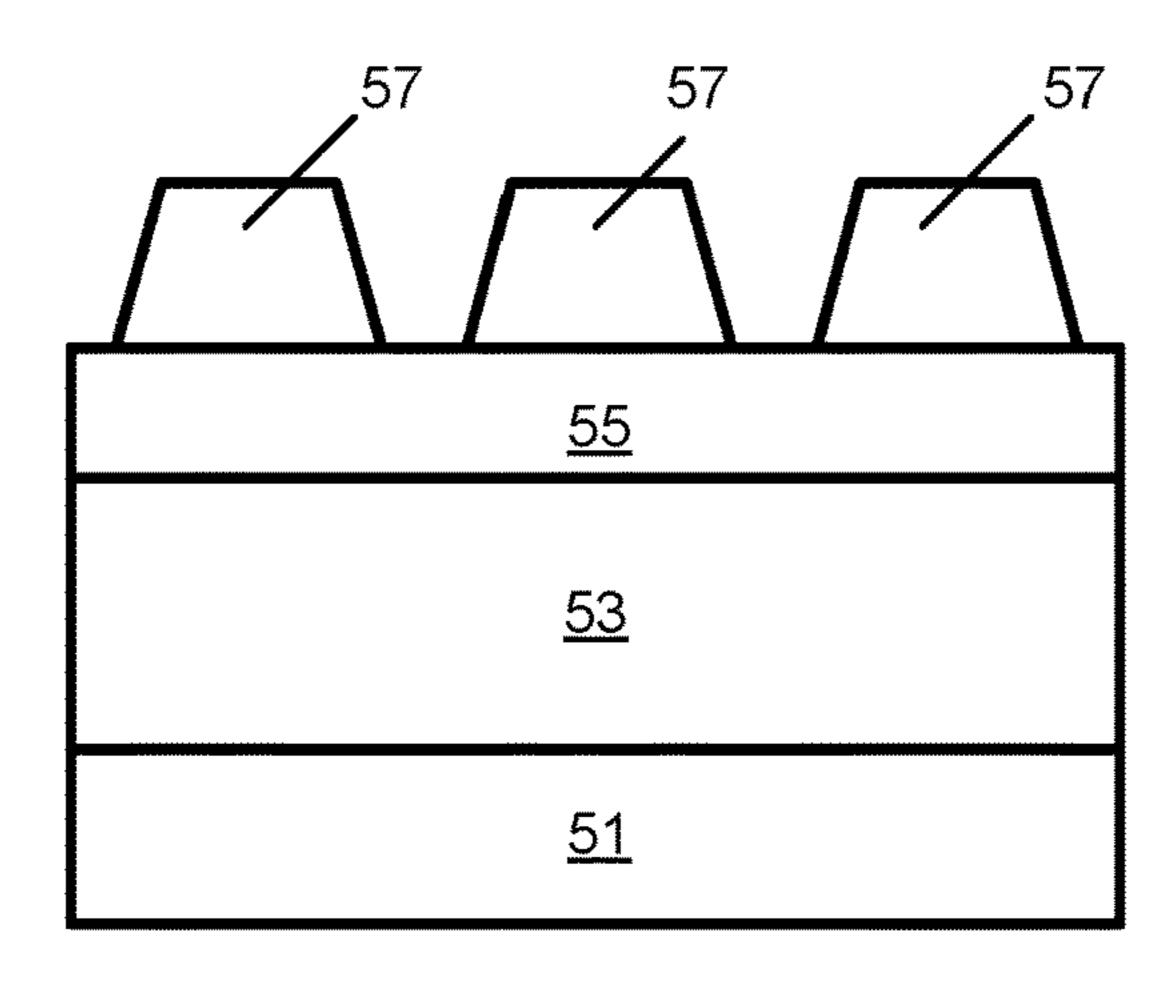

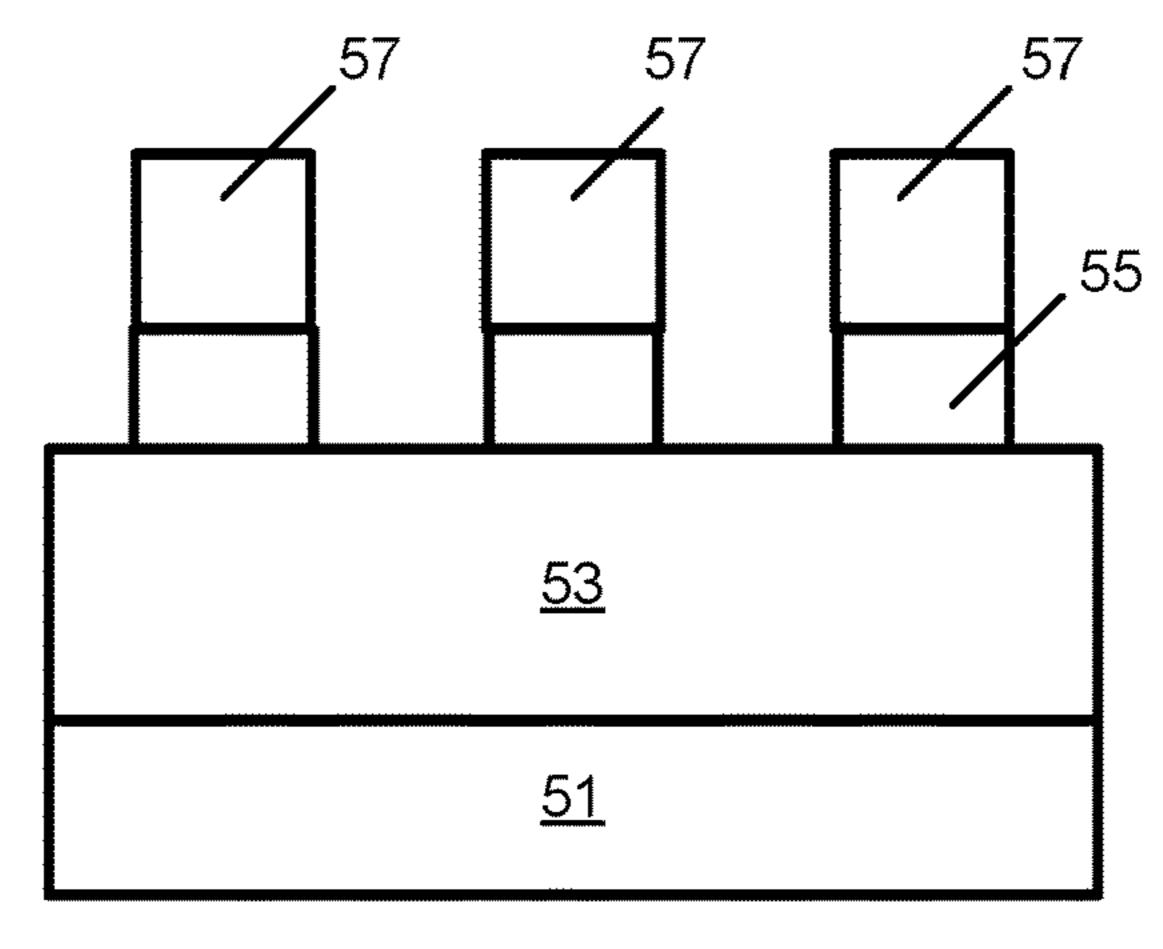

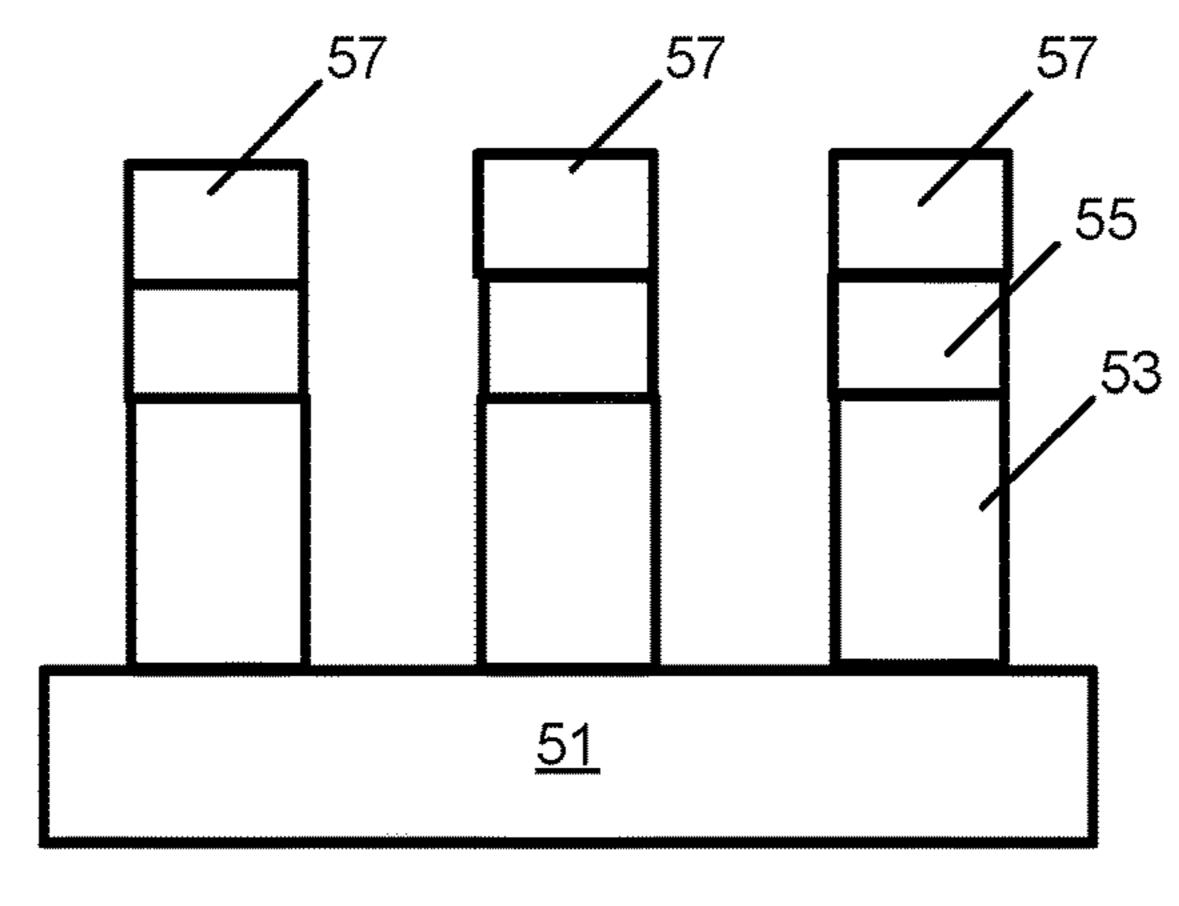

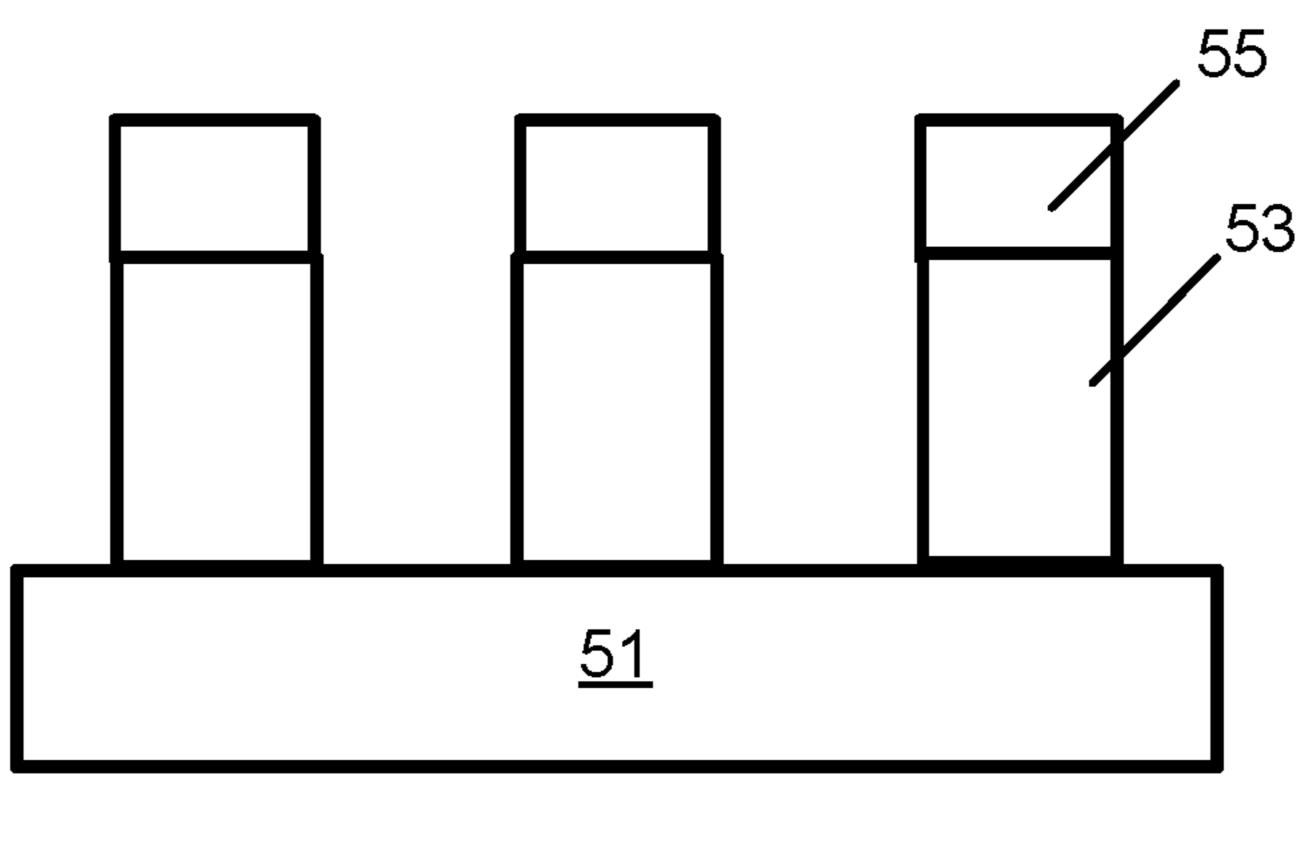

FIGS. 1A-1F show schematic cross-sectional views of a semiconductor substrate undergoing processing that 55 (e.g., a middle layer positioned below photoresist and above a target layer). For example, tin oxide can be a spacer in

FIG. 2 is a process flow diagram for a method according to an embodiment provided herein.

FIGS. 3A-3E show schematic cross-sectional views of a semiconductor substrate undergoing processing according to 60 an embodiment provided herein.

FIG. 4 is a process flow diagram for a method of forming tin oxide spacers according to an embodiment provided herein.

FIGS. **5**A-**5**C show schematic cross-sectional views of a 65 semiconductor substrate undergoing processing according to an embodiment provided herein.

6

FIGS. **5**D**-5**G show schematic cross-sectional views of a semiconductor substrate undergoing processing according to another embodiment provided herein.

FIGS. 5H-5K show schematic cross-sectional views of a semiconductor substrate undergoing processing according to another embodiment provided herein.

FIGS. **5**L-**5**O show schematic cross-sectional views of a semiconductor substrate undergoing processing according to another embodiment provided herein.

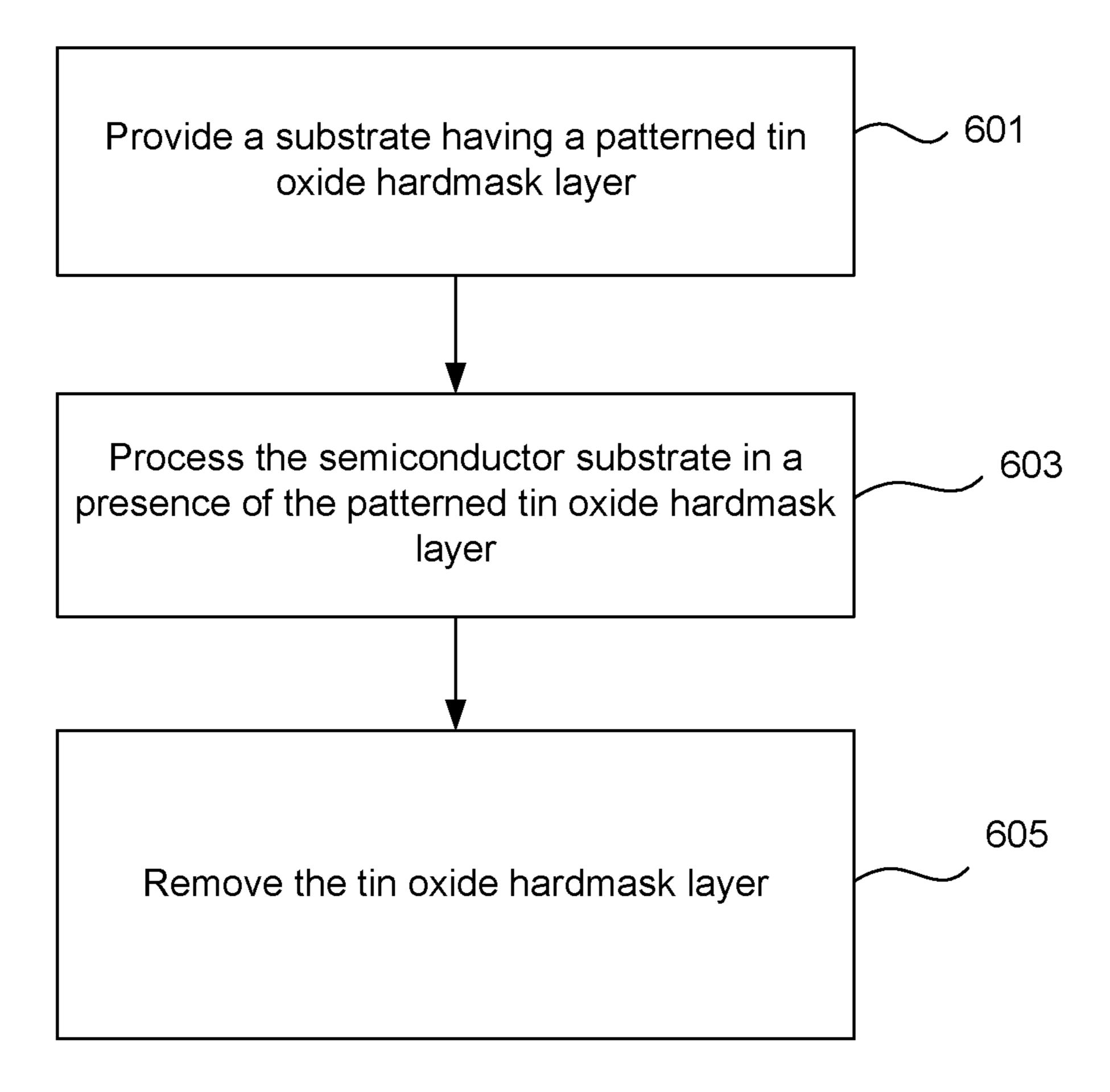

FIG. 6 is a process flow diagram for a method of semiconductor according to an embodiment provided herein.

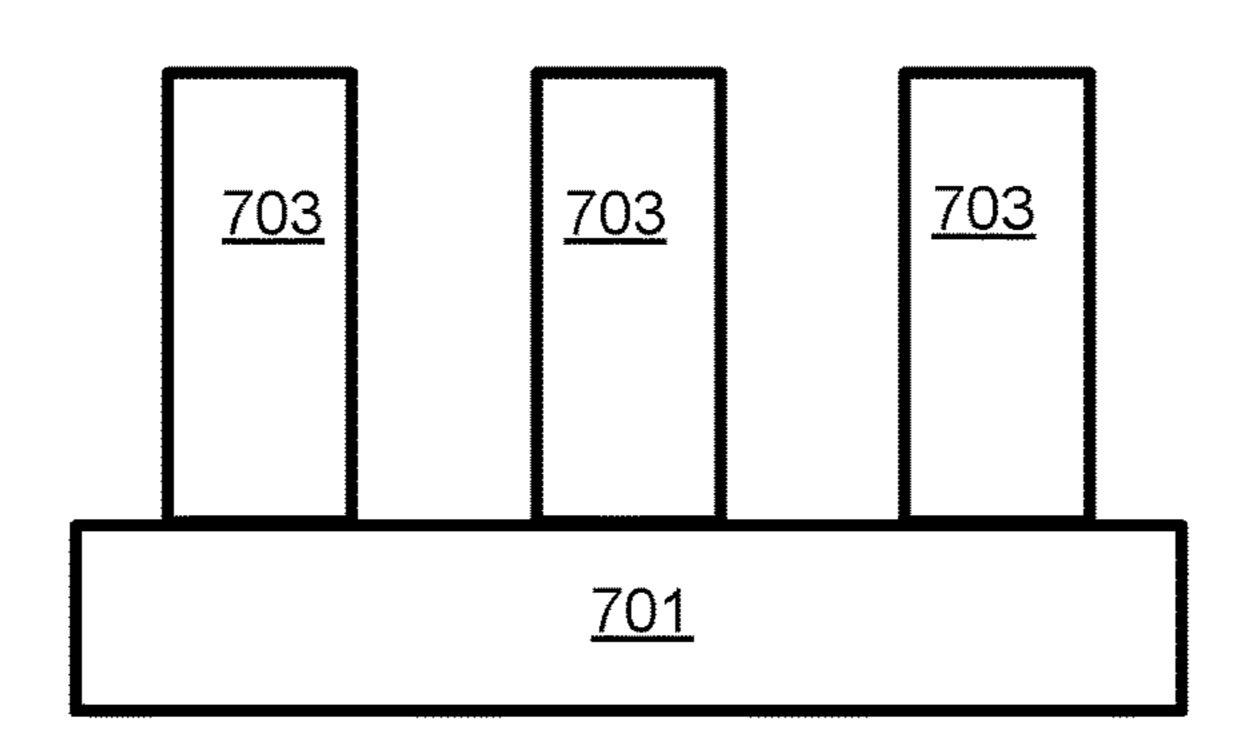

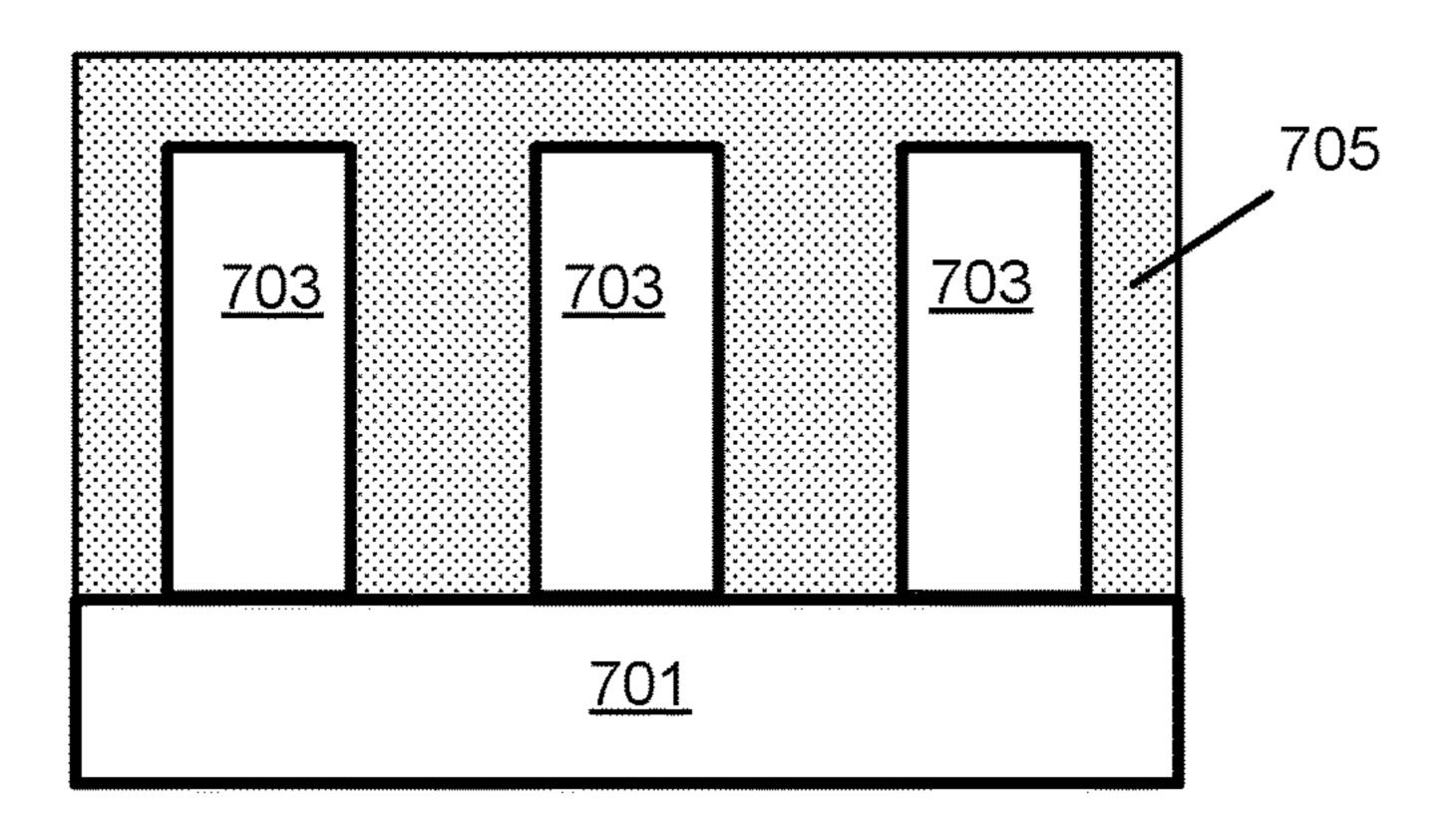

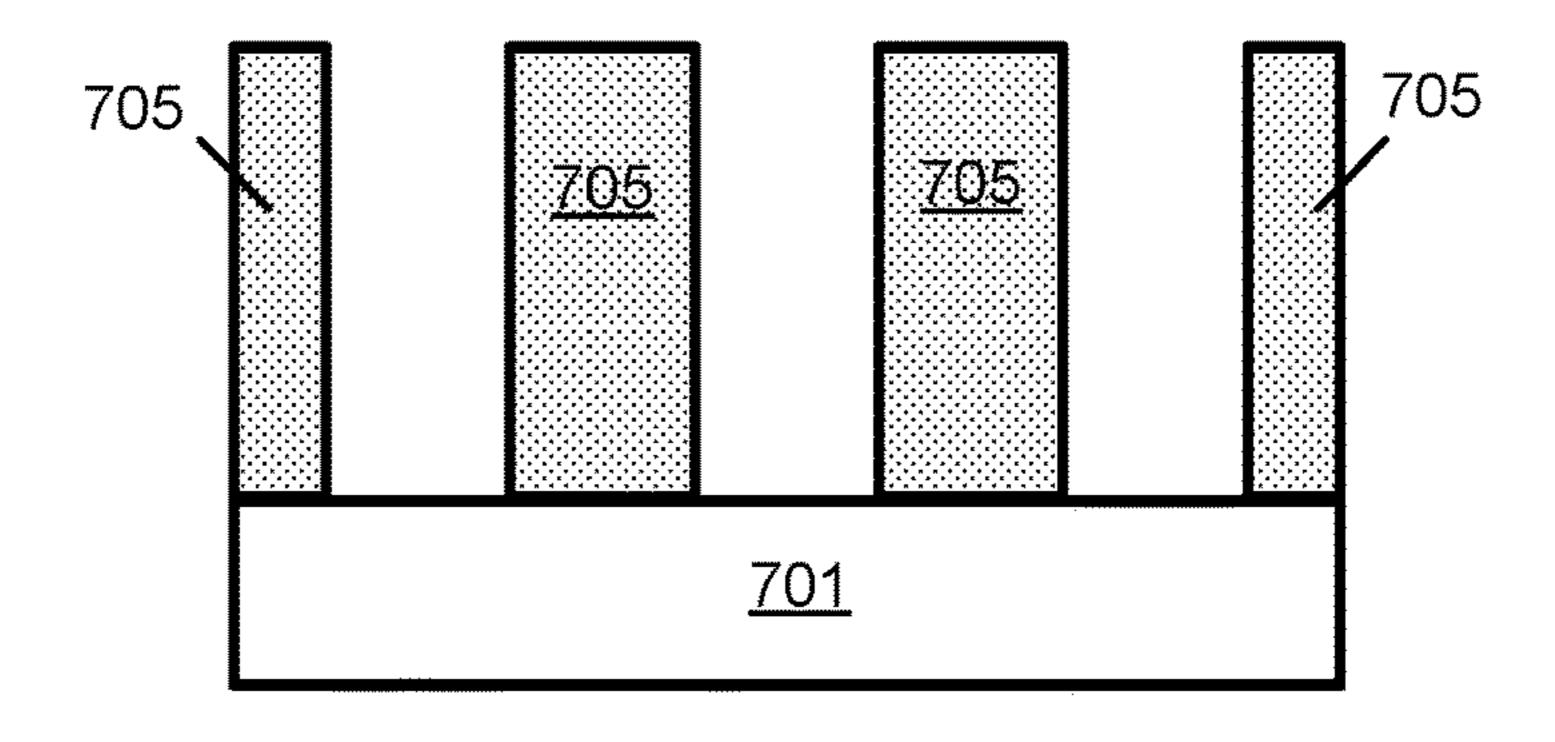

FIGS. 7A-7C show schematic cross-sectional views of a semiconductor substrate undergoing processing according to an embodiment provided herein.

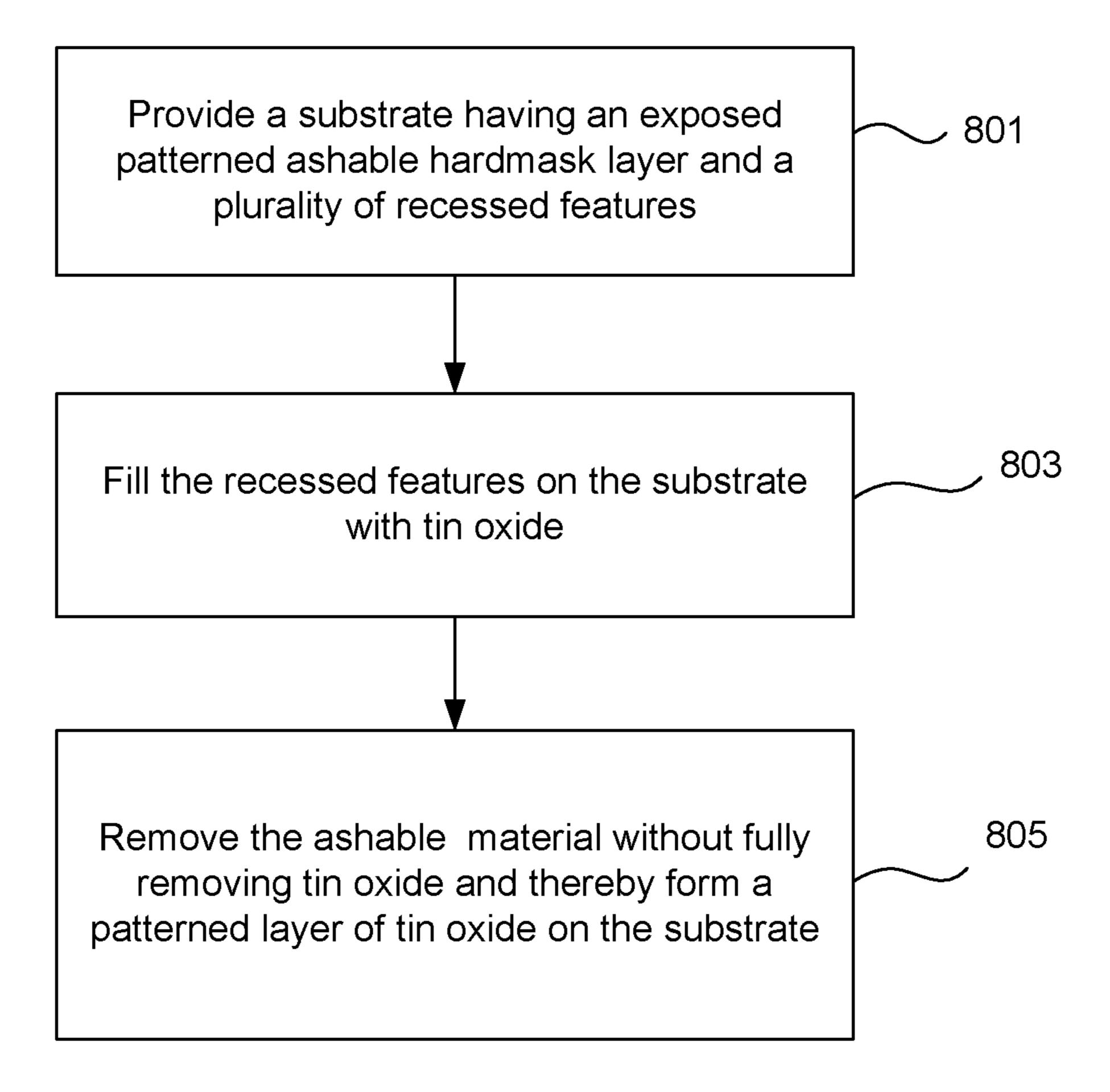

FIG. 8 is a process flow diagram for a method according to an embodiment provided herein.

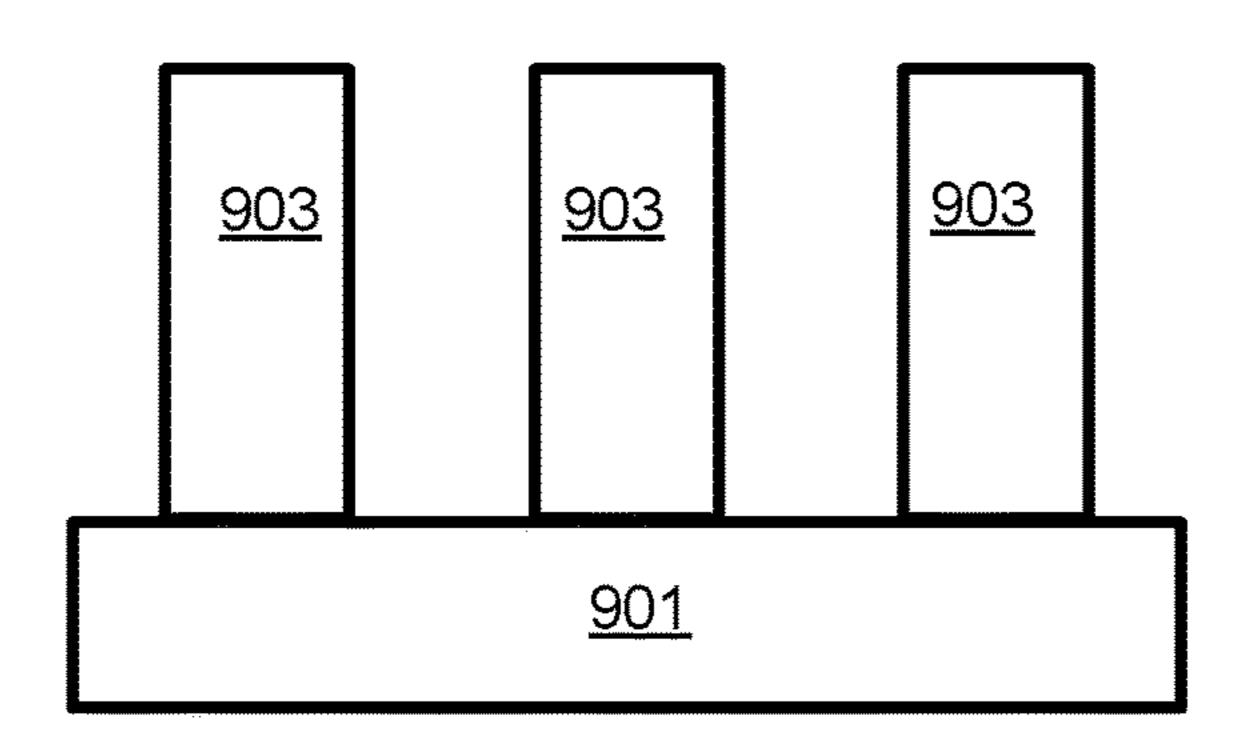

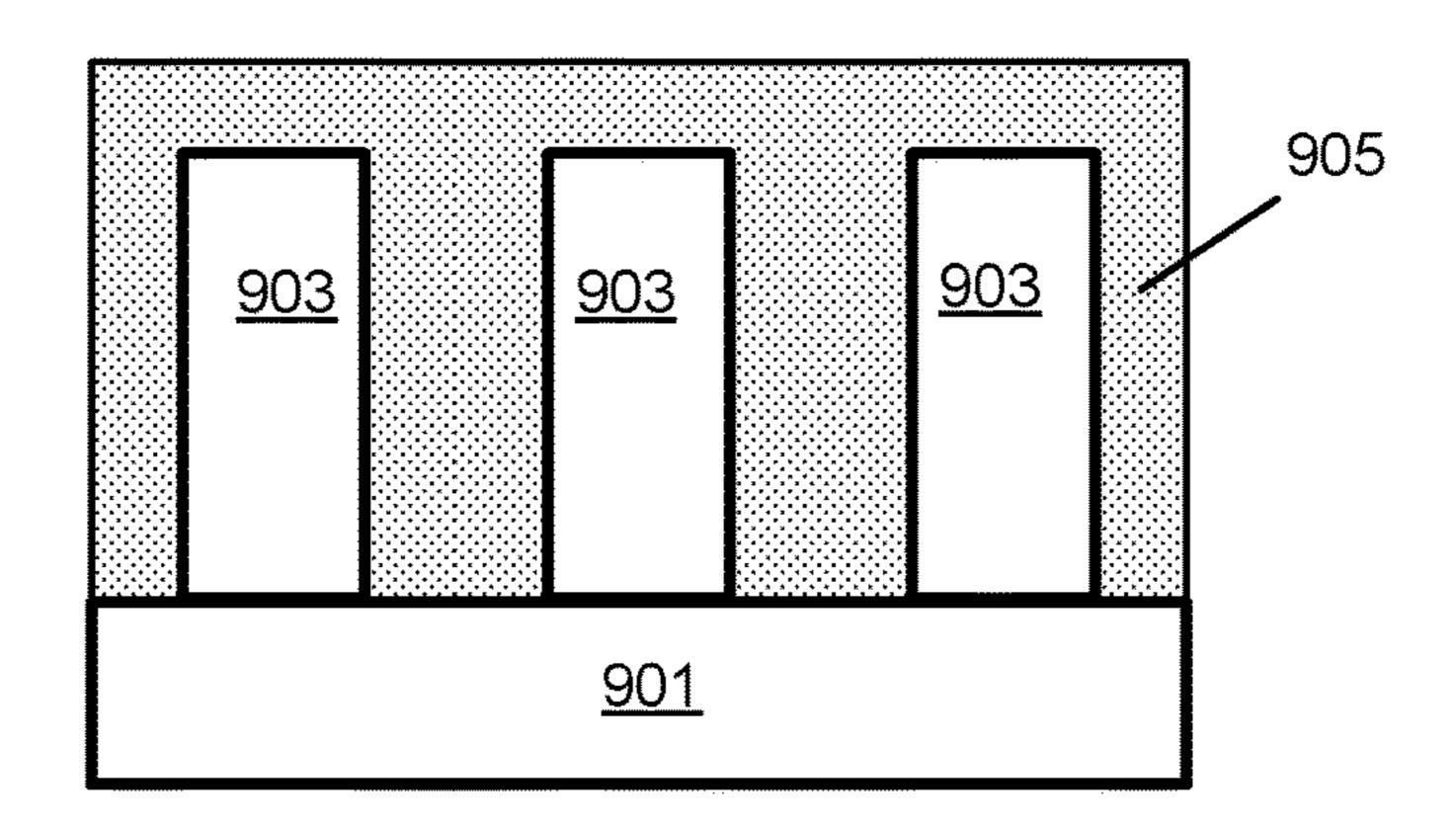

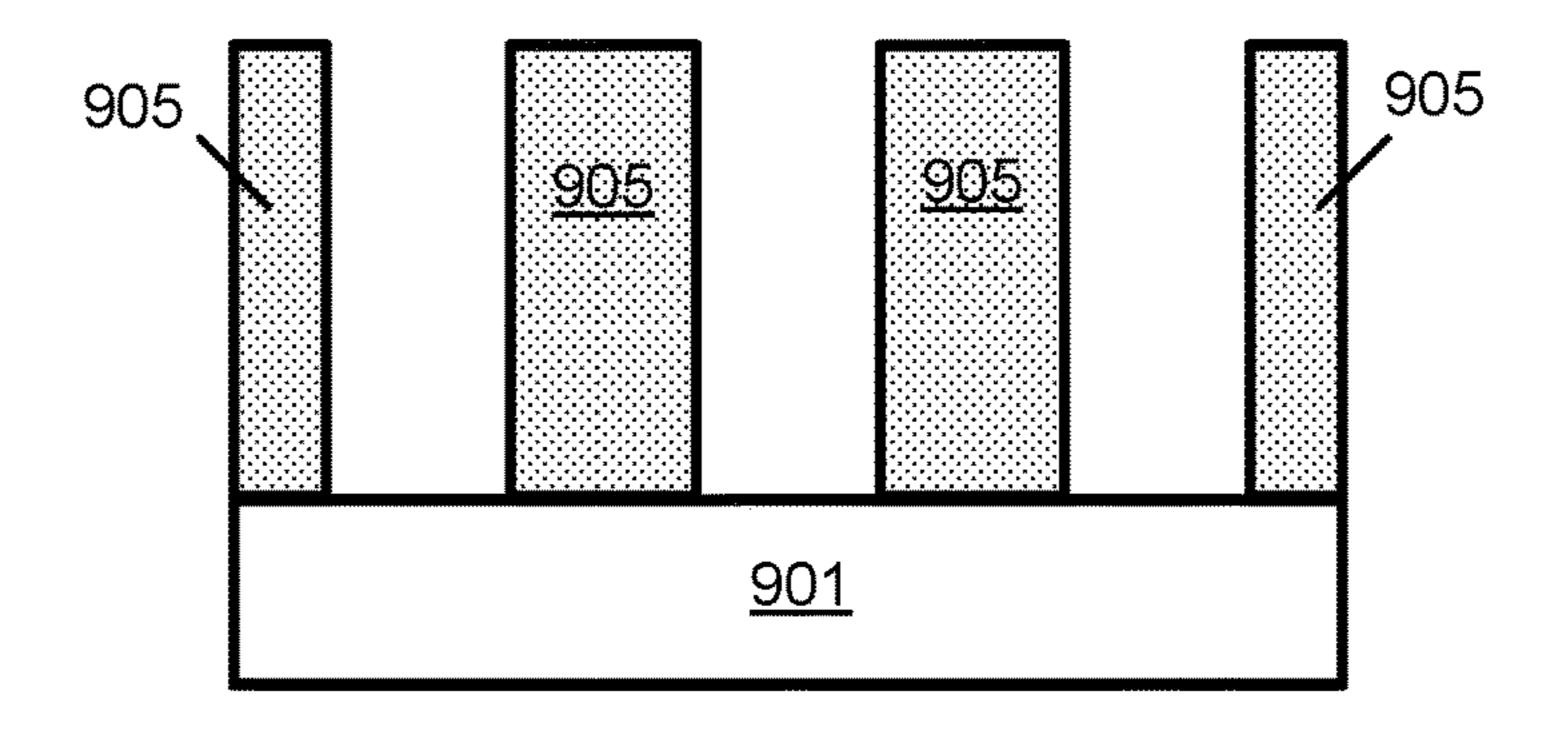

FIGS. 9A-9C show schematic cross-sectional views of a semiconductor substrate undergoing processing according to an embodiment provided herein.

FIG. 10 is a process flow diagram for a method according to an embodiment provided herein.

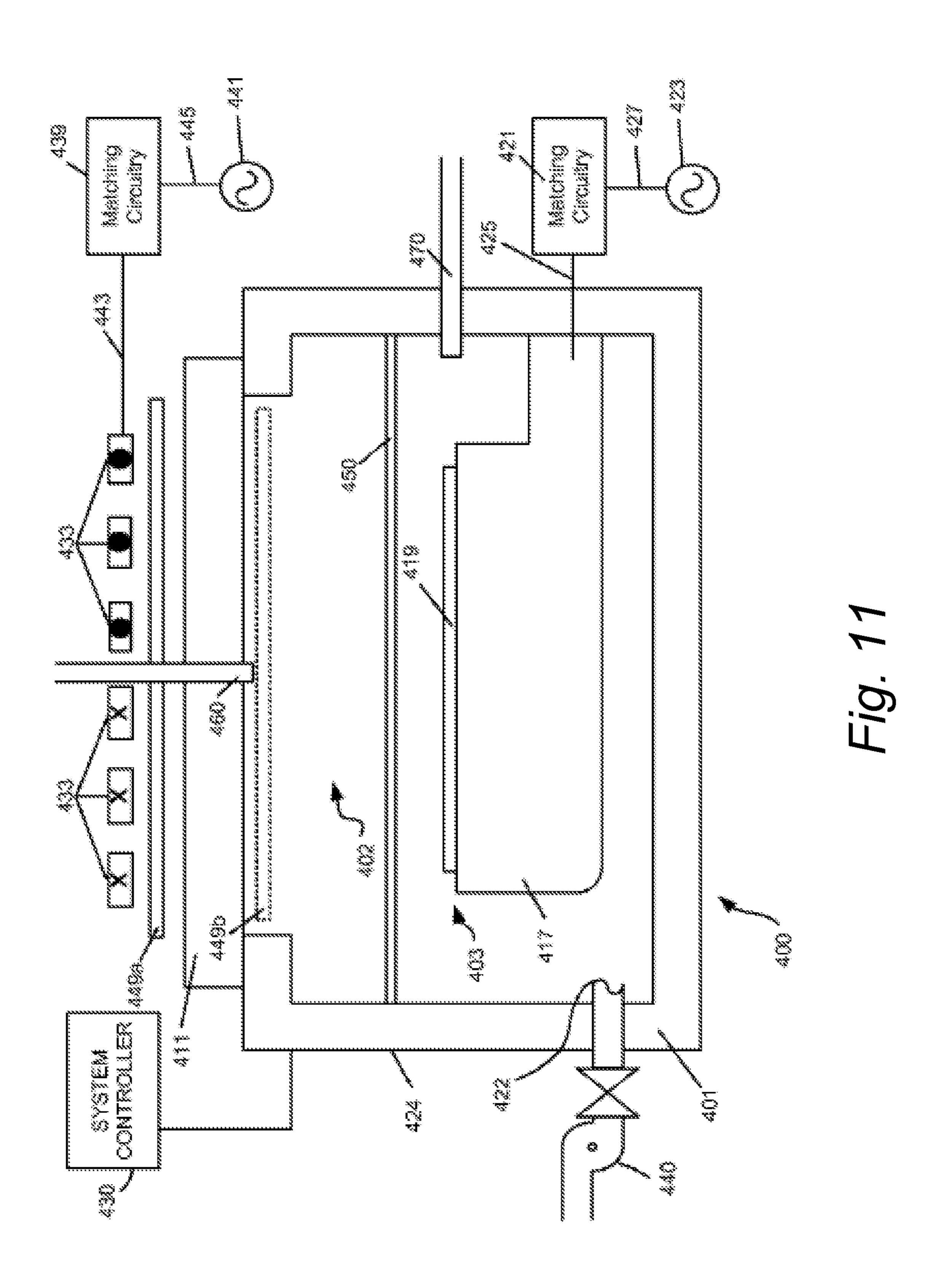

FIG. 11 is a schematic presentation of an apparatus that is suitable for etching tin oxide using etch chemistries provided herein.

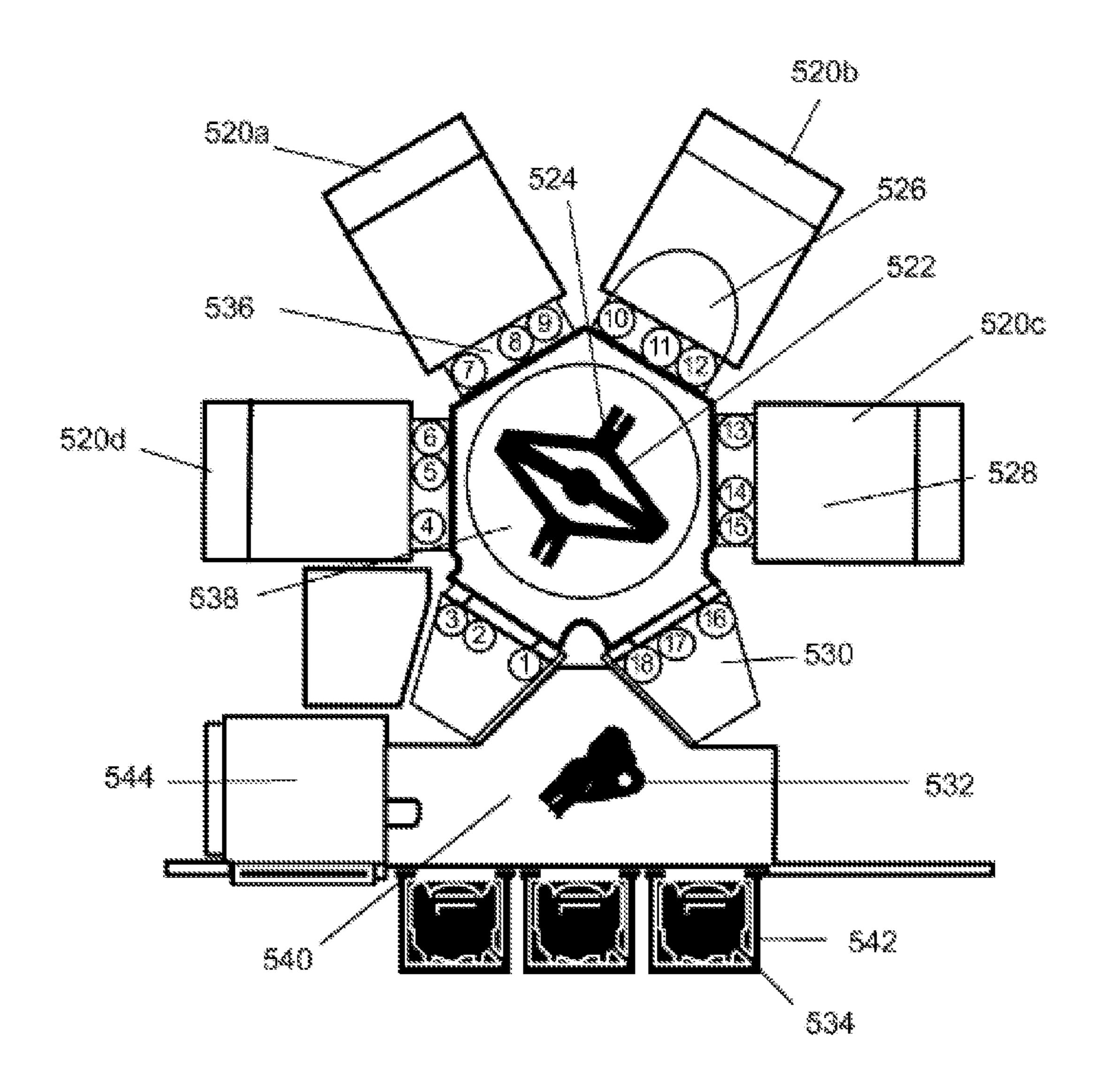

FIG. 12 shows a schematic view of a multi-station processing system according to an embodiment provided herein.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Methods that employ tin oxide films in semiconductor device manufacturing are provided. The methods utilize a number of etching processes with tunable etch rates and selectivities that allow integration of tin oxide films into process schemes that employ a wide variety of materials, such as silicon-containing compounds (e.g., silicon oxide (SiO<sub>2</sub>), silicon carbide (SiC), silicon nitride (SiN), silicon oxycarbide (SiOC), silicon oxynitride (SiNO), silicon oxycarbonitride (SiCNO), and silicon carbonitride (SiCN)), elemental silicon (Si), carbon (including amorphous carbon and diamond-like carbon), photoresist, carbon-containing compounds (e.g., organic polymers, metal carbides, tungsten-containing carbon), metals (e.g., tungsten), metal oxides (e.g., titanium oxide, hafnium oxide, zirconium oxide, tantalum oxide), and metal nitrides (e.g., tantalum nitride (TaN) and titanium nitride (TiN)). In some embodiments tin oxide is etched in a presence of any of these materials with an etch selectivity of at least about 10:1, such as at least about 20:1. In some embodiments, any of these materials is etched in a presence of tin oxide with an etch selectivity of at least about 10:1, such as at least about 20:1.

In some embodiments, tin oxide is used in patterning processes, where the tin oxide film is a spacer, or a hardmask (e.g., a middle layer positioned below photoresist and above a target layer). For example, tin oxide can be a spacer in self-aligned spacer-assisted patterning, a middle layer in self-aligned double patterning (SADP) or self-aligned quadruple patterning (SAQP), a contact hole hard mask, an extreme UV (EUV) hardmask, a reverse tone mask, or a back end of the line (BEOL) hard mask. In conjunction with selective etching processes, tin oxide meets stringent critical dimension (CD)/profile and selectivity requirements that are imposed by these applications. The etching processes can be implemented on a variety of tools that allow plasma etching, such as Kiyo® and Flex<sup>TM</sup> etch tools provided by Lam Research Corporation.

Tin oxide can be etched selectively to a wide variety of materials using hydrogen-based etches that convert tin oxide to volatile tin hydride products (e.g., tin tetrahydride). The term "tin hydride" as used herein includes a plurality of tin hydrides (compounds with tin-hydrogen bonding) and is not limited only to tin tetrahydride (SnH<sub>4</sub>)). Terms like "tin chloride" and "silicon fluoride" similarly may include multiple chlorides and fluorides. Tin tetrahydride, unlike hydrides of many other metals, has a low boiling point, and therefore can be easily removed from the process chambers by purging and/or evacuation thereby making hydrogen-based etch a particularly attractive process for selective tin oxide etching.

Tin oxide, as used herein, refers to materials that include tin (Sn) and oxygen (O), and may optionally include hydrogen. Tin oxide, as used herein, may further include small amounts of other elements, such as carbon, and nitrogen, where the total amount of other elements is 10 atomic % or less (where hydrogen is not included in the calculation of the 20 content). For example ALD-deposited tin oxide can contain about 0.5-5 atomic % carbon. Tin oxide can be deposited, for example, by ALD, PECVD, or PVD. The stoichiometry of tin oxide generally can vary. In some embodiments the atomic ratio of tin to oxygen is about 1:2 (SnO<sub>2</sub>). It is 25 understood that small deviations from 1:2 tin to oxygen stoichiometry are possible in SnO<sub>2</sub> and are within the scope of SnO<sub>2</sub> structure. For example, O to Sn atomic ratio is between about 2.0-2.3 in some examples of SnO<sub>2</sub>. Tin oxides with O to Sn ratio of between about 1.5-2.5 are within 30 the scope of SnO<sub>2</sub> material, as used herein. Tin oxide materials described herein are distinct from indium tin oxide materials, and other mixed oxides.

It is understood that in other chemical compounds as used herein, stoichiometry may vary, unless it is specified. For 35 example, formulas such as SiN and HfO specify the elements that are present but not the stoichiometry. Further, it is understood that materials described herein may include hydrogen (even if not specified in the formula) and small amounts of dopants not explicitly listed in the chemical 40 name (such as less than 10 atomic % of a dopant).

The term "semiconductor substrate" as used herein refers to a substrate at any stage of semiconductor device fabrication containing a semiconductor material anywhere within its structure. It is understood that the semiconductor material 45 in the semiconductor substrate does not need to be exposed. Semiconductor wafers having a plurality of layers of other materials (e.g., dielectrics) covering the semiconductor material, are examples of semiconductor substrates. The following detailed description assumes the disclosed imple- 50 mentations are implemented on a wafer. However, the disclosed implementations are not so limited. The work piece may be of various shapes, sizes, and materials. In addition to semiconductor wafers, other work pieces that may take advantage of the disclosed implementations 55 include various articles such as printed circuit boards and the like.

In some embodiments, provided selective etch chemistries are used to remove certain materials or features on a substrate without removing other materials or features. As 60 used herein, the etch chemistry "removes" a material or feature when at least 90% (such as 100%) of the material or feature is removed (referring to thickness in vertical direction). The term "without removing", as used herein means that at least 50% of material or feature (such as at least 80%) 65 remains after the etch, where % refers to thickness in a vertical direction.

8

In some embodiments provided methods are used to remove materials from horizontal surfaces without removing materials residing at sidewalls of protruding features. It is understood that horizontal surfaces, as used herein, include surfaces with local deviations from horizontal plane, such as convex caps on top of protruding features.

A variety of etch chemistries have been developed for selective etching of tin oxide in a presence of other materials, as well as for selective etching of other materials in a 10 presence of tin oxide. Selective etching of tin oxide in a presence of another material refers to tin oxide etching, wherein the ratio of the etch rate of tin oxide to the etch rate of the other material is greater than one, and wherein the other material is exposed to the same etch chemistry as tin oxide at any time of the etching process. For example, the other material may be exposed when the etching begins, or may become exposed during the course of etching. Etch selectivity for selective etching of tin oxide in a presence of another material refers to a ratio of an etch rate of tin oxide to an etch rate of the other material for a given chemistry. For example, tin oxide can be selectively etched in a presence of a silicon-containing compound using a hydrogen-based etch chemistry with an etch selectivity of greater than 50.

atomic ratio of tin to oxygen is about 1:2 (SnO<sub>2</sub>). It is 25 understood that small deviations from 1:2 tin to oxygen stoichiometry are possible in SnO<sub>2</sub> and are within the scope of SnO<sub>2</sub> structure. For example, O to Sn atomic ratio is between about 2.0-2.3 in some examples of SnO<sub>2</sub>. Tin oxides with O to Sn ratio of between about 1.5-2.5 are within oxides with O to Sn ratio of between about 1.5-2.5 are within the scope of SnO<sub>2</sub> material, as used herein. Tin oxide materials described herein are distinct from indium tin oxide materials, and other mixed oxides.

It is understood that in other chemical compounds as used herein, stoichiometry may vary, unless it is specified. For example, formulas such as SiN and HfO specify the elements that are present but not the stoichiometry. Further, it

In some embodiments a semiconductor substrate is provided, where the semiconductor substrate includes an exposed tin oxide layer and a layer of a second material, where the second material may be exposed or not exposed. Next tin oxide is selectively etched in a presence of the second material using one of the selective tin oxide etch chemistries described herein. The second material may be exposed prior to this etch or may become exposed during the course of tin oxide etching.

In some embodiments a semiconductor substrate is provided, where the semiconductor substrate includes an exposed layer of a first material and a layer of tin oxide, where the tin oxide may be exposed or not exposed. Next, the first material is selectively etched in a presence of the tin oxide using one of the selective chemistries described herein. The tin oxide may be exposed prior to this etch or may become exposed during the course of tin oxide etching.

Hydrogen-based etch. In some embodiments selective tin oxide etching is performed using a hydrogen-based etch. Hydrogen-based etch involves exposing tin oxide to a hydrogen-containing reactant (typically with plasma activation of the reactant) such that it converts tin oxide to a volatile tin hydride. SnH<sub>4</sub> has a boiling temperature of -52° C. and can be easily removed from the process chamber. Examples of hydrogen-containing reactants include H<sub>2</sub>, HBr, NH<sub>3</sub>, H<sub>2</sub>O, and hydrocarbons (such as CH<sub>4</sub>). Mixtures of hydrogen-containing reactants can also be used. Hydrogen-based etching involves forming a plasma in a process gas containing a hydrogen-containing reactant, and, optionally, an inert gas, and contacting the substrate with the

formed plasma. Examples of inert gases include nitrogen (N<sub>2</sub>), helium (He), argon (Ar), and neon (Ne), and xenon (Xe). In some embodiments  $H_2$  is the preferred hydrogencontaining reactant, and in some embodiments it is preferable to form plasma in a gas that contains at least 50%, such 5 as at least 80% H<sub>2</sub> by volume. In other embodiments HBr is used as the hydrogen-containing reactant. For example tin oxide can be selectively etched with a plasma formed in a process gas consisting essentially of HBr and an inert gas, such as in a mixture of HBr, N<sub>2</sub> and argon. The hydrogen- 10 based etch is typically conducted with a process gas that does not include oxygen-containing and fluorine-containing species. In some embodiments, the process gas consists essentially of one or more hydrogen-containing reactants and, optionally, an inert gas.

Hydrogen-based etch can selectively remove tin oxide in a presence of the following materials: silicon-containing compounds, such as SiO<sub>2</sub>, SiN, SiC, SiOC, SiCN, SiON, SiCNO, spin on glass; metal oxides, such as titanium oxide, tungsten oxide, and zirconium oxide; metal nitrides, such as 20 titanium nitride and tantalum nitride; metals, such as tungsten; photoresist and organic polymers. Further, hydrogen based etch can be used to selectively etch tin oxide in a presence of silicon oxide covered silicon. Silicon oxide often forms on silicon surfaces when silicon is exposed to 25 atmosphere. Hydrogen-based etch can be also used to selectively etch tin oxide in a presence of elemental silicon (e.g., amorphous silicon), and carbon. Further, hydrogen-based etch can be used to selectively etch tin oxide in a presence of metal carbides, and materials that contain metal and 30 carbon. For example, tin oxide can be selectively etched with a hydrogen-based etch in a presence of a tungsten carbon material (also referred to as tungsten-doped carbon). In some embodiments, tungsten carbon material includes between about 20-60 atomic % tungsten.

In some embodiments a semiconductor substrate is provided, where the semiconductor substrate includes an exposed tin oxide layer and a layer of any of these materials. Next, tin oxide is selectively etched in a presence of these materials. These materials may be exposed prior to this etch 40 or may become exposed during the course of tin oxide etching.

The etch selectivity of the hydrogen-based etch in some embodiments is greater than 10, such as greater than 30, e.g., greater than 50, or greater than 80. The etch selectivity refers 45 to the ratio of the etch rate of tin oxide to the etch rate of the other material for selected process conditions. In some examples, etch selectivity of 100 was achieved for etching tin oxide relative to SiO<sub>2</sub> with the use of H<sub>2</sub> plasma.

The tin oxide etching methods that utilize hydrogen 50 iv. CH<sub>4</sub>: 0 to 500 sccm (e.g., 5-100 sccm). plasma (referring to a plasma formed in a hydrogen-containing reactant) can be implemented in a variety of apparatuses under a wide range of process conditions. In one implementation the methods involve, providing a semiconductor substrate having an exposed layer of tin oxide to an 55 etch chamber, and contacting the substrate with a plasma formed in a process gas comprising H<sub>2</sub> (or another hydrogen-containing gas), and, optionally a carrier gas, such as helium or another inert gas. The term "etch chamber" or an "etching apparatus" refers to a chamber and an apparatus 60 i. H<sub>2</sub>: 100 to 300 sccm; that are configured for etching. In some embodiments the "etch chamber" or the "etching apparatus" are exclusively configured for etching operations. In other embodiments the "etch chamber" or "etching apparatus" may be configured to perform other operations in addition to etching, such as, for 65 pressure of between about 1 to 30 mTorr. example, deposition. For example, in some embodiments the etch chamber may also be used for ALD deposition.

**10**

In some embodiments the plasma used for in the hydrogen plasma etch is generated in the same process chamber that houses the semiconductor substrate. In other embodiments the plasma is generated remotely, and is introduced into the process chamber that houses the substrate through one or more inlets in the process chamber.

The etching is controlled such as to convert tin oxide to a volatile tin hydride. In one embodiment the H<sub>2</sub> content in the process gas is at least 50% by volume, such as at least 80% by volume (can be up to and including 100%). In some embodiments, the process gas may further include a hydrocarbon, such as CH<sub>4</sub>. In some embodiments, the process gas further includes Cl<sub>2</sub>.For example, the process gas may consist essentially of H<sub>2</sub> and an inert gas (e.g., He), or the 15 process gas may consist essentially of H<sub>2</sub>, inert gas and a hydrocarbon (e.g.,  $CH_{4}$ ). The etch is performed at a temperature of less than about 100° C., measured near the substrate. The etch reaction, advantageously, generates only volatile materials, such as SnH<sub>4</sub>, which can be easily removed from the etch process chamber by evacuation and/or purging. The etch process temperature is preferably selected to be less than about 100° C., because higher temperatures can lead to decomposition of formed SnH<sub>4</sub> and to formation of particles that can contaminate the process chamber and the substrate. The composition of the process gas and process conditions are selected such as to reduce or eliminate formation of particles during the etch. Significantly, the etch reaction does not require any significant sputtering component, and can be performed in an absence of external bias at the substrate, and in an absence of heavy ions (e.g., argon ions). Reducing sputtering component can be beneficial for increasing the etch selectivity relative to the second material on the substrate. Thus, in some embodiments etching is performed without providing an external 35 bias to the substrate and/or involves using helium (a light gas) as the carrier gas, in order to reduce sputtering.

Plasma for the hydrogen plasma etch can be generated using a variety of frequencies (low and high). Examples of suitable frequencies include 400 KHz, 2 MHz, 13.56 MHz, 27 MHz or 2.45 GHz. Power used for plasma generation can range in some embodiments, from between about 50 W to 1,000 W corresponding to power density of between about 0.0018 and 0.36 W/cm<sup>2</sup>. The bias at the substrate is optional, and bias power can range from about 0 to 500 W. Suitable gas flow rates per showerhead (for processing one 300 mm wafer) are:

```

i. H<sub>2</sub>: 25 to 750 sccm;

ii. Cl<sub>2</sub>: 0 to 500 sccm (e.g., 5-200 sccm);

iii. He: 0 to 500 sccm (e.g., 5-100 sccm); and

```

The etch process can be performed, in some embodiments, at a pressure of between about 1 to 175 mTorr.

In some specific embodiments the plasma is generated using high frequency generation (e.g., 13.56 MHz or 27 MHz), and it is provided using plasma power of between about 200 to 500 W corresponding to power density of 0.07 and 0.18 W/cm<sup>2</sup>. The power for the bias at the substrate is between about 0 and 200 W. Suitable gas flow rates per showerhead (for processing one 300 mm wafer) are:

```

ii. Cl<sub>2</sub>: 0 to 200 sccm (e.g., 5-100 sccm);

iii. He: 0 to 100 sccm (e.g., 5-50 sccm);

iv. CH<sub>4</sub>: 0 to 100 sccm (e.g., 5-50 sccm).

```

The etch process is performed in these embodiments at a

It was discovered that the selectivity of the hydrogenbased etch can be significantly increased by using carbon-

containing reactants in the process gas that form a carboncontaining polymer (e.g.  $CH_x$  polymer) on the surface of the substrate during the etch. In some embodiments, the process gas used in this embodiment includes H<sub>2</sub> and a hydrocarbon (e.g., methane  $(CH_4)$ ). The process gas typically also <sup>5</sup> includes an inert gas. The ratio of H<sub>2</sub> to hydrocarbon, in some embodiments is preferably at least 5, such as at least 10. In some embodiments the volume ratio of H<sub>2</sub> to hydrocarbon is between about 5-500, such as about 10-300. In some embodiments selective etching of tin oxide in a presence of another material (or materials) includes exposing the substrate to a plasma formed in a process gas comprising H<sub>2</sub> and a hydrocarbon (e.g., CH<sub>4</sub>). In one implementation H<sub>2</sub> is provided at a flow rate of between about 100-500 sccm, and hydrocarbon is provided at a flow rate of between about 1-20 sccm (such as between about 5-10 sccm). The process can be conducted using plasma power of between about 100-1,000 W, such as between about 200-500 W (for a single 300 mm wafer), corresponding to power 20 densities of between about 0.14-1.3 W/cm<sup>2</sup>, such as 0.28-0.71 W/cm<sup>2</sup>. In some implementations, the etch is conducted using a substrate bias of between about 50-500 Vb, such as between about 100-200 Vb. The process is preferably performed at a temperature of less than about 100° C. In one 25 specific example the following gases are provided: H<sub>2</sub> at 100 sccm; CH<sub>4</sub> at 5 sccm, and helium at 100 sccm. The plasma is formed in the process gas using a power of 300 W, and the substrate bias of 100 Vb at 25% duty cycle is used. The process is performed at 30° C. and at a pressure of 5 mTorr. 30 The formation of carbon-containing polymer on a substrate as described herein can increase the etch selectivity of tin oxide relative to any of the materials listed herein. This effect is particularly useful when tin oxide is etched in a presence of photoresist, carbon, carbon-containing materi- 35 als, and silicon (Si). For example when the etching is conducted in a presence of photoresist, the etch selectivity can be greater than 100, and in some cases is nearly infinite. The use of this highly selective etch allows the use of photoresist of smaller thickness to lower photolithographic 40 exposure dose and/or to prevent photoresist line collapse due to high aspect ratio at small fine pitch. In the described method the CH<sub>x</sub> polymer protects the photoresist from being etched. Further this etch can be used to improve the geometry of the photoresist layer. In some embodiments, the tin 45 oxide on a semiconductor substrate is selectively etched using this etch in a presence of a photoresist disposed above the tin oxide layer, and in a presence of a material that underlies tin oxide, with an etch selectivity of at least 10 relative to both photoresist and the material that underlies tin 50 oxide. In some embodiments the material that underlies tin oxide includes one or more of silicon (e.g., amorphous silicon), silicon-containing compound (e.g., SiO<sub>2</sub>, SiN, SiC, SiON, SiOC), carbon (e.g., amorphous carbon), and a carbon-containing compound (e.g., carbon tungsten).

In some embodiments, HBr is used as a hydrogen-containing reactant in the hydrogen-based etch. In one implementation, the etching method involves flowing HBr at a flow rate of 100-50 sccm, and an inert gas (e.g., helium) at a flow rate of 100-500 sccm and forming a plasma in this 60 process gas using RF power of 100-500 W (per one 300 mm wafer) corresponding to power densities of 0.14-0.71 W/cm². This etch can be conducted with or without a substrate bias. For example, substrate bias may be between 0-200 Vb, such as 50-200 Vb. The process can be performed 65 at a temperature of less than 100° C. and a pressure of 5-50 mTorr.

12