### US010437644B2

# (12) United States Patent

# Sandstrom

# (10) Patent No.: US 10,437,644 B2

# (45) **Date of Patent:** \*Oct. 8, 2019

# (54) TASK SWITCHING AND INTER-TASK COMMUNICATIONS FOR COORDINATION OF APPLICATIONS EXECUTING ON A MULTI-USER PARALLEL PROCESSING ARCHITECTURE

(71) Applicant: ThroughPuter, Inc., Jersey City, NJ (US)

(72) Inventor: Mark Henrik Sandstrom, Helsinki

(FI)

(73) Assignee: ThroughPuter, Inc., Jersey City, NJ

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 16/399,593

(22) Filed: Apr. 30, 2019

(65) Prior Publication Data

US 2019/0258519 A1 Aug. 22, 2019

# Related U.S. Application Data

- (60) Continuation of application No. 16/226,502, filed on Dec. 19, 2018, now Pat. No. 10,310,902, which is a (Continued)

- (51) **Int. Cl.**

G06F 9/46 (2006.01) G06F 9/50 (2006.01)

(Continued)

(52) **U.S. Cl.**CPC ...... *G06F 9/5011* (2013.01); *G06F 9/46*(2013.01); *G06F 9/4881* (2013.01); *G06F*9/505 (2013.01);

(Continued)

(58) Field of Classification Search

None

See application file for complete search history.

# (56) References Cited

# U.S. PATENT DOCUMENTS

4,402,046 A 8/1983 Cox et al. 4,404,628 A 9/1983 Angelo (Continued)

# FOREIGN PATENT DOCUMENTS

DE 3340123 A1 5/1985 EP 255857 A2 2/1988 (Continued)

#### OTHER PUBLICATIONS

Han, Wei, et al., Multi-core Architectures with Dynamically Reconfigurable Array Processors for the WiMAx Physical layer, pp. 115-120, 2008. (submitted in related U.S. Appl. No. 16/226,502). (Continued)

Primary Examiner — Bing Zhao (74) Attorney, Agent, or Firm — Gardella Grace P.A.

# (57) ABSTRACT

Systems and methods provide an extensible, multi-stage, realtime application program processing load adaptive, manycore data processing architecture shared dynamically among instances of parallelized and pipelined application software programs, according to processing load variations of said programs and their tasks and instances, as well as contractual policies. The invented techniques provide, at the same time, both application software development productivity, through presenting for software a simple, virtual static view of the actually dynamically allocated and assigned processing hardware resources, together with high program runtime performance, through scalable pipelined and parallelized program execution with minimized overhead, as well as high resource efficiency, through adaptively optimized processing resource allocation.

### 20 Claims, 10 Drawing Sheets

### Related U.S. Application Data

continuation of application No. 16/145,632, filed on Sep. 28, 2018, now Pat. No. 10,310,901, which is a continuation of application No. 16/014,674, filed on Jun. 21, 2018, now Pat. No. 10,133,600, which is a continuation of application No. 14/521,490, filed on Oct. 23, 2014, which is a continuation of application No. 13/297,455, filed on Nov. 16, 2011, now abandoned, said application No. 16/145,632 is a continuation of application No. 16/014,674, filed on Jun. 21, 2018, now Pat. No. 10,133,600, which is a continuation of application No. 15/933,724, filed on Mar. 23, 2018, now Pat. No. 10,061,615, which is a continuation of application No. 15/273,731, filed on Sep. 23, 2016, which is a continuation of application No. 15/183,860, filed on Jun. 16, 2016, now Pat. No. 9,465,667, which is a division of application No. 15/042,159, filed on Feb. 12, 2016, now Pat. No. 9,400,694, which is a continuation of application No. 14/261,384, filed on Apr. 24, 2014, now Pat. No. 9,262,204, which is a continuation of application No. 13/684,473, filed on Nov. 23, 2012, now Pat. No. 8,789,065.

(60) Provisional application No. 61/657,708, filed on Jun. 8, 2012, provisional application No. 61/673,725, filed on Jul. 19, 2012, provisional application No. 61/721,686, filed on Nov. 2, 2012, provisional application No. 61/727,372, filed on Nov. 16, 2012, provisional application No. 61/556,065, filed on Nov. 4, 2011.

# (51) Int. Cl. G06F 15/173 (2006.01) H04L 12/933 (2013.01) G06F 9/54 (2006.01) G06F 9/48 (2006.01)

# (56) References Cited

# U.S. PATENT DOCUMENTS

| 4,956,771 A | 9/1990  | Neustaedter                |

|-------------|---------|----------------------------|

| 5,031,146 A | 7/1991  | Umina et al.               |

| 5,237,673 A | 8/1993  | Orbits et al.              |

| 5,303,369 A | 4/1994  | Borcherding et al.         |

| 5,452,231 A | 9/1995  | Butts et al.               |

| 5,519,829 A | 5/1996  | Wilson                     |

| 5,612,891 A | 3/1997  | Butts et al.               |

| 5,752,030 A | 5/1998  | Konno et al.               |

| 5,809,516 A | 9/1998  | Ukai et al.                |

| 5,931,959 A | 8/1999  | Kwiat                      |

| 6,072,781 A | 6/2000  | Feeney et al.              |

| 6,108,683 A | 8/2000  | Kamada et al.              |

| 6,212,544 B | 4/2001  | Borkenhagen et al.         |

| 6,289,434 B | 9/2001  | Roy                        |

| 6,289,440 B | 9/2001  | Casselman                  |

| 6,334,175 B | 12/2001 | Chih                       |

| 6,345,287 B | 2/2002  | Fong et al.                |

| 6,353,616 B | 3/2002  | Elwalid et al.             |

| 6,366,157 B | 4/2002  | Abdesselem et al.          |

| 6,721,948 B |         | $\boldsymbol{\mathcal{U}}$ |

| 6,769,017 B | 7/2004  | Bhat et al.                |

| 6,782,410 B | 8/2004  | Bhagat et al.              |

```

6,816,905 B1

11/2004 Sheets et al.

6,912,706 B1

6/2005 Stamm et al.

6/2006 Guettaf

7,058,868 B2

7,093,258 B1

8/2006 Miller et al.

7,099,813 B2

8/2006 Nightingale

7,110,417 B1

9/2006 El-Hennawey et al.

7,178,145 B2

2/2007 Bono

7,328,314 B2

2/2008 Kendall et al.

7,370,013 B1

5/2008 Aziz et al.

6/2008 Alpert et al.

7,389,403 B1

7,406,407 B2

7/2008 Laws

11/2008 Nordquist

7,447,873 B1

7,461,376 B2

12/2008 Geye et al.

7,503,045 B1

3/2009 Aziz et al.

7,518,396 B1

4/2009 Kondapalli et al.

8/2009 Pechanek

7,581,079 B2

7,665,092 B1

2/2010 Vengerov

7,698,541 B1

4/2010 Robles

7,738,496 B1

6/2010 Raza

6/2010 Vermeulen et al.

7,743,001 B1

7/2010 Miyaho et al.

7,760,625 B2

7/2010 Cismas et al.

7,765,547 B2

7,802,255 B2

9/2010 Pilkington

7,805,706 B1

9/2010 Ly et al.

7,861,063 B1

12/2010 Golla et al.

7,908,606 B2

3/2011 Depro et al.

7/2011 Yung et al.

7,984,246 B1

7,990,974 B1

8/2011 Gmuender et al.

8,001,549 B2

8/2011 Henmi

8,015,392 B2

9/2011 Naik et al.

8,018,961 B2

9/2011 Gopinath et al.

8,024,731 B1

9/2011 Cornwell et al.

8,032,889 B2

10/2011 Conrad et al.

8,046,766 B2

10/2011 Rhine

8,059,674 B2

11/2011 Cheung et al.

8,060,610 B1

11/2011 Herington

8,087,029 B1

12/2011 Lindholm et al.

8,095,662 B1

1/2012 Lappas et al.

1/2012 Fouladi et al.

8,098,255 B2

8,230,070 B2

7/2012 Buyya et al.

8,271,730 B2

9/2012 Piry et al.

12/2012 Bell, Jr. et al.

8,327,126 B2

1/2013 Maddhuri et al.

8,352,611 B2

4/2013 Nickolov et al.

8,429,630 B2

8,429,656 B1*

4/2013 Duluk, Jr. ...... G06F 9/5027

718/102

8,447,933 B2

5/2013 Nishihara

8,533,674 B2

9/2013 Abrams et al.

8,539,207 B1

9/2013 LeGrand

8,566,836 B2

10/2013 Ramaraju et al.

4/2014 Chambliss et al.

8,713,572 B2

4/2014 Creamer et al.

8,713,574 B2

8,745,241 B2

6/2014 Waldspurger

8,893,016 B2 *

345/502

9,348,724 B2

5/2016 Ota et al.

9,448,847 B2

9/2016 Sandstrom

11/2016 Hartog ...... G06F 9/4881

9,507,632 B2*

9,608,933 B2

3/2017 Emaru

4/2002 Masters

2002/0040400 A1

2002/0056033 A1

5/2002 Huppenthal

8/2002 Schott et al.

2002/0112091 A1

2002/0124012 A1

9/2002 Liem et al.

2002/0129080 A1

9/2002 Hentschel et al.

10/2002 Bays

2002/0141343 A1

2002/0143843 A1

10/2002 Mehta

2002/0169828 A1

11/2002 Blanchard

2003/0018807 A1

1/2003 Larsson et al.

2003/0235200 A1

12/2003 Kendall et al.

2004/0088488 A1

5/2004 Ober et al.

6/2004 Libby

2004/0111724 A1

2004/0128401 A1

7/2004 Fallon et al.

2004/0158637 A1

8/2004 Lee

2004/0168170 A1

8/2004 Miller

9/2004 Koga et al.

2004/0193806 A1

2004/0210900 A1

10/2004 Jones et al.

2005/0010502 A1

1/2005 Birkestrand et al.

2005/0013705 A1

1/2005 Farkas et al.

```

2/2005 Cheung et al.

2005/0036515 A1

| (56)                         |            | Referen          | ces Cited                          |              |                            |                                         | Peterson et al.                                                         |

|------------------------------|------------|------------------|------------------------------------|--------------|----------------------------|-----------------------------------------|-------------------------------------------------------------------------|

| -                            | U.S. I     | PATENT           | DOCUMENTS                          | 2013/022     | 2402 A1                    | 8/2013                                  | Bell, Jr. et al. Peterson et al.                                        |

| 2005/0055604                 |            | 2/2005           | <b>T</b>                           |              | 3135 A1<br>31501 A1        |                                         | Huang et al.<br>Hicok et al.                                            |

| 2005/0055694<br>2005/0080999 |            | 3/2005<br>4/2005 | Lee<br>Angsmark et al.             |              | 7378 A1                    | 10/2014                                 |                                                                         |

| 2005/0080555                 |            |                  | Sheets et al.                      |              |                            | 11/2014                                 | Mitra et al.                                                            |

| 2005/0188372                 |            |                  | Inoue et al.                       |              | 8116 A1                    |                                         | Jorgensen et al.                                                        |

| 2005/0193186                 |            |                  | Gazsi et al.                       |              |                            | 12/2015                                 | Peterson et al.<br>Lippett                                              |

| 2005/0198476<br>2005/0235070 |            |                  | Gazsi et al.<br>Young et al.       |              |                            |                                         | Vorbach et al.                                                          |

| 2005/0268298                 |            |                  | Hunt et al.                        |              | 30201 A1                   |                                         | Huang et al.                                                            |

| 2005/0278551                 |            |                  | Goodnow et al.                     |              | 8538 A1                    | 12/2016                                 |                                                                         |

| 2006/0036774                 |            |                  | Schott et al.                      | 2017/009     | 7838 A1                    | 4/201/                                  | Nagapudi et al.                                                         |

| 2006/0059485<br>2006/0061794 |            |                  | Onufryk et al.<br>Ito et al.       |              | FOREIG                     | N PATE                                  | NT DOCUMENTS                                                            |

| 2006/0070078                 |            |                  | Dweck et al.                       |              | TOTALIO                    | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | THE DOCUMENTS                                                           |

| 2006/0075265                 |            |                  | Hamaoka et al.                     | EP           | 889                        | 622 A2                                  | 7/1999                                                                  |

| 2006/0179194                 |            | 8/2006           |                                    | EP           |                            | 9388 A1                                 | 4/2011                                                                  |

| 2006/0195847<br>2006/0218376 |            |                  | Amano et al.<br>Pechanek           | GB<br>GB     |                            | 5177 A<br>5255 A                        | 6/1971<br>3/1985                                                        |

| 2007/0074011                 |            |                  | Borkar et al.                      | GB           |                            | 2311 A                                  | 5/1994                                                                  |

| 2007/0153802                 |            |                  | Anke et al.                        | JP           |                            | '619 A                                  | 8/1993                                                                  |

| 2007/0220517                 |            |                  | Lippett                            | JP           |                            | 314 A                                   | 1/1994                                                                  |

| 2007/0226482<br>2007/0291576 |            | 12/2007          | Borkar et al.                      | JP<br>SU     |                            | 3291 A<br>7106 A1                       | 12/1999<br>7/1987                                                       |

| 2008/0077927                 |            |                  | Armstrong et al.                   | WO           |                            | 100 A1<br>0426 A2                       | 11/2000                                                                 |

| 2008/0086395                 | <b>A</b> 1 |                  | Brenner et al.                     | WO           |                            | 3467 A1                                 | 10/2011                                                                 |

| 2008/0189703                 |            |                  | Im et al.                          |              |                            |                                         |                                                                         |

| 2008/0244588<br>2008/0256339 |            |                  | Leiserson et al.<br>Xu et al.      |              | OTI                        | HER PU                                  | BLICATIONS                                                              |

| 2008/0230339                 |            |                  | Herington                          |              |                            |                                         |                                                                         |

| 2009/0049443                 |            |                  | Powers et al.                      |              | -                          |                                         | nation to support concurrent appli-                                     |

| 2009/0070762                 |            |                  | Franaszek et al.                   | •            |                            |                                         | Computers, vol. 48, Issue 6, pp.                                        |

| 2009/0178047<br>2009/0187756 |            |                  | Astley et al.                      |              | •                          |                                         | related U.S. Appl. No. 16/226,502).                                     |

| 2009/0187730                 |            |                  | Nollet et al.<br>Chen et al.       | ,            | •                          |                                         | emory Architectures for Multi-Core lety, pp. 453-464, 2008. (submitted  |

| 2009/0265712                 |            |                  | Herington                          |              | U.S. Appl. N               |                                         |                                                                         |

| 2009/0327446                 |            |                  | Wittenschlaeger                    |              |                            |                                         | ic Processor Allocation Policy for                                      |

| 2010/0043008                 |            |                  | Marchand<br>Dall In at al          |              |                            |                                         | ory Multiprocessors, 1993, ACM,                                         |

| 2010/0049963<br>2010/0058346 |            |                  | Bell, Jr. et al.<br>Narang et al.  | <b>.</b> .   | ,                          |                                         | related U.S. Appl. No. 16/226,502).                                     |

| 2010/0100883                 |            |                  | Booton                             | ·            | ·                          | •                                       | pased static allocation policies for eedings International Phoenix Con- |

| 2010/0131955                 |            |                  | Brent et al.                       | ~ , ,        | -                          | •                                       | nunications, Scottsdale, AZ, 1995,                                      |

| 2010/0138913                 |            |                  | Saroj et al.                       |              | -                          |                                         | U.S. Appl. No. 16/226,502).                                             |

| 2010/0153700<br>2010/0153955 |            |                  | Capps, Jr. et al.<br>Sirota et al. |              | '                          |                                         | multiprocessor system supporting                                        |

| 2010/0162230                 |            |                  | Chen et al.                        | -            | ~                          |                                         | cation, Journal of the Faculty of                                       |

| 2010/0192155                 |            |                  | Nam et al.                         | •            | •                          | •                                       | yo, Series A, No. 24, 1986, pp.                                         |

| 2010/0205602                 |            |                  | Zedlewski et al.                   | `            |                            |                                         | S. Appl. No. 16/226,502).                                               |

| 2010/0232396<br>2010/0268889 |            |                  | Jing et al. Conte et al.           | ·            |                            | •                                       | sos: A Platform for Fine-Grained nter, Proceedings of NSDI '11: 8th     |

| 2010/0287320                 |            |                  | Querol et al.                      |              | •                          |                                         | orked Systems Design and Imple-                                         |

| 2011/0014893                 |            |                  | Davis et al.                       |              | • •                        |                                         | 95-308. (submitted in related U.S.                                      |

| 2011/0035749                 |            |                  | Krishnakumar et al.                | Appl. No.    | 16/226,502)                |                                         | · · · · · · · · · · · · · · · · · · ·                                   |

| 2011/0050713<br>2011/0055480 |            |                  | McCrary et al. Guyetant et al.     | _            |                            |                                         | ecture of Next Generation Apache                                        |

| 2011/0096667                 |            |                  | Arita et al.                       | -            | -                          |                                         | k, 2011, 14 pages. (submitted in                                        |

| 2011/0119674                 |            |                  | Nishikawa                          |              | S. Appl. No.               | •                                       | <i>'</i>                                                                |

| 2011/0154348                 |            |                  | Elnozahy et al.                    | r            |                            | ~                                       | Data Center Network, Proceedings mposium on Networked Systems           |

| 2011/0161969<br>2011/0173432 |            |                  | Arndt et al.<br>Cher et al.        |              |                            | •                                       | : 30, 2011, pp. 309-322. (submitted                                     |

| 2011/0197048                 |            |                  | Chung et al.                       | •            | U.S. Appl. N               | •                                       | , 11                                                                    |

| 2011/0247012                 |            | 10/2011          |                                    | [#HADOO      | P-3445] Im                 | plementin                               | g core scheduler functionality in                                       |

| 2011/0249678                 |            |                  | Bonicatto et al.                   |              | - '                        | •                                       | doop, Accessed May 18, 2018, 12                                         |

| 2011/0258317<br>2011/0296138 |            |                  | Sinha et al.<br>Carter et al.      | <b>.</b> • • | -                          |                                         | /jira/si/jira.issueviews:issue-html/                                    |

| 2011/0220150                 |            |                  | Mejdrich et al.                    |              |                            |                                         | S.html. (submitted in related U.S.                                      |

| 2012/0022832                 |            |                  | Shannon et al.                     | 1 1          | 16/226,502)<br>Iatei et al |                                         | duling for Multi-User MapReduce                                         |

| 2012/0079501                 |            |                  | Sandstrom Adar et al               |              |                            |                                         | ublication date unknown,18 pages,                                       |

| 2012/0089985<br>2012/0173734 |            |                  | Adar et al.<br>Kimbrel et al.      | ·            | <u>-</u>                   | · -                                     | puter Sciences, University of Cali-                                     |

| 2012/01/5/51                 |            |                  | Vorbach et al.                     | fornia at B  | erkeley, http              | s://www2                                | .eecs.berkeley.edu/Pubs/TechRpts/                                       |

| 2012/0221886                 |            |                  | Barsness et al.                    |              | · ·                        | df. (subm                               | nitted in related U.S. Appl. No.                                        |

| 2012/0222038                 |            |                  | Katragadda et al.                  | 16/226,502   | /                          | Onin                                    | Enin Cahadadina fan Dist it it i                                        |

| 2012/0222042<br>2012/0246450 |            | 8/2012<br>9/2012 | Chess<br>Abdallah                  |              |                            | ~ •                                     | Fair Scheduling for Distributed lay 18, 2018, 20 pages, sigops.org/     |

|                              |            |                  | Vojnovic et al.                    |              |                            |                                         | pdf. (submitted in related U.S. Appl.                                   |

| 2012/0200170                 |            |                  |                                    | No. 16/226   | <b>-</b> -                 |                                         | r ( tpp:                                                                |

No. 16/226,502).

2012/0303809 A1 11/2012 Patel et al.

# (56) References Cited

#### OTHER PUBLICATIONS

Tsai, Chang-Hao, System Architectures with Virtualized Resources in a Large-Scale Computing Infrastructure, 2009, 146 pages, Computer Science and Engineering, The University of Michigan, kabru. eecs.umich.edu/papers/thesis/chtsai-thesis.pdf. (submitted in related U.S. Appl. No. 16/226,502).

Sandholm, Thomas et al., Dynamic Proportional Share Scheduling in Hadoop, Accessed May 18, 2018, 20 pages, Hewlett-Packard Laboratories, citeseerx.ist.psu.edu/viewdoc/download?doi=10.1.1. 591.4477&rep=rep 1&type=pdf. (submitted in related U.S. Appl. No. 16/226,502).

Mohan, Shiwali et al., Towards a Resource Aware Scheduler in Hadoop, Dec. 21, 2009, 10 pages, Computer Science and Engineering, University of Michigan, Ann Arbor, pdfs.semanticscholar.org/d2e3/c7b60967934903f0837219772c6972ede93e.pdf. (submitted in related U.S. Appl. No. 16/226,502).

Tian, Chao et al., A Dynamic MapReduce Scheduler for Heterogeneous Workloads, 2009, pp. 218-224, IEEE Computer Society, pdfs.semanticscholar.org/679f/

73d810e2ac9e2e84de798d853b6fb0b0206a.pdf. (submitted in related U.S. Appl. No. 16/226,502).

Fischer, Michael J. et al., Assigning Tasks for Efficiency in Hadoop, 2010, 11 pages, researchgate.net/profile/Xueyuan\_Su/publication/221257628\_Assigning\_tasks\_for\_efficiency\_in\_Hadoop/links/53df31100cf216e4210c5fd1/Assigning-tasks-for-efficiency-in-Hadoop. pdf. (submitted in related U.S. Appl. No. 16/226,502).

Cooper, Brian F. et al., Building a Cloud for Yahoo!, 2009, 9 pages, IEEE Computer Society Technical Committee on Data Engineering, researchgate.net/profile/Rodrigo\_Fonseca3/publication/220282767\_Building\_a\_Cloud\_for Yahoo/links/0912f5109da99ddf6a000000/Building-a-Cloud-for-Yahoo.pdf. (submitted in related U.S. Appl. No. 16/226,502).

Lim, Harold C. et al., Automated Control in Cloud Computing: Challenges and Opportunities, Jun. 19, 2009, 6 pages, ACM, https://www2.cs.duke.edu/nicl/pub/papers/acdc09-lim.pdf. (submitted in related U.S. Appl. No. 16/226,502).

Wen et al., "Minimizing Migration on Grid Environments: an Experience on Sun Grid Engine" Journal of Information Technology and Applications, vol. 1, No. 4, pp. 297-304 (2007) (submitted in related U.S. Appl. No. 16/226,502).

Gentzsch, et al., "Sun Grid Engine: Towards Creating a Compute Power Grid." IEEE Computer Society, Proceedings of the 1st International Symposium on Cluster Computing and the Grid (2001). (submitted in related U.S. Appl. No. 16/226,502).

Borges, et al., "Sun Grid Engine, a new scheduler for EGEE middleware," (2018). (submitted in related U.S. Appl. No. 16/226,502). Shankar, Uma, Oracle Grid Engine Administration Guide, Release 6.2 Update 7, Aug. 2011, 202 pages, Oracle Corporation. (submitted in related U.S. Appl. No. 16/226,502).

Non-Final Rejection issued in related U.S. Appl. No. 13/297,455 dated Mar. 14, 2013, 23 pages. (submitted in related U.S. Appl. No. 16/226,502).

Final Rejection issued in related U.S. Appl. No. 13/297,455 dated Apr. 18, 2013, 18 pages. (submitted in related U.S. Appl. No. 16/226,502).

Non-Final Rejection issued in related U.S. Appl. No. 13/297,455 dated Jun. 19, 2014, 15 pages. (submitted in related U.S. Appl. No. 16/226,502).

Final Rejection issued in related U.S. Appl. No. 13/297,455 dated Sep. 3, 2014, 18 pages. (submitted in related U.S. Appl. No. 16/226,502).

Non-Final Rejection issued in related U.S. Appl. No. 13/297,455 dated Oct. 3, 2014, 29 pages. (submitted in related U.S. Appl. No. 16/226,502).

Final Rejection issued in related U.S. Appl. No. 13/297,455 dated Mar. 26, 2015, 14 pages. (submitted in related U.S. Appl. No. 16/226,502).

Examiner's Answer issued in related U.S. Appl. No. 13/297,455 dated Feb. 10, 2016, 9 pages. (submitted in related U.S. Appl. No. 16/226,502).

Non-Final Rejection issued in related U.S. Appl. No. 14/521,490 dated May 4, 2017, 19 pages. (submitted in related U.S. Appl. No. 16/226,502).

Final Rejection issued in related U.S. Appl. No. 14/521,490 dated Jul. 28, 2017, 16 pages. (submitted in related U.S. Appl. No. 16/226,502).

Non-Final Rejection issued in related U.S. Appl. No. 14/521,490 dated May 17, 2018, 23 pages. (submitted in related U.S. Appl. No. 16/226,502).

Ghodsi, Ali, et al., Dominant Resource Fairness: Fair Allocation of Multiple Resource Types, Proceedings of NSDI '11: 8th USENIX Symposium on Networked Systems Design and Implementation, Mar. 30, 2011, pp. 323-336. (submitted in related U.S. Appl. No. 16/226,502).

Final Rejection issued in related U.S. Appl. No. 14/521,490 dated Nov. 14, 2018, 21 pages. (submitted in related U.S. Appl. No. 16/226,502).

Notice of Allowance issued in related U.S. Appl. No. 16/014,658 dated Aug. 29, 2018, 22 pages. (submitted in related U.S. Appl. No. 16/226,502).

Notice of Allowance issued in related U.S. Appl. No. 16/014,674 dated Aug. 27, 2018, 21 pages. (submitted in related U.S. Appl. No. 16/226,502).

Notice of Allowance issued in related U.S. Appl. No. 16/145,632 dated Dec. 13, 2018, 11 pages. (submitted in related U.S. Appl. No. 16/226,502).

Partial Reconfiguration User Guide, a Xilinx, Inc. user document UG702 (v14.2) Jul. 25, 2012. (submitted in related U.S. Appl. No. 16/226,502).

Dye, David, Partial Reconfiguration of Xilinx FPGAs Using ISE Design Suite, a Xilinx, Inc. White Paper WP374 (v1.2), May 30, 2012. (submitted in related U.S. Appl. No. 16/226,502).

Lamonnier et al., Accelerate Partial Reconfiguration with a 100% Hardware Solution, Xcell Journal, Issue 79, Second Quarter 2012, pp. 44-49. (submitted in related U.S. Appl. No. 16/226,502).

7 Series FPGAs Configuration User Guide, a Xilinx, Inc. User Guide UG470 (v1.4) Jul. 19, 2012. (submitted in related U.S. Appl. No. 16/226,502).

Partial Reconfiguration Tutorial, PlanAhead Design Tool, a Xilinx, Inc. User Guide UG743 (v14.1) May 8, 2012. (submitted in related U.S. Appl. No. 16/226,502).

Tam et al., Fast Configuration of PCI Express Technology through Partial Reconfiguration, a Xilinx, Inc. Application Note XAPP883 (v1.0) Nov. 19, 2010. (submitted in related U.S. Appl. No. 16/226,502). Singh, Deshanand, Implementing FPGA Design with the OpenCL Standard, an Altera Corporation White Paper WP-01173-2.0, Nov. 2012. (submitted in related U.S. Appl. No. 16/226,502).

First Examination Report issued in IN Application No. 401/MUM/2011 dated Nov. 9, 2018. (submitted in related U.S. Appl. No. 16/226,502).

Notice of Allowance issued in related U.S. Appl. No. 16/226,502 dated Feb. 6, 2019, 10 pages. (submitted herewith).

Warneke et al., "Nephele: efficient parallel data processing in the cloud," MTAGS '09 Proceedings of the 2nd Workshop on Many-Task Computing on Grids and Supercomputers, Article No. 8 (2009). (submitted herewith).

Examination Report issued in IN Application No. 1220/MUM/2012 dated May 22, 2019.

\* cited by examiner

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

# TASK SWITCHING AND INTER-TASK COMMUNICATIONS FOR COORDINATION OF APPLICATIONS EXECUTING ON A MULTI-USER PARALLEL PROCESSING ARCHITECTURE

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation of U.S. application Ser. 10 No. 16/226,502 filed Dec. 19, 2018, which is a continuation of U.S. application Ser. No. 16/145,632 filed Sep. 28, 2018, which is a continuation of U.S. application Ser. No. 16/014, 674 filed Jun. 21, 2018 (now U.S. Pat. No. 10,133,600), which is a continuation of U.S. application Ser. No. 15/933, 15 724 filed Mar. 23, 2018 (now U.S. Pat. No. 10,061,615), which is a continuation of U.S. application Ser. No. 15/273, 731 filed Sep. 23, 2016, which is a continuation of U.S. application Ser. No. 15/183,860 filed Jun. 16, 2016 (now U.S. Pat. No. 9,465,667), which is a divisional of U.S. <sup>20</sup> application Ser. No. 15/042,159 filed Feb. 12, 2016 (now U.S. Pat. No. 9,400,694), which is a continuation of U.S. application Ser. No. 14/261,384 filed Apr. 24, 2014 (now U.S. Pat. No. 9,262,204), which is a continuation of U.S. application Ser. No. 13/684,473 filed Nov. 23, 2012 (now 25) U.S. Pat. No. 8,789,065), which claims the benefit and priority of the following provisional applications:

- [1] U.S. Provisional Application No. 61/657,708 filed Jun. 8, 2012;

- [2] U.S. Provisional Application No. 61/673,725 filed Jul. 19, 2012;

- [3] U.S. Provisional Application No. 61/721,686 filed Nov. 2, 2012; and

- [4] U.S. Provisional Application No. 61/727,372 filed Nov. 16, 2012.

U.S. application Ser. No. 16/014,674 is also a continuation of U.S. application Ser. No. 14/521,490 filed Oct. 23, 2014, which is a continuation of U.S. application Ser. No. 13/297,455 filed Nov. 16, 2011, which claims the benefit and priority of U.S. Provisional Application No. 61/556,065 <sup>40</sup> filed Nov. 4, 2011.

This application is also related to the following: [5] U.S. application Ser. No. 13/184,028 filed Jul. 15, 2011; [6] U.S. application Ser. No. 13/270,194 filed Oct. 10, 2011 (now U.S. Pat. No. 8,490,111); and

[7] U.S. application Ser. No. 13/277,739 filed Nov. 21, 2011 (now U.S. Pat. No. 8,561,076).

All above identified applications are hereby incorporated by reference in their entireties for all purposes.

### BACKGROUND

# Technical Field

This invention pertains to the field of data processing and 55 networking, particularly to techniques for connecting tasks of parallelized programs running on multi-stage manycore processor with each other as well as with external parties with high resource efficiency and high data processing throughput rate.

### Descriptions of the Related Art

Traditionally, advancements in computing technologies have fallen into two categories. First, in the field conventionally referred to as high performance computing, the main objective has been maximizing the processing speed of

2

one given computationally intensive program running on a dedicated hardware comprising a large number of parallel processing elements. Second, in the field conventionally referred to as utility or cloud computing, the main objective has been to most efficiently share a given pool of computing hardware resources among a large number of user application programs. Thus, in effect, one branch of computing technology advancement effort has been seeking to effectively use a large number of parallel processors to accelerate execution of a single application program, while another branch of the effort has been seeking to efficiently share a single pool of computing capacity among a large number of user applications to improve the utilization of the computing resources.

However, there have not been any major synergies between these two efforts; often, pursuing any one of these traditional objectives rather happens at the expense of the other. For instance, it is clear that a practice of dedicating an entire parallel processor based (super) computer per individual application causes severely sub-optimal computing resource utilization, as much of the capacity would be idling much of the time. On the other hand, seeking to improve utilization of computing systems by sharing their processing capacity among a number of user applications using conventional technologies will cause non-deterministic and compromised performance for the individual applications, along with security concerns.

As such, the overall cost-efficiency of computing is not improving as much as any nominal improvements toward either of the two traditional objectives would imply: traditionally, single application performance maximization comes at the expense of system utilization efficiency, while overall system efficiency maximization comes at the expense of performance of by the individual application programs. There thus exists a need for a new parallel computing architecture, which, at the same time, enables increasing the speed of executing application programs, including through execution of a given application in parallel across multiple processor cores, as well as improving the utilization of the computing resources available, thereby maximizing the collective application processing throughput for a given cost budget.

Moreover, even outside traditional high performance computing, the application program performance require-45 ments will increasingly be exceeding the processing throughput achievable from a single central processing unit (CPU) core, e.g. due to the practical limits being reached on the CPU clock rates. This creates an emerging requirement for intra-application parallel processing (at ever finer grades) also for mainstream software programs (i.e. applications not traditionally considered high performance computing). Notably, these internally parallelized mainstream enterprise and web applications will be largely deployed on dynamically shared cloud computing infrastructure. Accordingly, the emerging form of mainstream computing calls for technology innovation supporting the execution of large number of internally parallelized applications on dynamically shared resource pools, such as manycore processors.

Furthermore, conventional microprocessor and computer system architectures use significant portions of their computation capacity (e.g. CPU cycles or core capacity of manycore arrays) for handling input and output (IO) communications to get data transferred between a given processor system and external sources or destinations as well as between different stages of processing within the given system. For data volume intensive computation workloads and/or manycore processor hardware with high IO band-

width needs, the portion of computation power spent on IO and data movements can be particularly high. To allow using maximized portion of the computing capacity of processors for processing the application programs and application data (rather than for system functions such as IO data movements), architectural innovations are also needed in the field of manycore processor IO subsystems. In particular, there is a need for a new manycore processor system data flow and IO architecture whose operation, while providing high IO data throughput performance, causes little or no overhead in terms of usage of the computation units of the processor.

#### **SUMMARY**

The invented systems and methods provide an extensible, multi-stage, application program load adaptive, parallel data processing architecture shared dynamically among a set of application software programs according to processing load variations of said programs. The invented techniques enable any program task instance to exchange data with any of the 20 task instances of its program within the multi-stage parallel data processing platform, while allowing any of said task instances to be executing at any core of their local processors, as well allowing any identified destination task instance to be not assigned for execution by any core for 25 periods of time, and while said task instances lack knowledge of which core, if any, at said platform is assigned for executing any of said task instances at any given time.

An aspect of the invention provides a system for information connectivity among tasks of a set of software pro- 30 grams hosted on a multi-stage parallel data processing platform. Such a system comprises: 1) a set of manycore processor based processing stages, each stage providing an array of processing cores, wherein each of said tasks is hosted on one of the processing stages, with tasks hosted on 35 a given processing stage referred to as locally hosted tasks of that stage, 2) a hardware implemented data packet switching cross-connect (XC) connecting data packets from an output port of a processing stage to an input port of a given processing stage if a destination software program task of 40 the data packet is hosted at the given processing stage, and 3) a hardware implemented receive logic subsystem, at any given one of the processing stages, connecting data packets from input ports of the given processing stage to the array of cores of that stage, so that a given data packet is connected 45 to such a core, if any exist at a given time, among said array that is assigned at the given time to process a program instance to which the given input packet is directed to. Various embodiments of such systems further comprise features whereby: a) at a given processing stage, a hardware 50 implemented controller i) periodically allocates the array of cores of the given stage among instances of its locally hosted tasks at least in part based on volumes of data packets connected through the XC to its locally hosted tasks and ii) accordingly inserts the identifications of the destination 55 programs for the data packets passed from the given processing stage for switching at the XC, to provide isolation between different programs among the set; b) the system supports multiple instances of each of the locally hosted tasks at their processing stages, and packet switching 60 through the XC to an identified instance of a given destination program task; c) said tasks are located across at least a certain subset of the processing stages so as to provide an equalized expected aggregate task processing load for each of the processing stages of said subset; and/or d) said tasks 65 are identified with incrementing intra-program task IDs according to their descending processing load levels within

4

a given program, wherein, among at least a subset of the processing stages, each processing stage of said subset hosts one of the tasks of each of the set programs so as to equalize sums of said task IDs of the tasks located on each of the processing stages of said subset.

An aspect of the invention further provides a method for information connectivity among tasks of a set of software programs. Such a method comprises: 1) hosting said tasks on a set of manycore processor based processing stages, each stage providing an array of processing cores, with tasks hosted on a given processing stage referred to as locally hosted tasks of that stage, 2) at a data packet switching cross-connect (XC), connecting data packets from an output port of a processing stage to an input port of a given processing stage if a destination software program task identified for a given data packet is hosted at the given processing stage, and 3) at any given one of the processing stages, connecting data packets from input ports of the given processing stage to the array of cores of that stage, so that a given data packet is connected to such a core, if any exist at a given time, among said array that is assigned at the given time to process a program instance to which the given input packet is directed to. Various embodiments of the method comprise further steps and features as follows: a) periodically allocating, by a controller at a given one of the processing stages, the array of cores of the given stage among instances of its locally hosted tasks at least in part based on volumes of data packets connected through the XC to its locally hosted tasks, with the controller, according to said allocating, inserting the identifications of the destination programs for the data packets passed from the given processing stage for switching at the XC, to provide isolation between different programs among the set; b) the steps of allocating and connecting, both at the XC and the given one of the processing stages, are implemented by hardware logic that operates without software involvement; c) supporting multiple instances of each of the locally hosted tasks at their processing stages, and packet switching through the XC to an identified instance of a given destination task; d) said tasks are located across at least a certain subset of the processing stages so as to provide an equalized expected aggregate task processing load for each of the processing stages of said subset; and/or e) said tasks are identified with incrementing intra-program task IDs according to their descending processing load levels within a given program, wherein, among at least a subset of the processing stages, each processing stage of said subset hosts one of the tasks of each of the set programs so as to equalize sums of said task IDs of the tasks located on each of the processing stages of said subset.

A further aspect of the invention provides hardware logic system for connecting input data to instances of a set of programs hosted on a manycore processor having an array of processing cores. Such a system comprises: 1) demultiplexing logic for connecting input data packets from a set of input data ports to destination program instance specific input port buffers based on a destination program instance identified for each given input data packet, and 2) multiplexing logic for connecting data packets from said program instance specific buffers to the array of cores based on identifications, for each given core of the array, of a program instance assigned for execution at the given core at any given time. An embodiment of the system further comprises a hardware logic controller that periodically assigns, at least in part based on volumes of input data packets at the program instance specific input port buffers, instances of the programs for execution on the array of cores, and accord-

ingly forms, for the multiplexing logic, the identification of the program instance that is assigned for execution at each core of the array of cores.

Yet further aspect of the invention provides a method for connecting input data to instances of a set of programs 5 hosted on a manycore processor having an array of processing cores. Such a method comprises: 1) demultiplexing input data packets from a set of input data ports to destination program instance specific input port buffers according to a destination program instance identified for each given input 10 data packet, and 2) multiplexing data packets from said program instance specific buffers to the array of cores according to identifications, for each given core of the array, of a program instance assigned for execution at the given core at any given time. In a particular embodiment of the 15 method comprise a further step as follows: periodically forming the identifications of the program instances executing at the array of cores through i) allocating the array of cores among the set of programs at least in part based on volumes of input data packets at the input port buffers 20 associated with individual programs of the set and ii) assigning, based at least in part based on said allocating, the cores of the array for executing specific instances of the programs. Moreover, in an embodiment, the above method is implemented by hardware logic that operates without 25 software involvement.

A yet further aspect of the invention provides a method for periodically arranging a set of executables of a given software program in an execution priority order, with an executable referring to a task, an instance, an instance of a task of 30 the program, or equals thereof. Such a method comprises: 1) buffering input data at an array of executable specific input port buffers, wherein a buffer within said array buffers, from an input port associated with the buffer, such data that arrived that is directed to the executable associated with the 35 buffer, 2) calculating numbers of non-empty buffers associated with each of the executables, and 3) ranking the executables in their descending execution priority order at least in part according to their descending order in terms numbers of non-empty buffers associated with each given 40 executable. In a particular embodiment of this method, the step of ranking involves I) forming, for each given executable, a 1<sup>st</sup> phase bit vector having as many bits as there are input ports from where the buffers receive their input data, with this number of ports denoted with X, and wherein a bit 45 at index x of said vector indicates whether the given executable has exactly x non-empty buffers, with x being an integer between 0 and X, II) forming, from bits at equal index values of the 1<sup>st</sup> phase bit vectors of each of the executables, a row of X  $2^{nd}$  phase bit vectors, where a bit at index y of the  $2^{nd}$  50 phase bit vector at index x of said row indicates whether an executable with ID number y within the set has exactly x non-empty buffers, wherein y is an integer from 0 to a maximum number of the executables less 1, as well as III) the following substeps: i) resetting the present priority order 55 index to a value representing a greatest execution priority; and ii) until either all bits of each of the  $2^{nd}$  phase bit vectors are scanned or an executable is associated with the lowest available execution priority, scanning the row of the  $2^{nd}$ phase bit vectors for active-state bits, one  $2^{nd}$  phase bit 60 vector at a time, starting from row index X while decrementing the row index after reaching bit index 0 of any given  $2^{nd}$  phase bit vector, and based upon encountering an active-state bit: i) associating the executable with ID equal to the index of the active-state bit within its  $2^{nd}$  phase bit 65 vector with the present priority order index and ii) changing the present priority order index to a next lower level of

6

execution priority. Moreover, in an embodiment, the above method is implemented by hardware logic that operates without software involvement.

#### BRIEF DESCRIPTION OF THE DRAWINGS

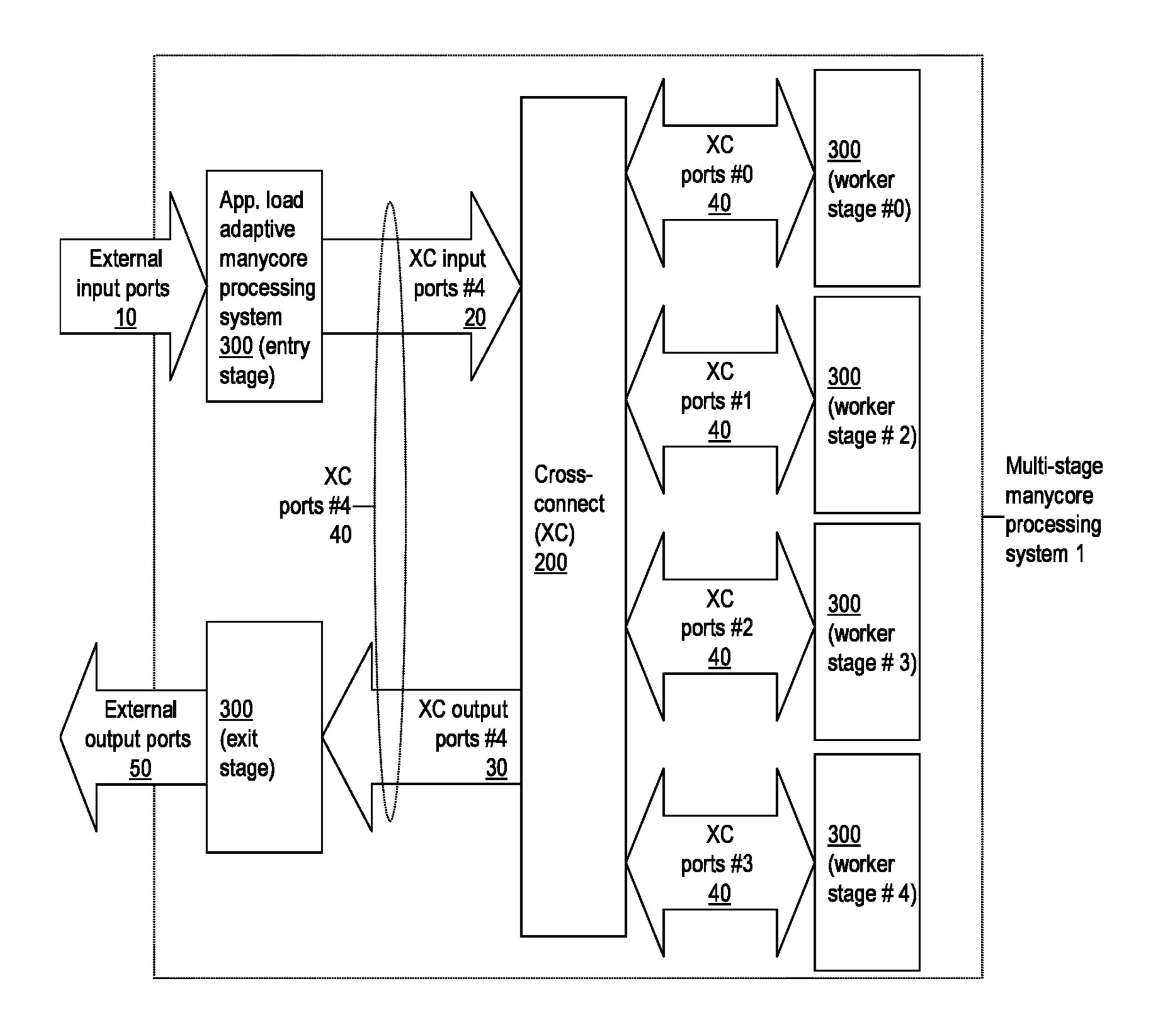

FIG. 1 shows, in accordance with an embodiment of the invention, a functional block diagram for multi-stage many-core processor system.

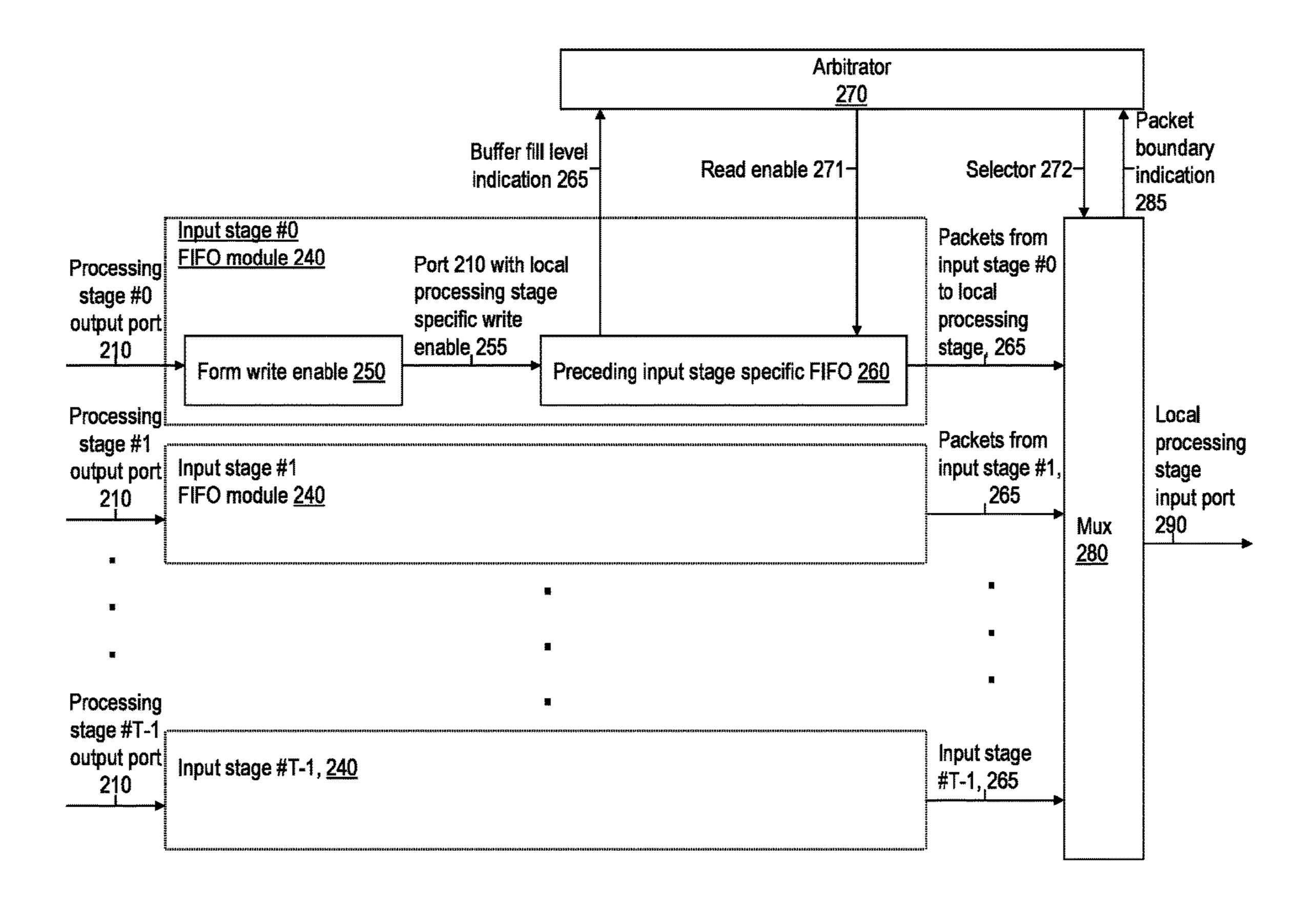

FIG. 2 shows, in accordance with an embodiment of the invention, a functional block diagram for a cross-connect at the multi-stage manycore processor system of FIG. 1.

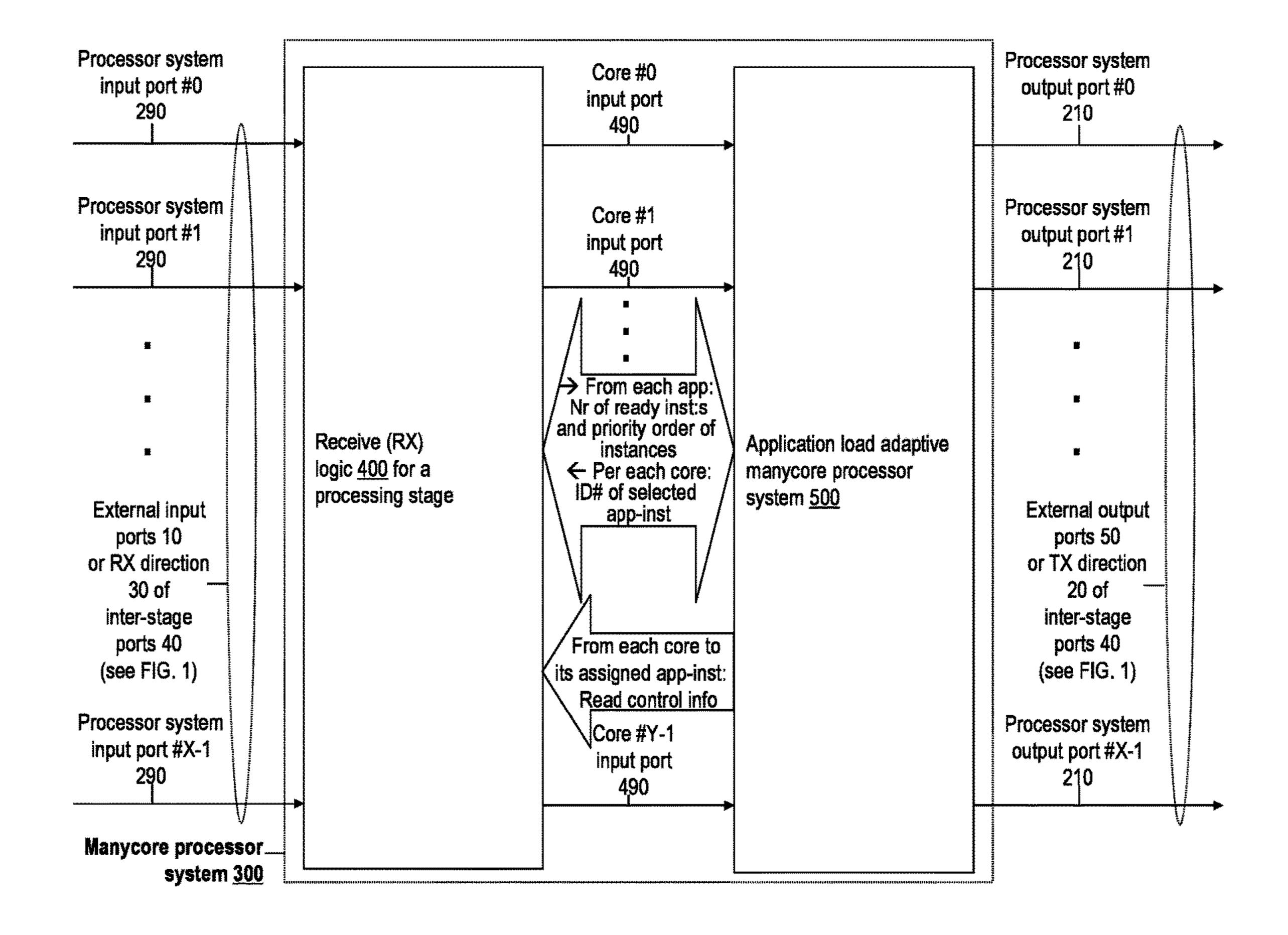

FIG. 3 shows, in accordance with an embodiment of the invention, a high-level functional block diagram for any of the manycore processor systems in the multi-stage processor system in FIG. 1.

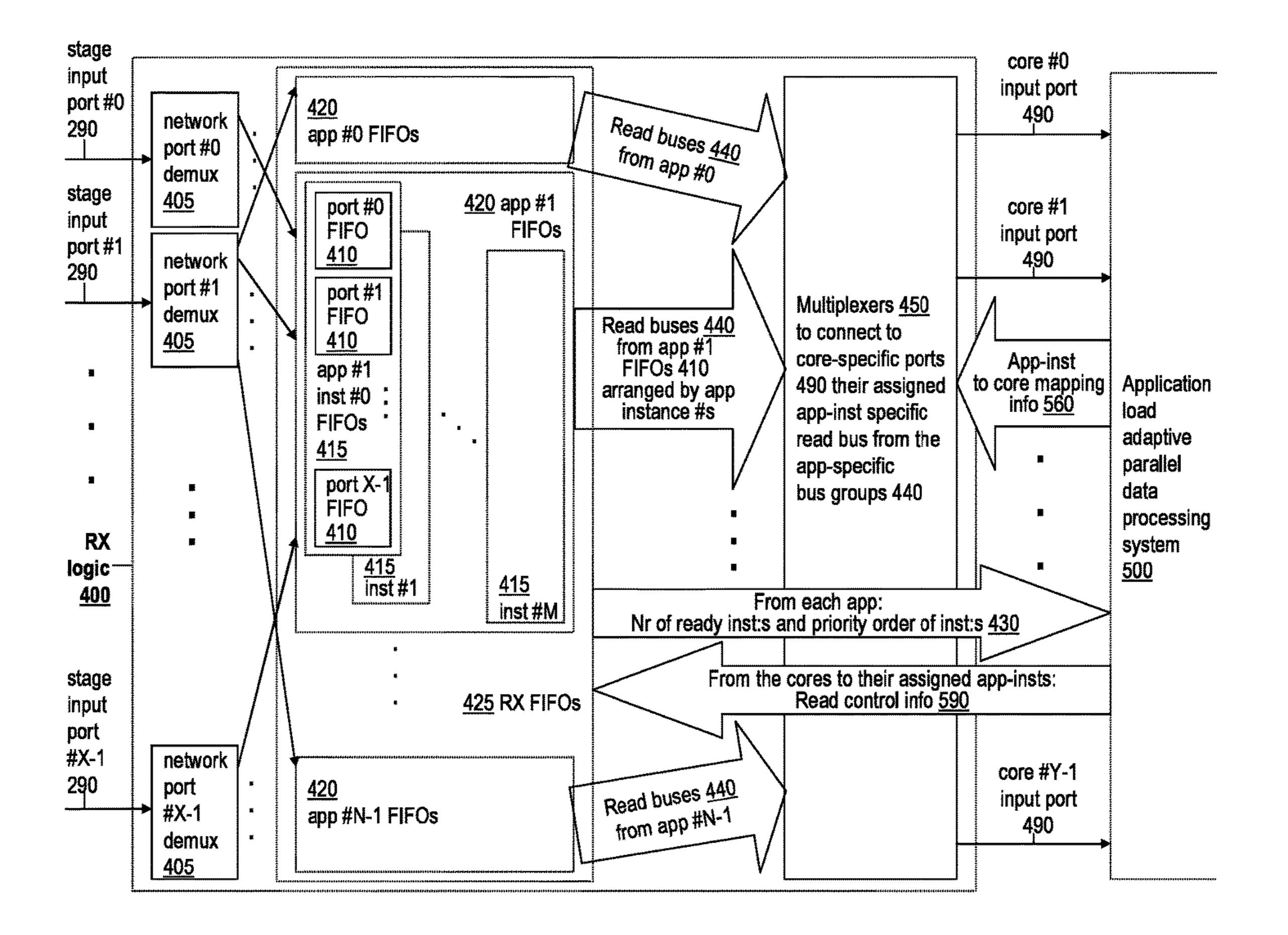

FIG. 4 shows, in accordance with an embodiment of the invention, a functional block diagram for the input data receive logic subsystem for the manycore processor system per FIG. 3.

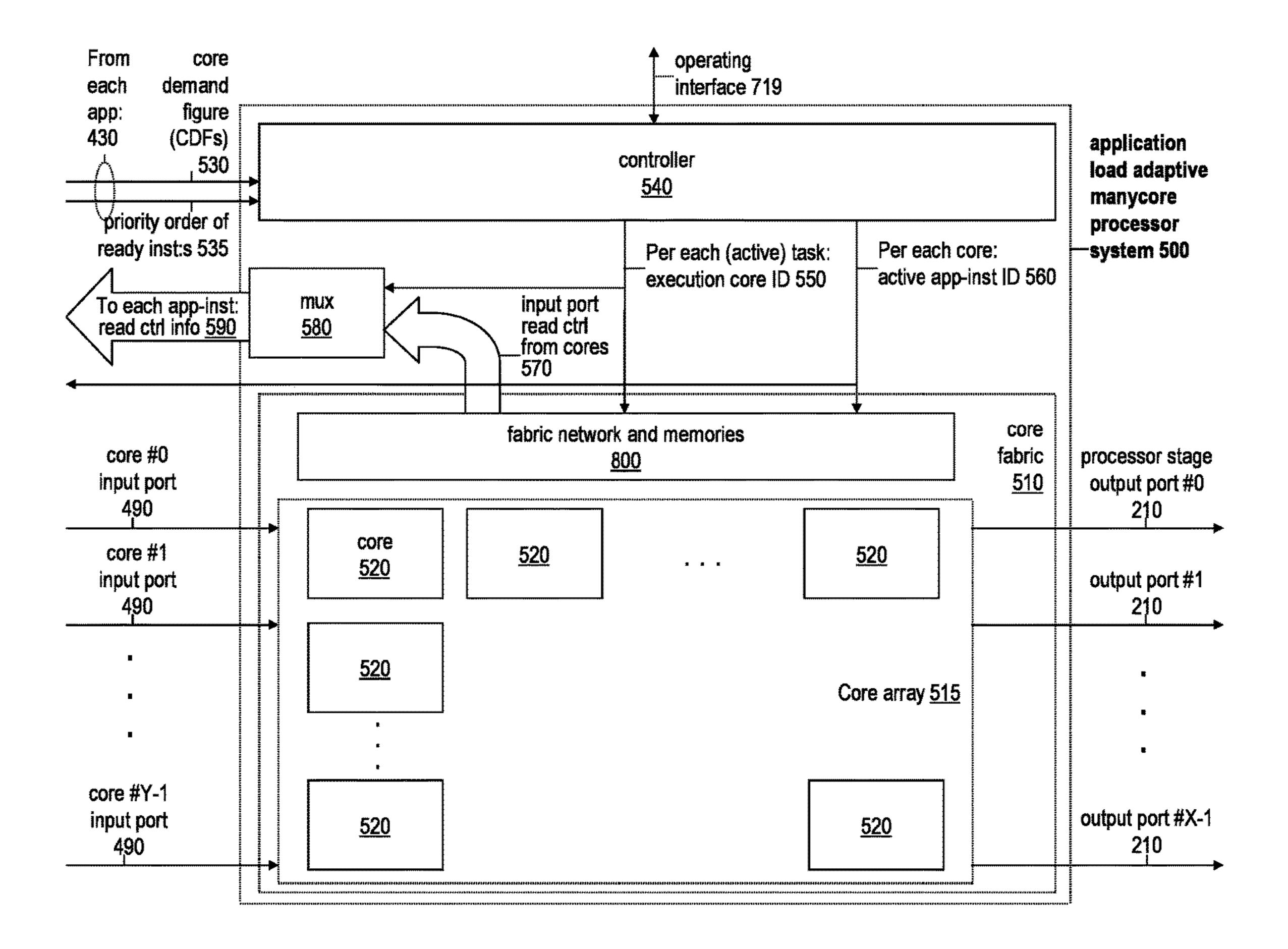

FIG. 5 shows, in accordance with an embodiment of the invention, a functional block diagram for the application load adaptive parallel data processing subsystem for a given manycore processing system of FIG. 3 within the multistage processor system in FIG. 1.

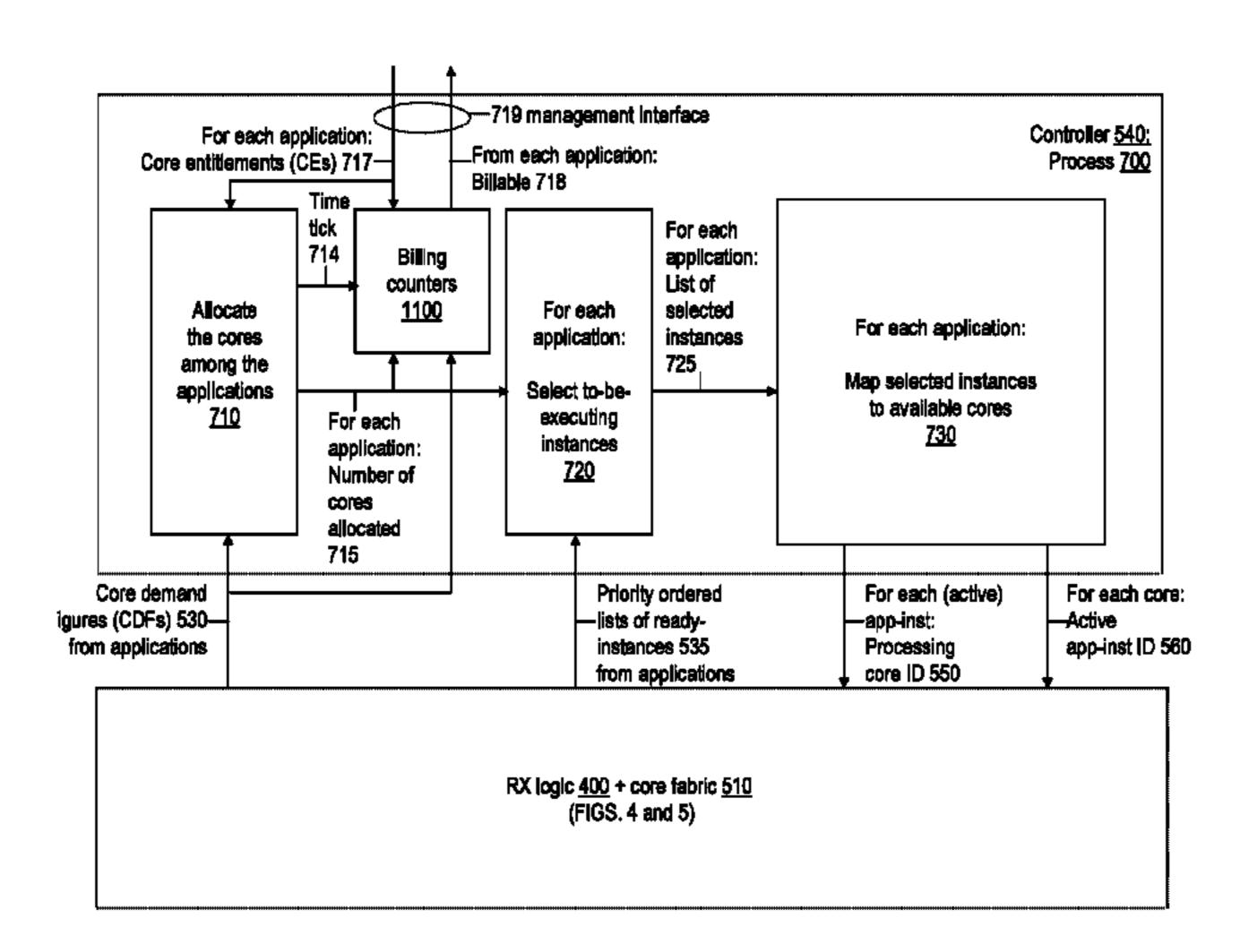

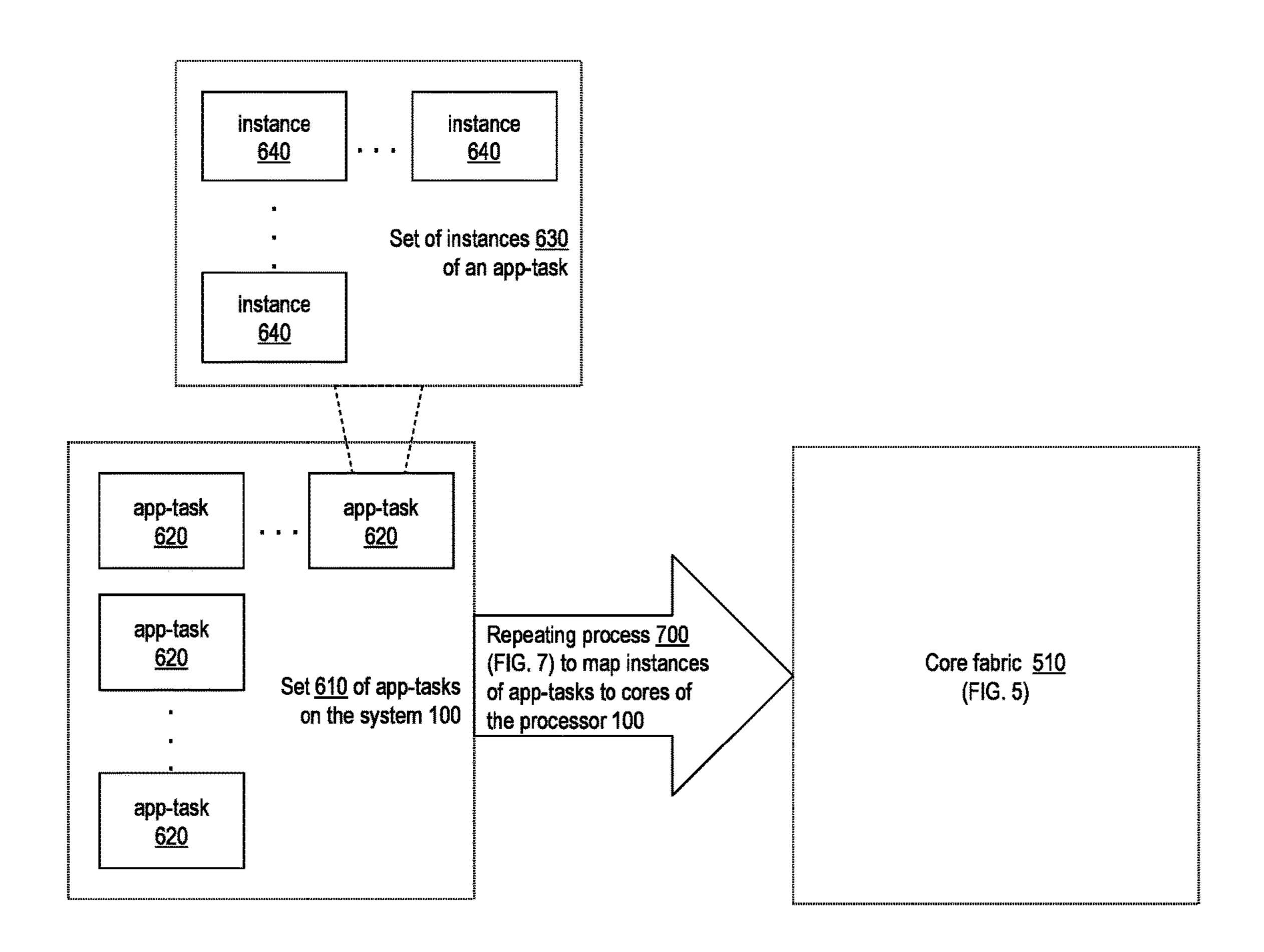

FIG. 6 illustrates, in accordance with an embodiment of the invention, a context diagram for the process of mapping (incl. selecting and placing) instances of the locally hosted application tasks to execute on the processing cores of the application load adaptive parallel data processing system per FIG. 5.

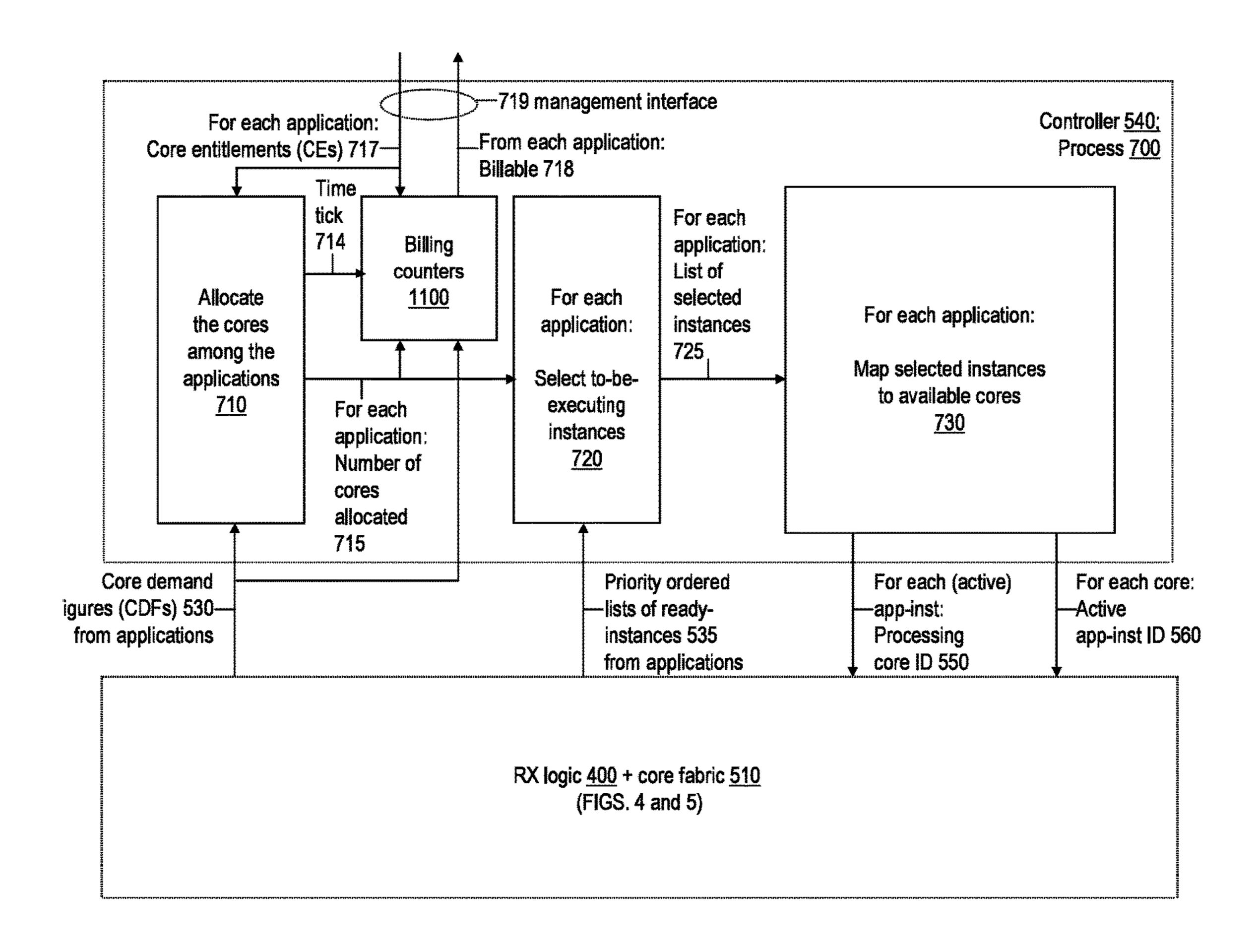

FIG. 7 illustrates, in accordance with an aspect of the invention, a flow diagram and major steps for the process per FIG. 6.

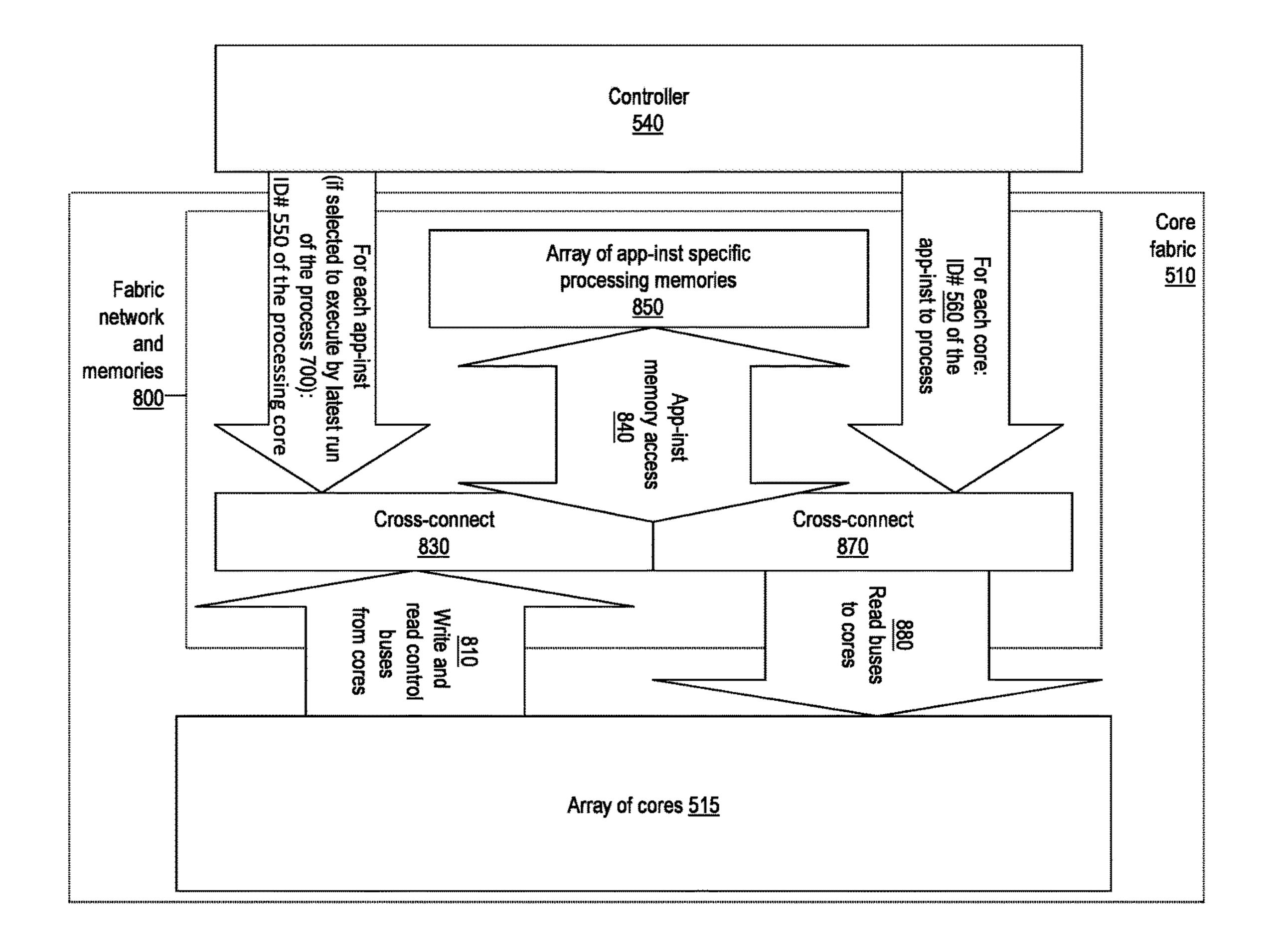

FIG. 8 illustrates, in accordance with an embodiment of the invention, a memory access architecture for the multicore fabric of the data processing system per FIG. 5.

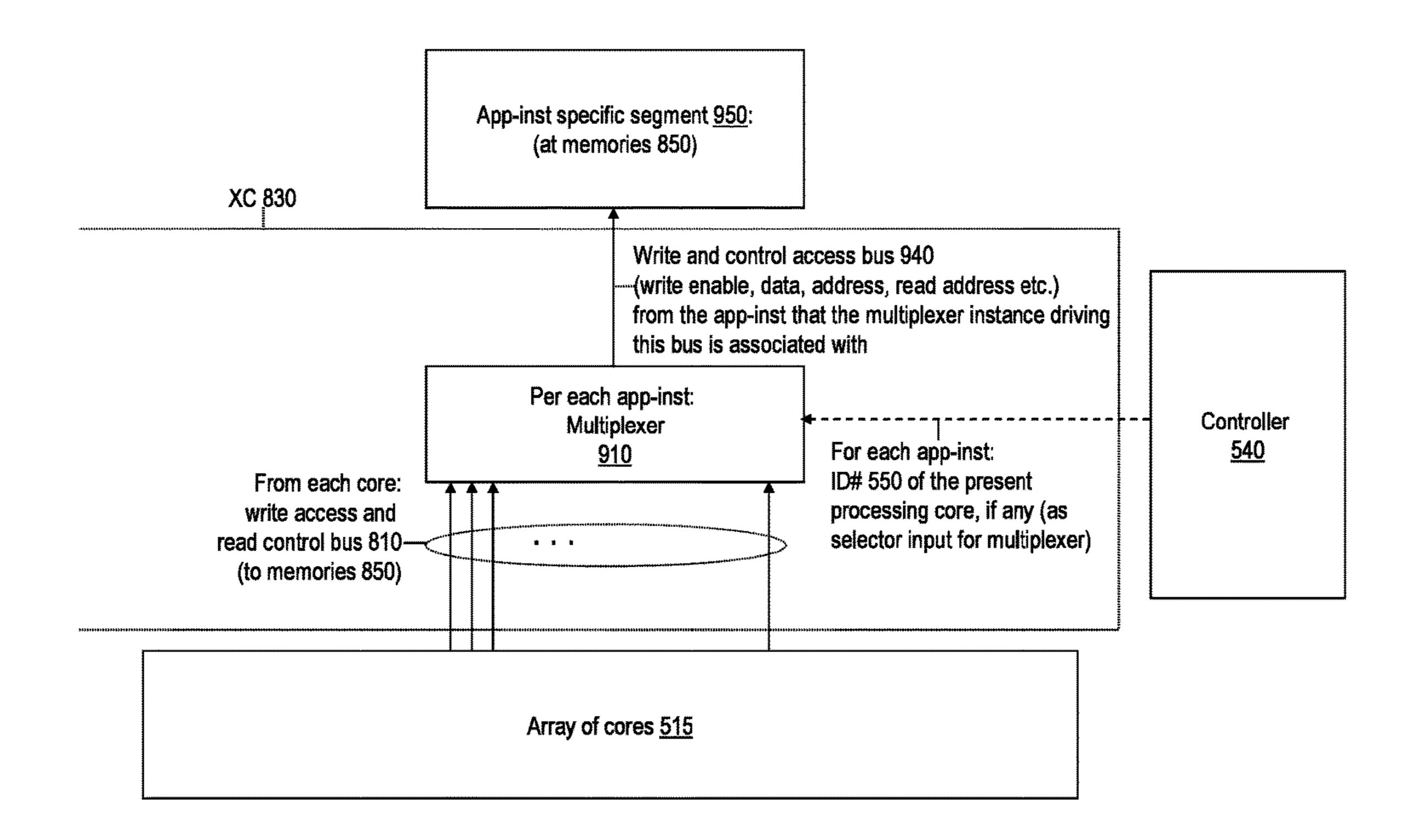

FIG. 9 shows, in accordance with an embodiment of the invention, at more detail level a portion of an embodiment of a logic system per FIG. 8 concerning write access from the cores of the fabric to the application instance (app-inst) specific fabric memory segments.

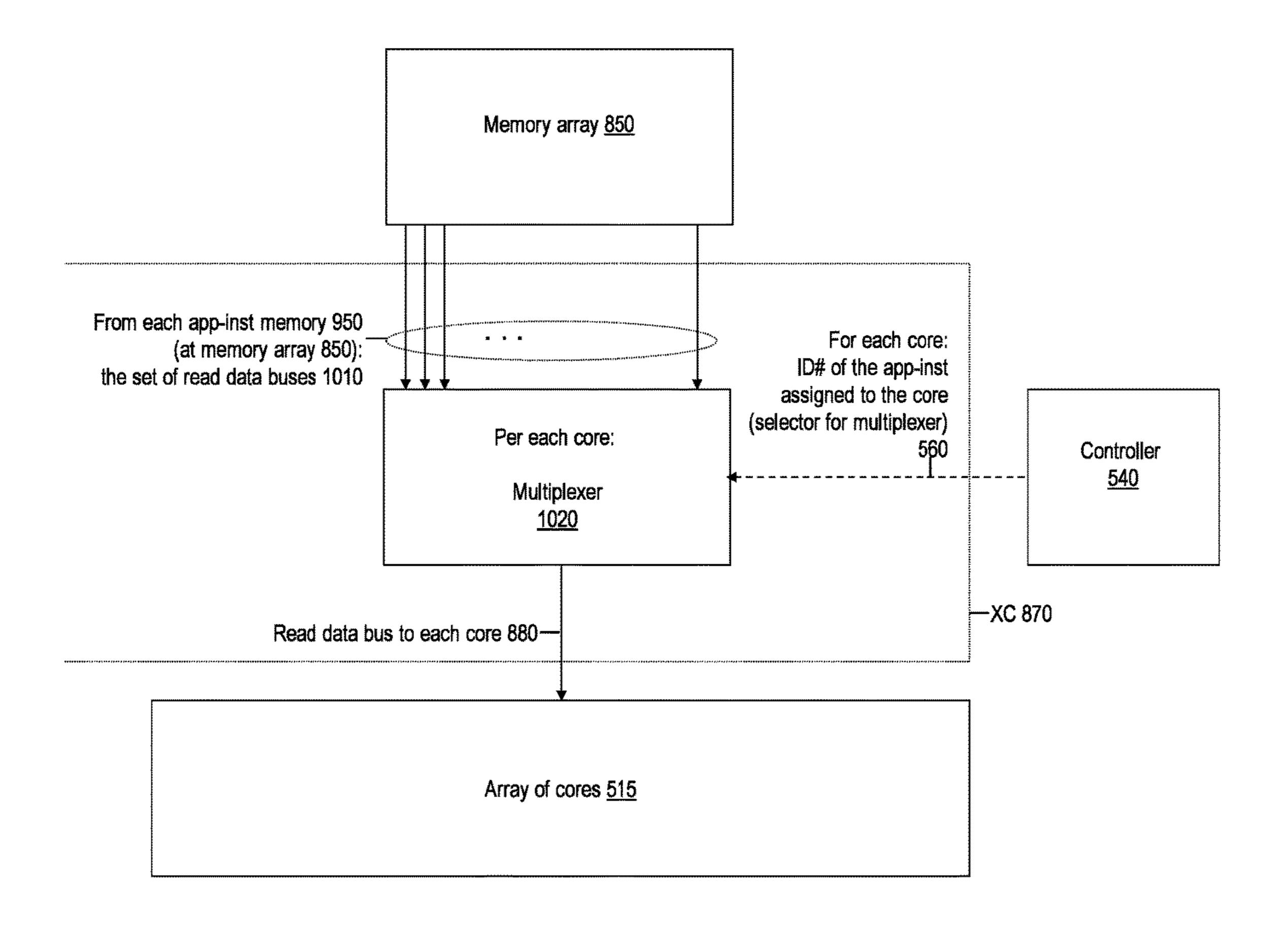

FIG. 10 shows, in accordance with an embodiment of the invention, at more detail level an embodiment of a portion of a logic system per FIG. 8 concerning read access by processing cores within the fabric to the app-inst specific fabric memory segments.

# DETAILED DESCRIPTION

General notes about this specification (incl. text in the drawings):

For brevity: 'application (program)' is occasionally written in as 'app', 'instance' as 'inst' and 'application-task/instance' as 'app-task/inst'

Receive (RX) direction is toward the cores of the manycore processor of a given processing stage, and transmit (TX) direction is outward from the cores.

The term IO refers both to the system 1 (FIG. 1) external input and output ports as well as ports interconnecting the processing stages 300 of the system.

Ports, such as external or inter-stage ports of the multistage parallel processing system 1 (FIG. 1) can be implemented either as distinct physical ports or as e.g. time or frequency division channels on shared physical connections.

Terms software program, application program, application and program are used interchangeably in this specification, and each generally refer to any type of computer software able to run on data processing systems based on the architecture.

Term 'task' in this specification refers to a part of a program, and covers the meanings of related terms such as actor, thread etc.

References to a "set of" units of a given type, such as programs, logic modules or memory segments can, depending on the nature of a particular embodiment or operating scenario, refer to any positive number of such units.

While the term 'processor' more specifically refers to the processing core fabric 510 (FIG. 5), it will also be used, where it streamlines the text, to refer to a processor system 500 (FIGS. 3-4) and a processing stage 300 (FIGS. 1 and 3) within the system 1.

Typically, there will be one task type per an application 20 hosted per each of the processing stages 300 in the system 1 per FIG. 1 (while the system 1 supports multiple processing stages and multiple application programs per each stage).

A master type task of a single application-instance (appinst) hosted at entry stage processing system can have multiple parallel worker type tasks of same type hosted at multiple worker stage processing systems. Generally, a single upstream app-inst-task can feed data units to be processed in parallel by multiple downstream app-inst- 30 task:s within the same system 1.

Identifiers such as 'master' and 'worker' tasks or processing stages are not used here in a sense to restrict the nature of such tasks or processing; these identifiers are here used primarily to illustrate a possible, basic type of 35 distribution of workloads among different actors. For instance, the entry stage processing system may host, for a given application, simply tasks that pre-process (e.g. qualify, filter, classify, format, etc.) the RX data units and pass them to the worker stage processing 40 systems as tagged with the pre-processing notations, while the worker stage processor systems may host the actual master (as well as worker) actors conducting the main data processing called for by such received data units. Generally, a key idea of the presented processing 45 system and IO architecture is that the worker stages of processing—where bulk of the intra-application parallel and/or pipelined processing typically is to occur, providing the performance gain of using parallel task instances and/or pipelined tasks to lower the processing 50 latency and improve the on-time IO throughput receive their input data units as directed to specific destination app-task instances, while the external parties are allowed to communicate with a given application program hosted on a system 1 through a single, 55 constant contact point (the 'master' task hosted on the entry stage processor, possibly with its specified instance).

Specifications below assume there to be X IO ports, Y core slots on a processor **500**, M application programs 60 configured and up to N instances per each application for a processor **500**, and up to T tasks (or processing stages) per a given application (instance), wherein the capacity parameters X, Y, M, N and T are some positive integers, and wherein the individual ports, cores, applications, tasks and instances, are identified with their ID#s ranging from 0 to said capacity parameter value

8

less 1 for each of the measures (ports, cores, apps, instances, tasks or processing stages).

The invention is described herein in further detail by illustrating the novel concepts in reference to the drawings. General symbols and notations used in the drawings:

Boxes indicate a functional digital logic module; unless otherwise specified for a particular embodiment, such modules may comprise both software and hardware logic functionality.

Arrows indicate a digital signal flow. A signal flow may comprise one or more parallel bit wires. The direction of an arrow indicates the direction of primary flow of information associated with it with regards to discussion of the system functionality herein, but does not preclude information flow also in the opposite direction.

A dotted line marks a border of a group of drawn elements that form a logical entity with internal hierarchy, such as the modules constituting the multi-core processing fabric 110 in FIG. 1.

Lines or arrows crossing in the drawings are decoupled unless otherwise marked.

For clarity of the drawings, generally present signals for typical digital logic operation, such as clock signals, or enable, address and data bit components of write or read access buses, are not shown in the drawings.

FIGS. 1-10 and related descriptions below provide specifications for embodiments and aspects of an extensible, multi-stage, application program load and type adaptive, multi-stage parallel data processing system, including for the input and output (IO) subsystems thereof.

FIG. 1 illustrates, according to an embodiment of the invention, a multi-stage manycore processor system architecture, comprising a set of application processing load adaptive manycore processing stages interconnected by a packet destination app-task-inst controlled cross connect. The discussion in the following details an illustrative example embodiment of this aspect of the invention. Note that the number of processing stages 300 and XC ports 40 shown is just for a purpose of one possible example; various implementations may have any practical number of such stages and ports.

General operation of the application load adaptive, multistage parallel data processing system 1 per FIG. 1, focusing on the main IO data flows, is as follows: The system 1 provides data processing services to be used by external parties (e.g. client portions of programs whose server portions run on the system 1) over networks. The system 1 receives data units (e.g. messages, requests, data packets or streams to be processed) from its users through its RX network ports 10, and transmits the processing results to the relevant parties through its TX network ports 50. Naturally the network ports of the system of FIG. 1 can be used also for connecting with other (intermediate) resources and services (e.g. storage, data bases etc.) as and if necessary for the system to produce the requested processing results to the relevant external parties. The application program tasks executing on the entry stage manycore processor 300 are typically of 'master' type for parallelized applications, i.e., they manage and distribute the processing workloads for 'worker' type tasks running on the worker stage manycore processing systems 300 (note that the processor system 300 hardware implementations are similar for all instances of the processing system 300). The instances of master tasks typically do preliminary processing (e.g. message/request classification, data organization) and workflow management based on given input packet(s), and then typically involve

appropriate worker tasks at their worker stage processors (see FIG. 1 for context) to perform the data processing called for by the given input packet(s), potentially in the context of and in connection with other related input packets and/or other data elements (e.g. in memory or storage resources 5 accessible by the system 1) referred to by such input packets. (Note that processors 300 can also have access to the system memories through interfaces additional to the IO ports shown in the FIGS.) Accordingly, the master tasks typically pass on the received data units (using direct connection 10 techniques to allow most of the data volumes being transferred to bypass the actual processor cores) through the XC 200 to the worker stage processors, with the destination app-task instance identified for each data unit. As a security feature, to provide isolation among the different applications 1 **620** (FIG. 6) configured to run on the processors **300** of the system 1, by default the hardware controller 540 (FIGS. 5 and 7) of each processor 300, rather than any application software (executing at a given processor 300), inserts the application ID# bits for the data packets passed to the XC 20 **200**. That way, the tasks of any given application running on the processing stages 300 in a system 1 can trust that the packets they received from the XC 200 are from its own application. Note that the controller **540** determines, and therefore knows, the application ID# that each given core 25 within its processor 500 is assigned to at any given time, via the app-inst to core mapping info 560 that the controller produces (FIGS. 4, 5 and 7). Therefore the controller 540 is able to insert the presently-assigned app ID# bits for the inter-task data units being sent from the cores of its pro- 30 cessing stage 300 over the core-specific output ports 20, 210 (FIG. 3) to the XC 200.

While the processing of any given application (server program) at a system 1 is normally parallelized and/or pipelined, and involves multiple tasks (many of which tasks 35 and instances thereof can execute simultaneously on the manycore arrays of the processors 300), the system enables external parties to communicate with any such application hosted on the system 1 without having to know about any specifics (incl. existence, status, location) of their internal 40 tasks or parallel instances thereof. As such, the incoming data units to the system 1 are expected to identify just their destination application (and where it matters, the application instance number), rather than any particular task within it. Moreover, the system enables external parties to communi- 45 cate with any given application hosted on a system 1 through any of the network ports 10, 50 without knowing whether or at which cores any instance of the given application task (app-task) may be executing at any time. Furthermore, the architecture enables the aforesaid flexibility and efficiency 50 through its hardware logic functionality, so that no system or application software running on the system 1 needs to either be aware of whether or where any of the instances of any of the app-tasks may be executing at any given time, or through which port any given inter-task or external communication 55 may have occurred or be occurring. Thus the system 1, while providing a highly dynamic, application workload adaptive usage of the system processing and communications resources, allows the software running on and/or remotely using the system to be designed with a straightforward, 60 abstracted view of the system: the software (both the server programs hosted on a system 1 as well as clients etc. remote agents interacting with such programs hosted on the system) can assume that all applications (as well all their tasks and instances thereof) hosted on by the given system 1 are 65 always executing on their virtual dedicated processor cores within the system. Also, where useful, said virtual dedicated

**10**

processors can also be considered by software to be timeshare slices on a single (very high speed) processor. The architecture thereby enables achieving, at the same time, both the vital application software development productivity (simple, virtual static view of the actually highly dynamic processing hardware) together with high program runtime performance (scalable parallel program execution with minimized overhead) and resource efficiency (adaptively optimized resource allocation) benefits. Techniques enabling such benefits of the architecture are described in the following through more detailed technical study of the system 1 and its sub systems.

In FIG. 1, the processing stage 300 specific XC IO ports 40 contain one input and output port per a processing core at any given stage, with such individual IO ports of any given stage identified as ports  $\#0, 1, \ldots, Y-1$  (noting that the input ports of any given processing stage are not tied to or associated with any particular core, but instead, input data units can be connected from all input ports to all cores of any given processing stage as needed). The XC 200 provides data unit (referred to as packet) level switched, restrictionfree, any-to-any connectivity among the mentioned processing stage IO ports of the same port index #y (y=0, 1, . . . Y-1): E.g. the XC provides packet-switched connectivity to input ports #5 of each stage 300 from the output ports #5 of each stage 300 of the system 1 (assuming Y is greater than 5). This cross-connectivity is implemented through data source specific buffering and load-weigh prioritized fair muxing of packets to the XC output ports (i.e. to processing stage 300 input ports 30). An embodiment of a microarchitecture for such XC output port logic is as illustrated in FIG. **2**.

FIG. 2 presents, according to an embodiment of the invention, a functional block diagram for forming at the XC 200 a given input port 290 (see FIG. 3) to a given processor 300 of FIG. 1. The discussion in the following details an illustrative example embodiment of this aspect of the invention.

The XC 200 subsystems per FIG. 2 provide data connectivity to a given input port #y (y=0, 1, ... Y-1) from output ports #y of each of the processing systems 300 of the system 1, and there is a subsystem per FIG. 2 for each input port 290 to each processing system 300. Note that the XC 200 is formed by providing the processing stage input port 290 specific subsystem per FIG. 2 for each input port of each of the processing stages 300 interconnected by the XC 200. At each a subsystem per FIG. 2, there are first-in first-out buffers (FIFOs) **260** per each preceding processing stage of the input packets, in which FIFOs packets whose identified next processing app-task ID matches the processing stage to which the XC output in question connects to (referred to as the local processing stage in FIG. 2) are queued, plus an arbitration logic module 270 for selecting, at times when a new packet is to be sent over the local XC output port 290, an appropriate input-stage specific FIFO 260 from which to send the next packet to the local processing stage. The next input-stage specific FIFO is chosen by the arbitrator 270 by running a round-robin selection algorithm first among those input-stage specific FIFOs whose fill level is indicated 265 as being above a defined threshold, and in the absence of such FIFOs, running a plain round robin algorithm across all the FIFOs for the given XC output port. For the FIFO module 260 selected by the arbitrator at any given time, the arbitrator activates the read enable signal 271. The arbitrator also controls the mux (mux) 280 to connect to its output 290 the packet output **265** from the FIFO module **240** selected at the time.

Note that in FIG. 2, there are submodules 250 and 260 associated with the input data streams from each of the preceding processing stages #0, 1, . . . T-1 similar to those drawn in more detail for the stage #0. Though not included in FIG. 2, similar signals (fill level indication 265 and read enable 271) exist between each of the preceding processing stage specific FIFO modules 240 and the arbitrator 270, as is shown between the module specific to preceding stage #0 and the arbitrator.

Moreover, the set of applications 610 (FIG. 6) configured to run on the system 1 have their tasks identified by (intra-application) IDs according to their descending order of relative (time-averaged) workload levels. The sum of the intra-application task IDs (each representing the workload ranking of its tasks within its application) of the app-tasks hosted at any given processing system 300 is equalized by appropriately configuring the tasks of differing ID#s (i.e. of differing workload levels) across the applications for each processing system 300, to achieve optimal overall load balancing. For instance, in case of four processing stages 300 (as shown in the example of FIG. 1), if the system is shared among four applications and each of that set of applications has four tasks, for each application of that set, the busiest task (i.e. the worker task most often called for or otherwise causing the heaviest processing load among the tasks of the app) is given ID#0, the second busiest task ID#1, the third busiest ID#2, and the fourth ID #3. To balance the processing loads across the applications among the worker stage processors 300 of the system 1, the worker stage processor #t gets task ID#t+m (rolling over at 3 to 0) of the application ID #m (t=0, 1, . . . T-1; m=0, 1, . . . M-1). In this example scenario of four application streams, four worker tasks per app as well as four processors 300 in a system 1, the above scheme causes the task IDs of the set of apps to be placed at the processing stages per the table below 35 (t and m have the meaning per the previous sentence):

| App ID # m (to right) => Stage # t (below) | 0 | 1 | 2 | 3 |  |

|--------------------------------------------|---|---|---|---|--|

| 0                                          | 0 | 1 | 2 | 3 |  |

| 1                                          | 1 | 2 | 3 | 0 |  |

| 2                                          | 2 | 3 | 0 | 1 |  |

| 3                                          | 3 | 0 | 1 | 2 |  |

As seen in the example of the table above, the sum of the task ID#s (with each task ID# representing the workload ranking of its task within its application) is the same for any 50 row i.e. for each of the four processing stages of this example. Applying this load balancing scheme for differing numbers of processing stages, tasks and applications is straightforward based on the above example and the discussion herein. In such system wide processing load balancing 55 schemes supported by system 1, a key idea is that each worker stage processor 300 gets one of the tasks from each of the applications so that collectively the tasks configured for any given worker stage processor 500 have the intra-app task IDs of the full range from ID#0 through ID#T-1 with 60 one task of each ID# value (wherein the intra-app task ID#s are assigned for each app according to their descending busyness level) so that the overall task processing load is to be, as much as possible, equal across all worker-stage processors 300 of the system 1. Advantages of these 65 schemes supported by systems 1 include achieving optimal utilization efficiency of the processing resources and elimi12

nating or at least minimizing the possibility or effects of any of the worker-stage processors 300 forming system wide performance bottlenecks. In FIG. 2, each of the logic modules 250 for forming write enable signal performs the algorithm per above, thus selecting which packets (based on their destination app-task ID#) to pass to its local FIFO 260 from its associated preceding processing stage.

In the following, we continue by exploring the internal structure and operation of a given processing stage 300, a high level functional block diagram for which is shown in FIG. 3.

FIG. 3, presents, according to an embodiment of the invention, a top level functional block diagram for any of the manycore processing systems 300 in the multi-stage parallel processing system in FIG. 1, involving a RX logic subsystem and manycore processor subsystem. The discussion in the following details an illustrative example embodiment of this aspect of the invention.

As illustrated in FIG. 3, any of the processing systems 300 20 of system 1 (FIG. 1) has, besides manycore processor system 500 (detailed in FIGS. 5-10), an RX logic subsystem 400, which connects input data units (packets) from any of the input ports 290 to any of the processing cores of the manycore processor 500, according at which core their indicated destination app-task-instance may be executing at any given time. Moreover, the monitoring of the buffered input data load levels per their destination app-task instances at the RX logic subsystem 400 allows optimizing the allocation of processing core capacity of the local manycore processor 500 among the application tasks hosted on the given processing system 300. The structure and operation of an embodiment of the RX logic subsystem 400 for the manycore processing system per FIG. 3 is detailed below in connection with FIG. 4.

FIG. 4 illustrates, according to an embodiment of the invention, main data flows of the RX logic subsystem 400, which connects input packets from any of the input ports 290 to any of the processing cores of the processor system 500, according to at which core the destination app-task instance indicated for any given input may be executing at any given time. The discussion below details an illustrative example embodiment of this aspect of the invention.

The RX logic connecting the input packets from the input ports 290 to the local processing cores arranges the data from all the input ports 290 according to their indicated destination applications and then provides for each core of the manycore processor 500 read access to the input packets for the app-task instance executing on the given core at any given time. At this point, it shall be recalled that there is one app-task hosted per processing stage 500 per each of the applications 610 (FIG. 6), while there can be up to Y instances in parallel for any given app-task. Since there is one app-task per app per processing stage, the term app-inst in the following, including in and in connection to FIGS. 4-11, means an instance of an application task hosted at the processing stage under study.

The main operation of the RX logic shown in FIG. 4 is as follows: First input packets arriving over the network input ports 290 are grouped to a set of destination application specific FIFO modules 420, whose fill levels (in part) drives the allocation and assignment of cores at the local manycore processor 500 among instances of the app-tasks hosted on that processor, in order to maximize the total (value-add, e.g. revenue, of the) data processing throughput across all the application programs configured for the manycore processor system. From the app-inst specific buffers 415 within the destination application buffer modules 420, the input pack-

ets are then connected **450** to specific cores of the processor **500** where their associated app-inst:s are executing at a given time (when the given app-inst is selected for execution). At greater level of detail, the data flow of the RX logic **400**, and its interactions with its local manycore processor **500**, are detailed in the following:

The input packets arriving over the input ports are demuxed by individual RX network port specific demultiplexers (demux:s) 405 to their indicated (via overhead bits) destination app-inst and input port specific FIFO buffers 10 410. At the RX subsystem 400, there will thus be FIFOs 410 specific to each input port 290 for each app-inst able to run on the manycore processor 500. In FIG. 4, the app-inst specific collections 415 and application-scope collections **420** of these FIFOs **410** is shown for the application ID #1 15 to keep the diagram reasonably simple; however similar arrangements exist for each of the applications IDs #0 through #N. Similarly, though FIG. 4 for clarity shows the connections from the input port #1 to the application FIFOs **425**, and connections from the input ports just to application 20 #1 FIFOs, these connections shall be understood to exist between each input port 290 and RX FIFO collection 420 of each application. A reason for these collections of input port specific buffers 410 for each app-inst is to allow writing all input packets directly, without delaying or blocking other 25 data flows, to a buffer, even when a given destination app-inst was receiving data from multiple, and up to all, of the input ports at the same time. Moreover, the app-inst level connection of packets between the processing stages 300 (enabled in part by the app-task-inst specific buffering 415) 30 also allows the system 1 to efficiently maintain continued data flows across the system specific to particular instances of application tasks originating or consuming a given sequence of data packets.