#### US010414519B1

# (12) United States Patent

Cameron et al.

## (10) Patent No.: US 10,414,519 B1

(45) **Date of Patent:** Sep. 17, 2019

# (54) SYSTEM AND METHOD FOR GENERATION OF DITHERED EXCITATION SIGNALS

- (71) Applicant: THE BOEING COMPANY, Chicago, IL (US)

- (72) Inventors: **Douglas C. Cameron**, Ladera Ranch, CA (US); **Dwayne C. Merna**, Yorba

Linda, CA (US); Manu Sharma, Long

Beach, CA (US)

(73) Assignee: The Boeing Company, Chicago, IL

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/934,124

(22) Filed: Mar. 23, 2018

(51) **Int. Cl.**

**B64G** 1/28 (2006.01) **G01C** 21/18 (2006.01) **G01C** 19/30 (2006.01)

(52) U.S. Cl.

(58) Field of Classification Search

CPC ...... B64G 1/288; B64G 1/286; G01C 21/18; G01C 19/30 USPC ..... 341/116, 155, 112 See application file for complete search history.

## (56) References Cited

### U.S. PATENT DOCUMENTS

| 4,151,570 A   | <b>*</b> 4/1979 | Ravizza G11B 5/588  |

|---------------|-----------------|---------------------|

|               |                 | 360/77.17           |

| 6,681,649 B2  |                 |                     |

| 9,774,809 B2  | <b>*</b> 9/2017 | Song H04N 5/3765    |

| 9,848,152 B1  | * 12/2017       | Lin H04N 5/378      |

| 10,132,661 B2 | * 11/2018       | Falabella G01C 9/02 |

<sup>\*</sup> cited by examiner

Primary Examiner — Brian K Young

(74) Attorney, Agent, or Firm — Toler Law Group, PC

#### (57) ABSTRACT

Dither circuitry includes harmonic signal generation circuitry configured generate a high order even harmonic of a base excitation signal. The dither circuitry also includes a combiner configured to generate a dithered excitation signal based on the high order even harmonic and the base excitation signal. The dither circuitry further includes an output terminal configured to output the dithered excitation signal to a sensor device.

#### 20 Claims, 41 Drawing Sheets

FIG. 3

828

Sep. 17, 2019

Sep. 17, 2019

Sep. 17, 2019

T G. 29

FIG. 38

# SYSTEM AND METHOD FOR GENERATION OF DITHERED EXCITATION SIGNALS

#### FIELD OF THE DISCLOSURE

The present disclosure is generally related to dithered excitation signals and gimbaled inertial measurement units.

#### **BACKGROUND**

A gimbaled inertial measurement unit is used for vehicle navigation and object tracking. The gimbaled inertial measurement unit includes multiple gimbals that each rotate along a single axis to position sensors along the vehicle's path. By using multiple gimbals, such as three or four gimbals, a vehicle's inertia can be monitored in multiple axes by the sensors and used for inertial navigation. Inertial navigation continuously calculates by dead reckoning the position, the orientation, and the velocity of a moving object without the need for external reference. Dead reckoning (or deductive reckoning) involves calculating the vehicle's current position by using a previously determined position and advancing that position based upon estimated speeds and headings.

Gimbaled inertial measurement units include additional sensors, such as resolvers, to determine a position of a motor that drives each of the multiple gimbals and positions the sensors that track the vehicle's inertia. A resolver is an analog sensor that is used to determine rotational position, 30 such as an angle. The resolver receives an excitation signal and generates analog output signals which are converted to digital samples. The digital samples are used to determine a position of the motor and the gimbal. The position outputs determined from the output analog signals may lose preci- 35 sion during the conversion from analog to digital or from processing the digital samples into the angle outputs. Additionally, interference from current switching during operating the gimbal motors can add noise and errors. Reduced precision and errors accumulate over time in inertial navi- 40 gation and can lead to incorrect data or navigation.

Complicated discrete solutions are often used to increase precision or bandwidth of the gimbaled inertial measurement units needed for mission or design requirements. However, these solutions do not generally provide increased 45 precision and increased bandwidth simultaneously. Additionally, these solutions add complexity, cost, weight, and volume to vehicle design. In the context of flying vehicles (aircraft, spacecraft, etc.), weight and volume greatly increase cost and reduce performance.

### SUMMARY

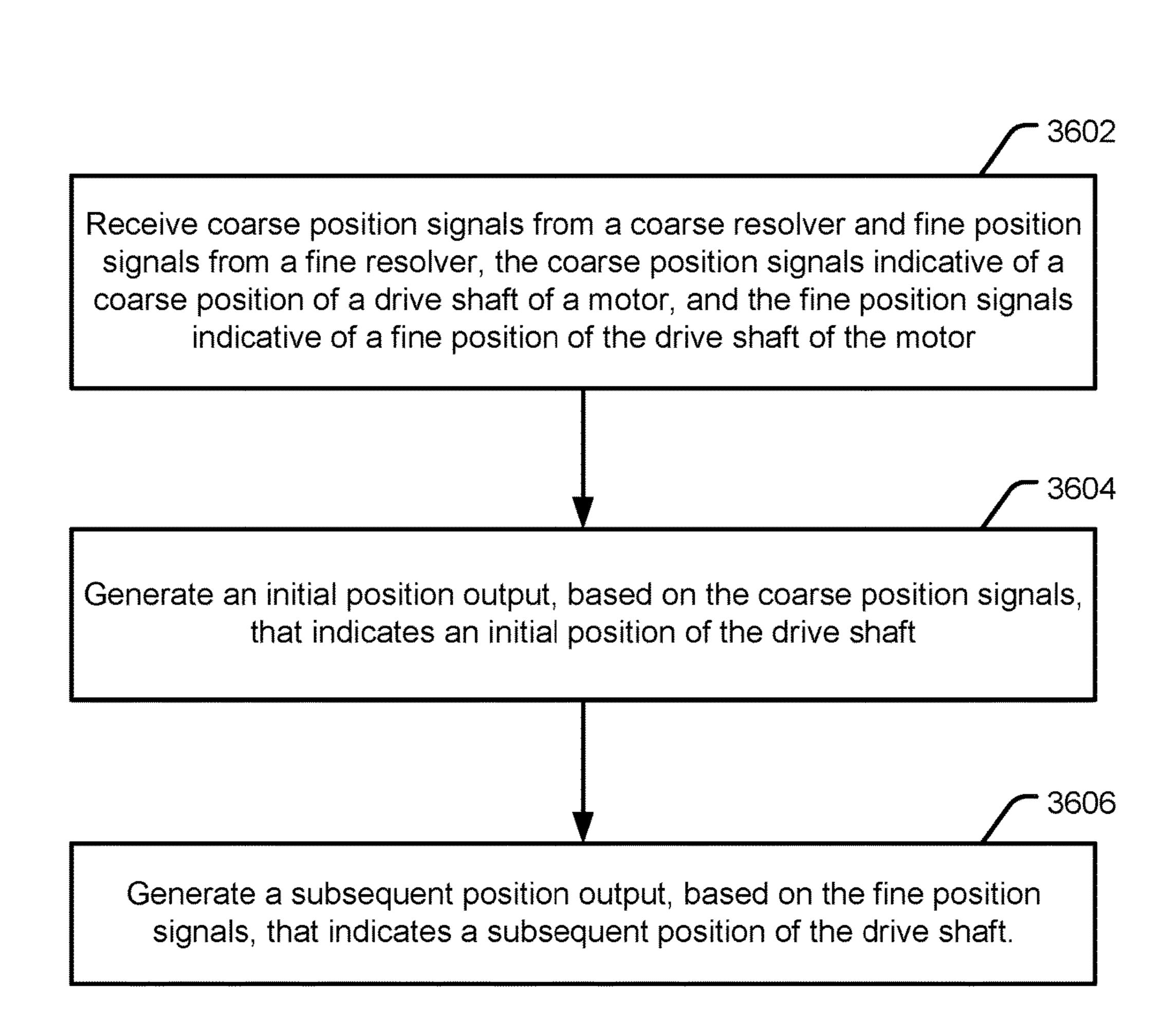

In a particular implementation, an apparatus includes a coarse resolver configured to output coarse position signals 55 indicative of a coarse position of a drive shaft of a motor. The apparatus also includes a fine resolver configured to output fine position signals indicative of a fine position of the drive shaft of the motor. The apparatus further includes a control circuit. The control circuit is configured to receive 60 the coarse position signals from the coarse resolver and the fine position signals from the fine resolver and generate an initial position output, based on the coarse position signals, that indicates an initial position of the drive shaft. The control circuit is further configured to generate a subsequent 65 position output, based on the fine position signals, that indicates a subsequent position of the drive shaft.

2

In another particular implementation, a method of determining rotational position includes receiving coarse position signals from a fine resolver. The coarse position signals are indicative of a coarse position of a drive shaft of a motor, and the fine position signals are indicative of a fine position of the drive shaft of the motor. The method also includes generating an initial position output, based on the coarse position signals, that indicates an initial position of the drive shaft. The method further includes generating a subsequent position output, based on the fine position signals, that indicates a subsequent position of the drive shaft.

In yet another particular implementation, a non-transitory computer readable medium stores instructions that, when executed by a processor, cause the processor to receive coarse position signals from a coarse resolver and fine position signals from a fine resolver. The coarse position signals are indicative of a coarse position of a drive shaft of a motor, and the fine position signals are indicative of a fine position of the drive shaft of the motor. The instructions further cause the processor to generate an initial position output, based on the coarse position signals, that indicates an initial position of the drive shaft and to generate a subsequent position output, based on the fine position signals, that indicates a subsequent position of the drive shaft.

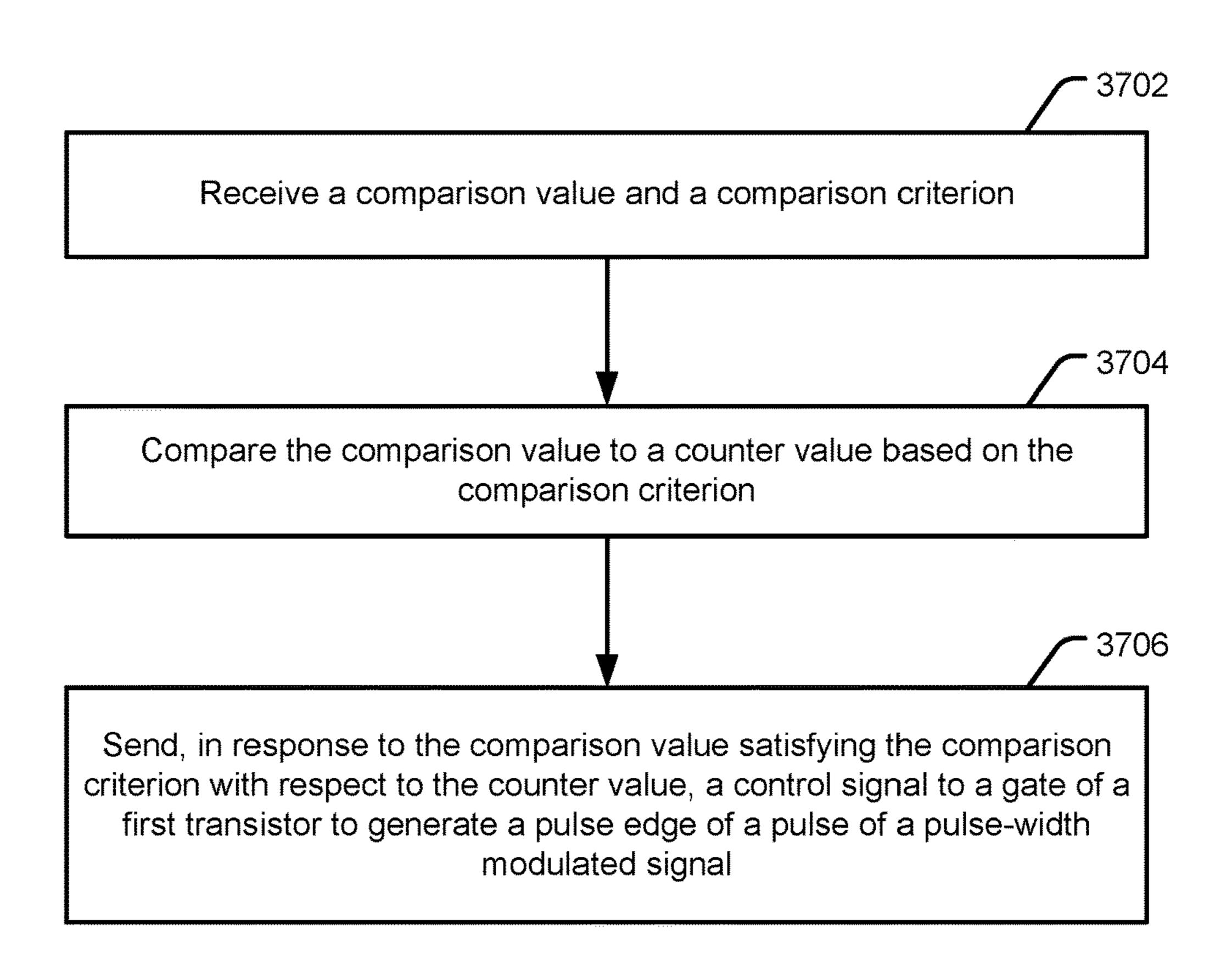

In a particular implementation, a pulse-width modulation control circuit includes a first transistor and a signal generator. The first transistor includes a first terminal coupled to a power source and a second terminal coupled to a first input of a controlled component. The signal generator includes a first node coupled to a gate of the first transistor. The signal generator is configured to receive a comparison value and a comparison criterion and to compare the comparison value to a counter value based on the comparison criterion. In response to the comparison value satisfying the comparison criterion with respect to the counter value, the signal generator is configured to send a control signal to the gate of the first transistor to generate a pulse edge of a pulse of a pulse-width modulated signal.

In another particular implementation, a system includes a motor and a pulse-width modulation control circuit coupled to the motor. The pulse-width modulation control circuit is configured to output a pulse-width modulated signal to the motor. The pulse-width modulation control circuit includes a first transistor and a signal generator. The first transistor includes a first terminal coupled to a power source and a second terminal coupled to a first input of the motor. The signal generator includes a first node coupled to a gate of the first transistor. The signal generator is configured to receive 50 a comparison value and a comparison criterion and to compare the comparison value to a counter value based on the comparison criterion. In response to the comparison value satisfying the comparison criterion with respect to the counter value, the signal generator is configured to send a control signal to the gate of the first transistor to generate a pulse edge of a pulse of the pulse-width modulated signal.

In yet another particular implementation, a method of pulse-width modulation includes receiving a comparison value and a comparison criterion and includes comparing the comparison value to a counter value based on the comparison criterion. The method further includes, in response to the comparison value satisfying the comparison criterion with respect to the counter value, sending a control signal to a gate of a first transistor to generate a pulse edge of a pulse of a pulse-width modulated signal.

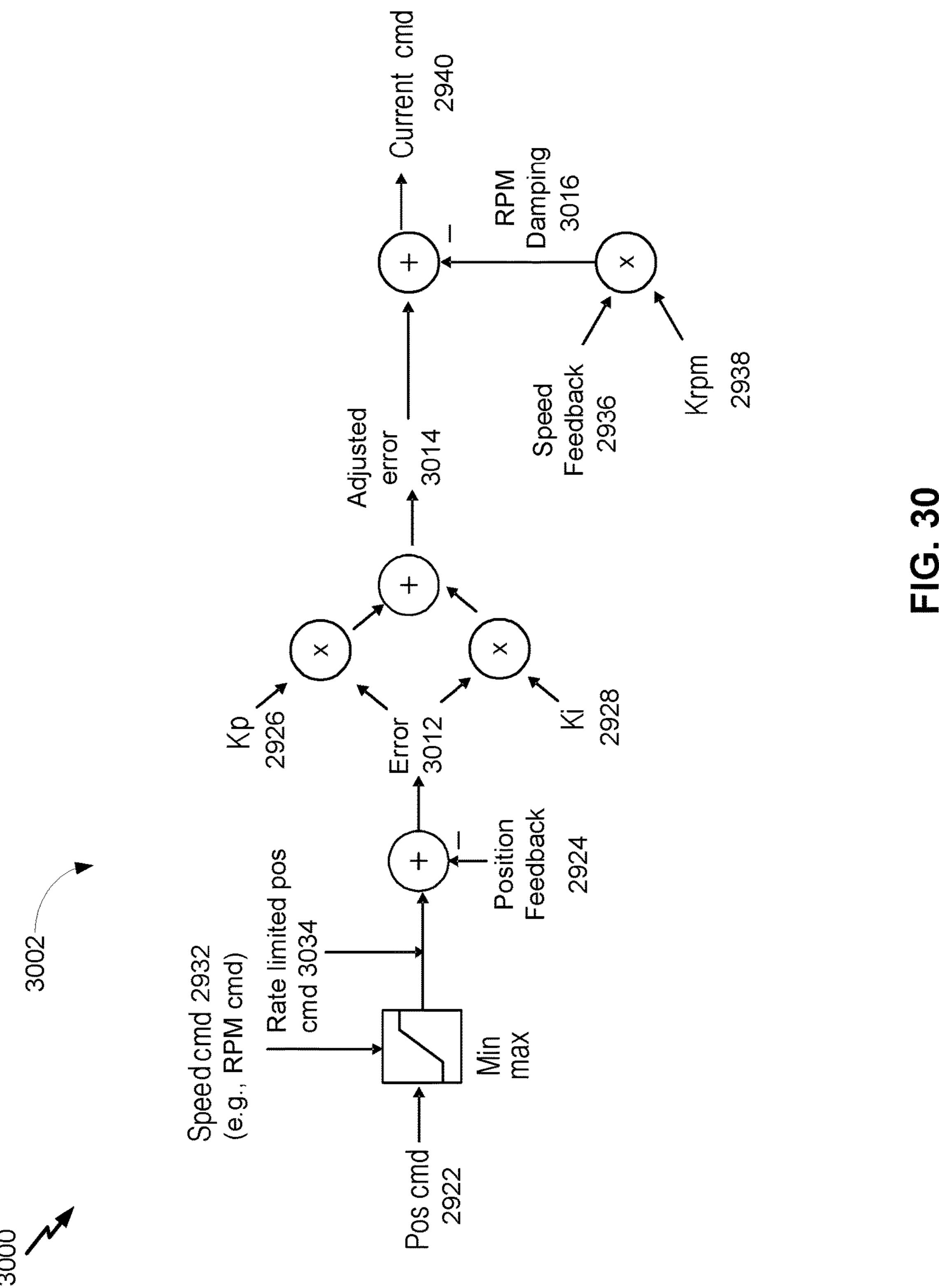

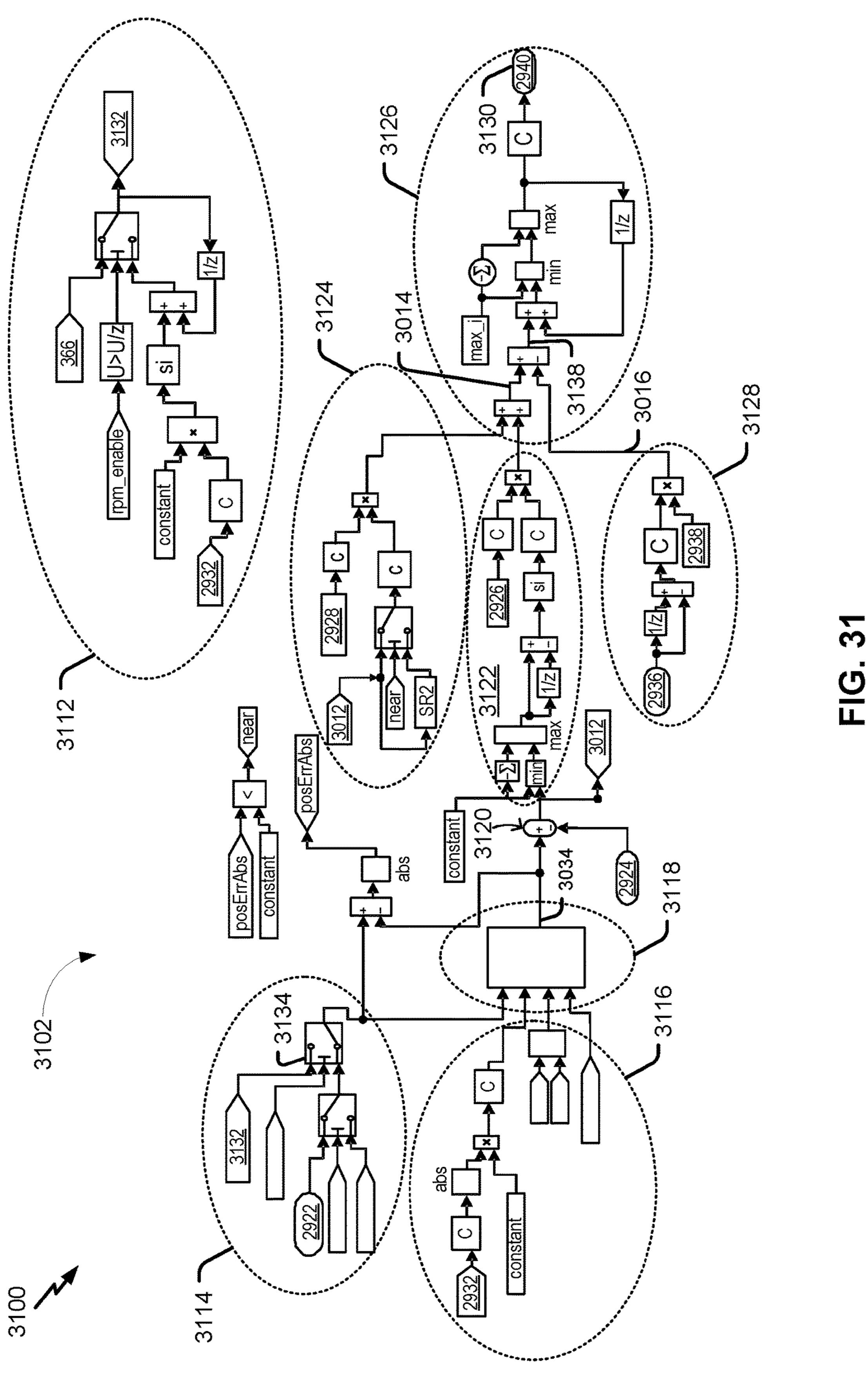

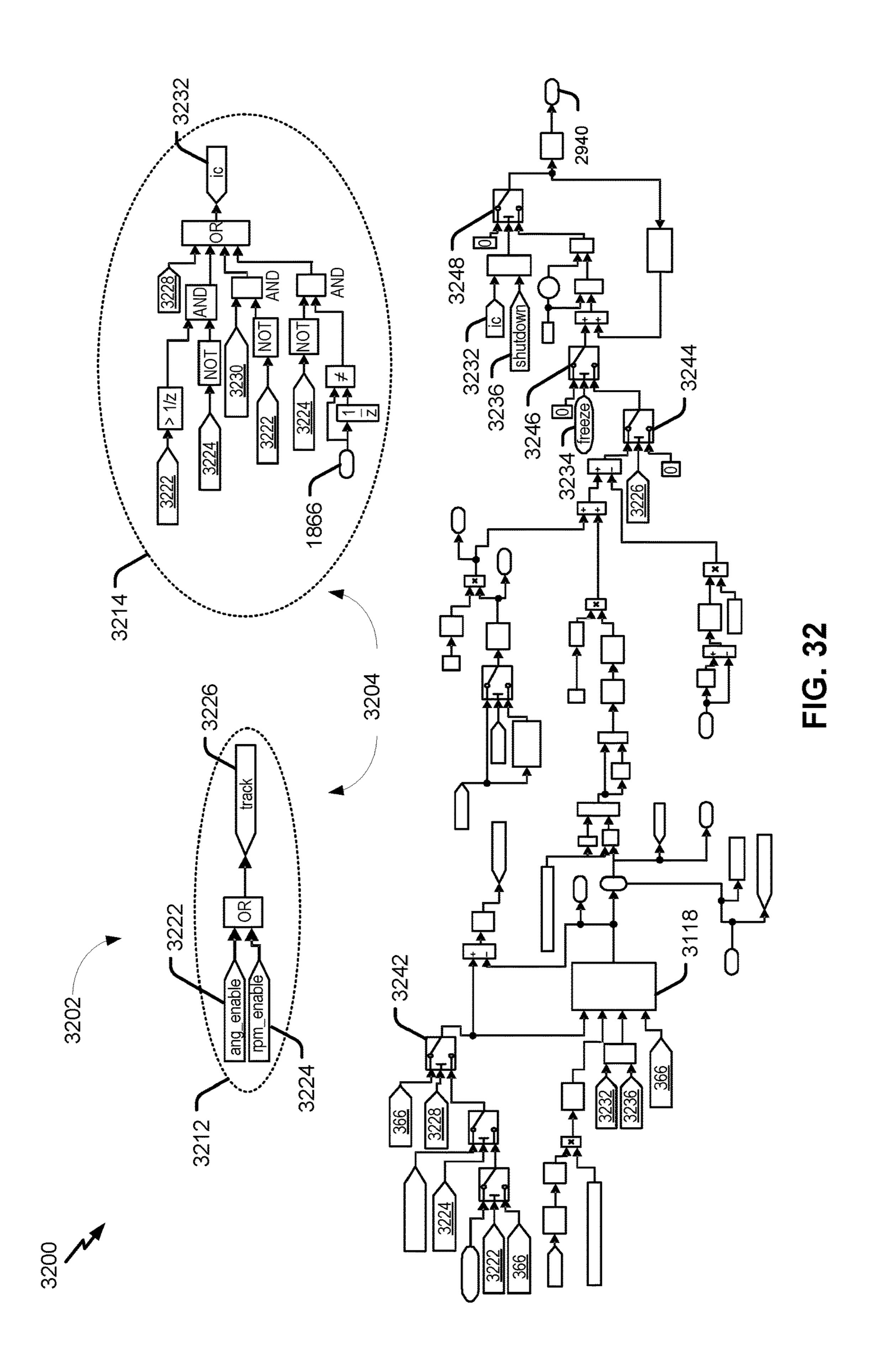

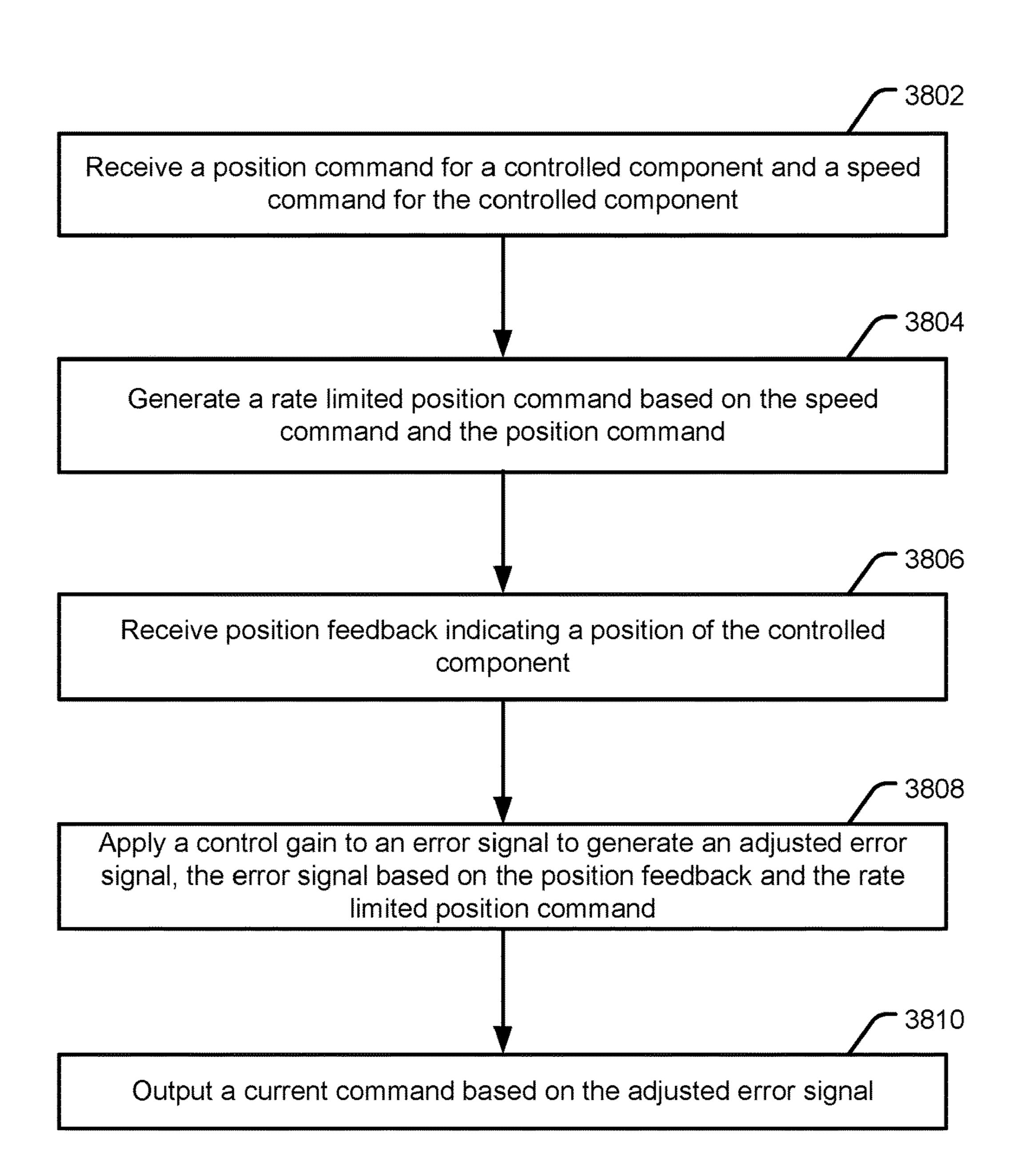

In a particular implementation, feedback control circuitry includes rate limiter circuitry configured to generate a rate

limited position command based on a position command for a controlled component and based on a speed command for the controlled component. The feedback control circuitry also includes error adjustment circuitry configured to apply a control gain to an error signal to generate an adjusted error signal. The error signal is based on position feedback and the rate limited position command, and the position feedback indicates a position of the controlled component. The feedback control circuitry further includes an output terminal configured to output a current command generated based on the adjusted error signal.

In another particular implementation, a system includes a motor and feedback control circuitry coupled to the motor. The feedback control circuitry includes rate limiter circuitry configured to generate a rate limited position command 15 based on a position command for the motor and based on a speed command for the motor. The feedback control circuitry also includes error adjustment circuitry configured to apply a control gain to an error signal to generate an adjusted error signal. The error signal is based on position feedback and the rate limited position command, and the position feedback indicates a position of the motor. The feedback control circuitry further includes an output terminal configured to output a current command generated based on the adjusted error signal.

In yet another particular implementation, a method for feedback control includes receiving a position command for a controlled component and a speed command for the controlled component and includes generating a rate limited position command based on the speed command and the 30 position command. The method also includes receiving position feedback indicating a position of the controlled component and applying a control gain to an error signal to generate an adjusted error signal. The error signal is based on the position feedback and the rate limited position 35 command. The method further includes outputting a current command based on the adjusted error signal.

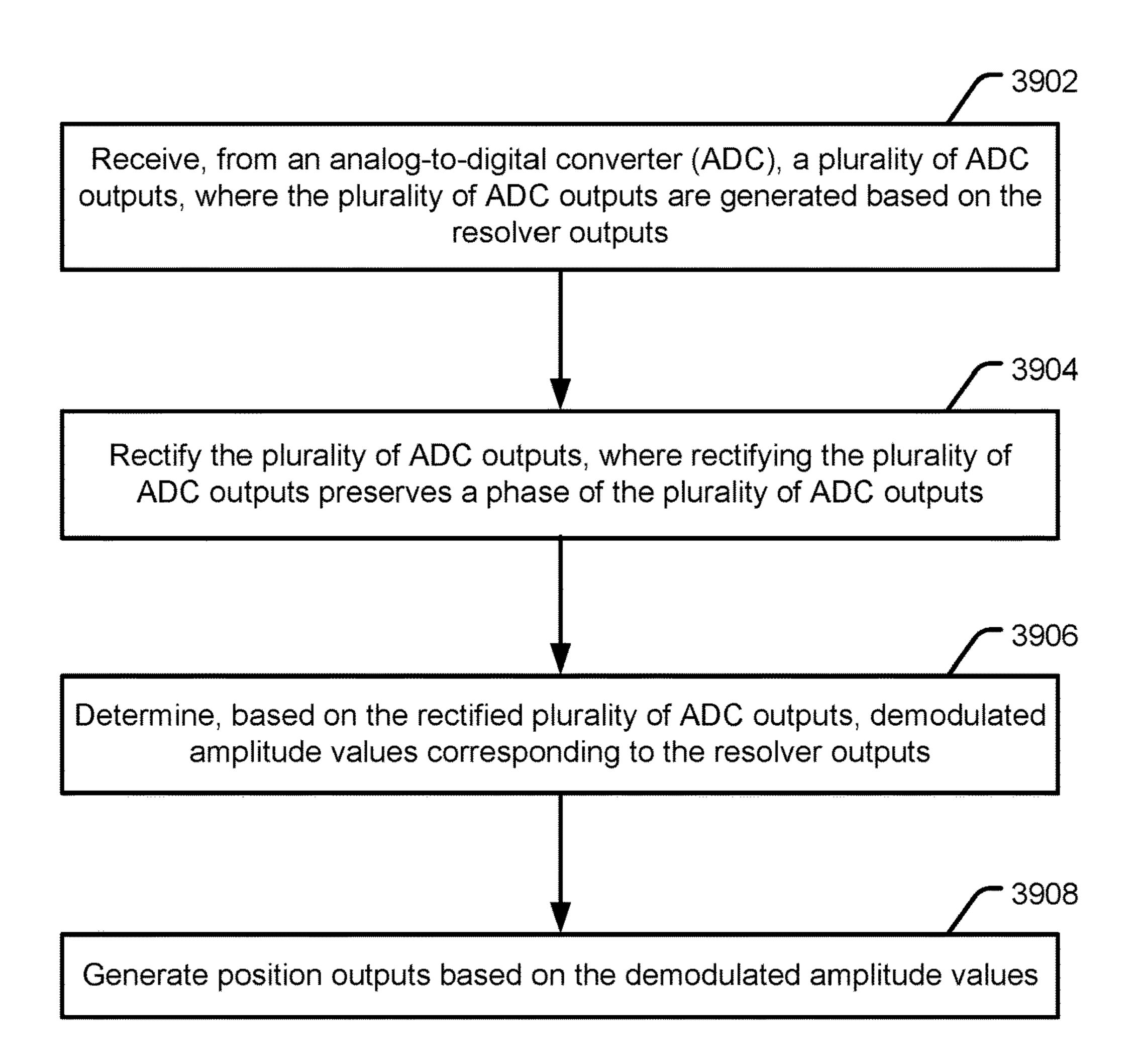

In a particular implementation, demodulation circuitry includes an input terminal configured to be coupled to an analog-to-digital converter (ADC) and configured to receive 40 a plurality of ADC outputs. The plurality of ADC outputs are generated based on resolver outputs. The demodulation circuitry also includes a rectifier configured to rectify the plurality of ADC outputs. Rectifying the plurality of ADC outputs preserves a phase of the plurality of ADC outputs. The demodulation circuitry includes amplitude determination circuitry configured to determine, based on the rectified plurality of ADC outputs, demodulated amplitude values corresponding to the resolver outputs. The demodulation circuitry further includes angle computation circuitry configured to generate position outputs based on the demodulated amplitude values.

In another particular implementation, a system includes a resolver, an ADC coupled to the resolver, and demodulation circuitry is circuitry coupled to the ADC. The demodulation circuitry is configured to generate demodulated resolver outputs and includes an input terminal configured to be coupled to the ADC and configured to receive a plurality of ADC outputs. The plurality of ADC outputs are generated based on resolver outputs. The demodulation circuitry also includes a processing rectifier configured to rectify the plurality of ADC outputs. Rectifying the plurality of ADC outputs preserves a phase of the plurality of ADC outputs. The demodulation circuitry configured to determine, based on the rectified plurality of ADC outputs, demodulated amplitude values corresponding to the resolver outputs. The demodulation circuitry further includes angle includes a processing resolver; and demodulation circuitry is former;

FIG. 4

FIG. 4

FIG. 4

FIG. 5

FIG. 5

FIG. 6

example speed resolver; and demodulation circuitry is processing rectified plurality of ADC outputs. The demodulation circuitry includes and includes and includes an input terminal configured to the ADC outputs. The demodulation circuitry also includes a processing resolver; and demodulate and includes and includes an input terminal configured to be coupled to the speed resolver; and includes an input terminal configured to be coupled to the speed resolver; and includes an input terminal configured to be coupled to the speed resolver; and includes an input terminal configured to the ADC outputs. The demodulation circuitry also includes a processing resolver; and includes an input terminal configured to the ADC outputs. The demodulation circuitry also includes a processing resolver; and includes an input terminal configured to processing the plurality of ADC outputs. The demodulation circuitry also includes an includes an input terminal configured to the ADC outputs. The demodulation circuitry includes an input terminal configured to the ADC outputs. Th

4

computation circuitry configured to generate position outputs based on the demodulated amplitude values.

In yet another particular implementation, a method of demodulating resolver outputs includes receiving, from an ADC, a plurality of ADC outputs. The plurality of ADC outputs are generated based on the resolver outputs. The method also includes rectifying the plurality of ADC outputs, and rectifying the plurality of ADC outputs preserves a phase of the plurality of ADC outputs. The method includes determining, based on the rectified plurality of ADC outputs, demodulated amplitude values corresponding to the resolver outputs. The method further includes generating position outputs based on the demodulated amplitude values.

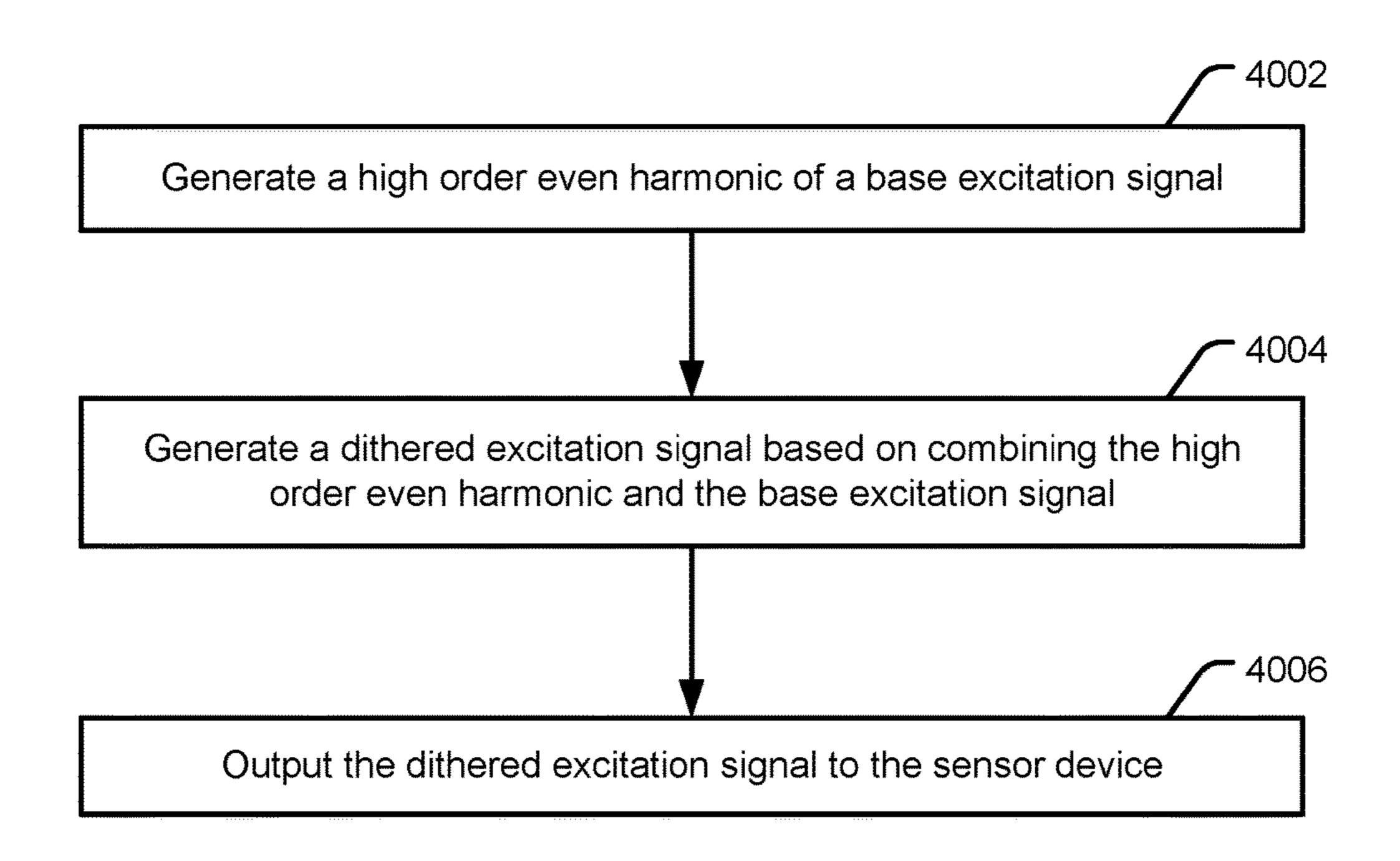

In a particular implementation, dither circuitry includes harmonic signal generation circuitry configured generate a high order even harmonic of a base excitation signal. The dither circuitry also includes a combiner configured to generate a dithered excitation signal based on the high order even harmonic and the base excitation signal. The dither circuitry further includes an output terminal configured to output the dithered excitation signal to a sensor device.

In another particular implementation, a system includes a resolver, a digital-to-analog converter (DAC) coupled to the resolver, and dither circuitry coupled to the DAC. The dither circuitry is configured to output a dithered excitation signal to the DAC. The dither circuitry includes harmonic signal generation circuitry configured generate a high order even harmonic of a base excitation signal. The dither circuitry also includes a combiner configured to generate the dithered excitation signal based on the high order even harmonic and the base excitation signal. The dither circuitry further includes an output terminal configured to output the dithered excitation signal to the resolver.

In yet another particular implementation, a method of generating an excitation signal for a sensor device includes generating a high order even harmonic of a base excitation signal. The method further includes generating a dithered excitation signal based on combining the high order even harmonic and the base excitation signal and outputting the dithered excitation signal to the sensor device.

### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a diagram that illustrates an example of an inertial measurement unit;

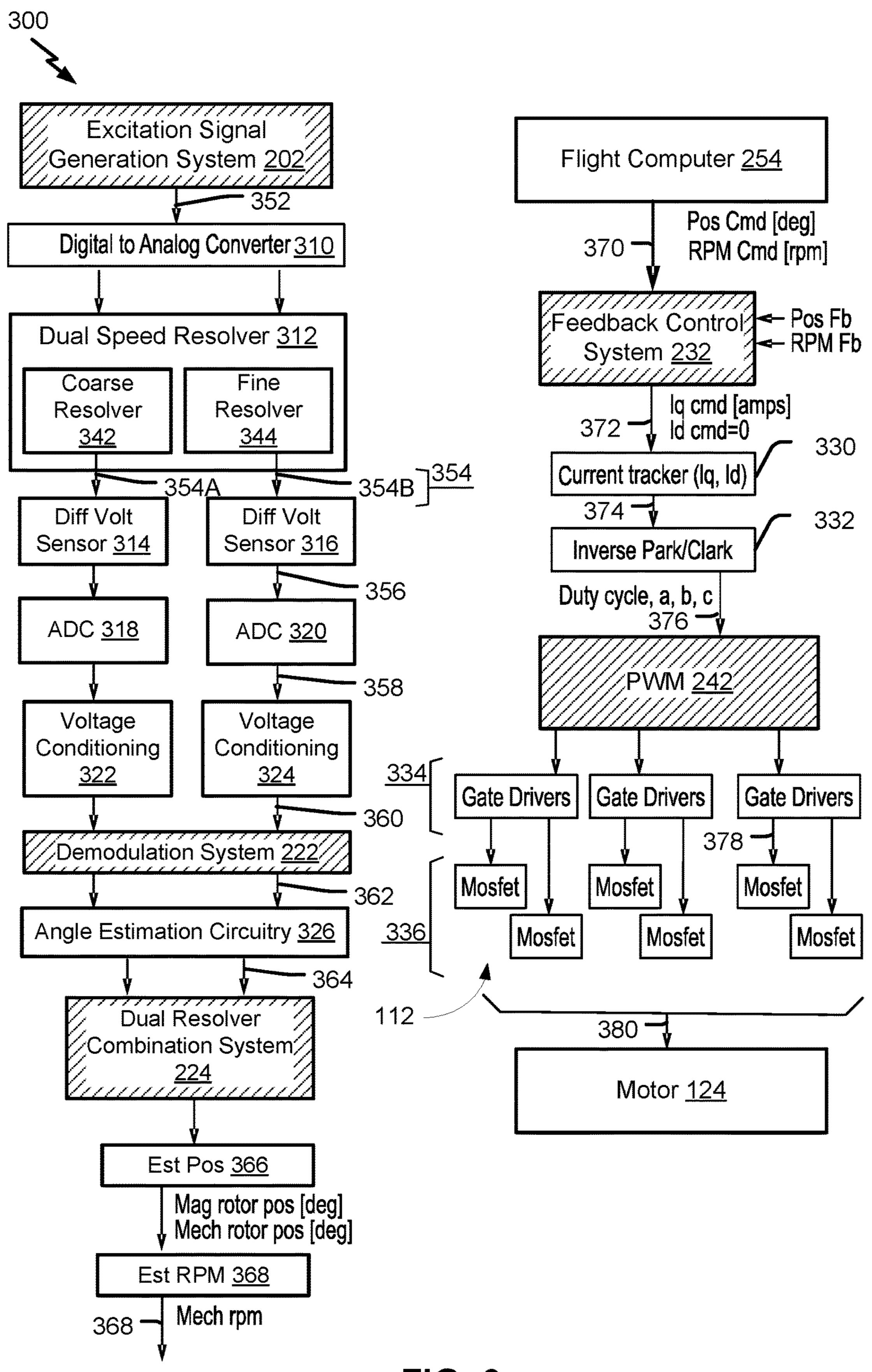

FIG. 2 is a diagram that illustrates an example of systems of the inertial measurement unit;

FIG. 3 is a diagram that illustrates an example of operation of the inertial measurement unit;

FIG. 4A illustrates a diagram of an example of a transformer;

FIG. 4B illustrates a diagram of an example of a resolver; FIG. 4C illustrates exemplary graphs of signals of a dual speed resolver;

FIG. **5** is a diagram that illustrates an example of flow processing for processing resolver outputs for the dual speed resolver:

FIG. 6 is a logic diagram that illustrates an overview of an example of logic for processing resolver outputs of the dual speed resolver;

FIG. 7 is a logic diagram that illustrates an overview of logic for demodulation and angle estimation;

FIG. 8 is a logic diagram that illustrates an example of logic for voltage conditioning;

- FIG. 9 is a logic diagram that illustrates an example of recursive median value analysis logic for recursive median value analysis;

- FIG. 10 is a logic diagram that illustrates an example of demodulation logic of FIG. 8;

- FIG. 11 is a logic diagram that illustrates an example of logic for rectification with phase preservation;

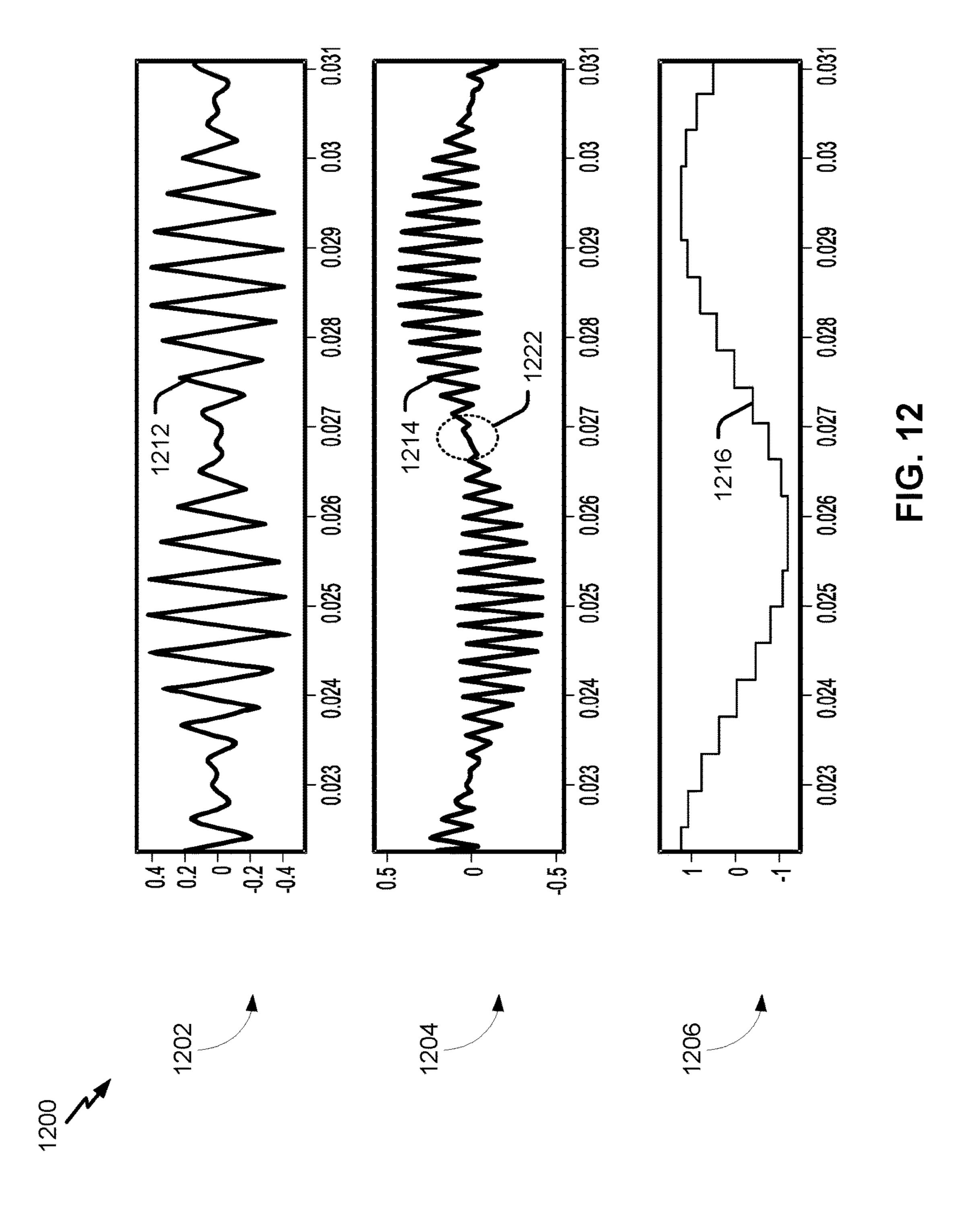

- FIG. 12 illustrates a diagram of exemplary signals generated during demodulation;

- FIG. 13 illustrates exemplary graphs of signals of the resolver of FIG. 4B;

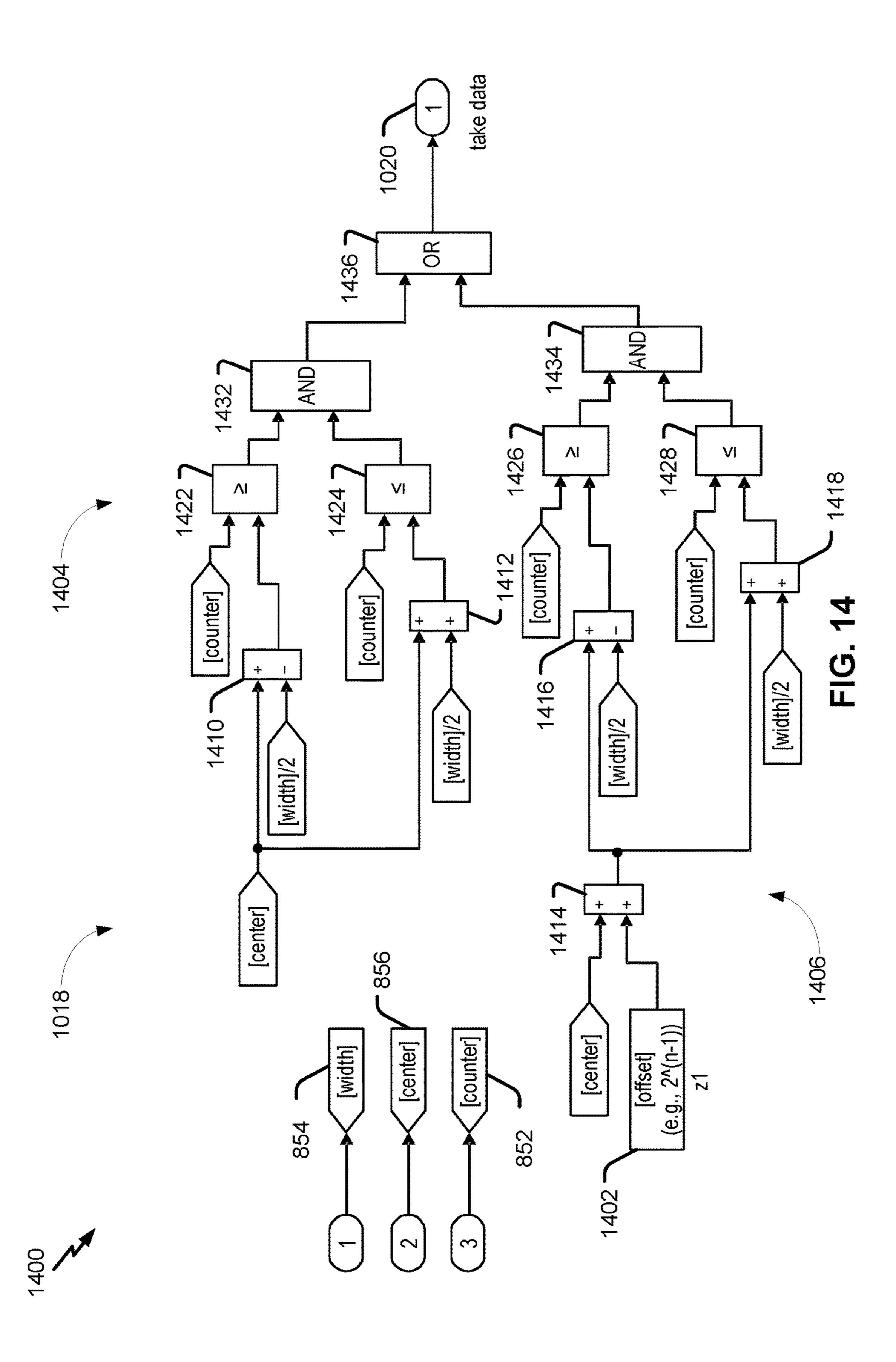

- FIG. 14 is a logic diagram that illustrates an example of mask logic of FIG. 10;

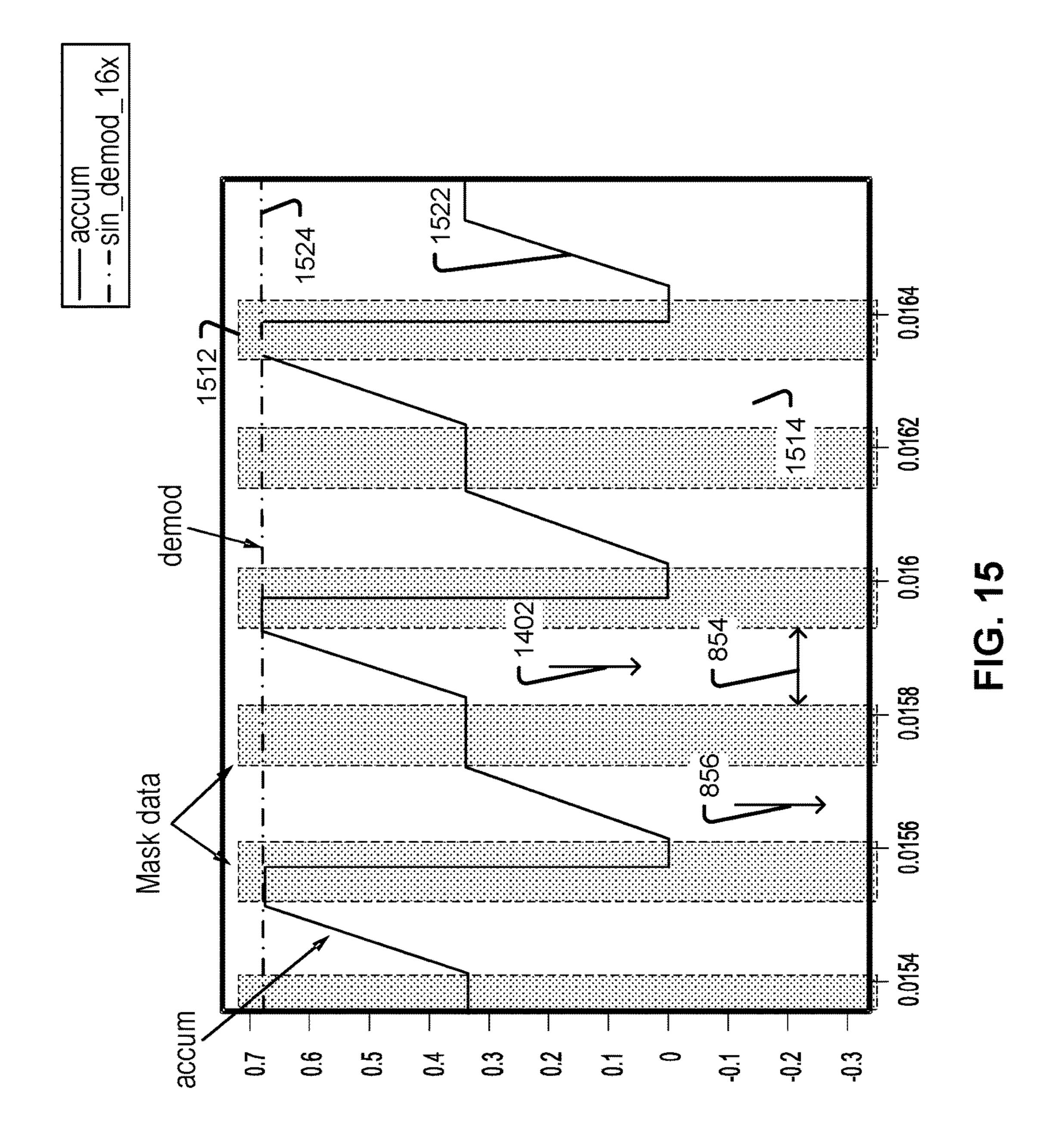

- FIG. **15** is a diagram that illustrates an example of masked data and accumulated data for demodulation;

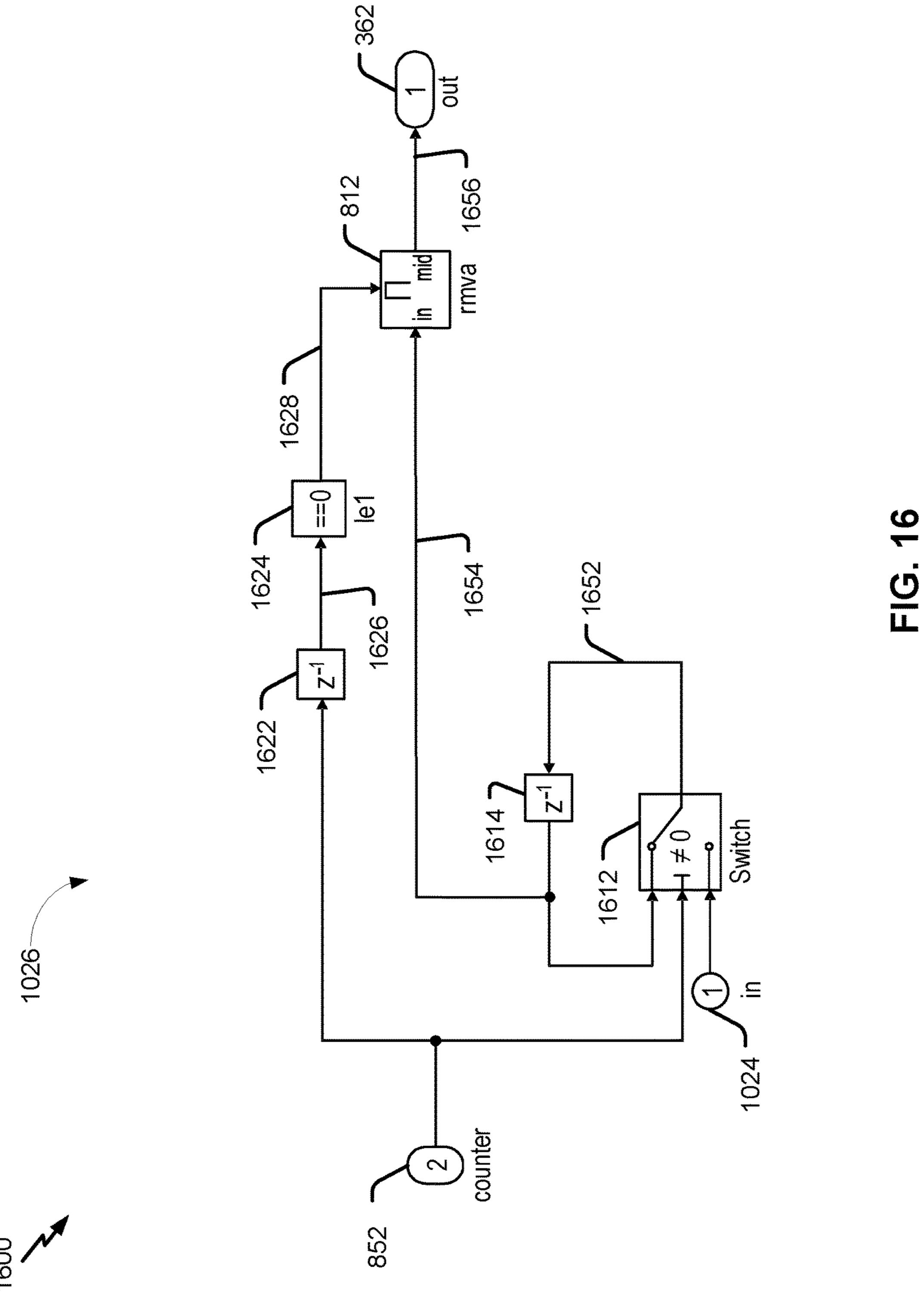

- FIG. 16 is a logic diagram that illustrates an example of output logic of FIG. 10;

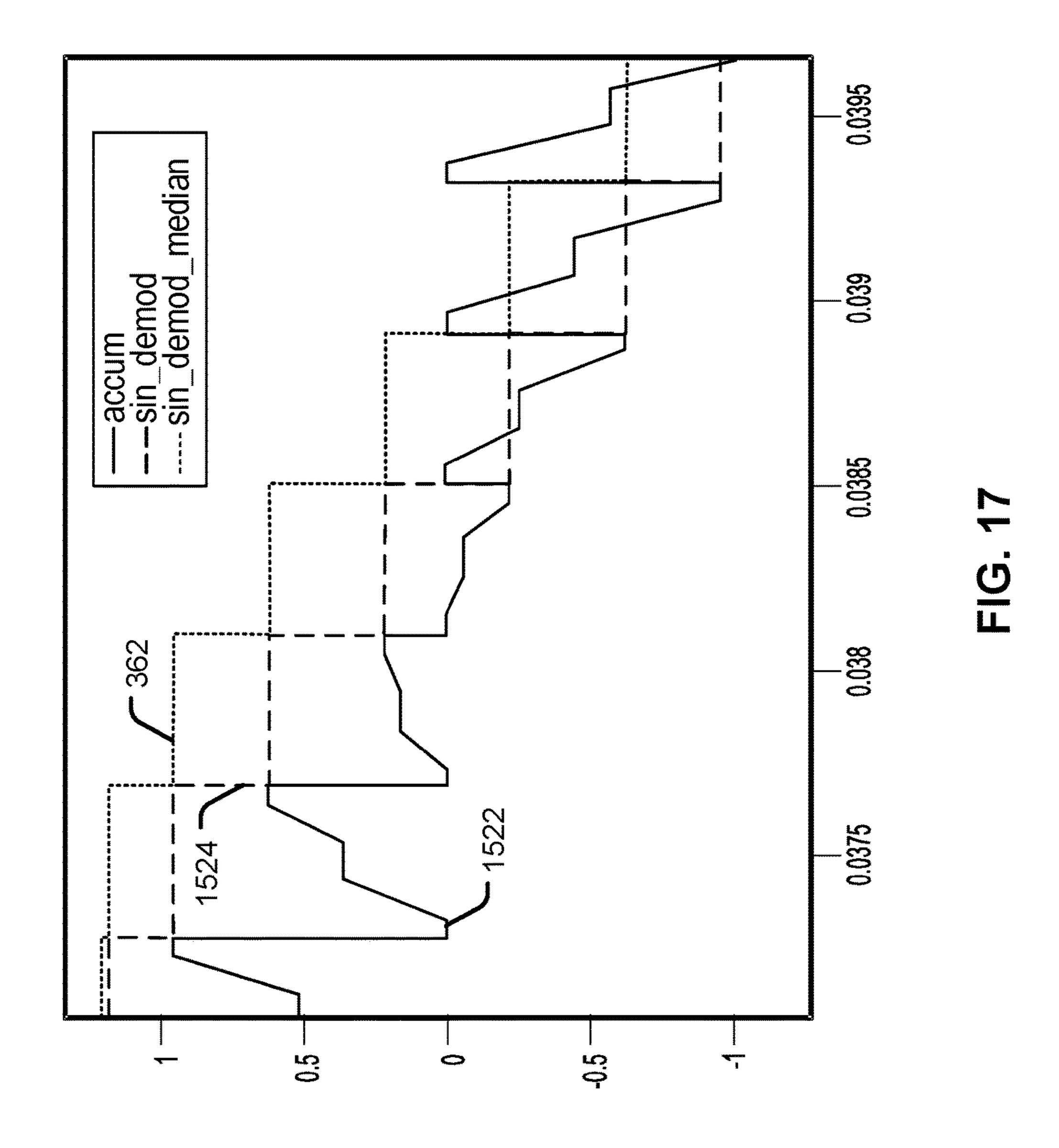

- FIG. 17 is a diagram that illustrates an example of accumulator inputs and accumulator outputs for demodulation;

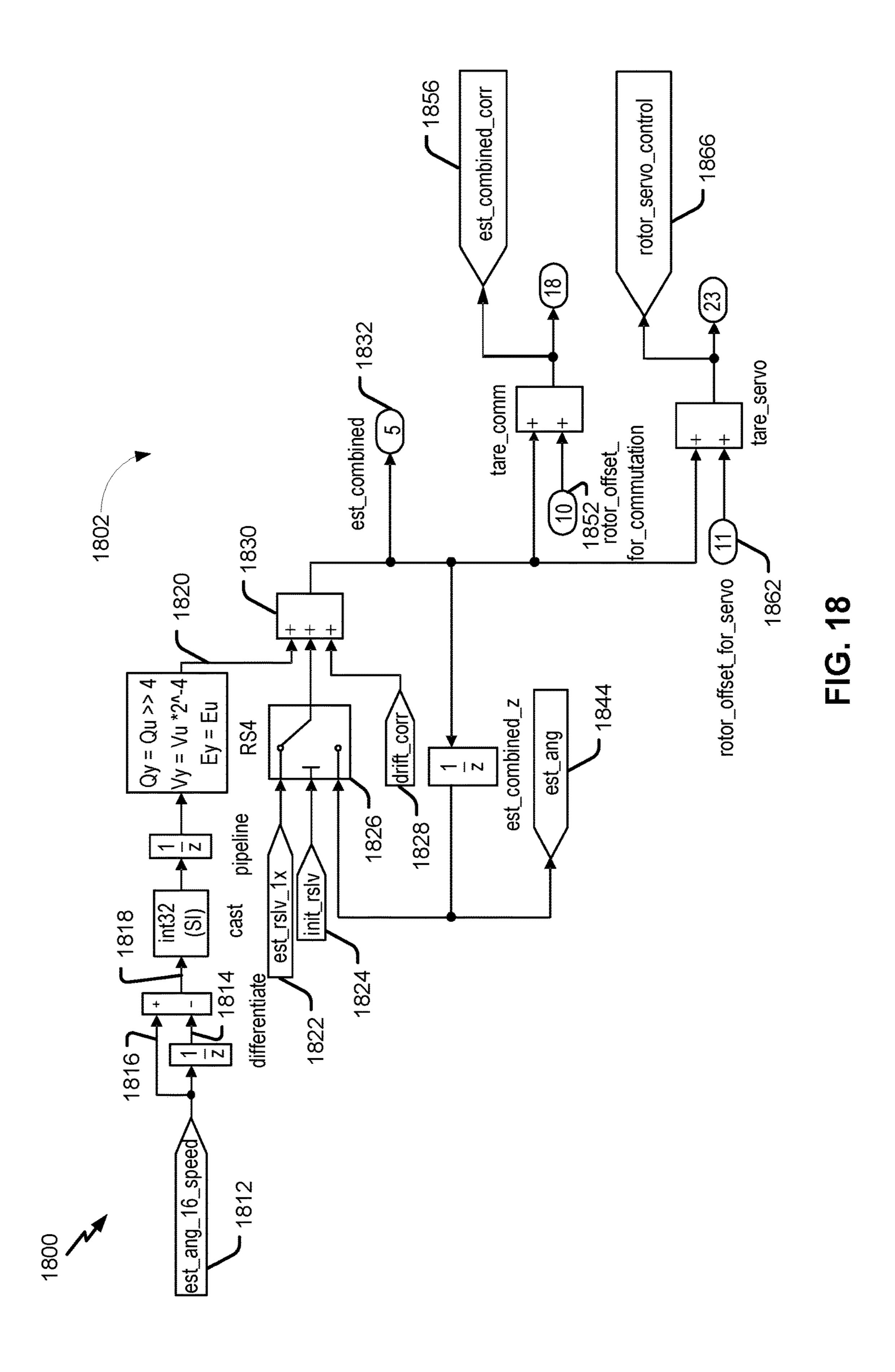

- FIG. 18 is a logic diagram that illustrates an example of logic for combining resolver outputs of a dual speed resolver;

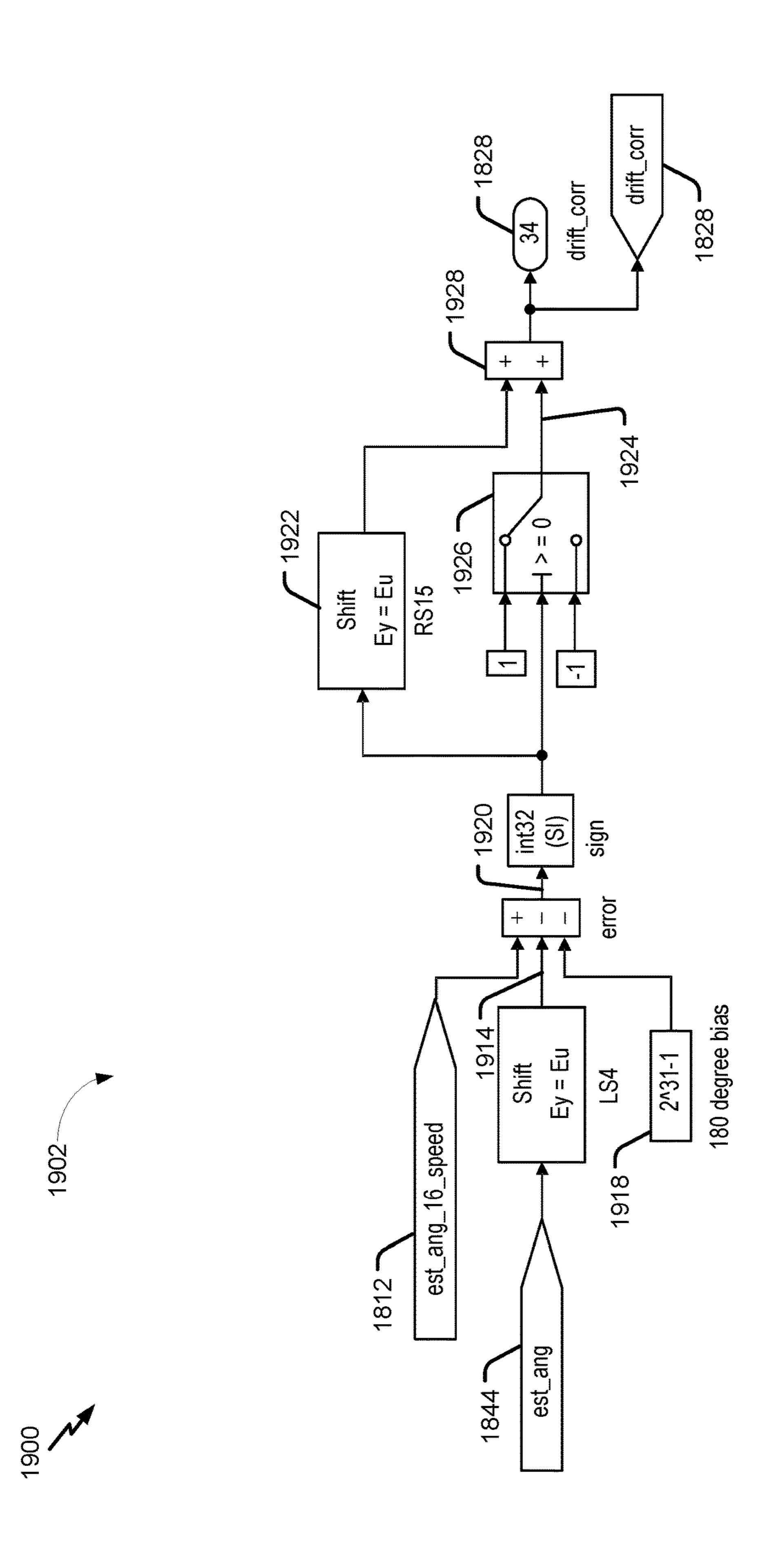

- FIG. **19** is a logic diagram that illustrates an example of <sup>25</sup> logic for a drift corrector of a dual speed resolver;

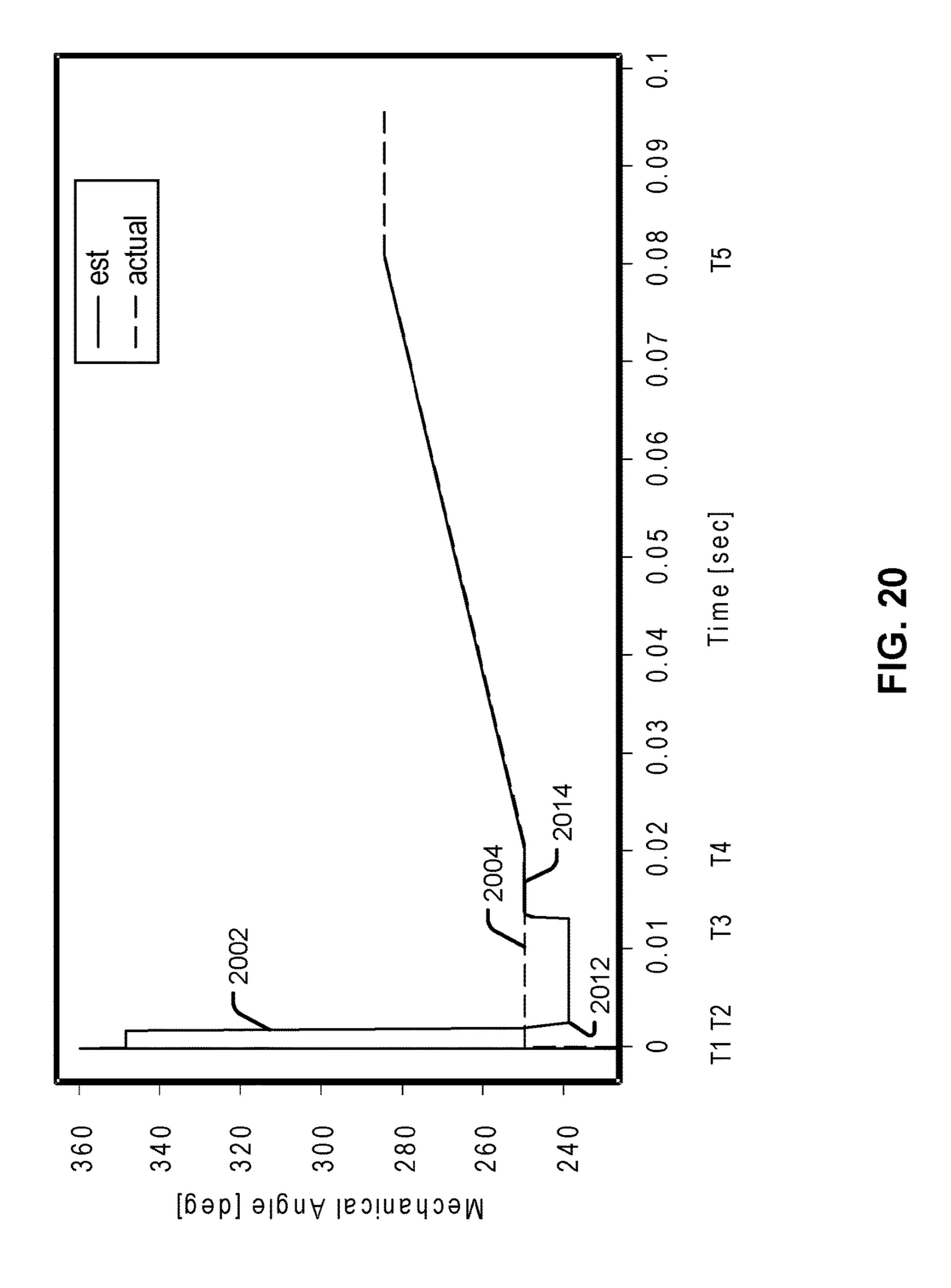

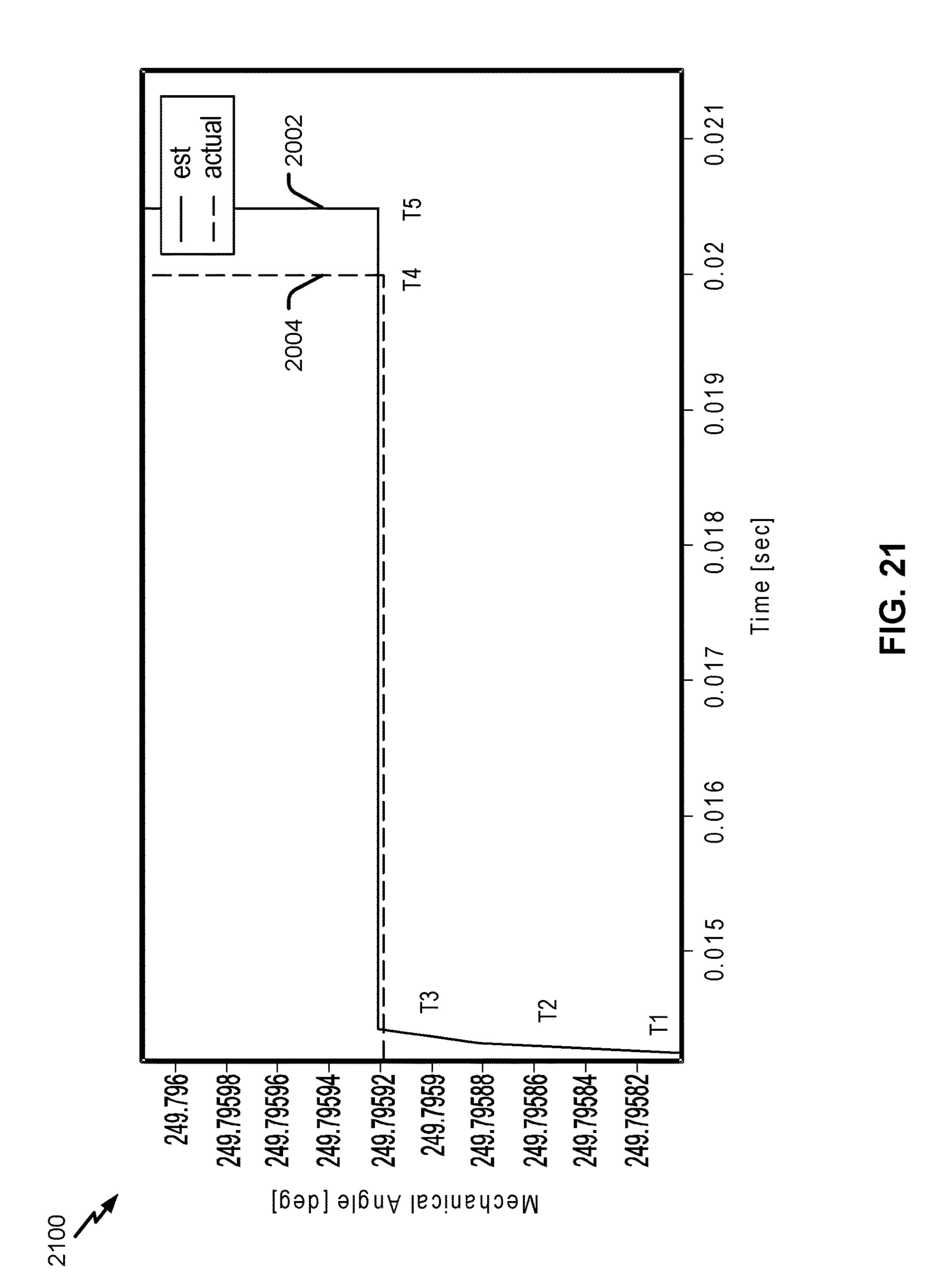

- FIG. 20 includes a diagram illustrating a mechanical angle estimated by the resolver system of FIG. 2 and an actual angle of the motor;

- FIG. 21 include a diagram that depicts an enlarged view of the diagram of FIG. 20;

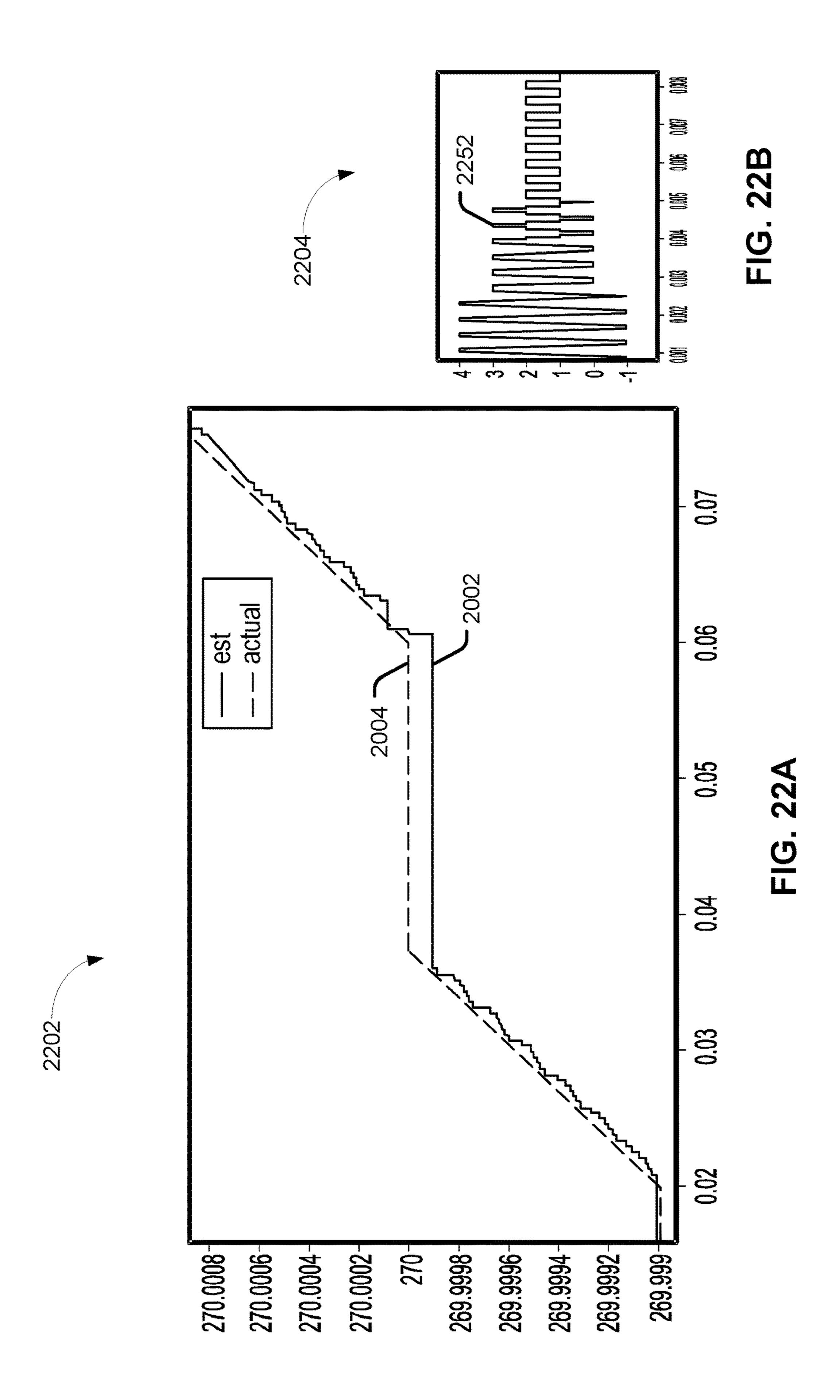

- FIG. 22A is a diagram that illustrates angles determined based on resolver outputs using an excitation signal without dither;

- FIG. **22**B is a diagram that illustrates analog-to-digital converter (ADC) outputs generated based on resolver outputs generated by an excitation signal without dither;

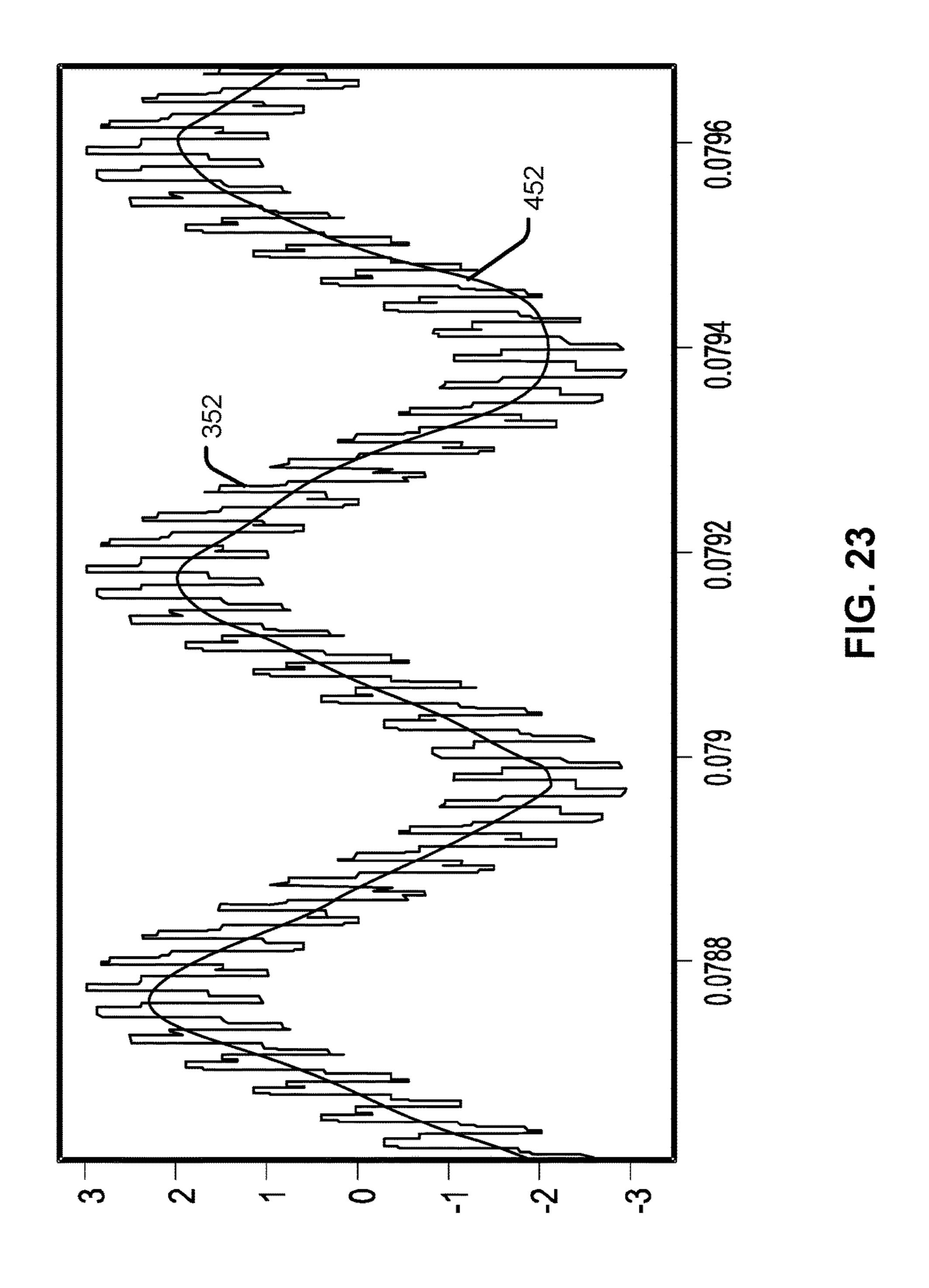

- FIG. 23 is a diagram that illustrates an example of a dithered excitation signal;

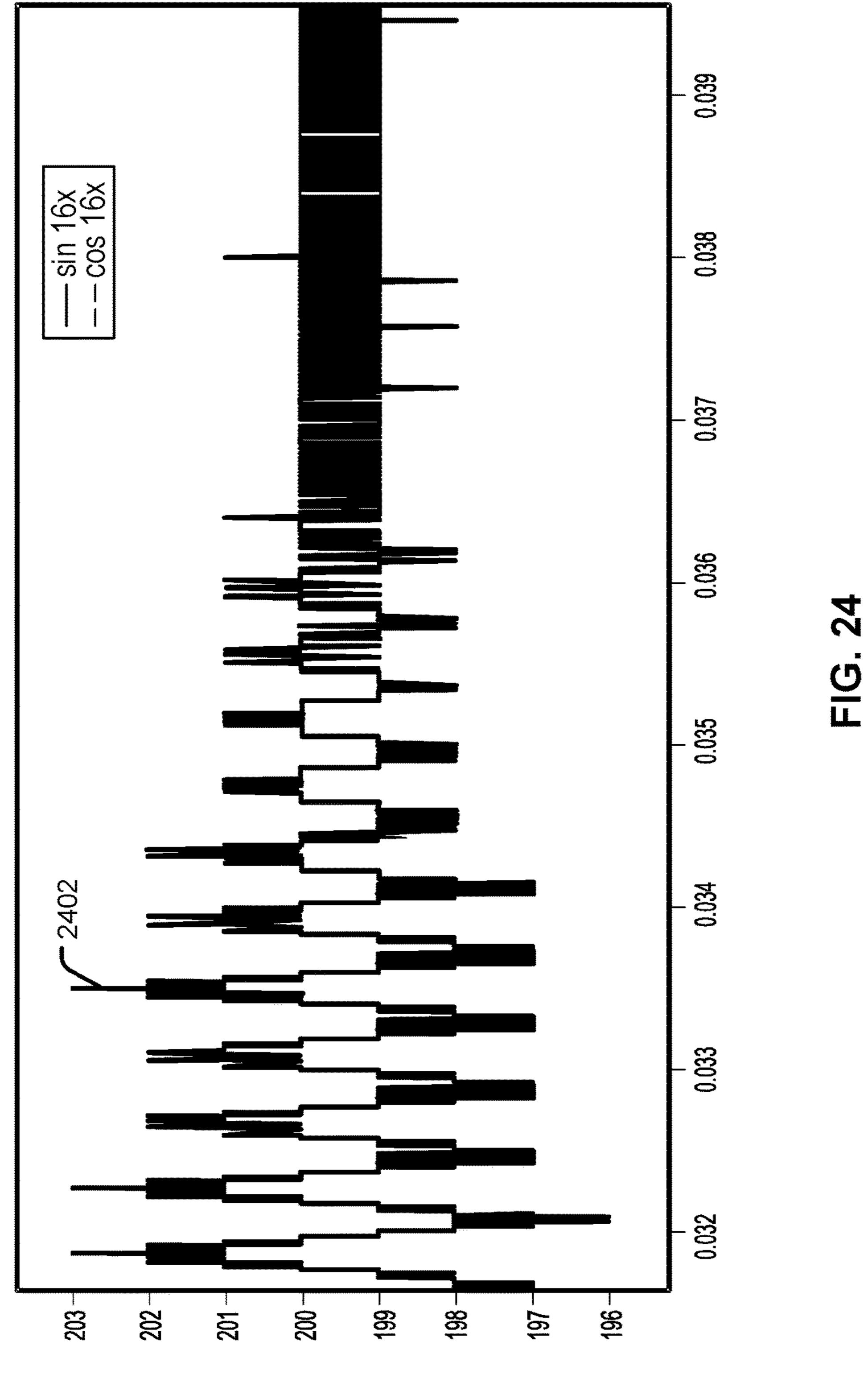

- FIG. **24** is a diagram that illustrates ADC outputs generated based on a dithered excitation signal;

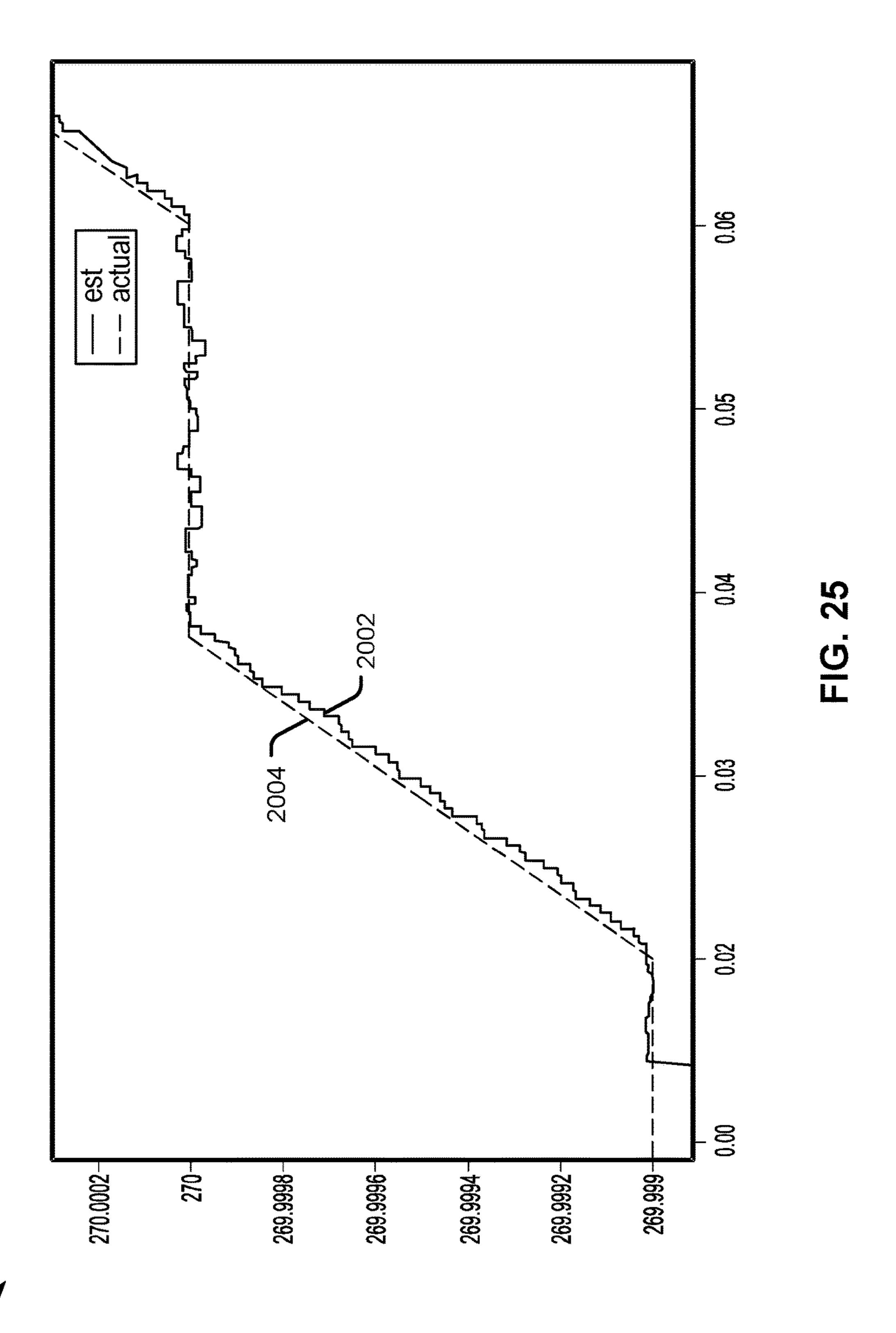

- FIG. 25 is a diagram that illustrates angles determined based on a dithered excitation signal;

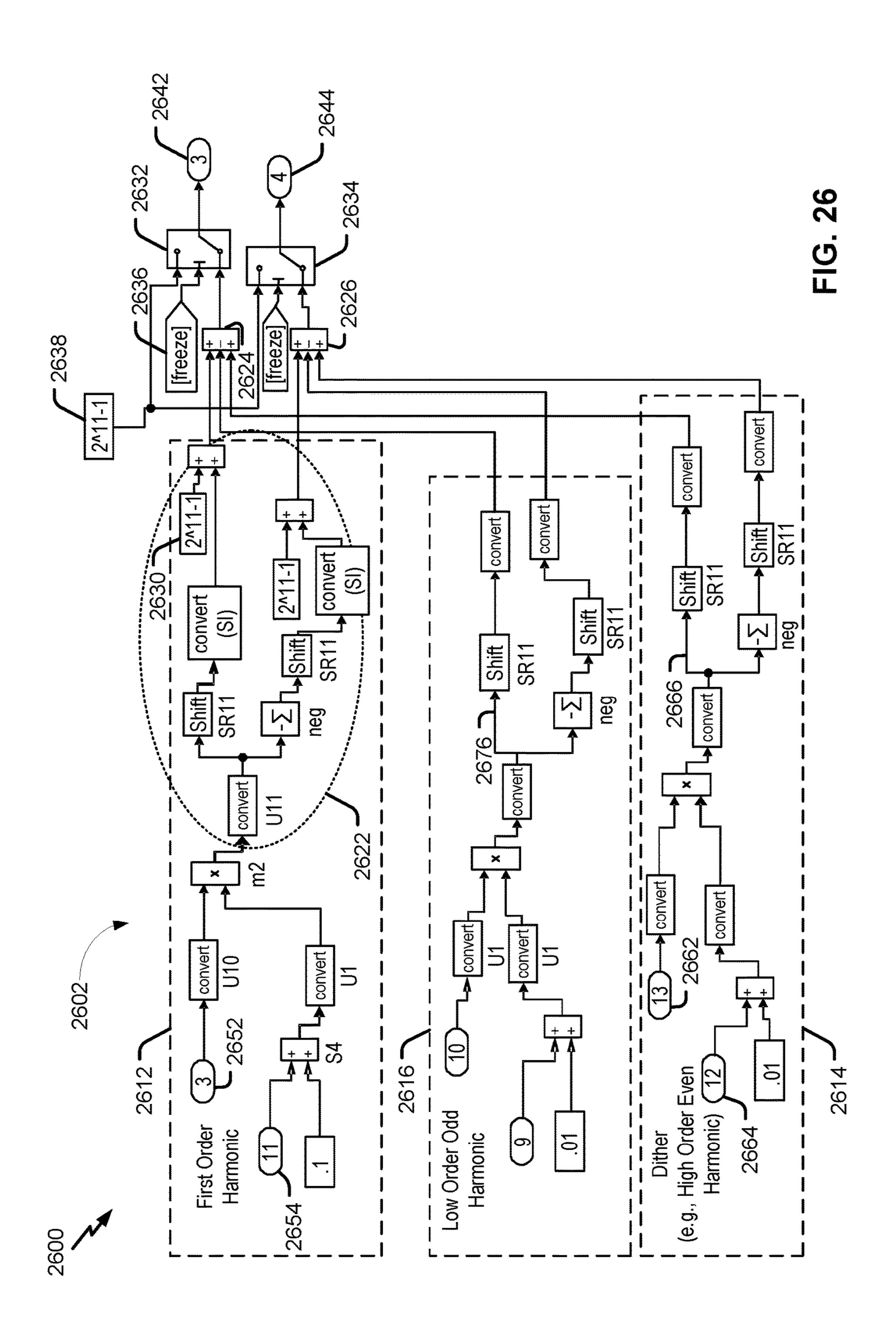

- FIG. **26** is a logic diagram that illustrates an example of 45 logic for excitation signal generation;

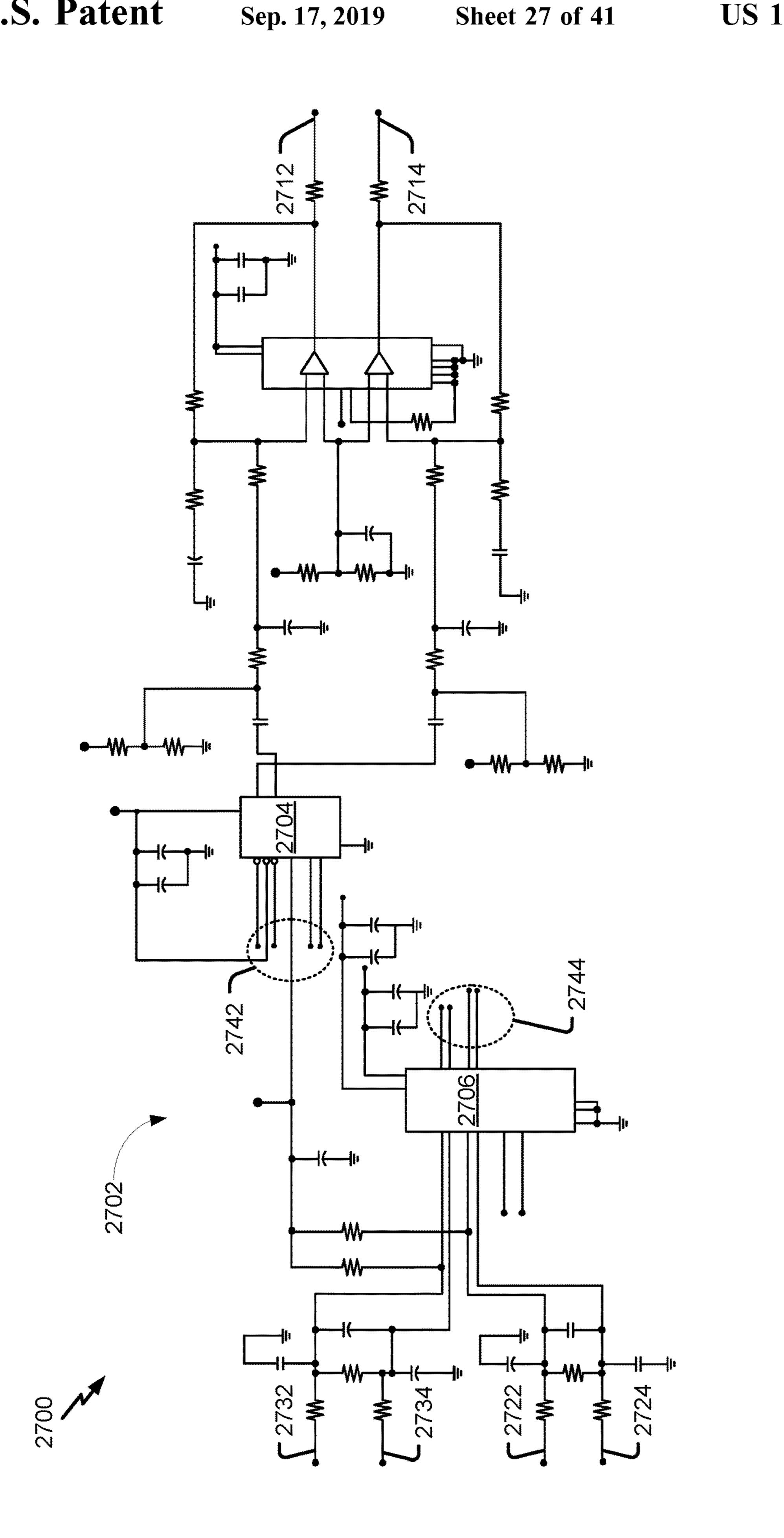

- FIG. 27 is a circuit diagram that illustrates an example of a resolver driver circuit;

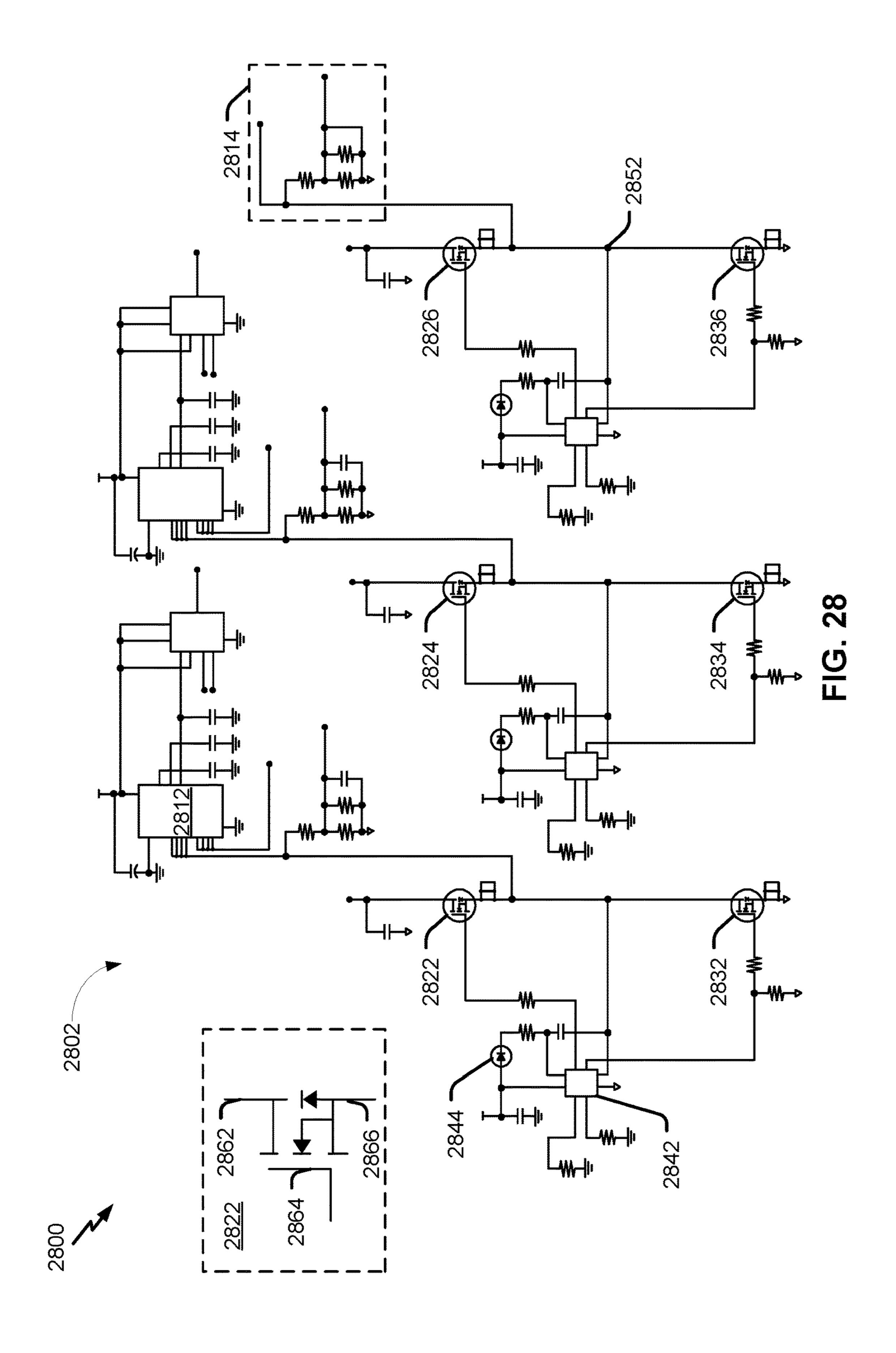

- FIG. 28 is a circuit diagram that illustrates an example of a motor driver circuit;

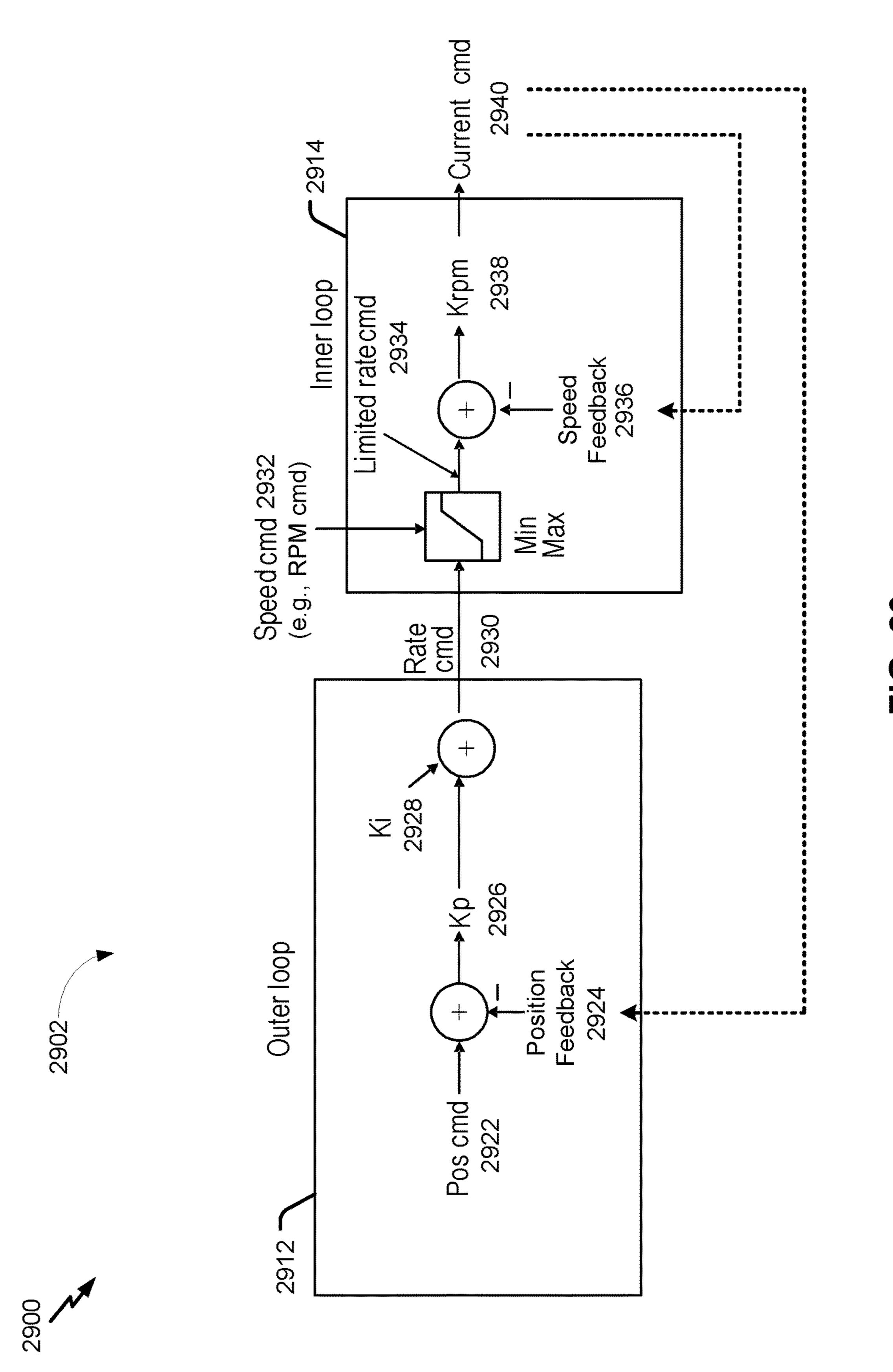

- FIG. 29 is a diagram that illustrates an example of cascaded feedback logic for speed feedback and position feedback;

- FIG. 30 is a logic diagram that illustrates an example of logic for combined speed and position feedback control;

- FIG. 31 is a logic diagram that illustrates an example of logic for combined speed and position feedback control including a direct speed command mode;

- FIG. 32 is a logic diagram that illustrates an example of logic for combined speed and position feedback control 60 including an initialization mode;

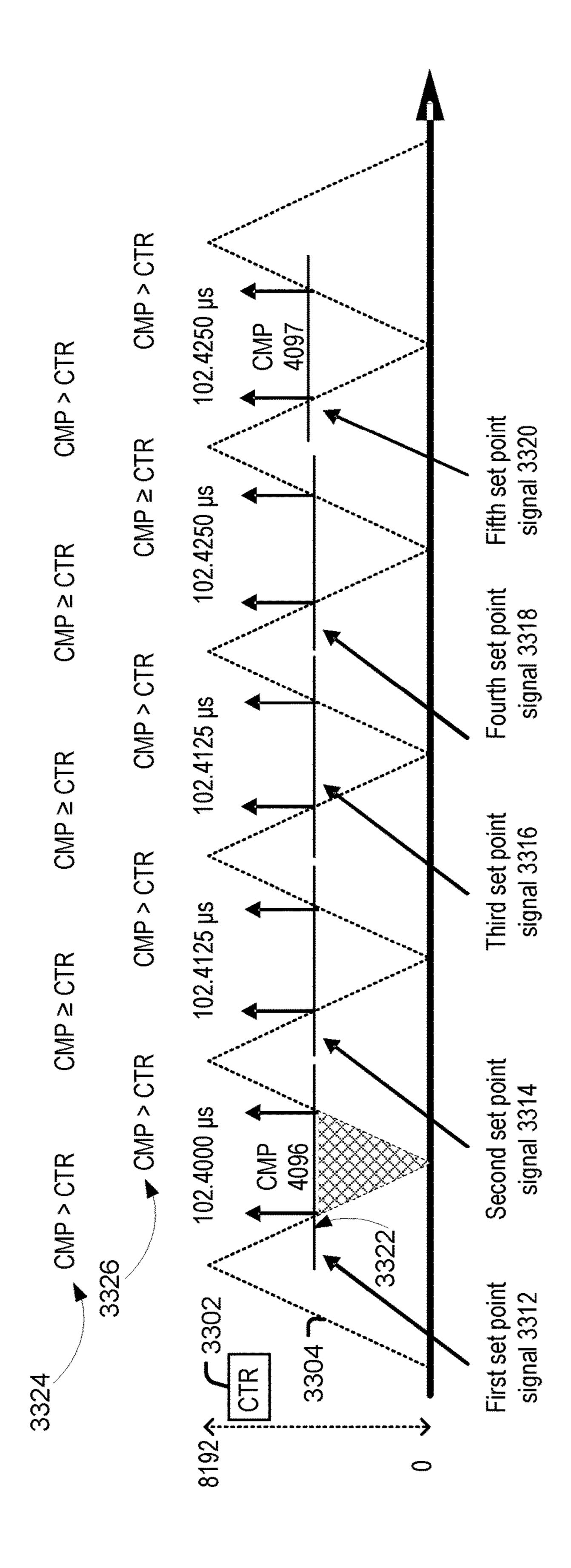

- FIG. 33 is a diagram that illustrates an example of pulse-width modulation (PWM) operation with an adjustable comparison criterion;

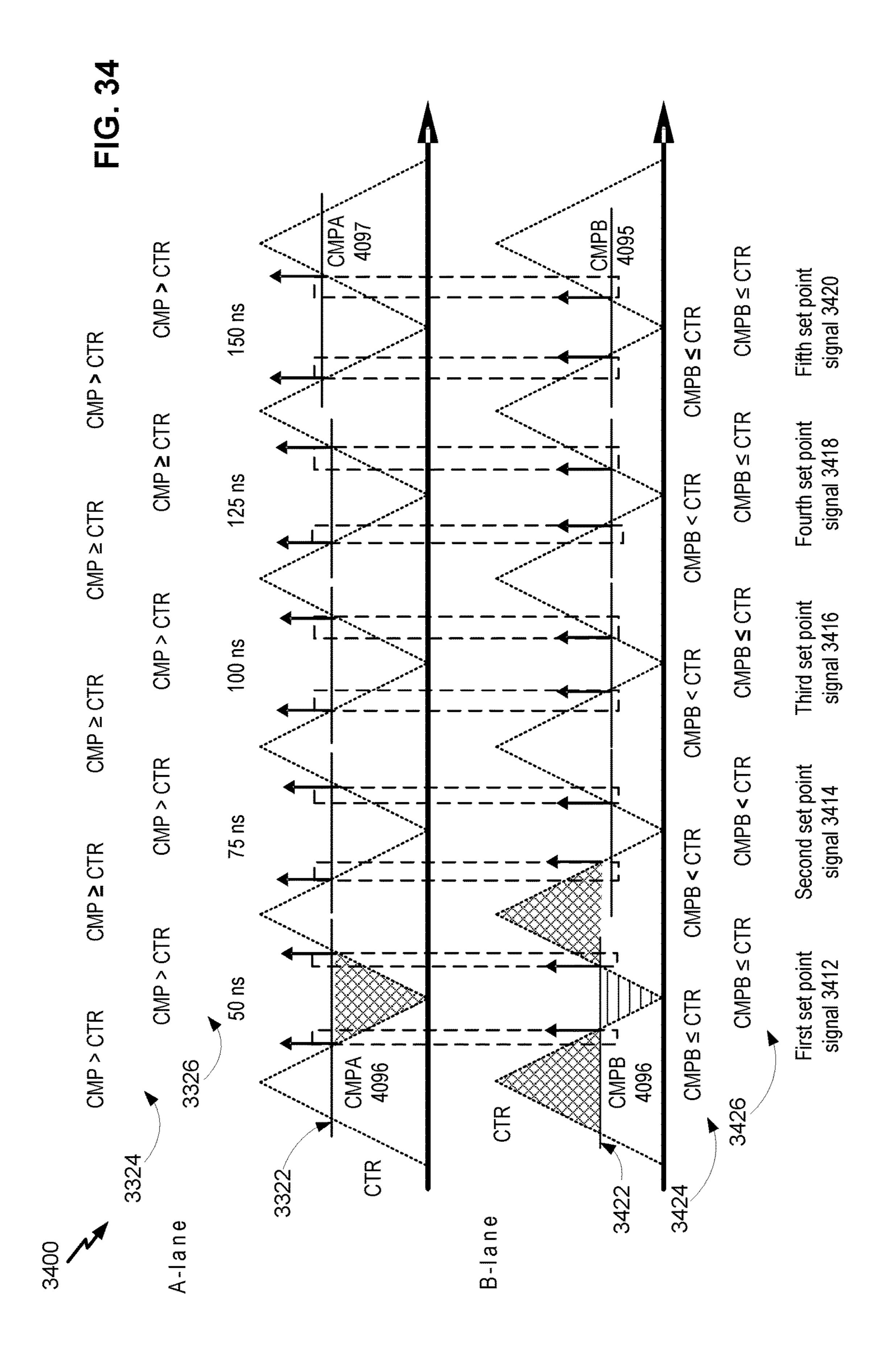

- FIG. **34** is a diagram that illustrates an example of two 65 lane PWM operation with an adjustable comparison criterion;

6

- FIG. **35** is a logic diagram that illustrates an example of logic for a PWM with an adjustable comparison criterion and dead band control;

- FIG. 36 is a flow chart of an example of a method of determining rotational position using a dual speed resolver;

- FIG. 37 is a flow chart of an example of a method of pulse-width modulation;

- FIG. 38 is a flow chart of an example of a method for feedback control;

- FIG. 39 is a flow chart of an example of a method of demodulating resolver outputs;

- FIG. 40 is a flow chart of an example of a method of generating an excitation signal for a sensor device; and

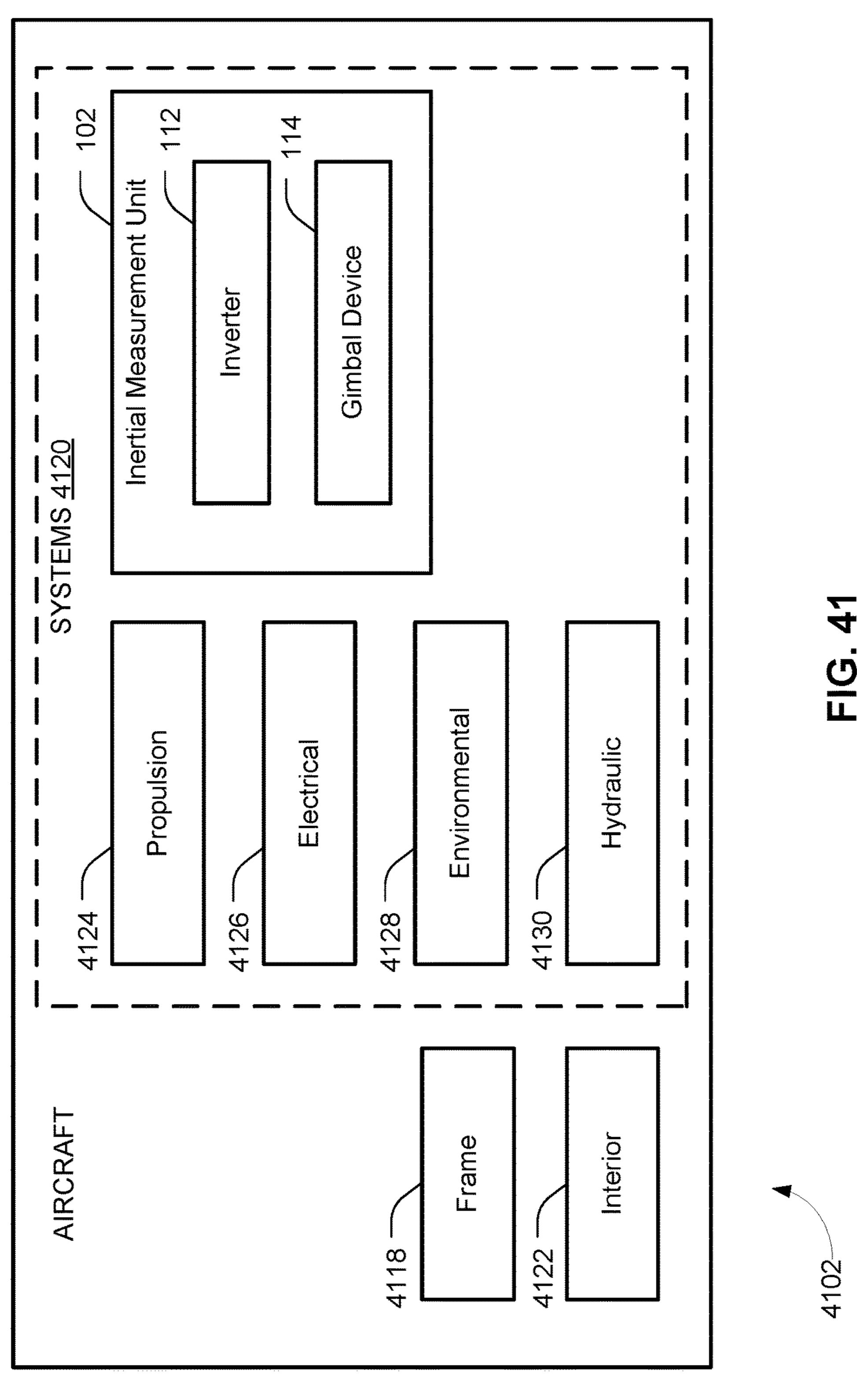

- FIG. **41** is a block diagram that illustrates an example of an aircraft including an inertial measurement unit.

## DETAILED DESCRIPTION

Implementations disclosed herein are directed to gimbaled inertial measurement units. A gimbaled inertial measurement unit includes sensors, such as accelerometers and gyroscopes, to determine vehicle inertia data, such as linear acceleration and angular velocity. In a gimbaled inertial measurement unit, an inertial measurement unit is mounted on a multi-axis gimbal device. The gimbal device includes multiple gimbals each with a corresponding motor. The motors are used to drive and position the gimbals such that the sensors are oriented along the vehicle's path. A control system of the vehicle tracks the position of the vehicle based on outputs from the sensors as the gimbals move based on changes in inertia of the vehicle. The control system then outputs commands to the gimbaled inertial measurement unit to adjust (readjust) the sensors such that the sensors are oriented along the vehicle's updated path.

In some implementations, the gimbaled inertial measurement unit uses a dual speed resolver for determining a position of the motor (e.g., a drive shaft of the motor) and thereby a position the sensors attached to the corresponding gimbal. The dual speed resolver determines the position of 40 the drive shaft of the motor using two resolvers each having a different "speed". A first resolver (e.g., a coarse resolver) may have a first speed that corresponds to a speed and a position (e.g., an absolute position) of the drive shaft. A resolver speed corresponds to a number of electrical cycles (e.g., a sine wave or a cosine wave) generated by a single mechanical revolution of the resolver. In a particular implementation, the first resolver is driven or rotated at the same rotational speed as the drive shaft, and thus an electrical cycle of the first resolver corresponds to a mechanical 50 revolution of the drive shaft. Accordingly, the absolute position of the drive shaft can be determined from the first

resolver. A second resolver (e.g., a fine resolver) has a second speed that is greater than the first speed and that corresponds 55 to a position of the drive shaft. For example, the second resolver may include multiple poles (e.g., pairs of coils) which generate multiple electrical cycles (e.g., sine waves) for a single mechanical revolution of the resolver (and the drive shaft). Alternatively, the second resolver may complete multiple mechanical revolutions for each revolution of the drive shaft. As compared to the first resolver (e.g., the coarse resolver), the second resolver (the fine resolver) has increased precision at the expense of not being able to determine a starting position (e.g., an absolute starting position). The second resolver can determine a more precise location of the drive shaft, but is unable to determine in which quadrant of a 360 degree rotation the drive shaft is in.

Dual speed resolvers (or dual resolvers) use outputs of both resolvers to determine a position of the drive shaft. For example, in conventional dual speed resolvers, outputs of both resolvers are input into a Kalman Filter to increase precision over a single resolver. However, the output of the coarse resolver has less accuracy and precision than the fine resolver and utilizing both the coarse and fine outputs reduces the accuracy and precision of the dual resolver to less than the accuracy of the fine resolver. By using the coarse resolver outputs to determine a starting position (e.g., 10 during an initialization process or time period) and the fine resolver outputs to determine subsequent positions (e.g., positions after the initialization process or time period), the accuracy and precision of the dual speed resolver is increased over conventional dual speed resolvers. Such a 15 dual speed resolver can be used to determine the absolute starting position and have the accuracy and precision of the fine resolver. Additionally, the fine resolver outputs can further be used to correct for a starting offset (error) of the coarse resolver. Furthermore, other methods described 20 herein can be combined to further increase the accuracy and precision of the dual speed resolver.

As explained above, a resolver receives excitation signals and in response generates an output signal. By adding dither (e.g., zero mean dither) to the excitation signal, the precision 25 of the angle determined from the resolver output is increased without increasing a speed of the resolver (e.g., a number of poles of the resolver) or a bandwidth (e.g., a sampling frequency of outputs of the resolver or a number of bits of the resolver outputs) of the processing circuitry. Zero mean 30 dither includes or corresponds to noise that does not alter a median amplitude value of the base excitation signal. Additionally, by time coordinating the dithered excitation signal with current drive switching signals of the gimbal motors, the dithered excitation signal can produce outputs that have 35 less noise and interference. Accordingly, the precision of the angle determined from the resolver output is increased without increasing a speed of the resolver or a bandwidth of the processing circuitry.

As explained above, resolver outputs are converted to 40 digital samples by an analog-to-digital converter (ADC) and the digital samples are demodulated during processing to determine the angle of the resolver and the drive shaft. During demodulation, the digital samples are rectified to produce a rectified signal. In some implementations, the 45 digital samples are rectified such that a phase of the excitation signal is preserved in the rectified signal. For example, conventional demodulators multiply the digital samples by the excitation signal to preserve the phase of when rectifying the digital samples. However, multiplying the digital 50 samples by the excitation signal generates noise. To illustrate, multiplying sine values of angles together reduces accuracy of the data between peaks of the sine waves, i.e., it squares any noise or errors.

improves a signal to noise ratio of off the data between peaks of the sine waves i.e., off peak voltages. Additionally, by flipping a sign of the square wave in accordance with the phase of the excitation signal, the phase of the digital samples and excitation signal can be preserved without 60 imparting additional noise or reducing the signal to noise ratio. Accordingly, the precision of the angle determined from the resolver output is increased without increasing a speed of the resolver or a bandwidth of the processing circuitry.

Additionally, recursive median value analysis and masking portions of the data further increases precision during

demodulation. Recursive median value analysis may be applied to the input digital samples and to the output amplitudes of the demodulator to further increase precision. For example, the demodulator may use a median value (a midvalue) of the last n input samples as the input value, where n is any integer greater than 1. As another example, the demodulator may output a midvalue of the last m output samples, where m is any integer greater than 1. Additionally or alternatively, the demodulator may output a midvalue of 3 different signals as the output value. The output value is used to determine the angle of the resolver and the drive shaft.

In some implementations, the demodulator masks portions of the data to eliminate noise and interference, which further increases precision of the gimbaled inertial measurement. The masked portion includes noisy data (data occurring during current drive switching and including current drive interference), data corresponding to a transition between peak amplitudes, or both. Thus, the demodulation improves results by using data near peak amplitudes of the excitation signal. Additionally or alternatively, demodulation outputs are based on a synced (synced with the excitation signal) accumulator output to further increase precision and reduce errors. For example, by synching the accumulator with the excitation signal that is time coordinated with current drive signals, the outputs of the accumulator can mask at least a portion of the current drive interference, average out the effects of the current drive interference, or both, leading to increased precision and accuracy.

The gimbaled inertial measurement unit also includes a feedback control system to control the gimbal motors. Gimbal motors are usually commanded or controlled by a direct rate command or a position command and a rate command. These commands may be received from user input or a vehicle's controller (e.g., a flight computer). Feedback control systems generally use a cascaded (e.g., multi-loop) tracking control law to process the position command and the rate command and to provide feedback. By using a combined rate and position feedback system (e.g., a single loop feedback system), lightly damped gimbal motors can be used with tight rate gains to achieve greater precision.

A pulse-width modulator (PWM) is used to drive the gimbal motors. The PWM controls activation of the gimbal motors based on the feedback control system. For example, when the gimbal motors correspond to 3-phase motors, the PWM controls the power delivery to the gimbal motors based on current commands generated by the feedback control system. To illustrate, the current commands are converted in a duty cycle value or signal. For example, the current commands are indicative of an amount of current to be provided to the motor. The duty cycle value (e.g., 50 percent) is determined based on the amount of current and Rectifying the digital samples with a square wave 55 a voltage of the power supply or motor. The duty cycle signal (e.g., a set point signal) indicates the duty cycle value. To illustrate, for an 8 bit duty cycle signal a value of 31 or 32 may indicate 50 percent duty cycle depending on which comparison condition is used. The duty cycle signal is sent to the PWM which generates pulses; a width of the pulses controls power delivery to the gimbal motors.

> The PWM generates the pulses based on comparing a counter value to a comparison value (indicative of a duty cycle value, such as 50 percent, 51 percent, etc.). For example, the PWM generates pulses based on determining whether the counter value is greater than or less than the comparison value. To illustrate, the PWM generates a first

pulse edge (e.g., activates a gate of a transistor) of a pulse when the counter value is greater than the comparison value and generates a second pulse edge (e.g., deactivates the gate of the transistor) of the pulse when the counter value is no longer greater than (does not exceed) the comparison value. 5 In conventional PWMs, increasing a precision or reducing granularity of control adjustment requires increasing an operating frequency of PWM components.

By utilizing an adjustable comparison criterion, PWM precision of control can be increased and control granularity 10 can be reduced without increasing the operating frequency of the PWM components. The adjustable comparison criterion may be indicated by a set point signal. The adjustable comparison criterion includes other comparison conditions or rules, such as a greater than or equal to condition and a 15 less than or equal to condition. PWM's utilize up-down counters which generate a counter signal that is a triangle wave. Thus, when adjusting the comparison value by one counter value (clock pulse), the PWM generate a first pulse one clock pulse earlier and a second pulse one clock pulse 20 later, leading to an increase in pulse-width of two clock pulses. However, when adjusting the comparison criterion, the PWM can generate a first pulse one clock pulse earlier and a second pulse at the same time, leading to an increase in pulse-width of one clock pulse. Accordingly, by using an 25 adjustable comparison criterion, a PWM has increased precision and reduced granularity of control adjustment of the motor without increasing an operating frequency of PWM components.

By utilizing one or more of the above improvements, a 30 gimbaled inertial measurement unit can offer greater precision in a smaller footprint over conventional gimbaled inertial measurement units. Additionally, the gimbaled inertial measurement unit can achieve the increased precision without increasing hardware capability. Accordingly, the 35 gimbaled inertial measurement unit enables a vehicle to inertial navigate safer due to the increased precision. Additionally, vehicles using the gimbaled inertial measurement unit may be smaller and lighter, leading to lower costs.

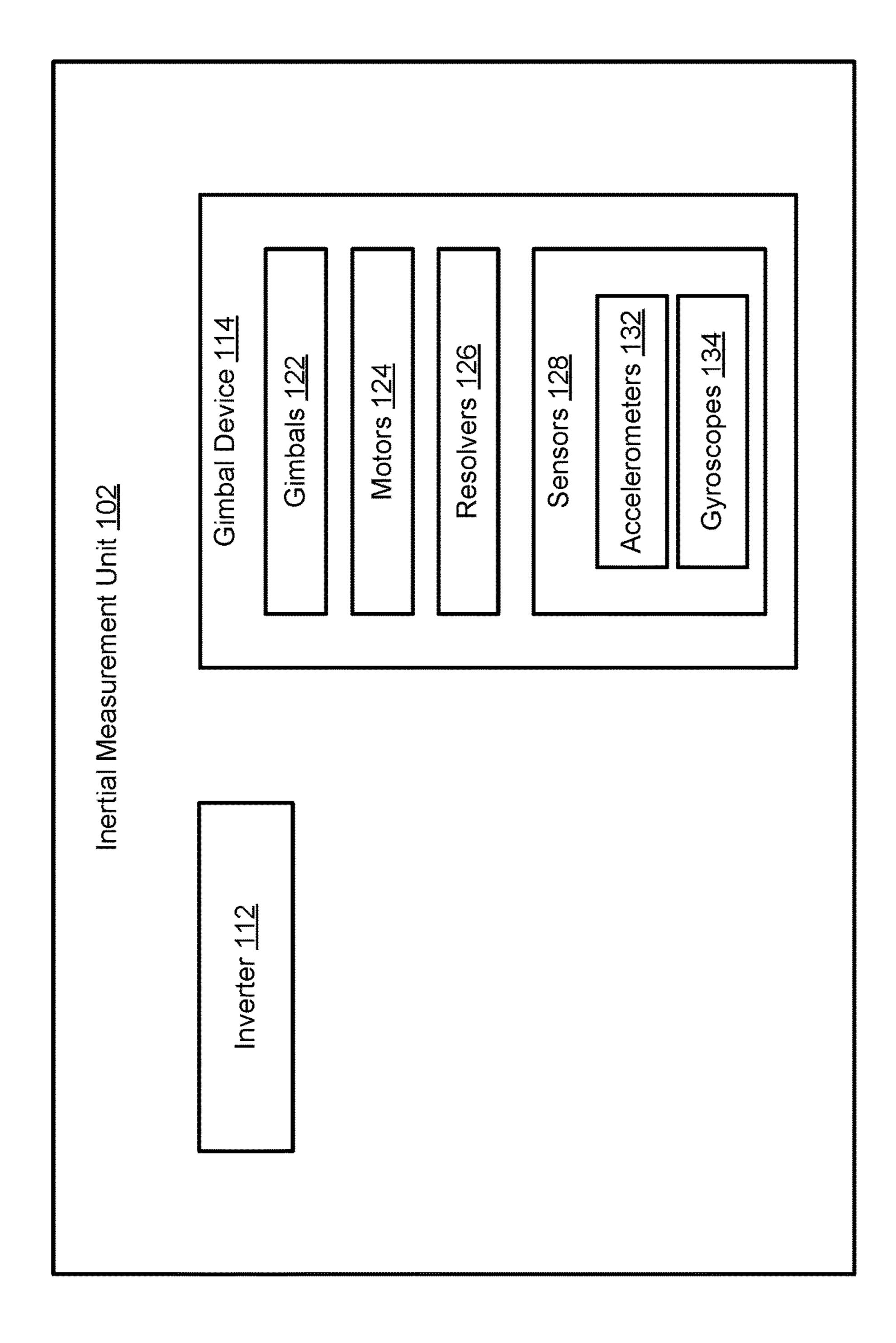

FIG. 1 is a diagram 100 that illustrates an example of an 40 inertial measurement unit 102, such as a gimbaled inertial measurement unit. In some implementations, the inertial measurement unit 102 is included in a vehicle (e.g., a ship, a submarine, an aircraft, a rocket, a satellite, a spacecraft, etc.) and is coupled to control system thereof, as shown in 45 FIGS. 2 and 41.

The inertial measurement unit 102 includes an inverter 112 and a gimbal device 114. The inverter 112 includes inverter electronics and firmware. The inverter **112** is configured to receive direct current (DC) power, convert the DC 50 power to alternating current (AC) power, and provide the AC power to the gimbal device **114**. For example, the inverter 112 is configured to provide power to control operation of the motors 124 of the gimbal device 114. The inverter electronics may include or correspond to a processor, a field 55 programmable gate array (FPGA), an application specific integrated circuit (ASIC), or a combination thereof. The firmware is configured to control operation of the inverter electronics. In some implementations, the inverter electronics and firmware include or correspond to a PWM, such as 60 the PWM 242 of FIG. 2, configured to control power delivery (e.g., current drive switching) to the motors 124.

The gimbal device 114 includes or corresponds to a multi-axis gimbal or a set of gimbals 122. The gimbal device 114 is configured to point the sensors 128 relative to a path 65 of the vehicle. In some implementations, the gimbal device 114 includes a three axis gimbal. In a particular implemen-

**10**

tation, the three axis gimbal includes a ball (e.g., a first axis gimbal 122), an inner shell (e.g., a second axis gimbal 122), and an outer shell (e.g., a third axis gimbal 122). In other implementations, the gimbal device 114 includes a two gimbal system or a four gimbal system.

The gimbal device 114 includes the motors 124. Each motor 124 is configured to drive or control a position of a corresponding gimbal 122 of the gimbal device 114 to orient the sensors 128 attached to the corresponding gimbal 122 in line with the path of the vehicle. The motors 124 may include or correspond to electric motors, such as a brushed electric motor or brushless electric motor.

The gimbal device 114 includes multiple resolvers 126. Each resolver 126 is configured to determine a position of a corresponding gimbal 122 of the gimbal device 114 such that the sensors 128 attached to the corresponding gimbal 122 can be oriented in line with the path of the vehicle. For example, each resolver 126 is coupled to a drive shaft of a corresponding motor 124 and outputs of each resolver 126 are used to determine a position of the drive shaft, and thus the position of the corresponding gimbal 122 and set of sensors 128.

The sensors 128 include accelerometers 132 and gyroscopes 134. The accelerometers 132 are configured to determine linear acceleration and the gyroscopes 134 are configured to determine angular velocity. For example, the accelerometers 132 and gyroscopes 134 generate sensor data indicative of linear acceleration and angular velocity or changes in linear acceleration and angular velocity. In some implementations, each gimbal 122 includes a set of sensors 128. Each set of sensors 128 includes one or more accelerometers 132 and one or more gyroscopes 134.

In some implementations, the sensors 128 further include magnetometers. In a particular implementation, each gimbal 122 of the gimbal device 114 further includes a magnetometer. The magnetometers are configured to detect a direction, a strength, or relative change of a magnetic field. Outputs of the magnetometers can be used to determine heading and/or position of the vehicle.

During operation of the vehicle, the vehicle may change its direction (e.g., a path, heading, or course). For example, the vehicle may change its direction from a first direction (e.g., an original direction) to a second direction (e.g., an updated direction). In response to the vehicle changing directions to the second direction, the inertial measurement unit 102 positions (e.g., repositions) the gimbals 122 of the gimbal device 114 to orient (e.g., point) the sensors 128 attached to the gimbals 122 along the second direction (e.g., the vehicle's current path or heading). The inertial measurement unit 102 positions the gimbals 122 of the gimbal device 114 based on the sensor data generated by the sensors 128 when the vehicle changed from the first direction to the second direction.

The vehicle may change its direction again. For example, the vehicle may change its direction from the second direction to a third direction. In response to the vehicle changing direction for the second time, the inertial measurement unit 102 positions (e.g., repositions) the gimbals 122 of the gimbal device 114 to orient (e.g., point) the sensors 128 attached to gimbals 122 along the third direction (e.g., the vehicle's current path). The inertial measurement unit 102 positions the gimbals of the gimbal device 114 based on the sensor data generated by the sensors 128 when the vehicle changed from the second direction to the third direction. Although, the above examples utilize a change in direction, the gimbal device 114 can sense any change in inertia (such as a change in speed along the same direction or heading) of

the vehicle and the inertial measurement unit 102 can position the gimbal device 114 responsive to the change in inertia of the vehicle. The inertial measurement unit 102 and components thereof are described further with respect to subsequent figures.

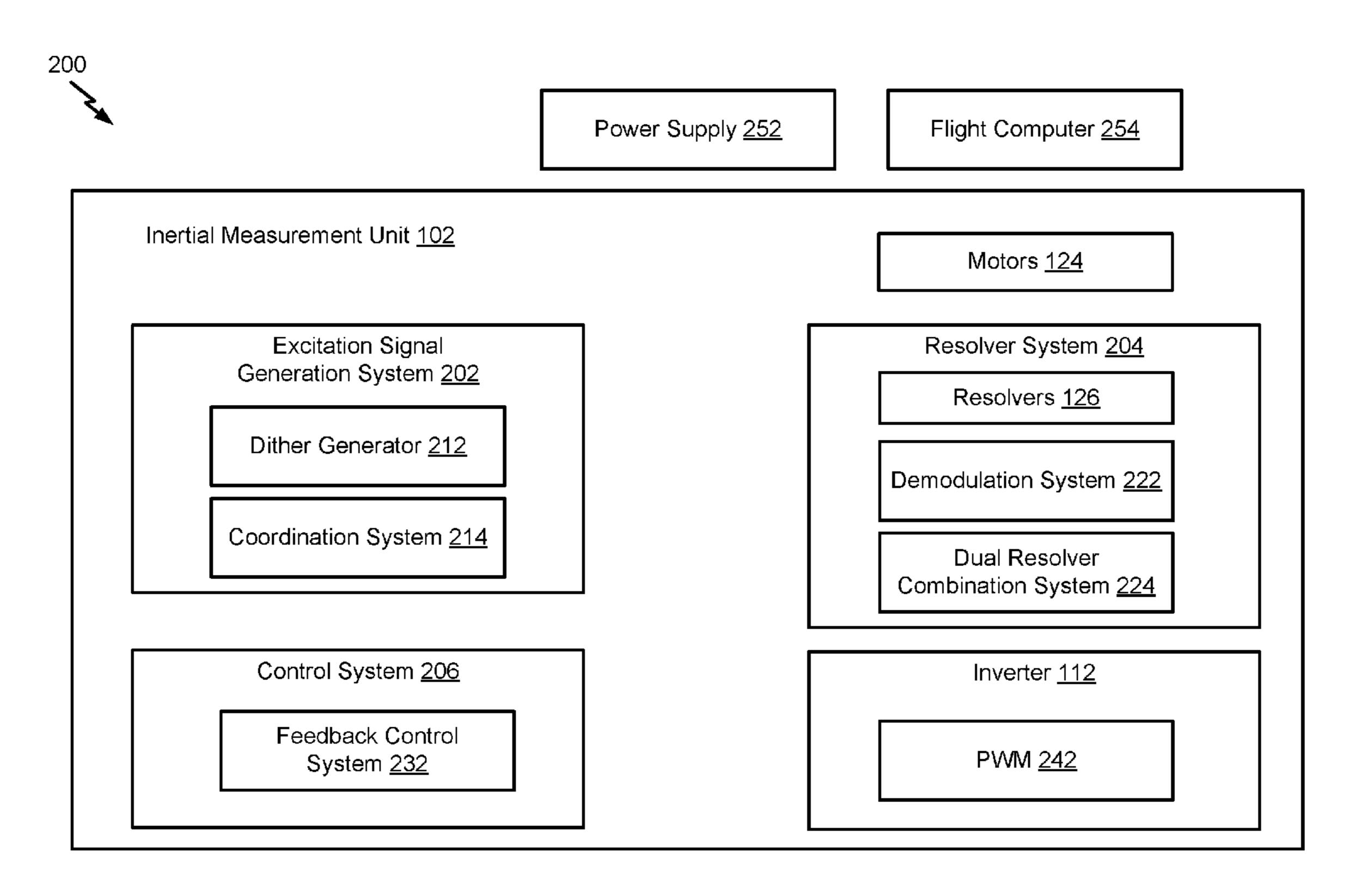

FIG. 2 illustrates a diagram 200 of an example of systems of the inertial measurement unit 102 of FIG. 1. In the diagram 200, the gimbal device 114 is not shown for clarity. In the particular example illustrated in FIG. 2, the inertial measurement unit 102 includes an excitation signal generation system 202, a resolver system 204, and a control system 206. Each of these systems, or subsystems thereof, improve the function of the inertial measurement unit 102 individually and in combination with the other systems, as will be described in more detail in subsequent figures. Additionally, 15 the inertial measurement unit 102 includes the inverter 112 and the motors 124 described with reference to FIG. 1.

The inertial measurement unit 102 and components thereof may be coupled to other equipment of the vehicle. As illustrated in FIG. 2, the inertial measurement unit 102 and 20 components thereof are coupled to a power supply 252 and a flight computer 254. In some implementations, the power supply 252 corresponds to a DC power supply of the vehicle, such as a battery or a generator. In other implementations, the power supply 252 may be included in the inertial 25 measurement unit 102, e.g., as an internal battery. The flight computer 254 may include or correspond to a flight control computer (FCC) or a guidance system configured to control the vehicle, such as cause a change in the course or direction of the vehicle responsive to user input or autonomously.

The excitation signal generation system 202 is configured to generate excitation signals and to output the excitation signals to the resolver system 204. The excitation signals are configured to cause the resolvers 126 to generate output signals indicative of a position of a drive shaft of the 35 corresponding motor 124, as described further with reference to FIG. 4.

The excitation signal generation system 202 includes a dither generator 212 and coordination system 214. The dither generator 212 is configured to generate and add dither 40 to the excitation signal (base excitation signal) to generate a dithered excitation signal. The dithered excitation signal enables more precise demodulation and more precise gimbal/motor control, which leads to better sensor outputs and increased precision of the inertial measurement unit 102, as 45 described further with reference to FIGS. 22-29.

The coordination system **214** is configured to coordinate the excitation signal (or dithered excitation signal) with current drive switching of the motors 124 to generate a coordinated excitation signal (or coordinated dithered exci- 50 tation signal). To illustrate, turning on and off transistors which provide power to the motors 124 may generate spikes, positive and negative spikes respectively. Waves of the excitation signal may be coordinated with (e.g., offset from) current drive switching such that a same number of transi- 55 tions from off to on and from on to off occur during each wave. Additionally, the current drive switching may be offset from peak amplitudes of the waves of the excitation signal. The coordinated excitation signal reduces noise and contamination of resolver outputs, which leads to better 60 sensor outputs and increased precision of the inertial measurement unit 102.

The resolver system 204 is configured to generate resolver outputs indicative of a position of the drive shafts of the motors 124 responsive to the excitation signals. The resolver 65 outputs are analog signals which are converted to digital samples by an ADC and processed to determine a position

12

(an angle) of the drive shaft. The resolver system 204 includes the resolvers, 126, a demodulation system 222, and a dual resolver combination system 224.

The demodulation system 222 is configured to demodulate the digital samples output by the ADC, as described further with reference to FIGS. 7-17. In some implementations, the demodulation system 222 performs recursive median value analysis to reduce or eliminate spikes in the digital samples input to the demodulation system 222, such as spikes caused by current drive switching and other interference. Additionally or alternatively, the demodulation system 222 includes an accumulator to reduce or eliminate spikes in the demodulation output of the demodulation system 222. The accumulator may also preform recursive median value analysis and masking (e.g., filtering) noisy data to reduce or eliminate spikes in the demodulation output.

The dual resolver combination system **224** is configured to generate angle estimations based on the demodulation outputs and to combine angle estimations from each resolver to determine the positions of the drive shafts, as described further with reference to FIGS. 18 and 19. The dual resolver combination system 224 uses the coarse resolver to determine a starting position of the drive shaft during an initialization process (e.g., an initialization mode). The starting position corresponds to an initial position of the drive shaft in absolute terms (0 to 360 degrees). The dual resolver combination system 224 uses the more accurate and precise 30 fine resolver outputs for determining subsequent positions of the drive shafts after the initialization process. In some implementations, the dual resolver combination system 224 includes a drift corrector to correct for drift. The drift corrector may use the fine resolver outputs to correct for an initial error (offset) of the starting position determined by the coarse resolver and to correct for integration errors of the fine resolver outputs.

The control system 206 includes a feedback control system 232. The feedback control system 232 is configured to receive flight control inputs from the flight computer 254, position feedback from the resolver system 204, and speed feedback (e.g., revolutions per minute (RPM) feedback) from the resolver system 204. The position feedback is indicative of a position (angle) of the motors 124 and the speed feedback is indicative of a rate, such as a rate of the motor in RPM.

The flight control inputs include a speed command (e.g., RPM command), a position command, or both. The feedback control system 232 generates a current command based on the flight control inputs, the position feedback, and the speed feedback, as described further with reference to FIGS. 30 and 31. The control system 206 converts the current command into a duty cycle setting or value used to control the motors 124. In some implementations, the duty cycle setting is indicated by a set point signal that indicates a comparison value and a comparison criterion.

The inverter 112 includes a PWM 242 configured to apply adjustable comparison criteria. The PWM is configured to receive the comparison value and one or more comparison criteria and to generate pulses of a pulse-width modulated signal based on the comparison value and one or more comparison criteria, as described with reference to FIGS. 33-35. The pulse-width modulated signal has increased precision or reduced granularity of control and is used to more precisely provide power from the power supply 252 to the motors 124. Operation of the inertial measurement unit 102 of FIG. 2 is described with reference to FIG. 3.

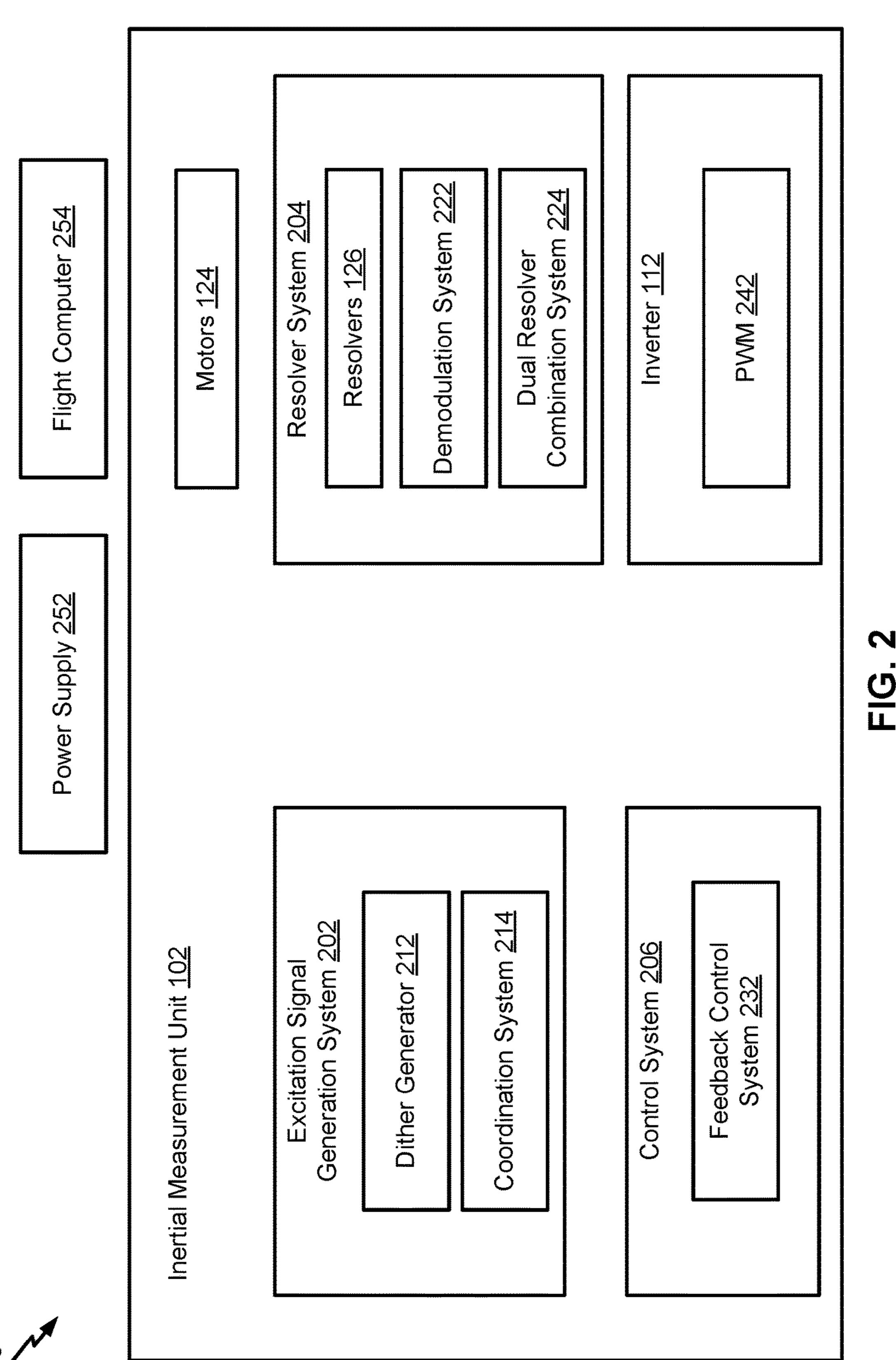

FIG. 3 is a diagram 300 that illustrates an example of operation of the inertial measurement unit 102. Diagram 300 corresponds to operation of a single motor 124 of the inertial measurement unit 102 and which positions the sensors 128 of a particular gimbal 122 (corresponding to the motor 124) of the gimbal device 114. In FIG. 3, cross hatching denotes operations or steps that may be time coordinated with each other. The time coordination can be achieved by using the same clock or counter, by synchronizing two or more clocks or counters, by offsetting two or more clocks or counters, or 10 a combination thereof, as described further with reference to FIGS. 27 and 28.

During operation of the inertial measurement unit **102**, the excitation signal generation system 202 generates a dithered excitation signal 352, coordinates the dithered excitation 15 signal with other components of the inertial measurement unit 102 (such as one or more cross hatched components), and provides the dithered excitation signal 352 to a digitalto-analog converter (DAC) 310. The DAC 310 converts the dithered excitation signal 352 into an analog signal and 20 provides the analog dithered excitation signal 352 to each resolver 342, 344 of the dual speed resolver 312. For example, the dual speed resolver 312 includes a 1 speed resolver and 16 speed resolver. Each resolver 342, 344 generates an output, such as a differential voltage output 25 **354**. For example, as illustrated in FIG. 3, the coarse resolver 342 outputs differential voltage output 354A (i.e., coarse position signals indicative of a course position) and the fine resolver outputs differential voltage output 354B (i.e., fine position signals indicative of a fine position).

The differential voltage outputs 354 are measured by corresponding differential voltage sensors 314, 316 to generate differential voltage signals 356. The differential voltage signals 356 generated by the differential voltage sensors 314, 316 are sampled by corresponding ADCs 318, 320. The 35 ADCs 318, 320 output digital samples of voltage values (referred to as ADC outputs 358) to voltage conditioning circuitry 322, 324 which correct for a voltage bias of the inertial measurement unit 102. The conditioned voltage values 360 are demodulated by the demodulation system 40 222 to generate demodulated outputs 362. Angle estimation circuitry 326 generates angle estimates 364 for both resolvers from the demodulated outputs 362. The angle estimates **364** are used to generate an estimated position **366** of the motor, such as an initial position and subsequent positions of 45 the motor, based on the demodulated outputs 362. One or more estimated positions 366 are used to determine an estimated RPM 368 of the motor. Additionally, the estimated positions 366 may be adjusted (tared) to account for the motor **124**, such as to account for commutation and servo 50 offset. Adjusting (taring) the estimated positions 366 generates a magnetic rotor position and a mechanical rotor position, such as tared position outputs. The estimated RPM 368 may be determined based further on the magnetic rotor position and the mechanical rotor position. The estimated 55 position 366 and the estimated RPM 368 of the motor 124 are provided to the feedback control system 232 to be used as feedback, i.e., position feedback and RPM feedback, for controlling the motor 124.

The feedback control system 232 receives commands 370 from the flight computer 254, such as a position command and an RPM command. The feedback control system 232 generates a rate limited position command based on the position command and the RPM command. The feedback control system 232 generates a current command 372 based 65 on the rate limited position command, the position feedback, and the RPM feedback. The current command 372 may

**14**

correspond to a torque command or indicate an amount of torque of the motor 124. The current command 372 is provided to a current tracker 330 to generate a duty cycle value 374. The duty cycle value 374 may be in terms of a two phase reference frame (e.g., a two phase reference frame of direct and quadrature, with quadrature corresponding to torque). An inverse Park/Clark transformation 332 can be applied to the duty cycle value 374 to convert the duty cycle value 374 to one or more duty cycle settings 376 for a three phase motor, such as a duty cycle in terms of A, B, and C lanes (phases) of the three phase motor. The one or more duty cycle settings 376 (e.g., set point signals) are sent to the PWM 242.

The PWM 242 receives the one or more duty cycle settings 376, each duty cycle setting 376 indicating a comparison value and two comparison criteria. The PWM 242 may receive one duty cycle setting 376 for each lane (A, B, and C) or may receive one duty cycle setting 376 for a particular lane and generate duty cycle settings 376 for each other lane based on the received duty cycle setting 376. The PWM 242 controls gate drivers 334 of transistors 336 (metal-oxide-semiconductor field-effect transistors (MOS-FETs)) of the inverter 112 based on the comparing the comparison value to a counter value based on the two comparison criteria for each lane.

The PWM 242 is configured to generate (or cause the gate drivers 344 to generate) pulse-width modulated signals 378. The PWM 242 generates pulses (a pulse for each comparison criteria) of the pulse-width modulated signals 378 for each lane, and the pulses activate and deactivate the transistors 336 (i.e., current drive switching). By activating the gate drivers 334, the PWM 242 controls power delivery from the power supply 252 to the motors 124. The PWM 242 and the inverter 112 convert the DC power from the power supply 252 into three phase AC power signals 380 with increased precision for controlling the motors 124.

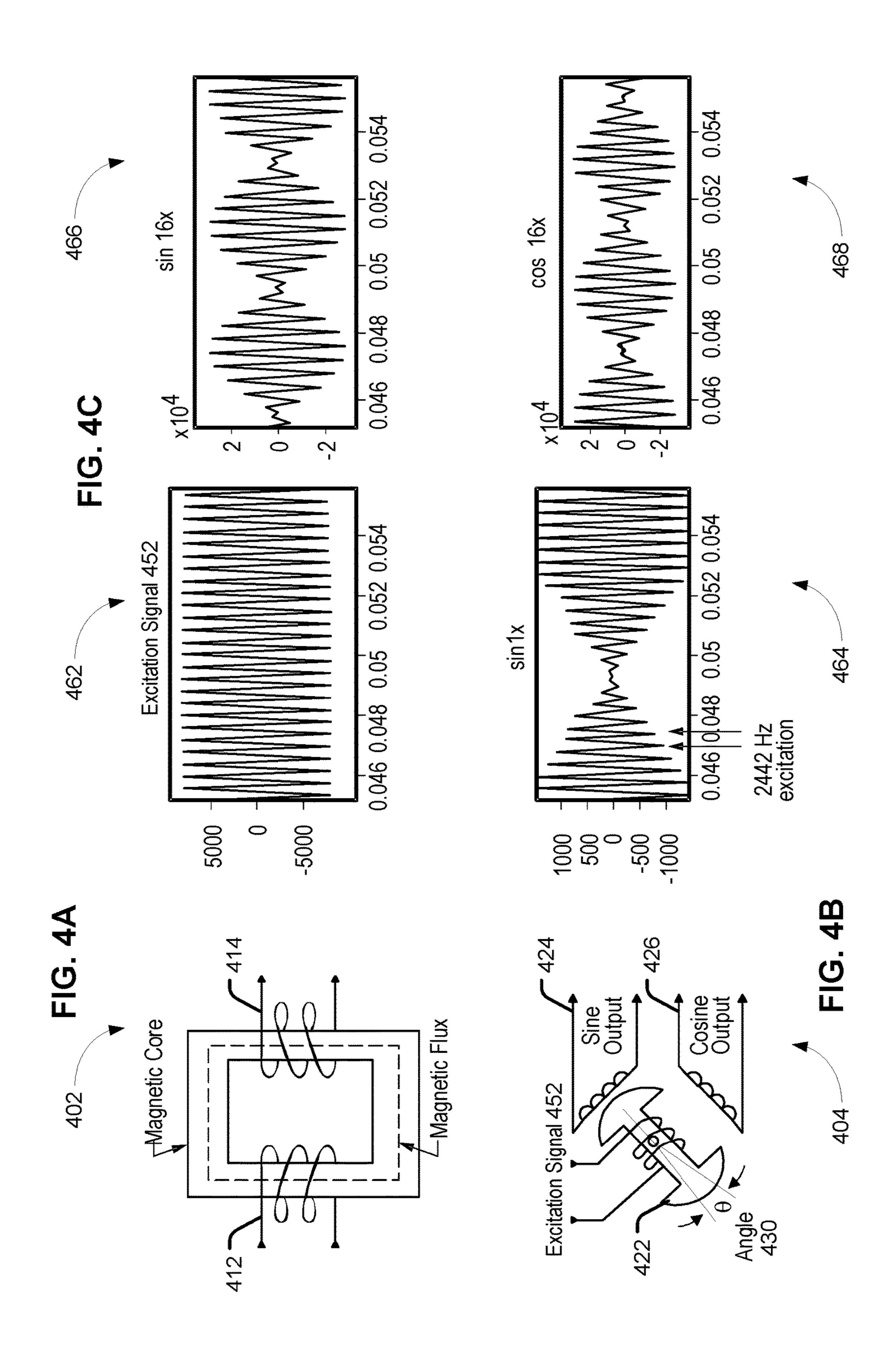

FIGS. 4A-4C illustrate example operation of a resolver. FIG. 4A illustrates a diagram of an example of a transformer 402, two coils 412, 414 of wire (referred to as "windings") wrapped around a magnetic core. A change in current applied to an input coil 412 creates a varying magnetic flux and varying magnetic field at an output coil 414. The varying magnetic field at the output coil 414 induces voltage in the output coil 414. A resolver operates using a rotatable transformer and outputs induced voltage.

FIG. 4B illustrates a diagram of an example of a resolver 404. The resolver 404 is an analog sensor configured to determine rotational position of a rotating component. The resolver 404 is an active sensor, i.e., it receives an excitation signal, such as the dithered excitation signal 352 of FIG. 3, which causes (induces) an output signal.

The resolver 404 includes three coils 422-426 forming a rotatable transformer. The resolver 404 includes a rotatable primary coil 422 (first coil) and two secondary coils 424, 426 (sine and cosine coils). The secondary coils 424, 426 may include or correspond to pairs of poles, e.g., 2n poles. Each pole is angularly offset from the other pole, such as by 90 degrees. Each pair of poles has a pole configured to deliver a sine output and another pole configured to deliver a cosine output. As the primary coil 422 rotates, the primary coil 422 receives the excitation signal 352 and induces voltage in the secondary coils 424, 426 may output a differential output, such as the differential voltage outputs 354 of FIG. 3. The ratio between the voltages of the secondary coils 424, 426 represents an angle 430 of the resolver 404 (which indicates an

angle of the motor 124). The resolver 404 in FIG. 4B is a two pole resolver and is a single speed resolver, e.g., the coarse resolver 342 of FIG. 3.

In multispeed resolvers, the multispeed resolver (e.g., the fine resolver 344) has a higher number of electrical cycles 5 per rotation of the multispeed resolver (and the component being tracked). For example, the multispeed resolver can be a multipole resolver and extra pairs of poles (coils) can be added to the resolver 404 to produce more electrical cycles per one mechanical rotation of the primary coil 422 (and the 10 component being tracked). As another example, the primary coil 422 of the multispeed resolver can be geared relative to the component being tracked such that one mechanical rotation for of the component being tracked causes more than one rotation of the primary coil 422.

FIG. 4C illustrates exemplary graphs 462-468 of signals of the dual speed resolver 312 of FIG. 3. Each of the graphs 462-468 of FIG. 4C corresponds to the same interval of time, which corresponds to a partial rotation of the resolvers 342, 344 of the dual speed resolver 312. A first graph 462 depicts 20 voltages of an excitation signal 452 (an AC signal) over the interval of time supplied to both resolver 342, 344. As illustrated in FIG. 4C, the excitation signal 452 has a frequency of 2442 Hertz. In other implementations, the excitation signal is a dithered excitation signal, such as the 25 dithered excitation signal 352 of FIG. 3 and illustrated in FIG. 23. The excitation signal 452 (base excitation signal) is depicted in FIG. 4 for illustrative purposes.

A second graph 464 depicts voltage outputs of the sine secondary coil 424 of the coarse resolver 342 (e.g., the 30 resolver 404) over the interval of time. A third graph 466 and a fourth graph 468 depict voltage outputs of the fine resolver **344** over the interval of time. As illustrated in FIG. **4**C, the fine resolver **344** is a 16 speed resolver and the third graph 466 depicts voltage outputs of the sine secondary coil 424 35 and the fourth graph 468 depicts voltage outputs of the cosine secondary coil 426 of the fine resolver 344. As compared to the voltage outputs of the sine secondary coil 424 of the coarse resolver 342 of the second graph 464, the voltage outputs of the sine secondary coil 424 of the fine 40 resolver 344 of the third graph 466 have higher voltages, a higher cycle frequency, and complete multiple electrical cycles over the interval of time. As compared to the voltage outputs of the sine secondary coil 424 of the fine resolver **344** of the third graph **466**, the voltage outputs of the fine 45 resolver 344 of the cosine secondary coil 426 of the fourth graph 468 have the same cycle frequency but are offset (e.g., out of phase) relative to the third graph 466. The voltage outputs of the cosine secondary coil **426** of the fine resolver **344** of the fourth graph **468** are also offset from the exci- 50 tation signal 452 of the first graph 462. Processing of resolver outputs, e.g., demodulation and angle combination, are described with reference to FIGS. 5-21. Generation of excitation signals for the resolver 404 are described with reference to FIGS. 22-28.

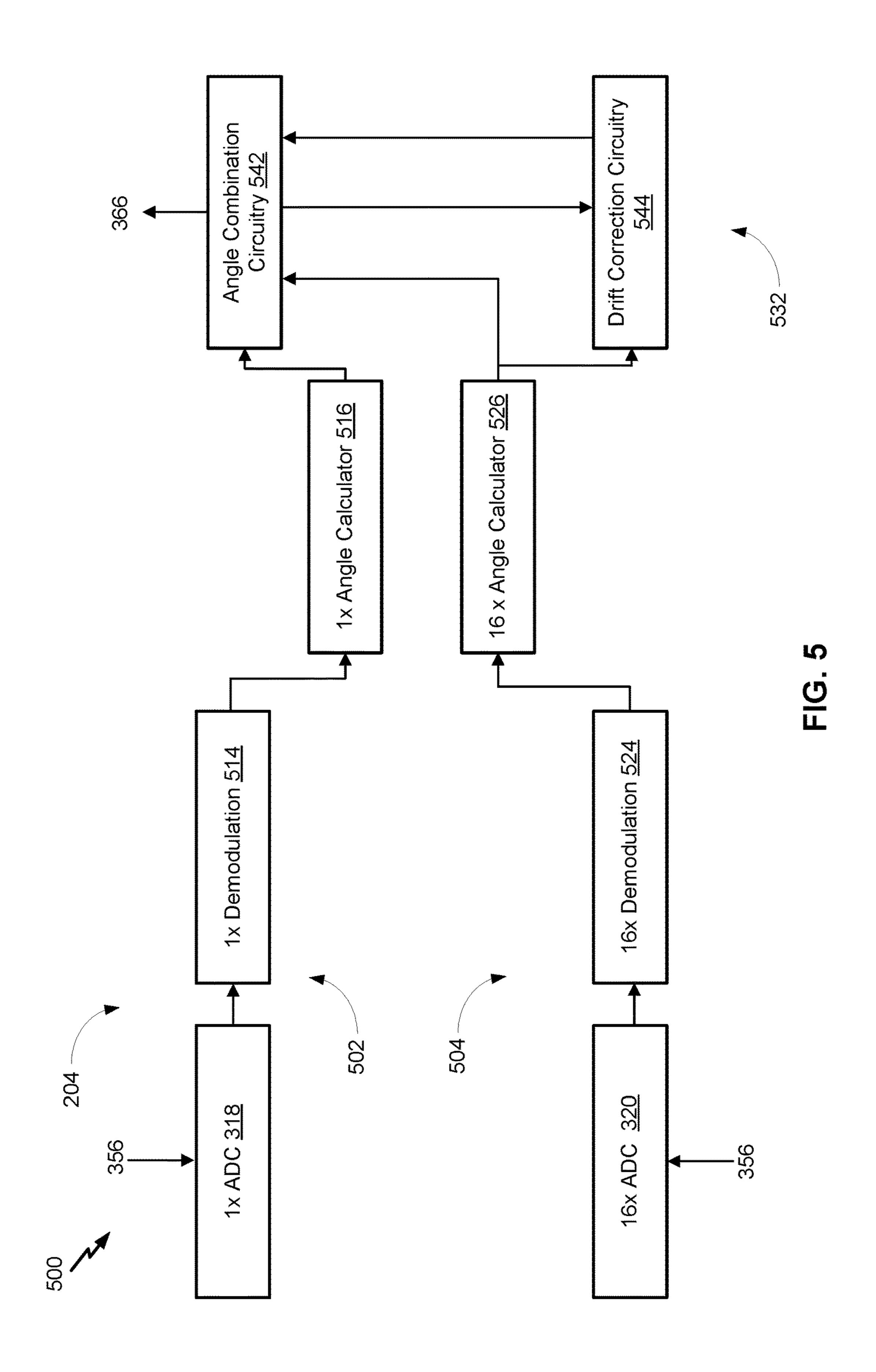

FIG. 5 is a diagram 500 that illustrates an example of flow processing for processing resolver outputs for the dual speed resolver 312 of FIG. 3. As illustrated in FIG. 5, the resolver system 204 includes two processing chains 502, 504, one for each resolver of the dual speed resolver 312. The processing chains 502, 504 include the ADCs 318, 320, demodulation circuitry 514, 524, and angle calculation circuitry 516, 526. Outputs from each processing chain 502, 504 are input into output circuitry 532.

As illustrated in FIG. 5, the output circuitry 532 includes 65 angle combination circuitry 542 and drift correction circuitry 544. A position of the drive shaft of the motor can be

**16**

determined based on outputs from the angle combination circuitry 542 and the drift correction circuitry 544.

During operation, the coarse resolver 342 (e.g., a first resolver or one speed resolver) of FIG. 3 outputs coarse position signals to an input of the first ADC 318, and the fine resolver 344 (e.g., a second resolver or a multi-speed resolver) of FIG. 3 outputs fine position signals to an input of the second ADC 320. In the example illustrated in FIG. 5, the ADCs 318, 320 receive the differential voltage signals 356 of FIG. 3. In a particular implementation, the fine position signals are 16 speed. The coarse and fine position signals include analog sine and cosine waves. In a particular implementation, the coarse and fine position signals each include a differential sine signal and a differential cosine signal.

The ADCs 318, 320 convert the analog outputs of the resolvers into digital samples. The digital samples output by the ADCs 318, 320 are received by the corresponding demodulation circuitry 514, 524. The demodulation circuitry 514, 524 demodulates the digital samples to produce amplitudes of the sine and cosine waves. In a particular implementation, the amplitudes include sign information, i.e., are "signed" and indicate whether the sample is positive or negative. Details of the demodulation are described further with reference to FIGS. 6-17.

The amplitude outputs of the demodulation circuitry 514, 524 are received by the corresponding angle calculation circuitry 516, 526. The angle calculation circuitry 516, 526 calculates estimated angles of the drive shaft using the sine and cosine amplitudes. In a particular implementation where the amplitudes include sign information, the angle calculation circuitry 516, 526 calculates the estimated angles of the resolvers 342, 344 (which are indicated of angles of the drive shaft) using arctan 2 (commonly abbreviated as atan 2). The atan 2 function is a four quadrant inverse arc tangent function capable of determining which quadrant the drive shaft is in based on the signed amplitudes.

The estimated angles of the drive shaft from each of the angle calculation circuitry 516, 526 are provided to output circuitry 532. In the example illustrated in FIG. 5, the angle combination circuitry 542 receives both estimated angle outputs, and the drift correction circuitry 544 receives the multispeed estimated angle output.

The angle combination circuitry **542** combines the estimate angles (e.g., the angle estimates **364** of FIG. **3**) from each angle calculation circuitry **516**, **526** to determine a starting position (an initial estimated position **366** of FIG. **3**) of the drive shaft and subsequent positions of the drive shaft. In a particular implementation, the angle combination circuitry **542** uses estimated angle outputs from the first angle calculation circuitry **526** to determine the starting position and uses estimated angle outputs from the subsequent positions of the drive shaft. Alternatively, the angle combination circuitry **542** uses both estimated angle outputs to determine the starting position and uses estimated angle outputs from the second angle calculation circuitry **526** to determine the subsequent positions of the drive shaft.

The drift correction circuitry **544** corrects for errors that are produced when combining the two estimated angles. For example, when determining the starting and subsequent positions of the drive shaft includes differentiation of the multispeed estimated angles, noise and integer error may be introduce into outputs of the angle combination circuitry **542**. To correct for the noise and integer error, the angle combination circuitry **542** receives, an estimated position from the angle combination circuitry **542**. The drift correc-

tion circuitry **544** generates a drift correction output based on the multispeed estimated angles from the second angle calculator. The drift correction circuitry **544** provides the drift correction output to the angle combination circuitry **542**. The angle combination circuitry **542** adjusts subsequent 5 outputs (subsequent estimated positions 366 of FIG. 3) based on the drift correction output. Details of the angle combination circuitry 542 are described further with reference to FIGS. 6, 7, and 18, and details of the drift correction circuitry **544** are described further with reference to FIGS. 10 **6**, **7**, and **19**.

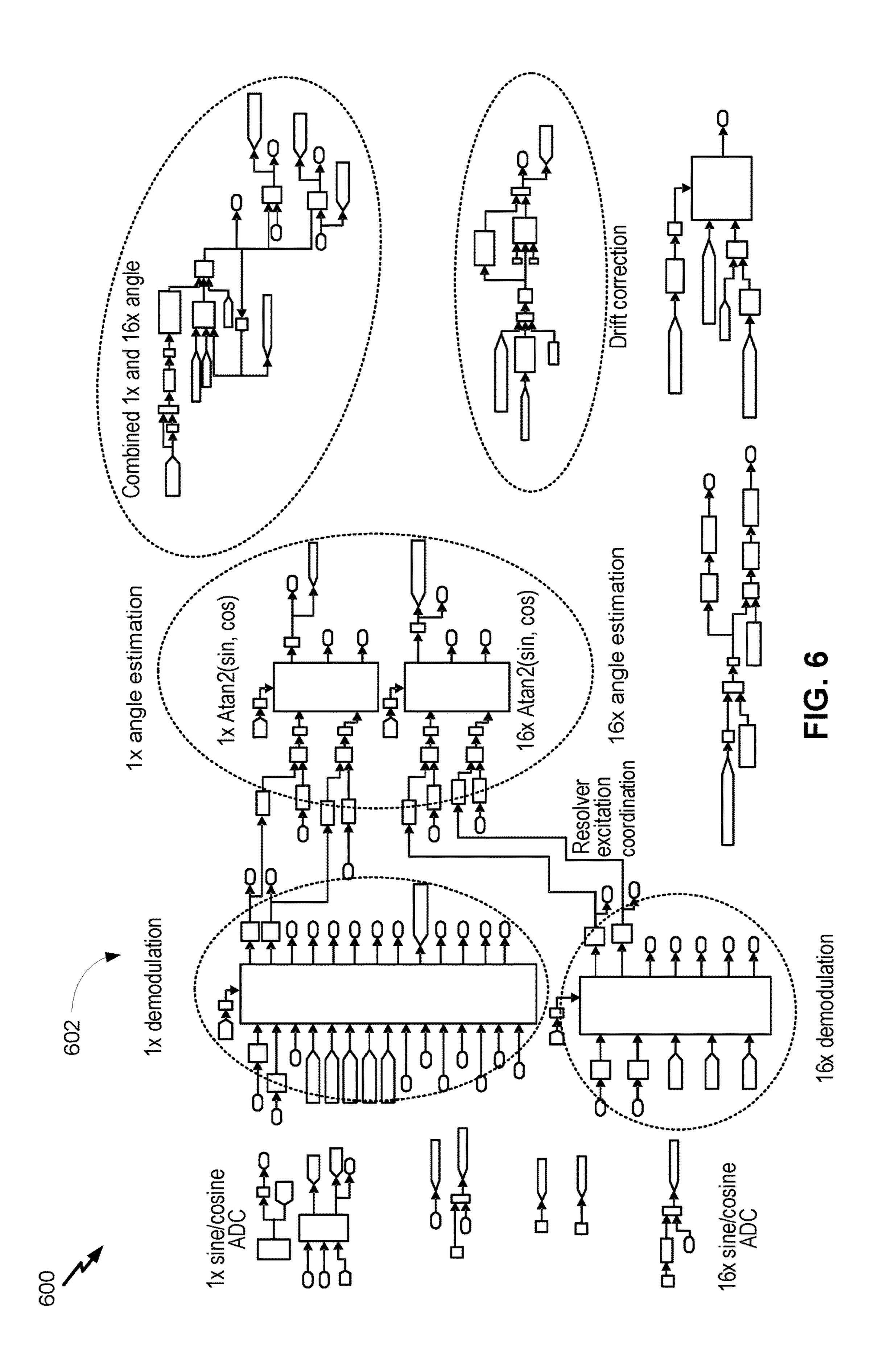

FIG. 6 is a logic diagram 600 that illustrates an overview of an example of logic 602 for processing resolver outputs of the dual speed resolver 312 of FIG. 3. The logic diagram **600** depicts an overview of conversion of resolver outputs to 15 ADC outputs, demodulation of the ADC outputs, angle estimation based on the demodulated outputs, and a combined position output based on the angle estimations. Each circled portion of the logic diagram 600 is described in further detail with respect to FIGS. 7-19. Logic or portions 20 thereof of FIG. 6 and subsequent FIGS. may be performed by one or more application specific circuits (circuitry), an FPGA, firmware (such as firmware of an FPGA), software executed by a processor, or a combination thereof. Additionally, the logic (or portions thereof) disclosed herein may 25 be replaced by equivalent logic. For example, any logic gate can be represented by one or more NOR logic gates.

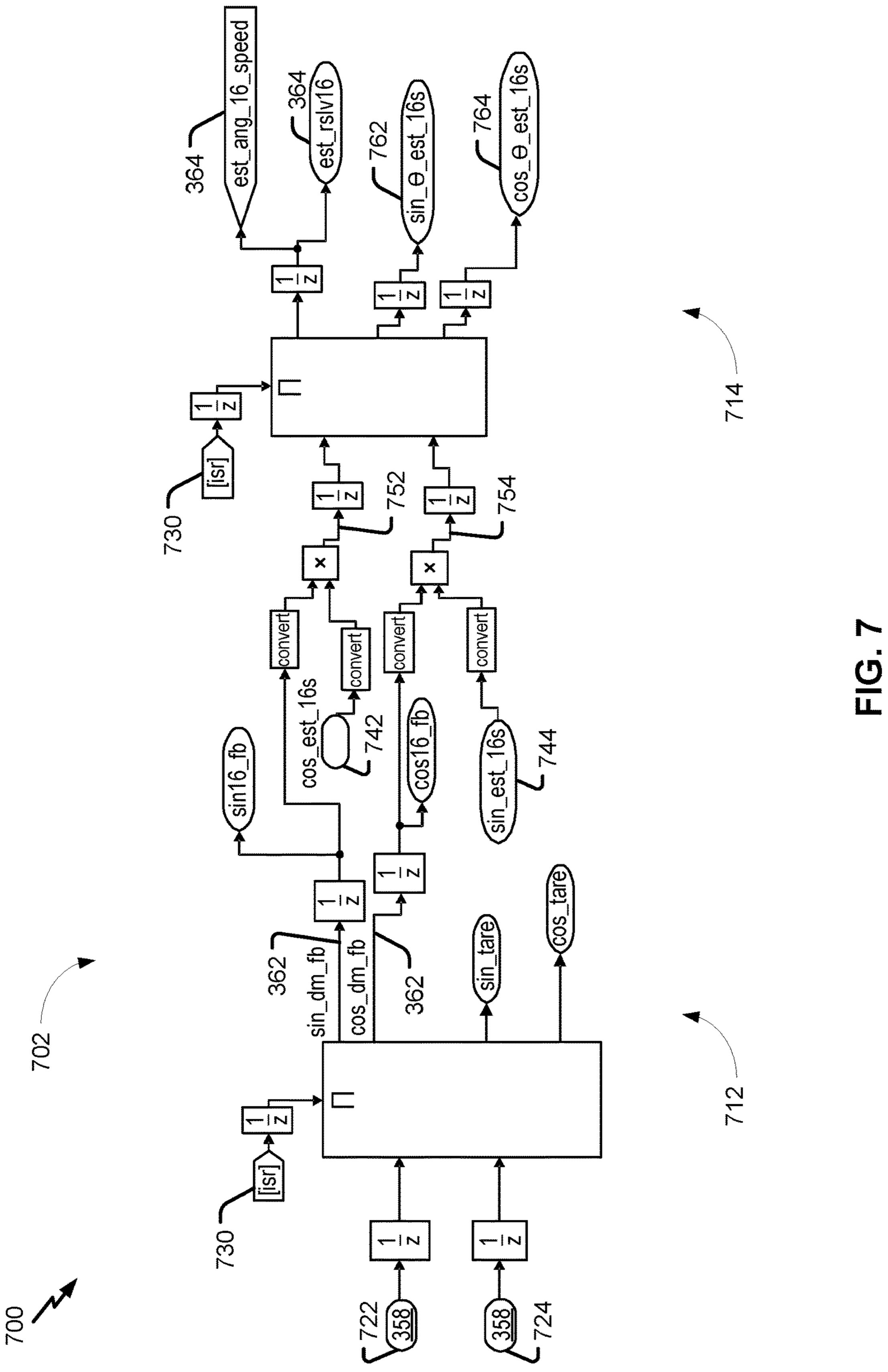

FIG. 7 is a logic diagram 700 that illustrates an overview of an example of logic 702 for demodulation and angle estimation. The logic 702 depicts demodulation and angle 30 estimation for a single resolver of the dual speed resolver 312. As illustrated in FIG. 7, the logic 702 corresponds to logic for demodulation and angle estimation for the fine resolver 344 (e.g., 16 speed) of FIG. 3.

estimation logic 714. The demodulation logic 712 is configured to the receive the resolver outputs (e.g., the differential voltage outputs 354) via the ADC 320 as the ADC outputs 358 and to output the demodulated outputs 362 to the angle estimation logic 714, as described further with 40 reference to FIGS. 8-17. The angle estimation logic 714 is configured to receive the demodulated outputs 362 (demodulated amplitude values) and calculate the angle estimates 364 for the resolvers, as described further with reference to FIGS. 18 and 19.

In some implementations, the angle estimation logic 714 is configured to calculate the angle estimates 364 based on a function of atan 2 (e.g., four quadrant inverse arc tangent). For example, the angle estimation logic **714** is configured to generate angle estimates 364 based on a product of the 50 demodulated outputs 362 (demodulated amplitude values) and based on sine and cosine feedback angle values 742, **744**.

By calculating the angle estimates 364 based on a function of atan 2, the angle estimates **364** indicate which 55 quadrant the motor is in. To illustrate, an angle output by atan 2 is from 0-360 degrees (as opposed to 0 to 90 degrees). The function atan 2 uses signed input angles to determine the specific quadrant (i.e., 0-90, 90-180, 180-270, or 270-360 degrees).

In some implementations, the demodulation logic 712 is further configured to adjust (tare) for voltage bias and other biases of the hardware, as described further with reference to FIG. 8. In some implementations, the angle estimation logic 714 is further configured to output estimated angle 65 outputs for the sine and cosine values in addition to the angle estimates 364.

**18**

During operation, the demodulation logic 712 receives digital samples from an ADC. For example, the demodulation logic 712 receives the ADC outputs 358 from the one of the ADCs 318, 320. The digital samples represent voltages of the sine and cosine coils 424, 426 of the resolvers 342, 344 of the dual speed resolver 312. As illustrated in FIG. 7, the digital samples correspond to sine and cosine inputs from the fine resolver **344**. The digital samples are demodulated to produce demodulated sine and cosine outputs 362. Multiple demodulated outputs 362 may be referred to as demodulated feedback or a demodulated feedback signal. In a particular implementation, the demodulation logic 712 generates a median value of the past three demodulated outputs 362 and outputs the median value as next the demodulated output 362 of the demodulated feedback signal. Detailed operation of the demodulation logic 712 is described further with reference to FIGS. 8-16.

The demodulated outputs 362 are multiplied by the sine and cosine feedback angle values 742, 744 to generate products 752, 754. To illustrate, the sine demodulated outputs 362 are multiplied by the cosine feedback angle values 744 to generate first products 752. The cosine demodulated outputs 362 are multiplied by the sine feedback angle values 746 to generate second products 754. The sine and cosine feedback angle values 742, 744 may be generated by the angle estimation logic 714 as sine and cosine estimated angle values 762, 764 and provided to the logic 702. For example, the sine and cosine estimated angle values 762, **764** are generated based on the demodulated outputs **362**. To illustrate, the sine estimated angle values 762 are calculated based on the first product 752 of the sine feedback angle values 742 and values (amplitudes) of the sine demodulated outputs 362.

The angle estimation logic 714 receives the products 752, The logic 702 includes demodulation logic 712 and angle 35 754 of the demodulated outputs 362 and the sine and cosine feedback angle values 742, 744 and generates the angle estimates 364 based on the demodulated outputs 362. For example, the angle estimation logic 714 generates the angle estimates 364 based on the function at 2 (i.e., four quadrant inverse arc tangent). To illustrate, a particular angle estimate **364** is calculated by applying the function at an 2 to a value (angle) of an integral of the product 752 minus the product 754, i.e., integral (sine\_amplitude\* $\cos(\theta)$ cosine\_amplitude\* $sin(\theta)$ -0). In such implementations, the demodulated outputs **362** are signed, i.e., include sign information. As explained with reference to FIGS. 7, 18, and 19, the angle estimates 364 indicated by the fine resolver 344 may be used in combination with the angle indicated by the coarse resolver 342 to generate an initial position and subsequent positions of the drive shaft of the motor 142.

> In some implementations, the demodulation logic 712, the angle estimation logic 714, or both, are configured to receive an interrupt service routine (ISR) input 730. The ISR input 730 is a Boolean value indicating an interrupt service routine mode. The demodulation logic 712, the angle estimation logic 714, or both, stop generating outputs responsive to receiving the ISR input 730.

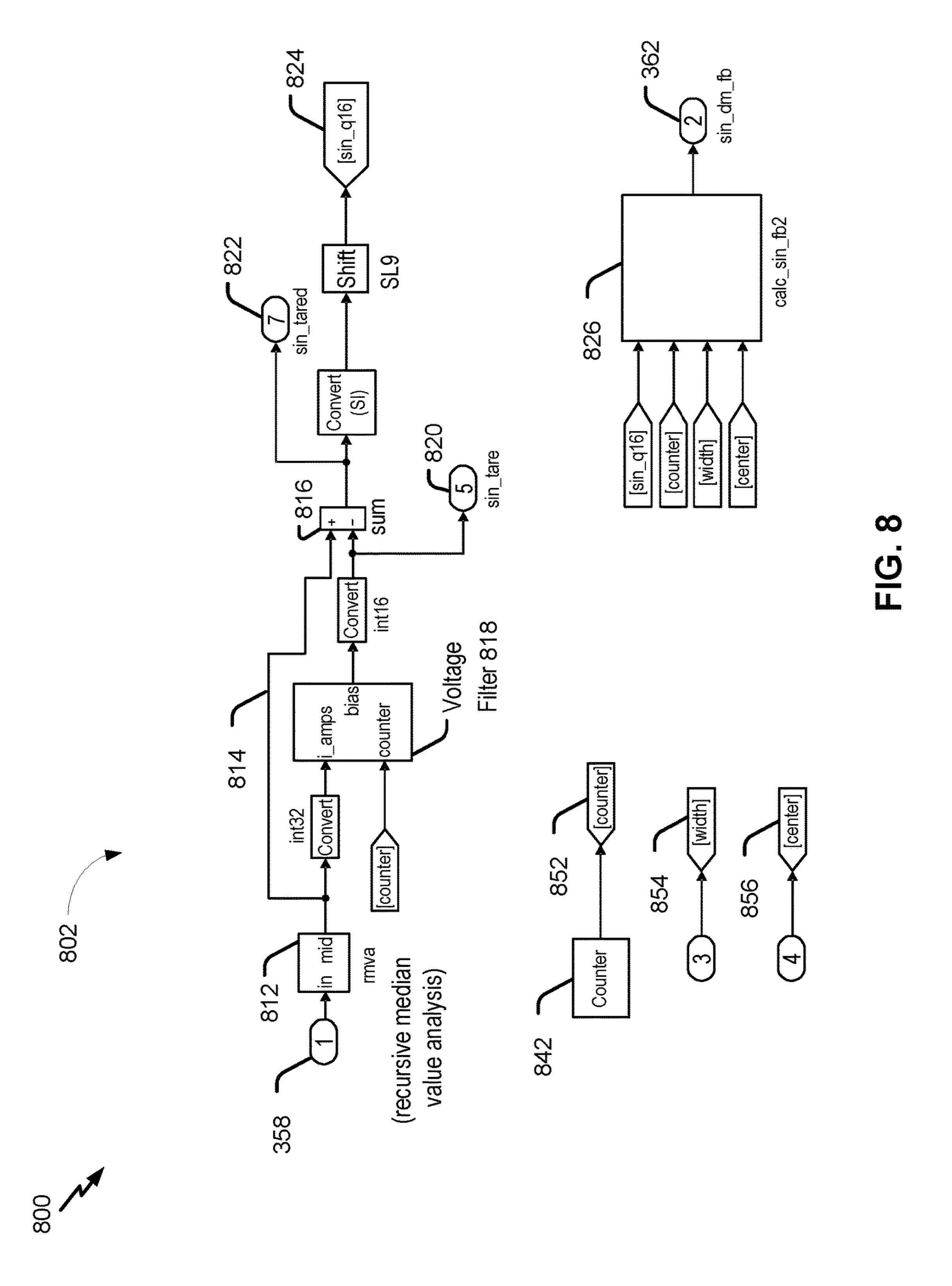

FIG. 8 is a logic diagram 800 that illustrates an example of logic 802 for voltage conditioning. The logic 802 is 60 configured to receive voltage values from a sensor, condition the voltage values to remove hardware bias, and output demodulated output values. In the particular example illustrated in FIG. 8, the logic 802 receives a voltage value measured by the differential voltage sensor 316 corresponding to the sine coils 424 of the fine resolver 344 and calculates the demodulated output 362 for the fine resolver **344**.

The logic **802** includes recursive midvalue analysis (RMVA) logic **812**, a voltage filter **818**, and a combiner **816**. The RMVA logic **812** is configured to determine a median (midvalue) of the last n number of input values or samples, where n is an integer of greater than 1. The RMVA logic **812** 5 is described further with reference to FIG. **9**.

During operation, the logic **802** receives multiple voltage values from the ADC **320** corresponding to the voltage at the sine coils **424** of the fine resolver **344** (e.g., a 16 speed resolver) measured by the differential voltage sensor **316**. 10 The RMVA logic **812** receives the multiple voltage values and outputs a midvalue voltage value **814** to the combiner **816**. The voltage filter **818**, such as a low pass filter, generates a voltage bias output **820**, sin tare as illustrated in FIG. **8**, based on the midvalue voltage value **814** and the 15 counter input **852**. The voltage bias output **820** corresponds to a voltage bias of or imparted by the hardware of the inertial measurement unit **102**. For example, the voltage bias output **820** may correct for a voltage drop associated with an FPGA of the inertial measurement unit **102**.

In a particular implementation, the midvalue voltage value **814** is converted to a higher bit value, such as from a 16 bit value to a 32 bit value. Converting from 16 bit to 32 bit (increasing a number of bits) reduces or eliminates a loss of precision caused by the voltage filter **818**. For example, 25 any right shifts by the voltage filter **818** do not cause a loss of precision.

The combiner **816** generates an adjusted voltage value **822** (e.g., the conditioned voltage value **360** of FIG. **3**) based on the midvalue voltage value **814** and the voltage bias 30 output **820**. As illustrated in FIG. **8**, the adjusted voltage value **822** is a difference of the midvalue voltage value **814** and the voltage bias output **820**. The adjusted voltage value **822** may be converted to a signed integer and shifted before demodulation. The adjusted voltage value **822** may be 35 output to the demodulation logic **826** and stored as an input voltage value **824**.

The demodulation logic **826** generates the demodulated output **362** based on the input voltage value **824**, the counter input **852**, the width input **854**, and the center input **856**. 40 Generation of the demodulated output **362** and examples of the RMVA logic **812** demodulation logic **826** are described further with reference to FIGS. **9-17**.

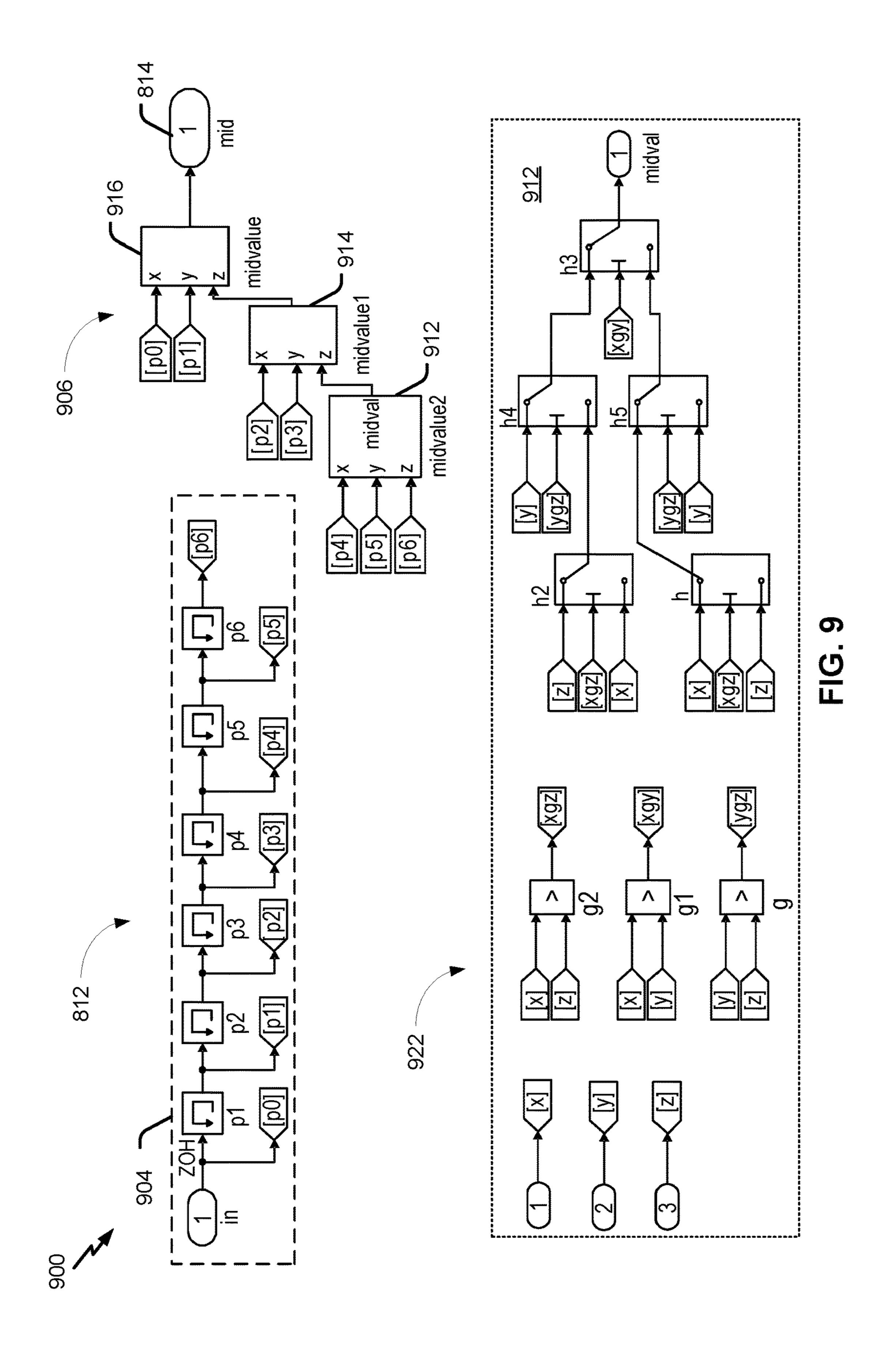

FIG. 9 is a logic diagram 900 that illustrates an example of RMVA logic 812 for recursive median value analysis of 45 inputs, such as the ADC outputs 358 of FIGS. 7 and 8. The RMVA logic 812 includes sliding window logic 904 configured to receive inputs and to store a last n number of inputs. The sliding window logic 904 may include one or more registers (e.g., memories, caches, buffers, etc.) to store 50 the last n number of inputs. The sliding window logic 904 may perform a zero-order hold (ZOH) to store the last n number of inputs. The zero-order hold (ZOH) holds each sample value for one sample interval. As new samples are received, each stored sample moves back one place and a 55 last stored sample is pushed out. In the example illustrated in FIG. 9, the sliding window logic 904 stores the last seven inputs (p0-p6).

The RMVA logic **812** includes cascaded midvalue logic **906** configured to determine a midvalue of the last n number of inputs, the midvalue voltage value **814** of FIG. **8**. The cascaded midvalue logic **906** includes multiple logic blocks **912-916** each configured determine a midvalue for a subset of the last n number of inputs. An output of a first logic block **912** is used as an input of the second logic block **914**, and output of the second logic block **914** is used an input for a third logic block **916**, and so on. An output of a final logic

**20**

block (i.e., the third logic block 916 in the implementation illustrated in FIG. 9) is the median value for the last n number of samples. FIG. 9 illustrates a particular example of the RMVA logic 812 where the multiple logic blocks 912-916 each determine a midvalue of three inputs and three logic blocks 912-916 are used. In other implementations, more than three logic blocks or less than three logic blocks may be used and/or each logic block may process a different number of inputs from another logic block. Additionally or alternatively, each of the logic blocks 912 and 914 can determine a midvalue of 3 samples and the logic block 916 can determine a midvalue of the two outputs and a single sample.

FIG. 9 further illustrates an example of logic 922 for a 3 value midvalue determination, such as the first logic block 912. The logic 922 allows parallel processing and faster determination of the median value for larger values of n. The first logic block 912 receives three inputs corresponding to a combination of samples and midvalue outputs. In the first 20 logic block **912** illustrated in FIG. **9**, the first logic block receives samples five, six, and seven (p4-p6) at inputs 1, 2, and 3 respectively. The samples are compared to each other by a Boolean condition, illustrated as a greater than condition in FIG. 9. Three comparison are used because three samples are used in the illustrated example. These comparisons produce Boolean outputs that are used to control switch outputs. To illustrate, the logic 922 compares the first input ([x]) to the third input ([z]) to generate a first Boolean condition ([xgz]) indicating whether or not the first input ([x]) is greater than the third input.

The logic 922 uses a series of switches (h-h5) to determine the midvalue output. Each switch (h-h5) receives two input sample values and the corresponding Boolean condition. For example, a first switch (h2) receives the first input ([x]) and the third input ([z]) and the corresponding Boolean condition generated by comparing the first and third inputs, i.e., the first condition ([xgz]). The first switch (h2) outputs the third input ([z]) based on the first condition indicating false, i.e., x is not greater than z. A second switch (h4) receives the second input ([y]), the output (the third input ([z])) of the first switch (h2), and a Boolean condition that corresponds to the second input (e.g., the second Boolean condition or the third Boolean condition). The second switch (h4) compares the second input to the third input based on one of the Boolean conditions that corresponds to the second input, i.e., the second condition ([ygz]) in FIG. 9. The second switch (h4) outputs the second input ([y]) to a fifth switch ((h3) e.g., an output switch) based on the first condition indicating true, i.e., y is greater than z.

Operation of a third switch (h) and a fourth switch (h5) mirror operation of the first switch (h2) and the second switch (h4). For example, the third switch (h) receive the same inputs and condition in opposite order and accordingly, the third switch (h) outputs the opposite output value based on the first condition to the fourth switch (h5). To illustrate, the third switch (h) will output the first output ([x]) if the first switch (h2) outputs the third output ([z]). One of the second switch (h4) and the fourth switch (h5) will always output the second input ([y]).

The fifth switch (h3) receives the output of the second and fourth switches (h4 and h5) and compares them based on the other Boolean condition that corresponds to the second input ([y]). The fifth switch (h3) outputs the midvalue based on the second input ([y]), when the first input ([x]) is greater than the second input ([y]), the top switches (h2 and h4) will output the midvalue. When the second input ([y]) is greater than the first input ([x]), the bottom switches (h and h5)

output will be the midvalue (given that a Boolean condition of true or high selects the top input at each switch). As compared to sorting (e.g., by a sort function) the last n number of inputs, the RMVA logic 812 and the logic 922 reduce firmware, circuit area, and processing speed.

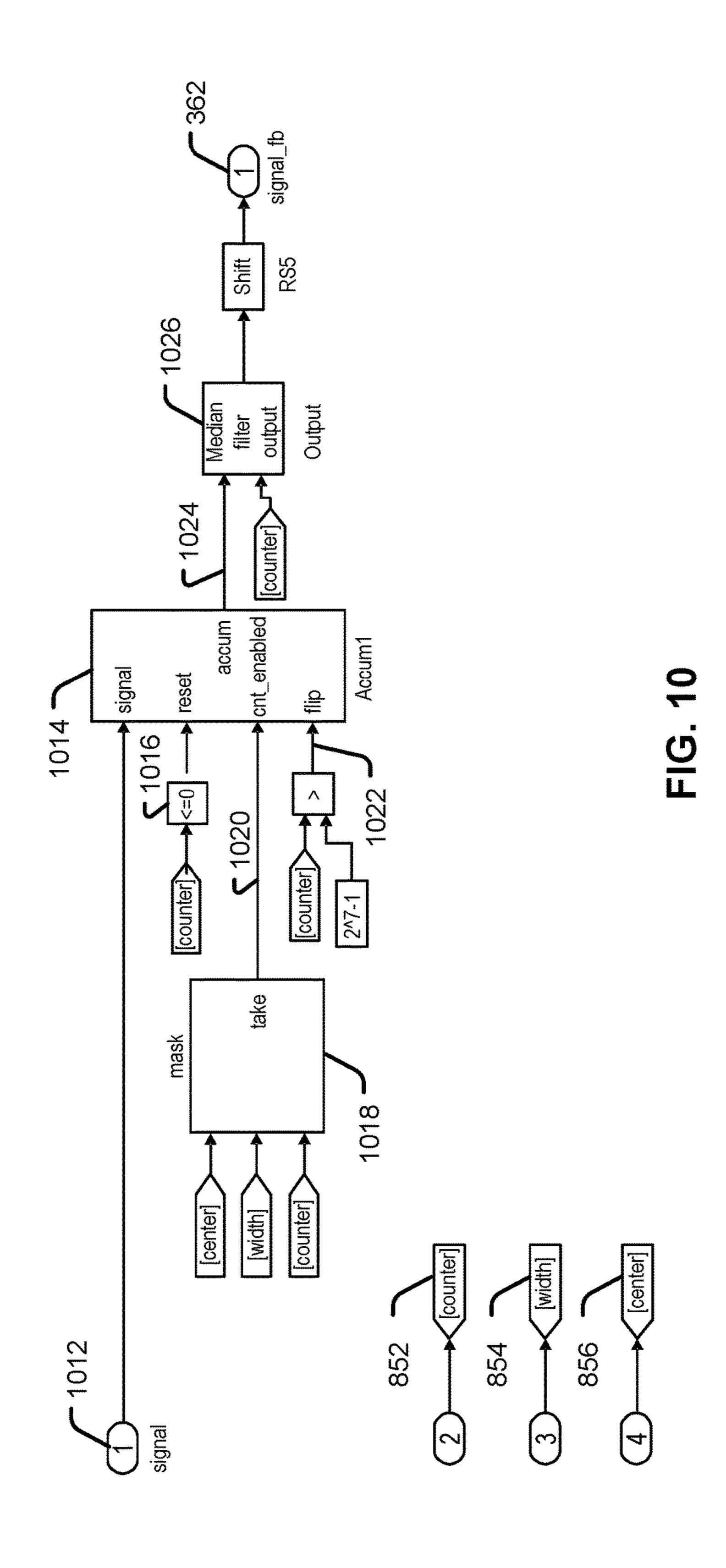

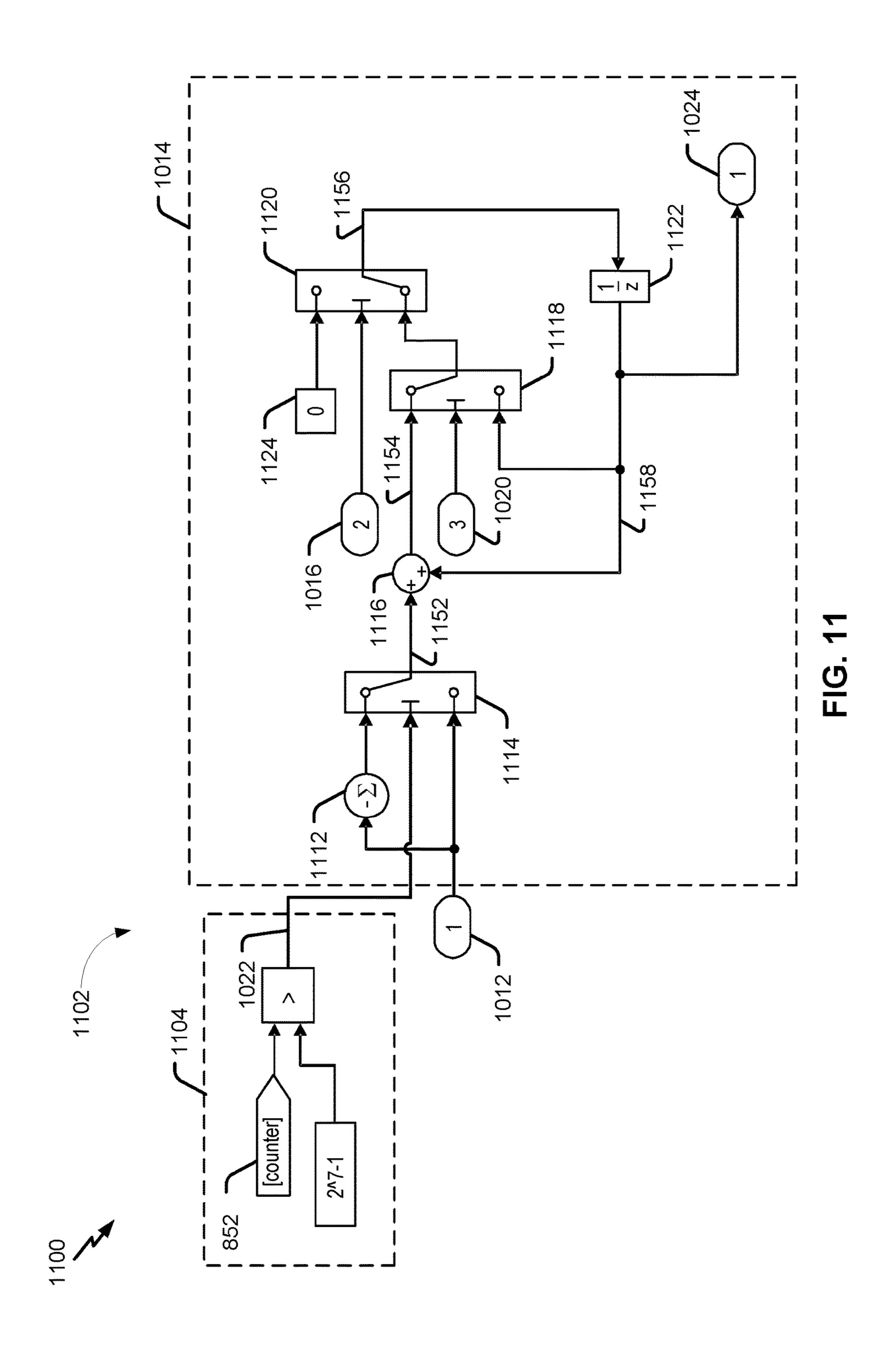

FIG. 10 is a logic diagram 1000 that illustrates an example of the demodulation logic 826 of FIG. 8. The demodulation logic **826** is configured to generate the demodulated output 362 based on the input voltage value 824 of FIG. 8 (included in a signal 1012), the counter input 852, the width input 854, and the center input 856. The demodulation logic 826 includes an accumulator logic 1014, mask logic 1018, and output logic 1026.

accumulated output 1024 based on the input voltage values **824**. For example, the accumulator logic **1014** is configured to accumulate values of the input voltage values 824 and output an accumulated output 1024 as an accumulation of the input voltage values **824**. To illustrate, accumulation 20 includes adding a current voltage value 824 to a sum of previous voltage values 824. Additionally, the accumulator logic **1014** is configured to determine and adjust a sign of the accumulated output 1024 based on a flip input 1022.