### US010339072B2

# (12) United States Patent

Nale et al.

## (10) Patent No.: US 10,339,072 B2

(45) Date of Patent: Jul. 2, 2019

### (54) READ DELIVERY FOR MEMORY SUBSYSTEM WITH NARROW BANDWIDTH REPEATER CHANNEL

(71) Applicant: **Intel Corporation**, Santa Clara, CA (US)

(72) Inventors: **Bill Nale**, Livermore, CA (US); **Pete D Vogt**, Boulder, CO (US)

(73) Assignee: Intel Corporation, Santa Clara, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/089,455

(22) Filed: Apr. 1, 2016

(65) **Prior Publication Data**US 2017/0285941 A1 Oct. 5, 2017

(51) Int. Cl.

G06F 13/16 (2006.01)

G06F 3/06 (2006.01)

(Continued)

(52) **U.S. Cl.**CPC ...... *G06F 13/16* (2013.01); *G11C 7/10*(2013.01); *G06F 3/061* (2013.01); *G06F 3/0629* (2013.01);

(Continued)

### (56) References Cited

## U.S. PATENT DOCUMENTS

7,296,129 B2 11/2007 Gower et al. 7,765,368 B2 7/2010 Gower et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

WO 2015065310 A1 5/2015

### OTHER PUBLICATIONS

International Search Report and Written Opinion for PCT Patent Application No. PCT/US2017/021003, dated Jun. 21, 2017, 16 pages.

International Search Report and Written Opinion for PCT Patent Application No. PCT/US2017/021004, dated Jun. 21, 2017, 18 pages.

International Search Report and Written Opinion for PCT Patent Application No. PCT/US2017/021005, dated Jun. 16, 2017, 16 pages.

Final Office Action for U.S. Appl. No. 15/089,453, dated Oct. 19, 2017, 43 pages.

(Continued)

Primary Examiner — Glenn Gossage (74) Attorney, Agent, or Firm — Compass IP Law PC

## (57) ABSTRACT

A system with memory includes a repeater architecture where the memory connects to a host with one bandwidth, and a repeater extends a channel with a lower bandwidth. A memory circuit includes a first group of memory devices coupled point-to-point to a host device via a first group of read signal lines. The memory circuit includes a second group of memory devices coupled point-to-point to the first group of memory devices second group of read signal lines to extend the memory channel to the second group of memory devices. The second group of read signal lines has fewer read signal lines than the first group. The memory circuit includes a repeater to share read bandwidth between the first and second groups of memory devices, with up to a portion of the bandwidth for reads to the second group of memory devices, and at least an amount equal to the bandwidth less the portion for reads to the first group of memory devices. The repeater or buffer may accumulate data read from the second group of memory devices or a second memory module and burst the accumulated data to the host device with the first bandwidth.

## 26 Claims, 16 Drawing Sheets

## US 10,339,072 B2

## Page 2

| (51)  | Int. Cl.                  |              |                                      | 2006/0146637             | A1*         | 7/2006            | Vogt                                   | G11C 5/04   |

|-------|---------------------------|--------------|--------------------------------------|--------------------------|-------------|-------------------|----------------------------------------|-------------|

|       | G06F 13/40                | •            | (2006.01)                            |                          |             |                   |                                        | 365/230.03  |

|       | G11C 5/06                 |              | (2006.01)                            | 2006/0157682             | A1*         | 7/2006            | Scheuerlein G11                        |             |

|       | G11C 7/10                 |              | (2006.01)                            | 2006/0200122             |             | 10/2006           | 3.6.011 . 1                            | 257/4       |

|       | G11C 7/10<br>G11C 5/04    |              | (2006.01)                            | 2006/0288132             |             |                   | McCall et al.                          | C11C 5/02   |

| (50)  |                           |              | (2000.01)                            | 2007/0058471             | Al          | 3/2007            | Rajan (                                |             |

| (52)  | U.S. Cl.                  | ~~~          | (0.404 (804 8.04)                    | 2007/0089030             | A 1 *       | 4/2007            | Beracoechea H                          | 365/222     |

|       | CPC                       | 2007/0009030 | Л                                    | 7/2007                   | Defacted 11 | 714/762           |                                        |             |

|       | `                         | / /          | 606F 13/1678 (2013.01); G06F         | 2008/0005496             | A 1 *       | 1/2008            | Dreps G06                              |             |

|       | 1.                        | 3/4018 (20   | 013.01); <i>G11C 5/04</i> (2013.01); | 2000,0005 150            | 7 1 1       | 1,2000            | D10ps                                  | 711/154     |

|       |                           |              | G11C 5/06 (2013.01)                  | 2008/0077731             | A1          | 3/2008            | Forrest et al.                         | . 11, 10 .  |

| (58)  | Field of Cla              | essificatio  | n Search                             | 2008/0189455             |             |                   | Dreps et al.                           |             |

| ()    |                           |              | ; G06F 3/0631; G06F 3/0655;          | 2009/0193201             | A1          | 7/2009            | Brittain et al.                        |             |

|       | C1 C O                    | 001 3/001    | G06F 3/067; G06F 13/1678             | 2009/0216924             | A1*         | 8/2009            | Bennett G06                            | F 13/1684   |

|       | Saa annliaat              | ion fila fo  | ,                                    |                          |             |                   |                                        | 710/104     |

|       | See applicat              | ion me ic    | or complete search history.          | 2009/0319719             |             |                   | Perego et al.                          |             |

| (5.6) |                           | D C          |                                      | 2011/0055617             |             |                   | Sankuratri et al.                      | T 10/1/50   |

| (56)  |                           | Referer      | ices Cited                           | 2011/0138133             | Al*         | 6/2011            | Shaeffer G06                           |             |

|       | TIC                       | DATENIT      | DOCLIMENTS                           | 2012/0101021             | A 1 *       | 7/2012            | Chaeffer C06                           | 711/149     |

|       | 0.5.                      | PAIENI       | DOCUMENTS                            | 2012/0191921             | Al          | 7/2012            | Shaeffer G06                           |             |

|       | 8,166,218 B2              | 4/2012       | Rajamani                             | 2012/0210089             | A 1         | 8/2012            | Larson                                 | 711/149     |

|       | 8,880,772 B2              |              | •                                    | 2012/0210089             |             |                   | Ware G06                               | SF 13/1694  |

|       | 8,930,647 B1              |              | Smith                                | 2012,0221709             | 111         | 0,2012            | ************************************** | 711/103     |

|       | 9,232,651 B2              |              |                                      | 2017/0093400             | <b>A</b> 1  | 3/2017            | Bains et al.                           | 7117105     |

|       | 9,317,427 B2*             |              | DeSota G06F 12/0646                  | 2017/0133083             |             |                   | Li et al.                              |             |

|       | 9,495,309 B2              |              |                                      | 2017/0249265             | A1          | 8/2017            | Shaeffer et al.                        |             |

| 2004  | 4/0081005 A1*             | 4/2004       | Garrett, Jr G06F 13/1657             |                          |             |                   |                                        |             |

|       |                           |              | 365/200                              |                          | ОТ          | HER DIT           | BLICATIONS                             |             |

| 2005  | 5/0108458 A1*             | 5/2005       | Vogt G06F 13/4256                    |                          | O1.         | TILK TO           | DLICATIONS                             |             |

| 2004  | 7/01/00/400   1.1.5       | 5/2005       | 711/1                                | Office Action for        | ·US         | Appl. No.         | 15/089,453, dated May 9                | 9. 2017. 34 |

| 2003  | 5/0108490 A1*             | 5/2005       | Vogt G06F 13/4243                    |                          |             | <b>1</b> pp1.110. | 15,005, 155, aatoa 141ay 5             | ,, 2017, 51 |

| 2004  | 5/0210216 A 1 8           | 0/2005       | 711/167<br>COSE 12/1678              | pages. Office Action for | rIIS        | Appl No           | 15/089,454, dated Dec.                 | 24 2017     |

| 2003  | 5/0210216 A1*             | 9/2003       | Jobs                                 | 49 pages.                | 1 0.8.      | тры то            | 15/005,757, ualed Dec.                 | Δ¬, ΔU1/,   |

| 2004  | 5/0004953 A1*             | 1/2006       | 711/170<br>Voot G06E 13/1657         | To pages.                |             |                   |                                        |             |

| 2000  | )/UUU <del>1</del> 333 A1 | 1/2000       | Vogt G06F 13/1657 711/105            | * cited by exa           | mina        | •                 |                                        |             |

|       |                           |              | /11/103                              | ched by exa              | mmei        |                   |                                        |             |

FIG. 2

FIG. 3

FIG. 6

FIG. 8

HG. 9

FIG. 10

FIG. 12

FIG. 13

| SECONDARY<br>DIMM 1406 | CLK<br>1412 | <br>CMD/WR<br>[0]                                                                                         | • • •         | CMD/WR<br>[(M/2)-1]                                                                                                                         |                     |                        | 201                                   | • • •  | RD [(N/2)-1]                        |                                                    |                    |

|------------------------|-------------|-----------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|---------------------------------------|--------|-------------------------------------|----------------------------------------------------|--------------------|

|                        |             | $\begin{pmatrix} B0 \\ B1 \end{pmatrix} \bullet \bullet \begin{pmatrix} B[2x-2] \\ B[2x-1] \end{pmatrix}$ |               | $\begin{pmatrix} B0 \end{pmatrix} B1 \end{pmatrix} \cdot \cdot \begin{pmatrix} B[2x-2] \end{pmatrix} \begin{pmatrix} B[2x-1] \end{pmatrix}$ |                     |                        | (B[2x-1]) $B[2x-2]$ • • • $(B1)$ $B0$ |        | (B[2x-1]) $B[2x-2]$ ••• $(B1)$ $B0$ |                                                    | FIG. 14            |

| M BUFFER               | CLK         | <br>CMD/WR<br>[0]                                                                                         |               | CMD/WR<br>[(M/2)-1]                                                                                                                         | SECONDARY<br>CMD/WR |                        | RD [0]                                | • • •  | RD [(N/2)-1]                        | SECONDARY<br>RD<br>1450                            |                    |

| PRIMARY DIMIN          |             | <br>CMD/WR<br>[0]                                                                                         | CMD/WR        | CMD/WR                                                                                                                                      | CMD/WR<br>[M-1]     | PRIMARY CMD/WR<br>1420 | 20.                                   |        | 2                                   |                                                    | PRIMARY RD<br>1440 |

|                        |             | (B[X-1])                                                                                                  | (B[X-1])      |                                                                                                                                             | (B[X-1])            |                        | 80                                    | B0     | 000                                 | B0   B0                                            |                    |

| <u>1400</u>            |             | B0                                                                                                        | B0            | BO • • •                                                                                                                                    | B0                  |                        | $\left(B[X-1]\right)$                 | B[X-1] |                                     | $ \begin{pmatrix} B[X-1] \\ B[X-1] \end{pmatrix} $ |                    |

| HOST <u>1402</u>       | 1412        | CMD/WR<br>[0]                                                                                             | CMD/WR<br>[1] | CMD/WR<br>M-21                                                                                                                              | ' 'a ÷ '            |                        |                                       |        | ••2                                 | N-2]                                               |                    |

FIG. 15

FIG. 16

FIG. 17

## READ DELIVERY FOR MEMORY SUBSYSTEM WITH NARROW BANDWIDTH REPEATER CHANNEL

### RELATED APPLICATIONS

The present application is related to U.S. patent application Ser. No. 15/089,453, entitled: "Memory Subsystem with Narrow Bandwidth Repeater Channel," filed concurrently herewith, now abandoned, and U.S. patent application Ser. No. 15/089,454, entitled: "Write Delivery for Memory Subsystem with Narrow Bandwidth Repeater Channel," filed concurrently herewith, now abandoned.

#### **FIELD**

The descriptions are generally related to memory channels, and more particular descriptions are related to read data delivery for a memory channel having a narrow bandwidth backend channel from a channel repeater.

### COPYRIGHT NOTICE/PERMISSION

Portions of the disclosure of this patent document may contain material that is subject to copyright protection. The 25 copyright owner has no objection to the reproduction by anyone of the patent document or the patent disclosure as it appears in the Patent and Trademark Office patent file or records, but otherwise reserves all copyright rights whatsoever. The copyright notice applies to all data as described below, and in the accompanying drawings hereto, as well as to any software described below: Copyright © 2016, Intel Corporation, All Rights Reserved.

### **BACKGROUND**

With increases in processor capability and performance, the demand for more functionality from electronic devices increases. The increased functionality in turn increases processor bandwidth demand, which is related to higher overall 40 data throughput. Thus, the inability to move data into and out of the processor with higher bandwidths can impede the continuation of processor performance improvements. Modern computing systems include layers of memory, from the fastest, smallest on die memory storage (e.g., cache), to main 45 memory, to larger and slower nonvolatile storage. Higher processor throughput typically requires moving more data into main memory from nonvolatile storage, and then moving that data between main memory and cache layers on the processor.

Traditional connection of the main memory to the processor is via native memory channels. Native memory channels rely on a direct connection from the memory devices to a controller circuit or memory manager/driver on the host processor. Traditional memory connection occurs 55 through multidrop channels, where the signal lines of a memory channel extend to multiple memory devices, from devices mounted physically closest to the processor to the devices mounted physically farthest from the processor. The devices connect in turn and drive and/or terminate the same 60 signal lines.

Multidrop channels limit the number of memory devices that can be connected to a processor, which limits the memory capacity of a system. When more memory devices and memory modules are connected with multidrop connections, the loading on the memory channel can degrade the communication over the bus. Thus, there is a tradeoff

2

between increasing the speed and increasing the capacity in a memory subsystem. The tradeoff represents a potential limitation in the ability of memory bandwidth to continue to scale to processor performance. Current systems are already hitting the data rate limit for a native multidrop memory channel with two memory modules installed. While increasing the number of channels can help with the data rate problem, it is not scalable with processor performance increases. Increasing channel bandwidth may also be impractical because of increasing the number of signal lines, as well as increasing device and connector size to accommodate the additional signal lines.

### BRIEF DESCRIPTION OF THE DRAWINGS

The following description includes discussion of figures having illustrations given by way of example of implementations of embodiments of the invention. The drawings should be understood by way of example, and not by way of limitation. As used herein, references to one or more "embodiments" are to be understood as describing a particular feature, structure, and/or characteristic included in at least one implementation of the invention. Thus, phrases such as "in one embodiment" or "in an alternate embodiment" appearing herein describe various embodiments and implementations of the invention, and do not necessarily all refer to the same embodiment. However, they are also not necessarily mutually exclusive.

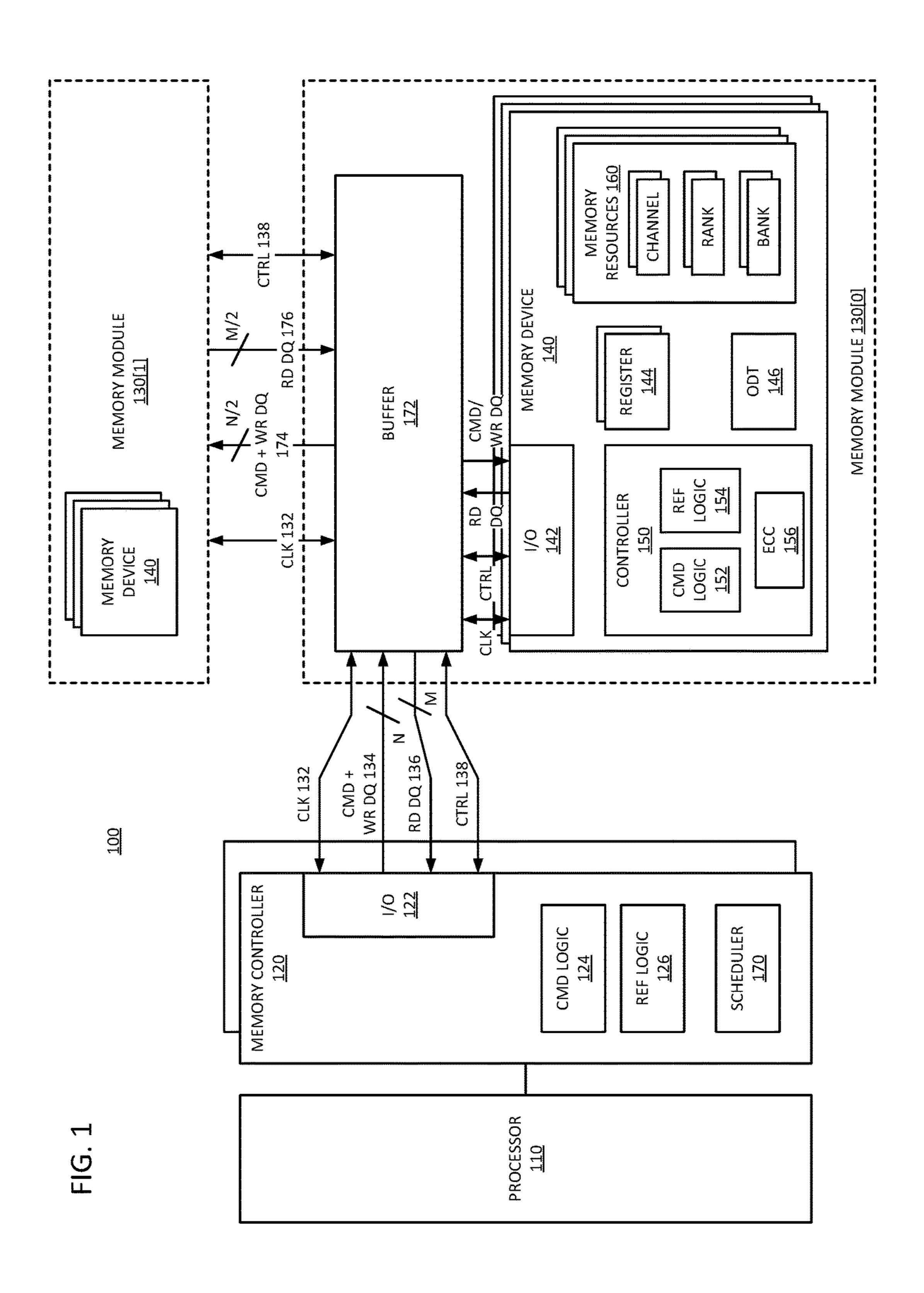

FIG. 1 is a block diagram of an embodiment of a system with a repeater channel architecture having a lower bandwidth repeater channel to extend the memory channel to another memory module.

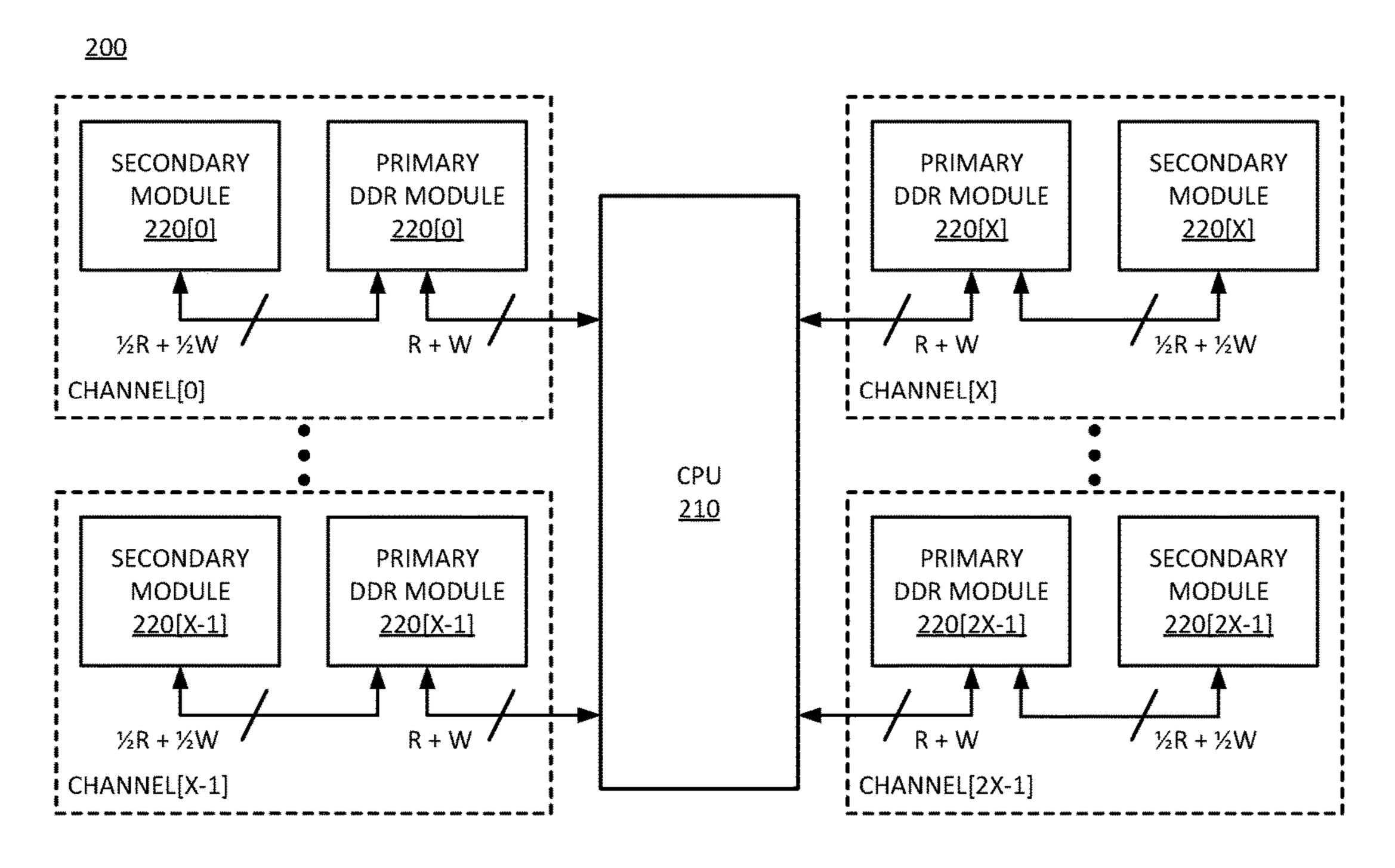

FIG. 2 is a block diagram of an embodiment of a system with a repeater channel architecture in which dual data rate (DDR) modules occupy both primary and secondary positions on the lower bandwidth repeated channel.

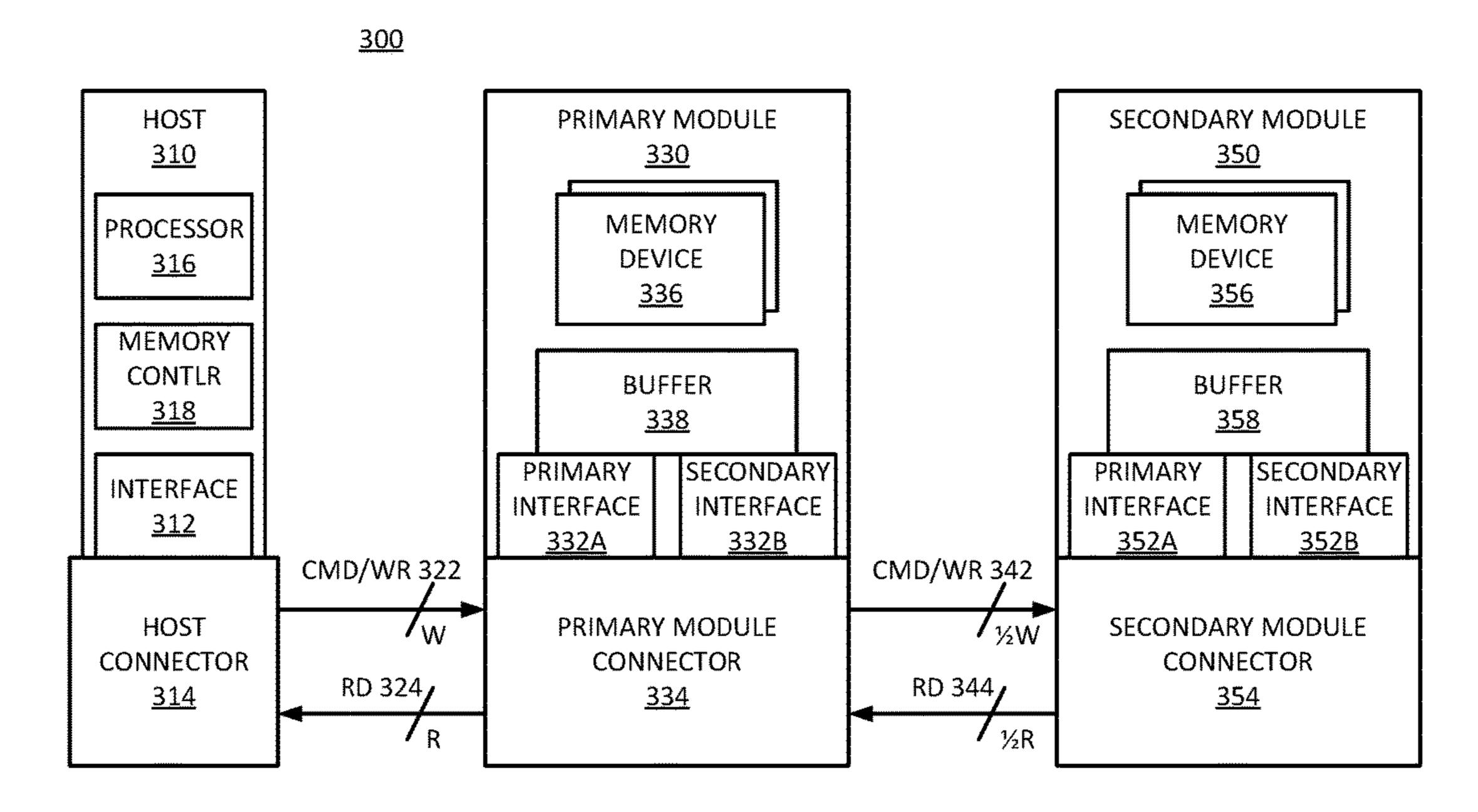

FIG. 3 is a block diagram of an embodiment of a system with a repeater channel architecture in which both primary and secondary memory modules include a buffer.

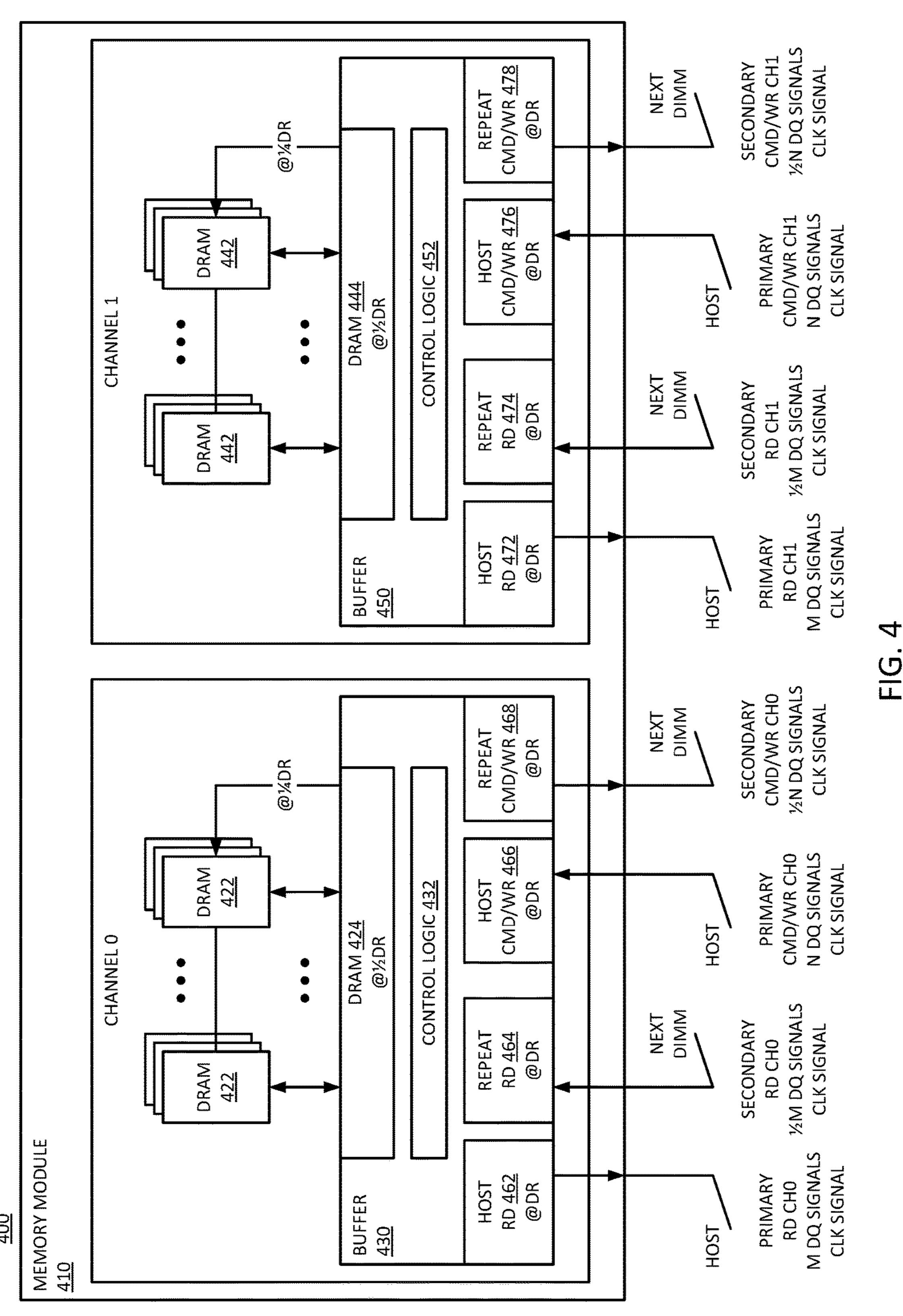

FIG. 4 is a block diagram of an embodiment of a system with a repeater channel architecture illustrating primary and secondary channel connections for first and second channels of a memory module.

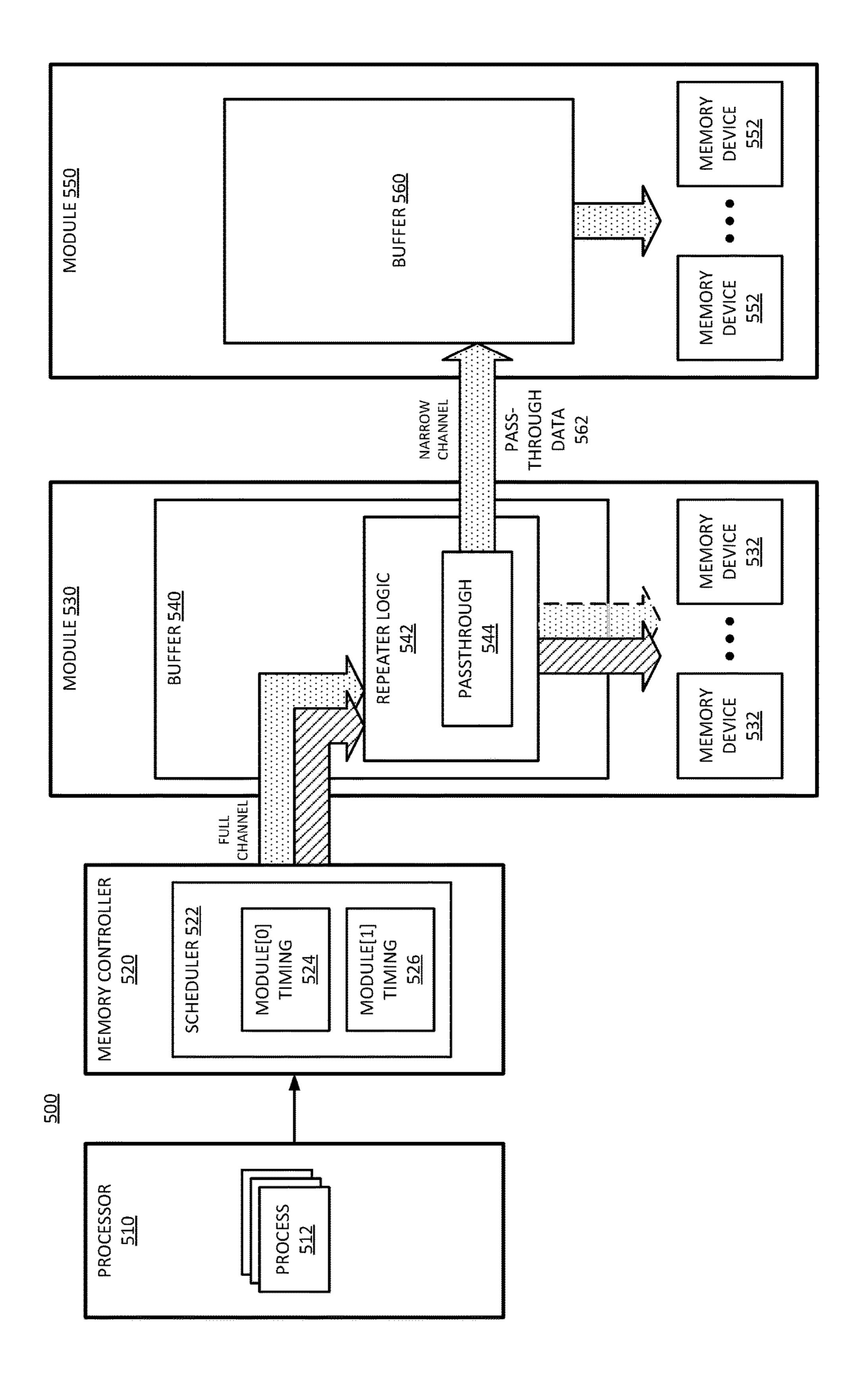

FIG. 5 is a block diagram of an embodiment of a system with a repeater channel architecture that implements write channel repeater passthrough.

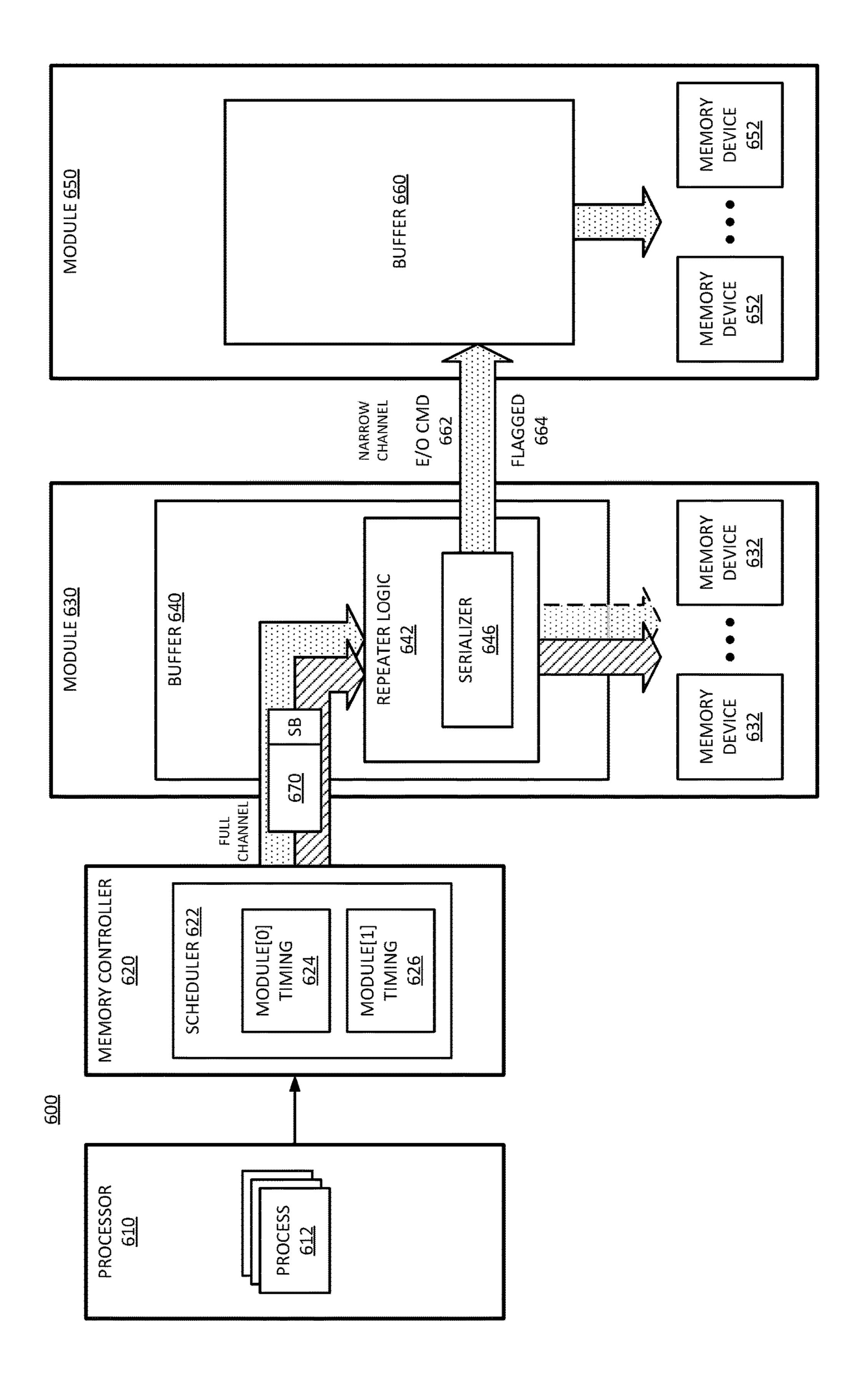

FIG. 6 is a block diagram of an embodiment of a system with a repeater channel architecture that implements write channel repeater memory module selection.

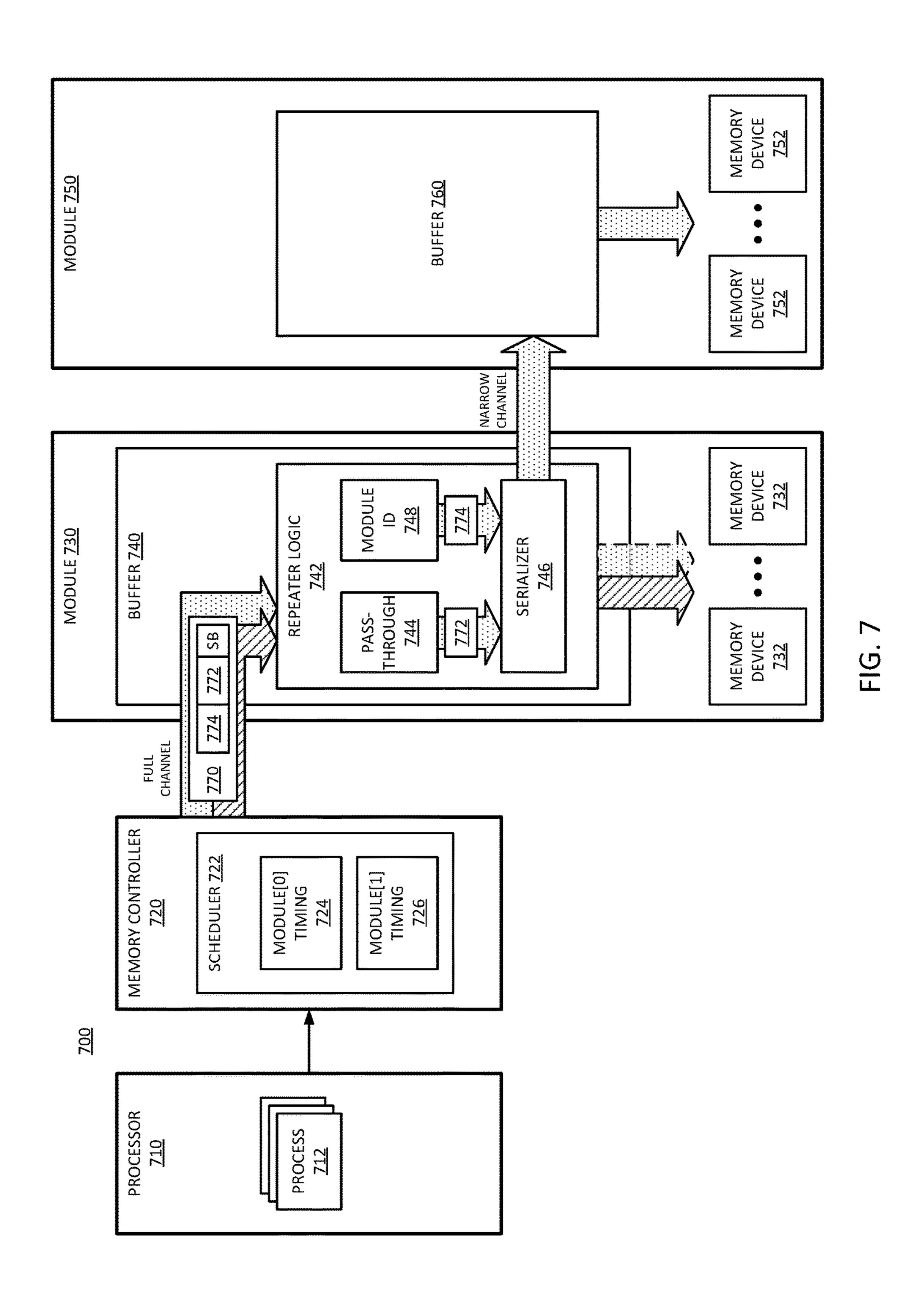

FIG. 7 is a block diagram of an embodiment of a system with a repeater channel architecture that implements write channel speculative passthrough.

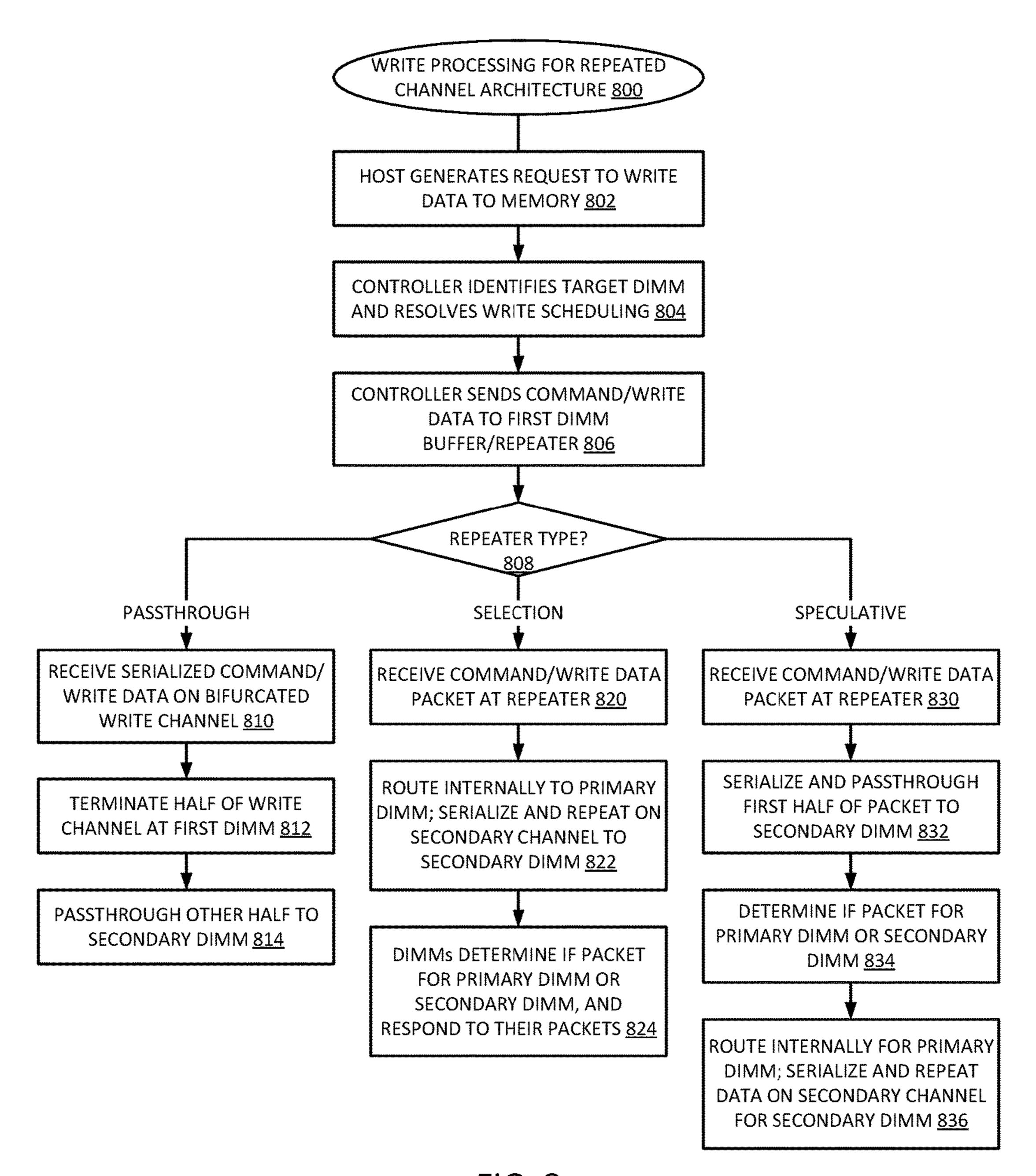

FIG. 8 is a flow diagram of an embodiment of a process for write processing in a repeated channel architecture with primary channel and secondary channel segments having different bandwidths.

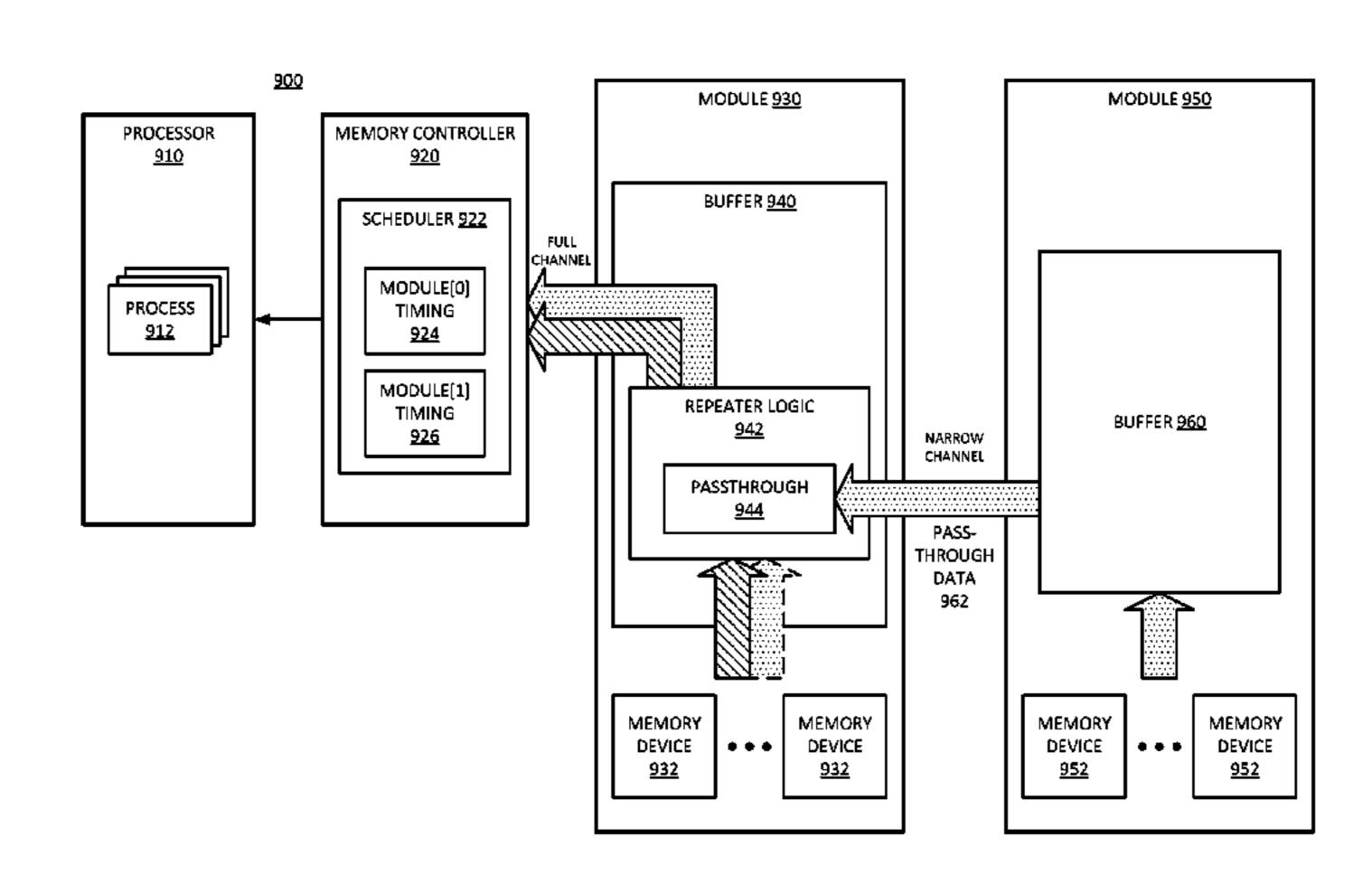

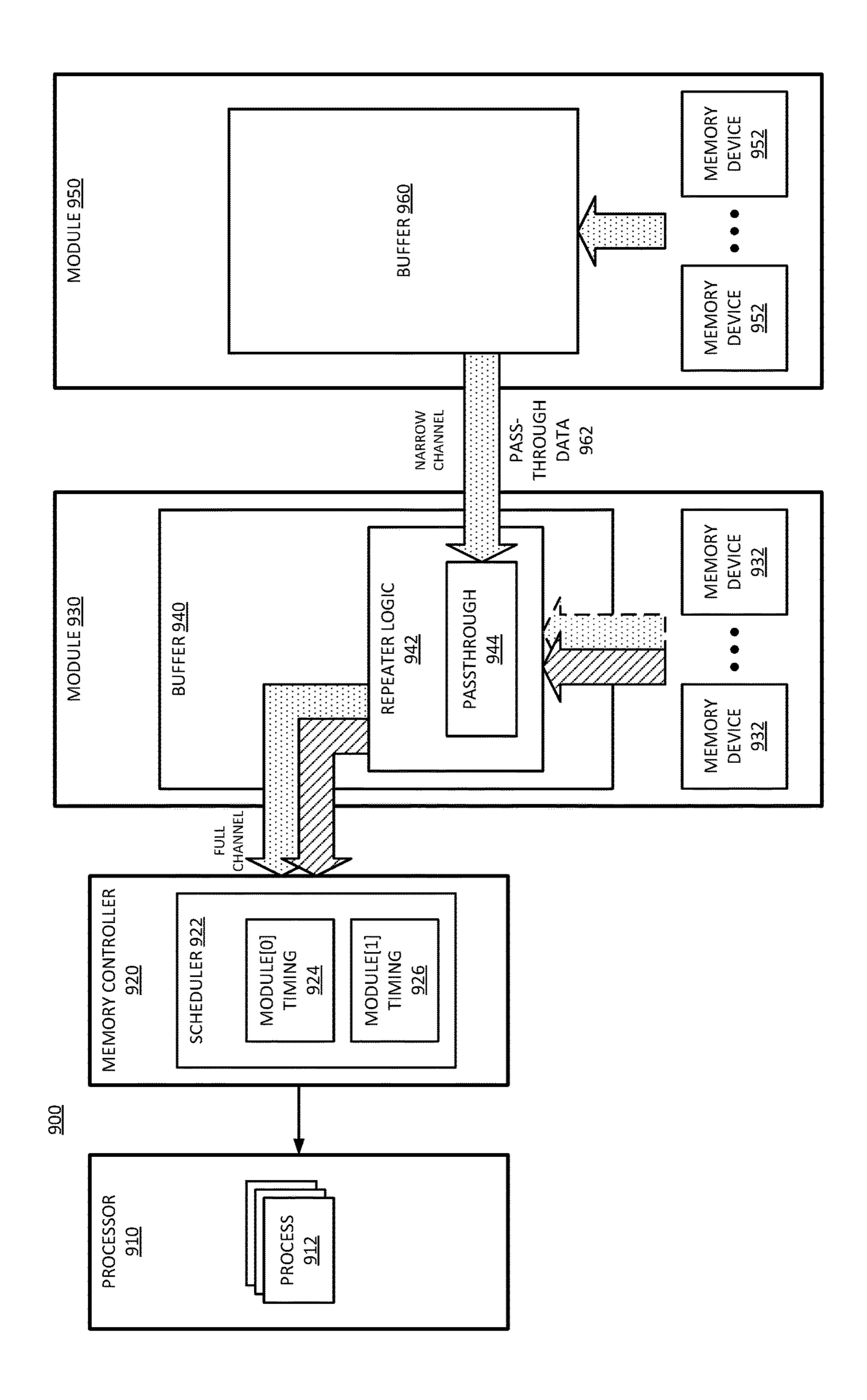

FIG. 9 is a block diagram of an embodiment of a system with a repeater channel architecture that implements read channel repeater passthrough.

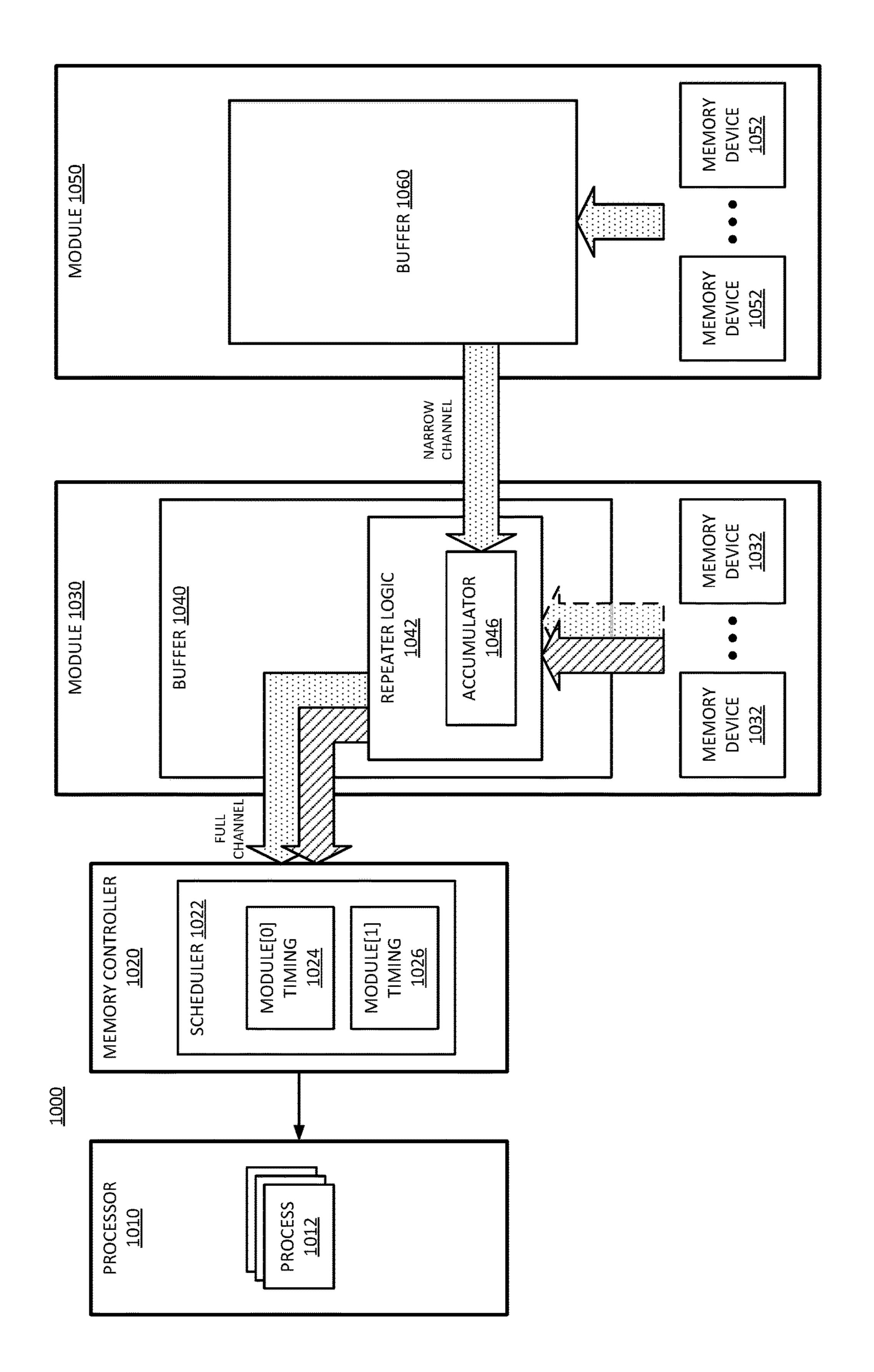

FIG. 10 is a block diagram of an embodiment of a system with a repeater channel architecture that implements read channel data accumulation at the repeater.

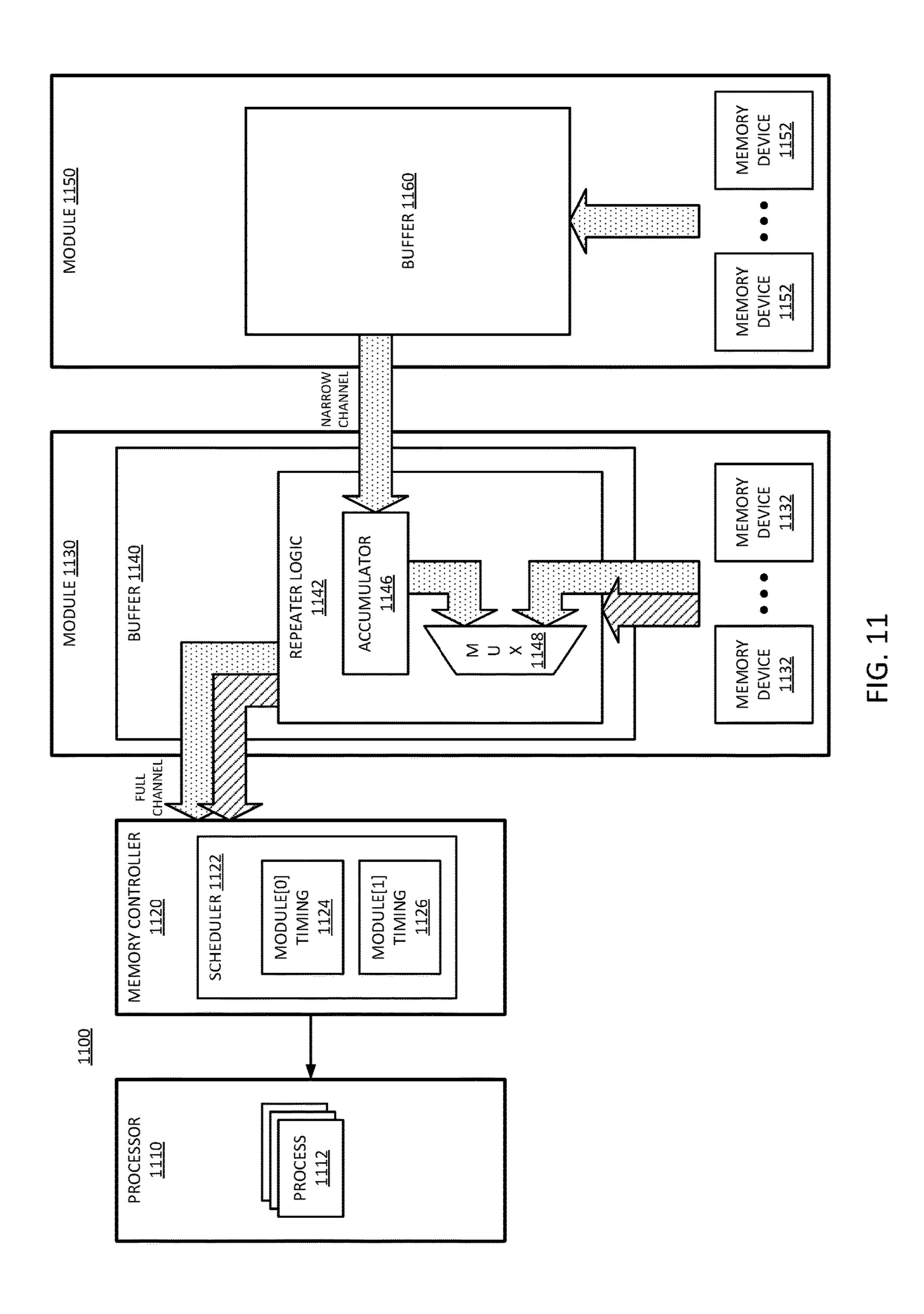

FIG. 11 is a block diagram of an embodiment of a system with a repeater channel architecture that implements read channel opportunistic primary module access.

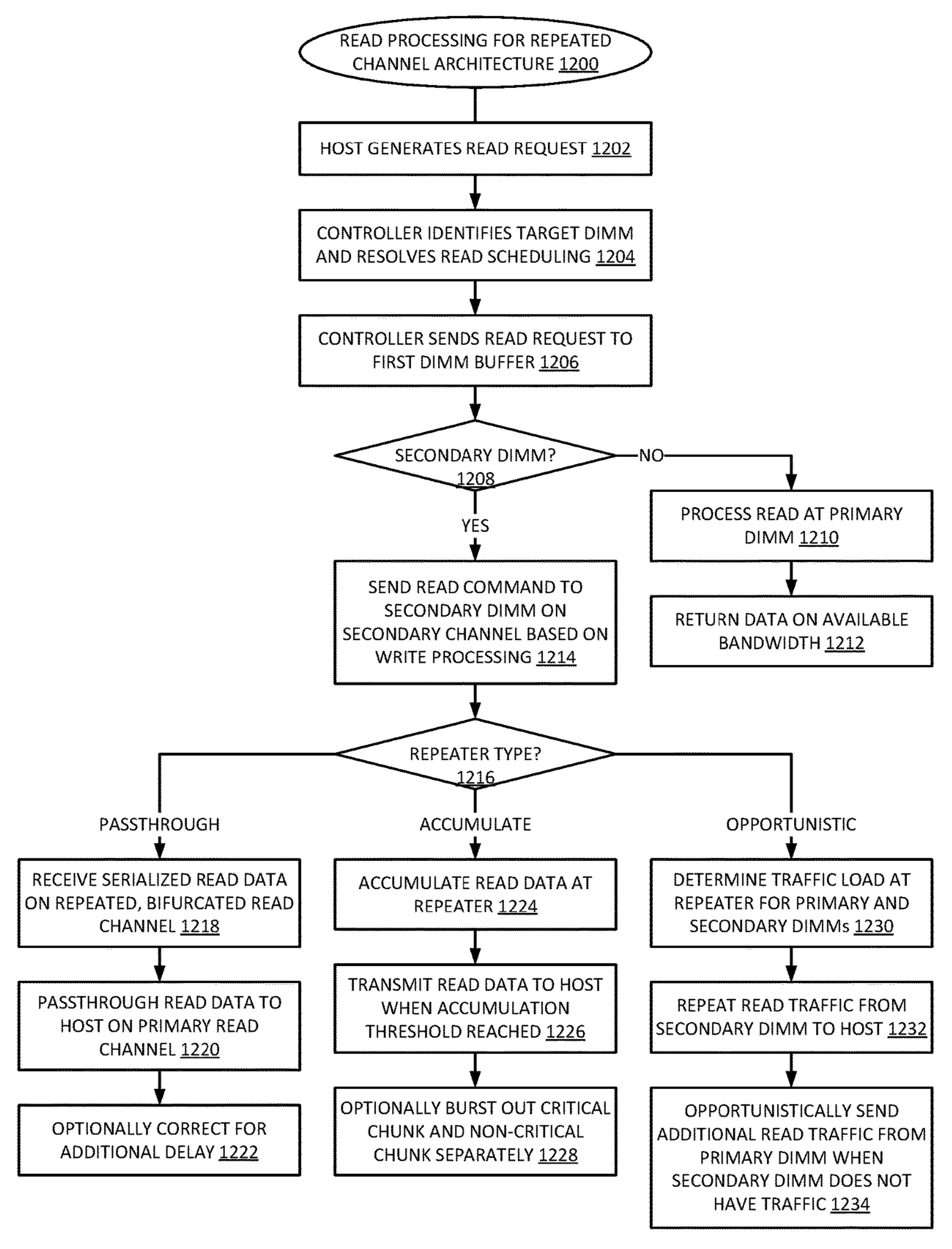

FIG. 12 is a flow diagram of an embodiment of a process for read processing in a repeated channel architecture with primary channel and secondary channel segments having different bandwidths.

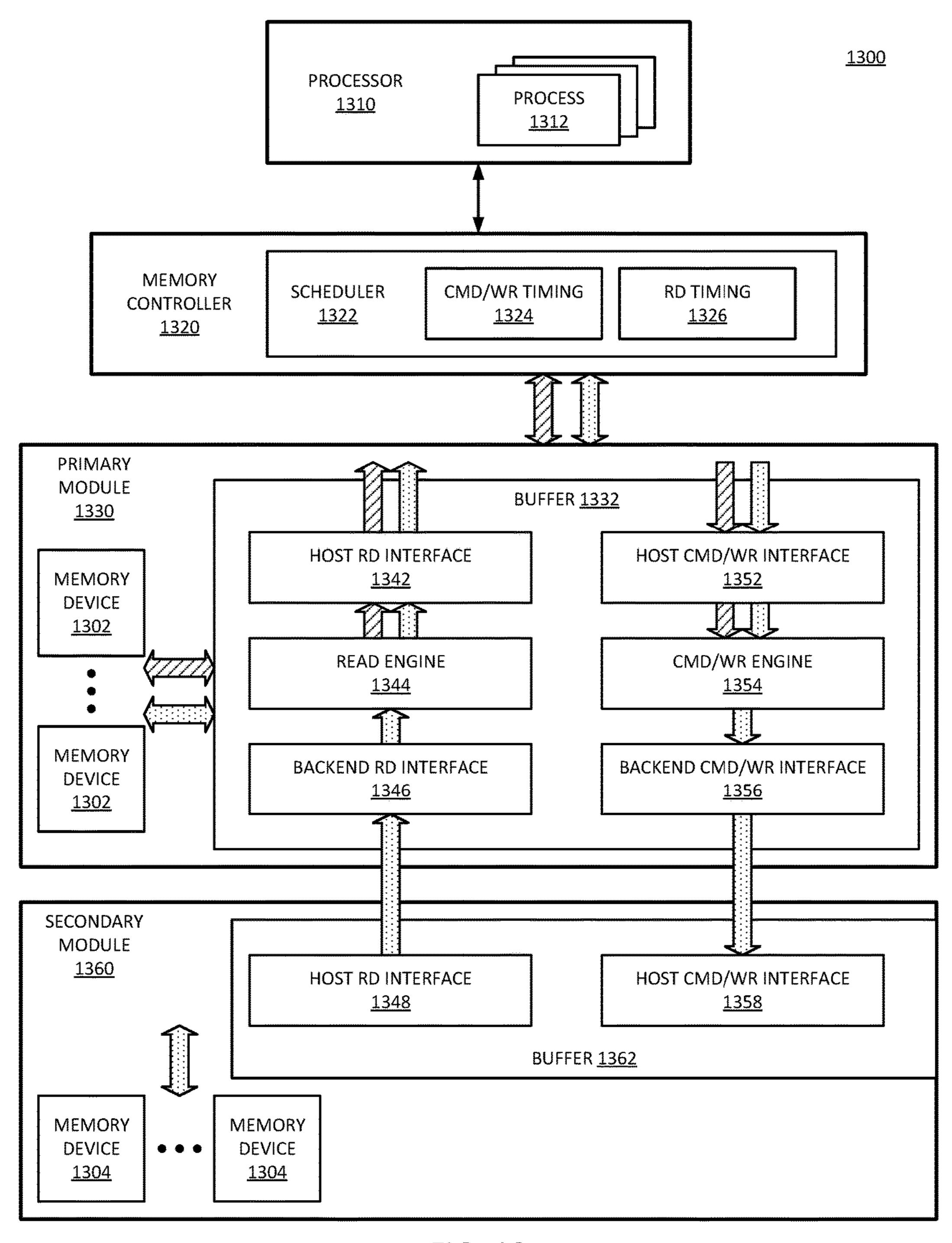

FIG. 13 is a block diagram of an embodiment of a system 5 in which a memory controller schedules commands for a repeater channel architecture having primary and secondary channel segments of different bandwidth.

FIG. 14 is a block diagram of an embodiment of a system including a timing representation for a repeater channel 10 architecture in which primary and secondary channel segments have different bandwidths.

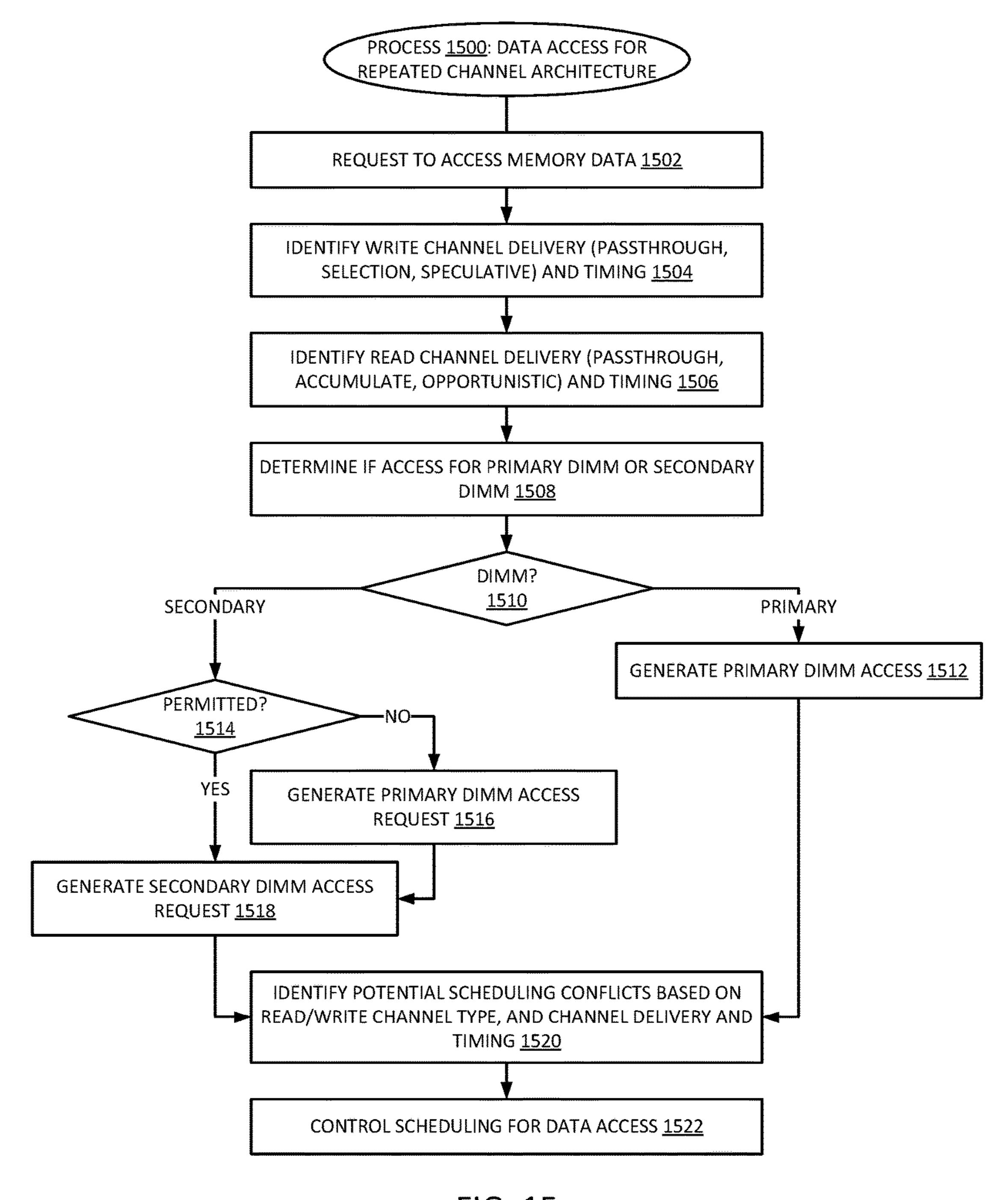

FIG. 15 is a flow diagram of an embodiment of a process for accessing data in a repeated channel architecture with primary channel and secondary channel segments having 15 different bandwidths.

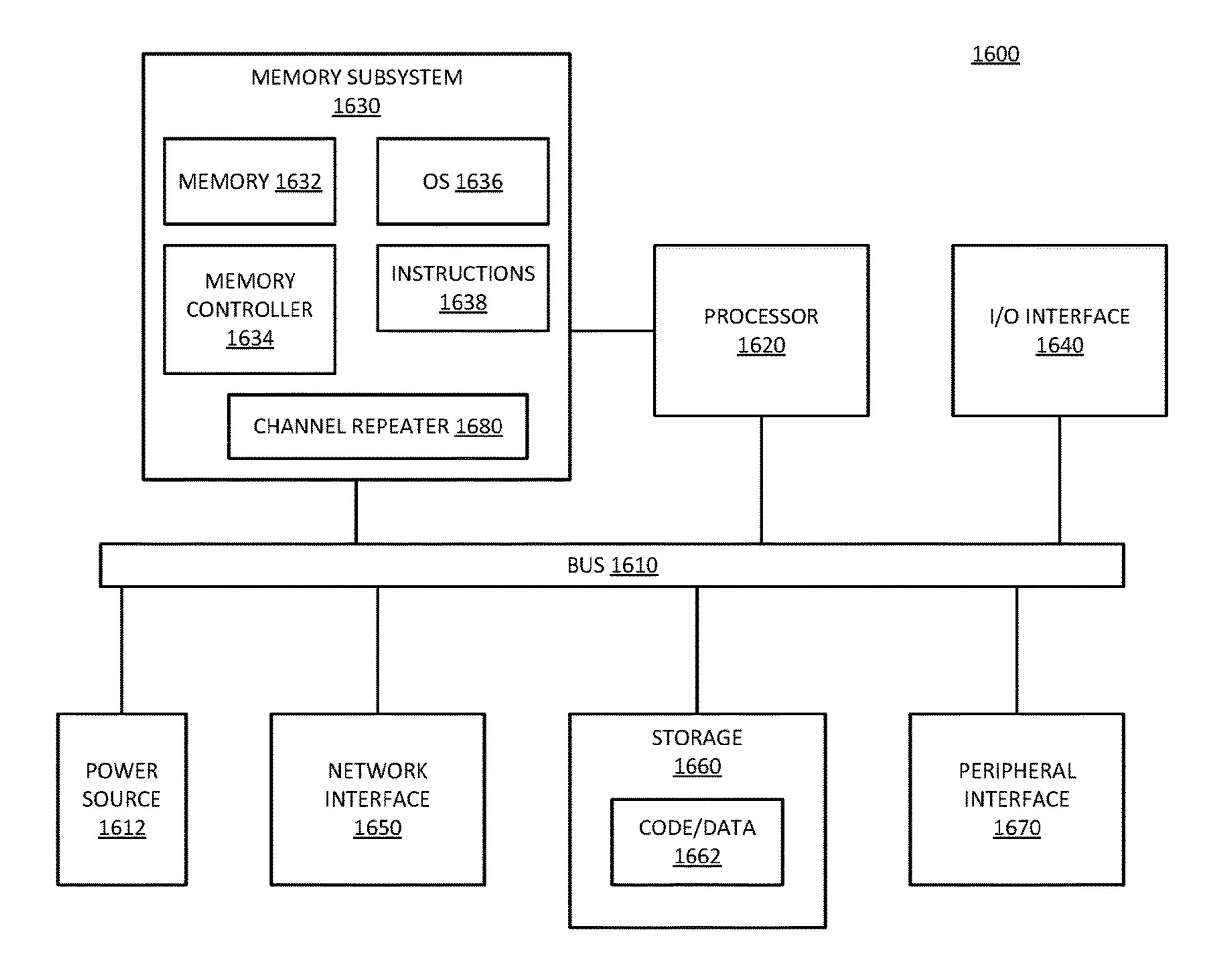

FIG. 16 is a block diagram of an embodiment of a computing system in which a repeated memory channel architecture can be implemented.

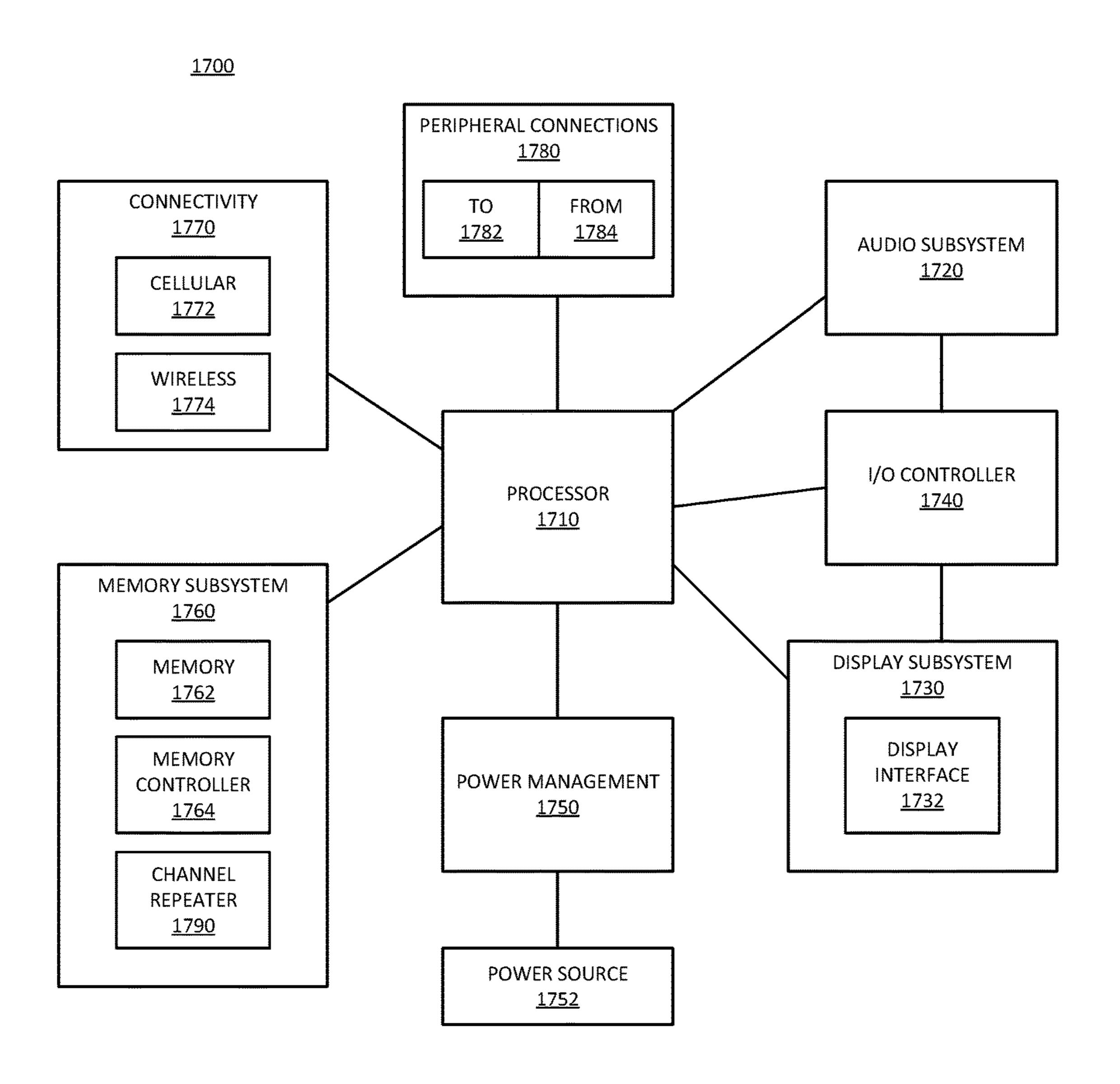

FIG. 17 is a block diagram of an embodiment of a mobile 20 device in which a repeated memory channel architecture can be implemented.

Descriptions of certain details and implementations follow, including a description of the figures, which may depict some or all of the embodiments described below, as well as 25 discussing other potential embodiments or implementations of the inventive concepts presented herein.

### DETAILED DESCRIPTION

As described herein, a system includes a repeater architecture for commands where memory connects to a host with one bandwidth, and repeats the channel with a lower bandwidth. Instead of a multidrop memory channel, such a Whereas a multidrop memory channel has all memory devices or memory modules loading the same signal lines that couple directly to the host, a point-to-point memory channel introduces a buffer that repeats the channel. The buffer can result in the host seeing the loading of only a 40 single connection, while the channel can be extended through the repeating to additional devices.

The memory channel includes unidirectional signal lines instead of bidirectional signal lines. Thus, the memory channel can include a primary command and write data 45 channel from the host to a first memory module, which is extended via a buffer on the first memory module to a second memory module over a narrower bandwidth secondary command and write data channel. The memory channel can further include a primary read channel from the first memory 50 module to the host, which is extended via a buffer on the first memory module to receive read data from a second memory module over a narrower bandwidth secondary read channel.

Reference is made throughout to sharing bandwidth between a first memory module and a second memory 55 module. For purposes of simplicity in description, examples and embodiments are described with respect to a secondary channel having half the bandwidth of the primary channel. Such descriptions will be understood as non-limiting examples. While certain implementations can share half the 60 bandwidth on a repeated channel, other implementations can share other portions of the bandwidth. As one example, the secondary channel could be allocated a third of the bandwidth, such as by alternating packets to/from the secondary memory module where every third memory access packet is 65 allocated to the secondary memory module. It will be understood that other divisions and other portions of the

memory channel could be shared in accordance with what is described herein. One of skill in the art will understand how to modify the system to share a portion of the bandwidth other than one half.

Furthermore, reference is made throughout to primary and secondary memory modules coupled to the same memory channel, with bandwidth shared between the memory modules. While connecting two memory modules or DIMMs to the same memory channel provides one example, it will be understood that it is also possible to extend the memory channel to additional memory modules over repeated channels in accordance with what is described herein. Thus, descriptions to a primary memory module can refer to a memory module that couples to a repeated channel, and further repeats the channel to another memory module. In such an implementation, the secondary module can be a secondary module from the perspective of the upstream memory module coupled closer to the host and can be a primary module from the perspective of a downstream memory module coupled farther from the host. The secondary memory module could thus repeat the channel on another repeated channel segment.

In a practical implementation of a system in which there are two memory modules coupled to a memory channel, it may not be practical to repeat any more than half the bandwidth. Thus, the repeated segment or portion may be up to half the native channel. In accordance with an embodiment where more than two memory modules are coupled to the same memory channel, the repeated portion may be more than half the bandwidth. For example, consider an example where each of three connected memory modules is allocated a third of the total bandwidth. The repeater on the first memory module could repeat 2/3 bandwidth on a repeated channel, and the repeater on the second memory module system can employ a point-to-point memory channel. 35 could repeat ½ bandwidth on a second repeated channel. The repeater logic may be more complex and the timing may be more complex in such implementations, but it will be understood that such implementation can fall within the scope of what is described herein. Thus, descriptions below with reference to first and second memory modules and a repeated channel with half the bandwidth will be understood as non-limiting examples, and system configurations with more memory modules and/or with different portions of the native memory channel repeated can also be applied to the descriptions herein.

For a write channel, a memory circuit includes a repeater to share the command bandwidth between the first and second memory modules, with up to half the bandwidth for commands to the second memory module, and at least half the bandwidth for commands to the first memory module. A write channel provides a link for access commands from the host to the memory devices, which can include commands to access/manipulate data (e.g., read and/or write commands), and commands to set configuration (e.g., MRS (mode register set) commands). A write channel also provides a link to send data to write to a specified address. Thus, the write channel can provide command, address, and write information. For a read channel, a memory circuit includes a repeater to share the read bandwidth between the first and second memory modules, with up to half the bandwidth for reads from the second memory module, and at least half the bandwidth for reads from the first memory module. A read channel provides a link for the memory devices to return data in response to a read command.

As described herein, a memory circuit includes a first group of signal lines (or a first portion or first segment) to couple point-to-point between a first group of memory

devices and a host device. The memory circuit includes a second group of signal lines (or a second portion or second segment) to couple point-to-point between the first group of memory devices (e.g., a first memory module) and a second group of memory devices (e.g., a second memory module). 5 The repeater or buffer architecture can convert a multidrop connection into a point-to-point connection. The point-topoint connection can enable higher data rates, due to the decrease of capacitive loading that would otherwise degrade high-speed communication on the connection.

In one embodiment, a memory subsystem includes pointto-point channels to connect the memory modules to a central processing unit (CPU). A point-to-point channel can scale to much higher data rates than a multidrop channel the memory subsystem supports the connection of two memory modules per channel to a CPU, with a point-topoint channel connected between the CPU and the first module, and a repeater on the first memory module to provide a second point-to-point channel to the second mod- 20 ule. In some descriptions, the connection can be described as a first point-to-point channel and a second point-to-point channel, or a primary channel and a secondary channel, or a primary segment and a secondary segment, or some other description. It will be understood that such descriptions are 25 for purposes of illustration and refer to a memory channel that is repeated. Thus, reference to a second channel or a secondary channel can be understood as referring to a second portion of the memory channel or a secondary portion of the memory channel. Thus, a single memory 30 channel can be considered to be separated into a first channel and an extension channel, or to be considered to be treated as separate sub-channels of the memory channel.

The separate read and write portions of the memory channel, respectively. In one embodiment, the read and write channels are independent with respect to each other. Thus, the implementation of read data processing and repeating can be controlled independently of the implementation of command and write data processing and repeating. As 40 described herein, there are several possible implementations for the read channel, and several possible implementations for the write channel. With the channels independent of each other, there can be any combination of write processing with read processing.

In one embodiment, write processing addresses the delivering of commands and write data to a second DIMM in a memory channel topology where the first DIMM has a full bandwidth unidirectional channel and the second DIMM has a partial bandwidth unidirectional channel. Previous solu- 50 tions included full bandwidth secondary channels where the commands and write data could simply be passed to the second DIMM without any manipulation. With a narrower repeated channel, the secondary channel is bandwidth limited and takes longer to deliver the commands and write data 55 information. In one embodiment, a buffer (which could also be referred to as a register device) on the first DIMM manipulates the commands and write data before passing the information to the second DIMM.

In one embodiment, command and write data delivery to 60 the secondary memory module includes channel bifurcation with channel passthrough. Bifurcation of the write channel includes treating the write channel as two independent channels, where the memory controller can independently write to the first memory module and the second memory 65 module on separate channels, where each memory module gets a half width command/write data channel. With channel

bifurcation, the repeater can simply pass command or write data through a register on the first memory module. With write bifurcation, the memory controller must serialize the command or write data, because the full signal will be transmitted on half the number of signal lines. Thus, bifurcation results in serialization latency, with each packet taking twice as long as a native channel.

In one embodiment, command and write data delivery to the secondary memory module includes selectively sending 10 commands or write data to each memory module. In one embodiment, a command or write data packet includes an identifier (e.g., a bit) to indicate whether it should be sent to the first memory module or the second memory module. In one embodiment, the buffer identifies the correct memory traditionally used in memory standards. In one embodiment, 15 module based on the identifier. In one embodiment, the buffer identifies the correct memory module based on whether the packet is an even packet or an odd packet, with one of the memory modules designated to receive commands and write data in odd numbered packets, and the other to receive commands and write data in even numbered packets. In one embodiment, the first memory module can receive both even and odd packets, and/or can be identified in consecutive packets, allowing temporary use of the full channel bandwidth to the first memory module. The second memory module receives at most half the bandwidth as the data is serialized (either by the host for passthrough, or by the repeater) and takes twice as many UI (unit intervals, or transmission cycles) to send the command or write data. It will be understood that a UI can be a full clock cycle in single data rate systems, or a time between clock edge transitions in a dual data rate system.

In one embodiment, command and write data delivery to the secondary memory module includes speculative passthrough at the repeater. In one embodiment, the host channel can be considered a read channel and a write 35 sends an indicator (e.g., a select bit in a first UI of a packet) to indicate which memory module is the target for the command or write data. The repeater sends the first half of every packet to the second memory module with minimum latency. If the select bit indicates the first memory module, the repeater only sends the first half of the packet to the secondary channel, which will complete its serialized transmission in time for the next command or write data to be received. If the select bit indicates the second memory module, the repeater also buffers and transmits the second 45 half of the packet to the secondary channel. In one embodiment, the host includes a rule to guarantee there are never two packets in a row sent to the second memory module.

In one embodiment, read processing addresses the delivering of read data from a second DIMM in a memory channel topology where the first DIMM has a full bandwidth unidirectional read channel and the second DIMM has a partial bandwidth unidirectional read channel. Previous solutions included full bandwidth secondary channels where the read data could simply be delivered from the second DIMM without any manipulation. With a narrower repeated read channel, the secondary channel is bandwidth limited and takes longer to deliver the read data to the first DIMM. In one embodiment, a buffer (which could also be referred to as a register device) on the first DIMM manipulates read data before passing the data to the host.

In one embodiment, read data delivery from the secondary memory module includes channel bifurcation with channel passthrough. Bifurcation of the read channel includes treating the read channel as two independent channels, where the memory controller can independently read from the first memory module and the second memory module on separate channels, where each memory module gets a half

width read data channel. With channel bifurcation, the repeater can simply pass read data from the second memory module through a register on the first memory module. With read bifurcation, the read data takes twice as long for the memory controller to receive, because the full signal will be 5 transmitted on half the number of signal lines. Thus, bifurcation results in serialization latency, with each packet taking twice as long as a native channel. In one embodiment, the memory controller can adjust for read latency from the second memory module. In one embodiment, the first 10 memory module buffer adds latency to the read data from the first memory module to match timing of the second memory module.

In one embodiment, read data delivery from the secondary memory module includes data accumulation at the 15 buffer, which can then burst the read data to the host. In one embodiment, the buffer on the first memory module knows when the data from the second memory module will arrive having seen the read command sent earlier, and accumulates the data. In one embodiment, the buffer accumulates half of 20 the read data from the second memory module before bursting the data to the host, and thus, the last bit of data will arrive at the buffer just in time to be sent to the host. In one embodiment, the buffer supports expedited operation for a critical chunk. The critical chunk refers to a chunk of read 25 data that includes the specific data requested by the host. In such a case, in one embodiment, the buffer stores a quarter of the cacheline or wordline and then bursts out the first half of the data, and waits for the rest of the read data to be sent before bursting out the rest of the cacheline/wordline.

In one embodiment, read data delivery from the secondary memory module includes bifurcation of the read channel to the host (e.g., treating the read channel as two separate channels), and the buffer on the first memory module includes logic to allow it to use both half read channels when 35 available. In one embodiment, the buffer knows when the data from the second memory module will arrive, and passes the data directly to the host on one of the half width read channels. When the second memory module does not deliver data, the first memory module can utilize the second half 40 channel to deliver read data, thus delivering full read bandwidth to the host.

Reference to memory devices can apply to different memory types. Memory devices generally refer to volatile memory technologies. Volatile memory is memory whose 45 state (and therefore the data stored on it) is indeterminate if power is interrupted to the device. Nonvolatile memory refers to memory whose state is determinate even if power is interrupted to the device. Dynamic volatile memory requires refreshing the data stored in the device to maintain 50 state. One example of dynamic volatile memory includes DRAM (dynamic random access memory), or some variant such as synchronous DRAM (SDRAM). A memory subsystem as described herein may be compatible with a number of memory technologies, such as DDR3 (dual data rate 55) version 3, original release by JEDEC (Joint Electronic Device Engineering Council) on Jun. 27, 2007, currently on release 21), DDR4 (DDR version 4, initial specification published in September 2012 by JEDEC), DDR4E (DDR version 4, extended, currently in discussion by JEDEC), 60 LPDDR3 (low power DDR version 3, JESD209-3B, August 2013 by JEDEC), LPDDR4 (Low Power Double Data Rate (LPDDR) version 4, JESD209-4, originally published by JEDEC in August 2014), WIO2 (Wide I/O 2 (WideIO2), JESD229-2, originally published by JEDEC in August 65 2014), HBM (High Bandwidth Memory DRAM, JESD235, originally published by JEDEC in October 2013), DDR5

8

(DDR version 5, currently in discussion by JEDEC), LPDDR5 (currently in discussion by JEDEC), HBM2 (HBM version 2), (currently in discussion by JEDEC), and/or others, and technologies based on derivatives or extensions of such specifications.

In addition to, or alternatively to, volatile memory, in one embodiment, reference to memory devices can refer to a nonvolatile memory device whose state is determinate even if power is interrupted to the device. In one embodiment, the nonvolatile memory device is a block addressable memory device, such as NAND or NOR technologies. Thus, a memory device can also include a future generation nonvolatile device, such as a three dimensional crosspoint (3DXP) memory device, or other byte addressable nonvolatile memory devices, or memory devices that use a chalcogenide phase change material (e.g., chalcogenide glass). In one embodiment, the memory device can be or include multi-threshold level NAND flash memory, NOR flash memory, single or multi-level Phase Change Memory (PCM), a resistive memory, nanowire memory, ferroelectric transistor random access memory (FeTRAM), magnetoresistive random access memory (MRAM) memory that incorporates memristor technology, or spin transfer torque (STT)-MRAM, or a combination of any of the above, or other memory.

Descriptions herein referring to a "DRAM" can apply to any memory device that allows random access, whether volatile or nonvolatile. The memory device or DRAM can refer to the die itself and/or to a packaged memory product.

FIG. 1 is a block diagram of an embodiment of a system with a repeater channel architecture having a lower bandwidth repeater channel to extend the memory channel to another memory module. System 100 includes elements of a memory subsystem in a computing device. Processor 110 represents a processing unit of a host computing platform that executes an operating system (OS) and applications, which can collectively be referred to as a "host" for the memory. The OS and applications execute operations that result in memory accesses. Processor 110 can include one or more separate processors. Each separate processor can include a single and/or a multicore processing unit. The processing unit can be a primary processor such as a CPU (central processing unit) and/or a peripheral processor such as a GPU (graphics processing unit). System 100 can be implemented as an SOC (system on a chip), or be implemented with standalone components.

Memory controller 120 represents one or more memory controller circuits or devices for system 100. Memory controller 120 represents control logic that generates memory access commands in response to the execution of operations by processor 110. Memory controller 120 accesses one or more memory devices 140. Memory devices 140 can be DRAMs in accordance with any referred to above. In one embodiment, memory devices 140 are organized and managed as different channels, where each channel couples to buses and signal lines that couple to multiple memory devices in parallel. Each channel is independently operable. Thus, each channel is independently accessed and controlled, and the timing, data transfer, command and address exchanges, and other operations are separate for each channel. As used herein, coupling can refer to an electrical coupling, communicative, and/or a physical coupling. Physical coupling can include direct contact. Electrical coupling includes an interface or interconnection that allows electrical flow and/or signaling between components. Communicative coupling includes connections, including wireless, that enable components to exchange data.

In one embodiment, settings for each channel are controlled by separate mode registers or other register settings. In one embodiment, each memory controller 120 manages a separate memory channel, although system 100 can be configured to have multiple channels managed by a single controller, or to have multiple controllers on a single channel. In one embodiment, memory controller 120 is part of host processor 110, such as logic implemented on the same die or implemented in the same package space as the processor.

Memory controller 120 includes I/O interface logic 122 to couple to a system bus and/or a memory bus, such as a memory channel as referred to above. I/O interface logic 122 (as well as I/O interface logic 142 of memory device 140) can include pins, pads, connectors, signal lines, traces, 15 wires, and/or other hardware to connect the devices. I/O interface logic 122 can include a hardware interface. As illustrated, I/O interface logic **122** includes at least drivers/ transceivers for signal lines. Commonly, wires within an integrated circuit interface couple with a pad, pin, or con- 20 nector to interface signal lines or traces or other wires between devices. I/O interface logic 122 can include drivers, receivers, transceivers, termination, and/or other circuitry to send and/or receive signal on the signal lines between the devices. The system bus can be implemented as multiple 25 signal lines coupling memory controller 120 to memory devices 140. The system bus includes at least clock (CLK) 132, command/address (CMD) and write data (WR DQ) 134, read data (RD DQ) 136, and zero or more other signal lines 138. In one embodiment, a bus or connection between 30 memory controller 120 and memory can be referred to as a memory bus. The signal lines for CMD can be referred to as a "C/A bus" (or ADD/CMD bus, or some other designation indicating the transfer of commands and address information) and the signal lines for write and read DQ can be 35 referred to as a "data bus." In one embodiment, independent channels have different clock signals, C/A buses, data buses, and other signal lines. Thus, system 100 can be considered to have multiple "system buses," in the sense that an independent interface path can be considered a separate 40 system bus. It will be understood that in addition to the lines explicitly shown, a system bus can include strobe signaling lines, alert lines, auxiliary lines, and other signal lines.

It will be understood that the system bus includes a command and write data bus 134 configured to operate at a 45 bandwidth. In one embodiment, the command and write signal lines (WR DQ 134) can include unidirectional lines for write and command data from the host to memory, and read DQ 136 can include unidirectional lines for read data from the memory to the host. In one embodiment, the data 50 bus can include bidirectional lines for read data and for write/command data. Based on design and/or implementation of system 100, the data bus can have more or less bandwidth per memory device 140. For example, the data bus can support memory devices that have either a ×32 55 interface, a ×16 interface, a ×8 interface, or other interface. The convention "xW," where W is a binary integer refers to an interface size of memory device 140, which represents a number of signal lines to exchange data with memory controller 120. The interface size of the memory devices is 60 a controlling factor on how many memory devices can be used concurrently per channel in system 100 or coupled in parallel to the same signal lines.

Memory devices 140 represent memory resources for system 100. In one embodiment, each memory device 140 is 65 a separate memory die. In one embodiment, each memory device 140 can interface with multiple (e.g., 2) channels per

**10**

device or die. Each memory device **140** includes I/O interface logic 142, which has a bandwidth determined by the implementation of the device (e.g., ×16 or ×8 or some other interface bandwidth). I/O interface logic 142 enables the memory devices to interface with memory controller 120. I/O interface logic 142 can include a hardware interface, and can be in accordance with I/O 122 of memory controller, but at the memory device end. In one embodiment, multiple memory devices 140 are connected in parallel to the same data buses. For example, system 100 can be configured with multiple memory devices 140 coupled in parallel, with each memory device responding to a command, and accessing memory resources 160 internal to each. For a Write operation, an individual memory device 140 can write a portion of the overall data word, and for a Read operation, an individual memory device 140 can fetch a portion of the overall data word.

In one embodiment, memory devices 140 are disposed directly on a motherboard or host system platform (e.g., a PCB (printed circuit board) on which processor 110 is disposed) of a computing device. In one embodiment, memory devices 140 can be organized into memory modules 130. In one embodiment, memory modules (DIMMs). In one embodiment, memory modules 130 represent dual inline memory modules (DIMMs). In one embodiment, memory modules 130 represent other organization of multiple memory devices to share at least a portion of access or control circuitry, which can be a separate circuit, a separate device, or a separate board from the host system platform. Memory modules 130 can include multiple memory devices 140, and the memory modules can include support for multiple separate channels to the included memory devices disposed on them.

Memory devices 140 each include memory resources 160. Memory resources 160 represent individual arrays of memory locations or storage locations for data. Typically memory resources 160 are managed as rows of data, accessed via wordline (rows) and bitline (individual bits within a row) control. Memory resources 160 can be organized as separate channels, ranks, and banks of memory. Channels are independent control paths to storage locations within memory devices 140. Ranks refer to common locations across multiple memory devices (e.g., same row addresses within different devices). Banks refer to arrays of memory locations within a memory device 140. In one embodiment, banks of memory are divided into sub-banks with at least a portion of shared circuitry (e.g., drivers, signal lines, control logic) for the sub-banks. It will be understood that channels, ranks, banks, and/or other organizations of the memory locations can overlap physical resources. For example, the same physical memory locations can be accessed over a specific channel as a specific bank, which can also belong to a rank. Thus, the organization of memory resources will be understood in an inclusive, rather than exclusive, manner.

In one embodiment, memory devices 140 include one or more registers 144. Register 144 represents one or more storage devices or storage locations that provide configuration or settings for the operation of the memory device. In one embodiment, register 144 can provide a storage location for memory device 140 to store data for access by memory controller 120 as part of a control or management operation. In one embodiment, register 144 includes one or more Mode Registers. In one embodiment, register 144 includes one or more multipurpose registers. The configuration of locations within register 144 can configure memory device 140 to operate in different "mode," where command and/or address information or signal lines can trigger different operations

within memory device 140 depending on the mode. Settings of register 144 can indicate configuration for I/O settings (e.g., timing, termination or ODT (on-die termination), driver configuration, and/or other I/O settings).

In one embodiment, memory device **140** includes ODT **146** as part of the interface hardware associated with I/O **142**. ODT **146** can be configured as mentioned above, and provide settings for impedance to be applied to the interface to specified signal lines. The ODT settings can be changed based on whether a memory device is a selected target of an access operation or a non-target device. ODT **146** settings can affect the timing and reflections of signaling on the terminated lines. Careful control over ODT **146** can enable higher-speed operation with improved matching of applied impedance and loading. ODT **146** can be applied to specific 15 signal lines of I/O interface **142**, **122**, and is not necessarily applied to all signal lines.

Memory device 140 includes controller 150, which represents control logic within the memory device to control internal operations within the memory device. For example, 20 controller 150 decodes commands sent by memory controller 120 and generates internal operations to execute or satisfy the commands. Controller 150 can be referred to as an internal controller. Controller 150 can determine what mode is selected based on register 144, and configure the access and/or execution of operations for memory resources 160 based on the selected mode. Controller 150 generates control signals to control the routing of bits within memory device 140 to provide a proper interface for the selected mode and direct a command to the proper memory locations 30 or addresses.

Referring again to memory controller 120, memory controller 120 includes command (CMD) logic 124, which represents logic or circuitry to generate commands to send to memory devices 140. Typically, the signaling in memory 35 subsystems includes address information within or accompanying the command to indicate or select one or more memory locations where the memory devices should execute the command. In one embodiment, controller 150 of memory device 140 includes command logic 152 to receive 40 and decode command and address information received via I/O **142** from memory controller **120**. Based on the received command and address information, controller 150 can control the timing of operations of the logic and circuitry within memory device 140 to execute the commands. Controller 45 150 is responsible for compliance with standards or specifications within memory device 140, such as timing and signaling requirements. Memory controller 120 can also ensure compliance with standards or specifications by access scheduling and control.

In one embodiment, memory controller 120 includes refresh (REF) logic 126. Refresh logic 126 can be used where memory devices 140 are volatile and need to be refreshed to maintain a deterministic state. In one embodiment, refresh logic 126 indicates a location for refresh, and 55 a type of refresh to perform. Refresh logic **126** can trigger self-refresh within memory device 140, and/or execute external refreshes by sending refresh commands. For example, in one embodiment, system 100 supports all bank refreshes as well as per bank refreshes, or other all bank and 60 per bank commands. All bank commands cause an operation of a selected bank within all memory devices 140 coupled in parallel. Per bank commands cause the operation of a specified bank within a specified memory device 140. In one embodiment, controller 150 within memory device 140 65 includes refresh logic 154 to apply refresh within memory device 140. In one embodiment, refresh logic 154 generates

12

internal operations to perform refresh in accordance with an external refresh received from memory controller 120. Refresh logic 154 can determine if a refresh is directed to memory device 140, and what memory resources 160 to refresh in response to the command.

In one embodiment, system 100 includes multiple memory modules 130 that include memory devices 140. In one embodiment, memory modules 130 provide a repeater architecture for a memory channel. The memory channel can include clock 132, command and write DQ 134, read DQ 136, and zero or more other control signals (CTRL) 138. In a repeater architecture, memory module 130[1] connects to memory controller 120 via buffer or repeater 172 of memory module 130[0]. Thus, memory module 130[0] has a pointto-point connection to memory controller 120, and memory module 130[1] has a point-to-point connection to memory module 130[0]. In the repeater architecture described herein, memory module 130[0] connects to memory controller 120 with a higher bandwidth connection than memory module 130[1]. In one embodiment, buffer 172 provides an input point for all memory channel signals from memory controller 120 to implement the point-to-point connection, and provides clock, command/write, read, and control interfaces to all memory devices 140 of memory module 130[0]. It will be understood that clock 132 and possibly other control signal lines 138 can be repeated via buffer 172. For purposes of illustration, the command and write signal lines as well as the read signal lines on the repeated channel have different reference numbers (174 and 176, respectively) to identify that the repeated channel or repeated channel portion has a lower bandwidth.

For purposes of description, the point-to-point connection from memory module 130[0] to memory controller 120 will be referred to as a primary channel or a primary connection, and the point-to-point connection from memory module 130[1] to memory module 130[0] will be referred to as a secondary channel or a secondary connection. In either case, it will be understood that memory controller 120 can treat a memory channel as having memory module 130[0] and memory module 130[1] connected to it. The timing of signaling to memory module 130[1] may be different than the timing from memory module 130[0].

As illustrated in system 100, memory module 130[0] has a native connection with memory controller 120 with N command and write DQ signal lines, and M read DQ signal lines. In one embodiment, M is greater than N, although in one embodiment M could be equal to N. Memory module 130[1] does not have a native connection with memory controller 120, and in one embodiment connects with N/2 command and write DQ signal lines 174 and M/2 read signal lines 176. It will be understood that buffer 172 includes hardware to interface the primary connection to the secondary connection. In one embodiment, buffer 172 can include software or other logic to control the connection of command and write signal lines 134 to write signal lines 174 and/or of read signal lines 136 to read signal lines 176.

With point-to-point connections, the loading on the memory channel at memory controller 120 is reduced relative to a multidrop architecture. With reduced loading, system 100 can operate the memory channel at a higher data rate than a corresponding multidrop memory channel. In one embodiment, the higher data rate can enable the use of fewer data pins to provide the same throughput. In one embodiment, the signaling timing on the repeated channel is the same as the signaling timing (e.g., the same data rate per signal line) on the primary channel. However, with a lower bandwidth connection or fewer signal lines, the overall data

throughput on the repeated channel would be less than the data throughput on the primary channel due to the reduced bandwidth of the channel. The system can compensate for the lower bandwidth by increasing the number of cycles (e.g., unit intervals or UIs) used to transfer the data on the primary channel. For example, data sent on N signal lines over X cycles might be sent over 2× cycles on N/2 signal lines.

Traditional memory systems included only bidirectional data channels, which allowed only a single operation on the data bus. In one embodiment, system **100** includes separate write and read data buses, including unidirectional signal lines. Such unidirectional signal lines can enable a read to be performed with one memory module **130** while a write is performed with the other memory module **130**.

In one embodiment, system 100 includes a first group of signal lines to couple point-to-point as a memory channel, such as the signal lines between memory controller 120 or other host device and memory module 130[0]. Memory 20 module 130[0] can be considered a first group of memory devices 140, referring to the memory devices on the memory module. System 100 includes a second group of signal lines to couple point-to-point between memory module 130[0] and memory module 130[1], which can be considered a 25 second group of memory devices 140. Thus, buffer 172 can extend the memory channel to memory module 130[1], but with fewer data lines and a narrow or lower bandwidth. Buffer 172 includes a repeater that can repeat signals from the host on the first group of signal lines to the second group 30 of signal lines, and repeat signals from the memory devices on the second group of signal lines to the host. In general, a buffer enables the point-to-point connection functionality, and provides a single instance of loading on the memory channel for multiple connected memory devices, which can 35 include devices on a repeated channel. A repeater enables the repeating of the memory channel to another memory module and/or group of memory devices.

In one embodiment, the repeated channel from memory module 130[0] to memory module 130[1] includes half as 40 many data signal lines as the primary channel from memory controller 120 to memory module 130[0]. In one embodiment, buffer 172 provides for approximately one half the total bandwidth of the primary channel for use by memory module 130[0], and approximately one half the total bandwidth of the primary channel to be repeated on the secondary channel for use by memory module 130[1]. In one embodiment, depending on the configuration of the primary and secondary channels, buffer 172 can provide more than half the available bandwidth to memory module 130[0], which 50 thus can use more bandwidth than memory module 130[1].

Buffer 172 can separately implement command and write data delivery on repeated write signal lines 174 and read data delivery on repeated read signal lines 176. System 100 can implement any combination of command and write data 55 delivery with read data delivery.

In one embodiment, buffer 172 implements command and write data delivery to the secondary memory module with channel bifurcation and channel passthrough. In one embodiment, buffer 172 implements command and write 60 data delivery to the secondary memory module with selectively sending commands or write data to each memory module, based on either even/odd packet identification or a specific memory module identifier. In one embodiment, buffer 172 implements command and write data delivery to 65 the secondary memory module with speculative passthrough.

**14**

In one embodiment, buffer 172 implements read data delivery from the secondary memory module with channel bifurcation and channel passthrough. In one embodiment, buffer 172 implements read data delivery from the secondary memory module with data accumulation at the buffer, which can then burst the read data to the host. In one embodiment, buffer 172 implements read data delivery from the secondary memory module with bifurcation of the read channel to the host (e.g., treating the read channel as two separate channels), and the buffer includes logic to allow the primary memory module to use both half read channels when available.

FIG. 2 is a block diagram of an embodiment of a system with a repeater channel architecture in which dual data rate (DDR) modules occupy both primary and secondary positions on the lower bandwidth repeated channel. System 200 provides one example of a system in accordance with system 100 of FIG. 1. System 200 includes central processing unit (CPU) 210, which represents a host or host device to which memory resources connect. CPU 210 includes processing resources to perform operations in system 200. CPU 210 also includes a memory controller circuit or equivalent circuitry and logic to drive commands to the memory resources and receive data from the memory resources.

As illustrated, system 200 includes 2× separate channels. In one embodiment, multiple channels connect to the same memory modules, for example in an implementation where a memory module includes memory devices configured to couple to two separate channels. The number of channels in system 200 will be an even number, for example, 2, 4, 6, 8, or some other number of channels. It will be understood that a system can be designed to use an odd number of channels in an alternate embodiment. The placement in the drawing of the channels is merely for illustration, and is not necessarily representative of a practical implementation. In one embodiment, the channels connect memory device groups organized as memory modules, such as DIMMs.

In system 200, each channel includes two memory modules, a primary memory module and a secondary memory module. In one embodiment, all memory modules 220 include the same type of memory devices. For example, in one embodiment, the memory modules all include DDR DRAMs. In one embodiment, the secondary memory modules include a different type of memory from the primary memory modules. Primary DDR module 220[0] couples to CPU 210 with a bandwidth of R for read data and a bandwidth of W for commands and write data. It will be understood that R and W are not necessarily equal, but they could be in one implementation. Secondary module 220[0] couples to primary DDR module 220[0] with a bandwidth of R/2 for read data and a bandwidth of W/2 for commands and write data. Thus, the bandwidth for the secondary connection has half the bandwidth as the primary connection on channel[0]. The remaining channels are similar.

There are known solutions for fully buffered DIMMs that use repeaters on the DIMM. Such solutions implement a full width channel between the first DIMM and the host, as well as a full width channel between the first and second DIMMs. However, in most cases the secondary DIMM does not require a full bandwidth connection, which means the secondary connection is overprovisioned in traditional implementations. System 200 includes a narrow repeated channel. Reducing the repeated channel bandwidth can reduce the number of signal pins required on a package of CPU 210, and on corresponding connectors and PCB trace connections to the secondary DDR module. The reduction of signal pins

and signal line traces results in lower silicon costs, lower power, and lower module connector pin counts.

In one embodiment, the X channels include unidirectional command and write data links and unidirectional read data links. In one embodiment, the width of the channel between 5 the primary module and secondary module is half as wide as the channel width between CPU **210** and the primary module. In one embodiment, primary and secondary modules 220 include DIMMs with DRAMs or SDRAMs compliant with a DDR5 standard. In such an implementation, the 10 primary and secondary DIMMs can each deliver approximately half of the CPU channel bandwidth as dictated by an even address distribution between the two modules. The read data link can deliver full read bandwidth from the memory modules to CPU **210**. In one embodiment, CPU **210** 15 can read from the primary DIMM simultaneously with writing data to the secondary DIMM. In one embodiment, system 200 can bias bandwidth usage towards the primary DIMM. For example, system 200 can provide up to full bandwidth (all of R and/or all of W) to the primary DIMM, 20 and provide whatever bandwidth is requested for the secondary DIMM.

In one embodiment, primary modules **220** include DDR DRAM memory devices, and second modules 220 include NV (nonvolatile) memory devices. In one embodiment, NV 25 modules 220 include three dimensional memory devices including memory cells with a chalcogenide glass. For example, one implementation of nonvolatile memory devices includes three dimensional crosspoint (3DXP) memory. If DDR modules 220 include DDR5 memory 30 devices and NV modules 220 include 3DXP memory devices, the 3DXP memory operates more efficiently at a narrow bandwidth channel than a traditional native memory channel connection. DDR5 memory devices operate at higher speed than 3DXP memory and at lower power. But 35 3DXP memory operates at speeds near DDR memory, and is nonvolatile. Thus, one embodiment of system 200 provides both high speed, low power memory with somewhat lower speed, nonvolatile memory on the same memory channel.

In one embodiment, when DDR modules 220 include 40 DDR5 DIMMs and NV modules 220 include 3DXP memory modules, system 200 shares bandwidth between the DDR5 memory and the 3DXP memory (e.g., via a buffer or repeater) on the DDR modules. In one embodiment, the DDR5 DIMM can deliver full channel bandwidth to CPU 45 230 when there is no 3DXP memory access demand. Due to the bandwidth headroom enabled by the dedicated write and read links, a significant amount of 3DXP memory bandwidth can be delivered to CPU 230 without reducing DDR5 bandwidth.

In one embodiment, the primary DDR modules 220 include a buffer (not specifically shown) that controls read and write portions of the memory channel in accordance with selected or configured delivery mechanisms. In one embodiment, the buffer implements command and write 55 data delivery to the secondary memory module with channel bifurcation and channel passthrough. In one embodiment, the buffer implements command and write data delivery to the secondary memory module with selectively sending commands or write data to each memory module, based on 60 either even/odd packet identification or a specific memory module identifier. In one embodiment, the buffer implements command and write data delivery to the secondary memory module with speculative passthrough.

In one embodiment, the buffer implements read data 65 delivery from the secondary memory module with channel bifurcation and channel passthrough. In one embodiment,

**16**

the buffer implements read data delivery from the secondary memory module with data accumulation at the buffer, which can then burst the read data to the host. In one embodiment, the buffer implements read data delivery from the secondary memory module with bifurcation of the read channel to the host (e.g., treating the read channel as two separate channels), and the buffer includes logic to allow the primary memory module to use both half read channels when available.

In one embodiment, when system 200 includes two memory modules installed on each CPU memory channel, the memory modules can deliver approximately half of the CPU channel bandwidth as dictated by a balanced address distribution between the two modules. When the first memory module is a DDR DIMM, and the second memory module is a 3DXP DIMM, the various delivery mechanisms can be understood as follows.

In one embodiment, with command and write data bifurcation, each DIMM is limited to half of the total bandwidth. Unused 3DXP module bandwidth cannot be utilized by the DDR DIMM. In one embodiment, with command and write data DIMM selection, in one embodiment, the DDR DIMM can respond to both even and odd commands and therefore deliver full command or write data bandwidth. The 3DXP DIMM would be limited to half bandwidth, and would have an additional latency penalty due to a request only being able to start on either the even or odd packet (depending on the system configuration). In one embodiment, with command and write data speculative passthrough, in one embodiment, the DDR DIMM could respond to both even and odd commands and therefore deliver full bandwidth, while the 3DXP DIMM would be limited to half bandwidth. In one embodiment, the 3DXP DIMM would not have an additional latency penalty, due to being able to start a request on both even and odd packets.

In one embodiment, with read channel bifurcation, each DIMM is limited to half of the total read bandwidth. Unused bandwidth available to the second DIMM (whether DDR or 3DXP) cannot be utilized by the first DDR DIMM. In one embodiment, with read accumulation at the first DIMM, the first DIMM delivers read data at full bandwidth and accumulates and bursts data from the second DIMM. The accumulation can be configured to avoid an additional latency penalty for the second DIMM by causing the end of the data burst from the second DIMM to arrive at the first DIMM just prior to sending it to the host. Thus, the data will arrive at the host with the same delay as read channel bifurcation.

In one embodiment, with read channel bifurcation and opportunistic use at the first DIMM, the first DIMM could utilize both half width read channels when available and therefore deliver full bandwidth, while the second DIMM would be limited to half bandwidth. Such an implementation may not require the buffer to accumulate read data from the second DIMM, but may be more complex to schedule.

FIG. 3 is a block diagram of an embodiment of a system with a repeater channel architecture in which both primary and secondary memory modules include a buffer. System 300 provides one example of a system in accordance with system 100, and/or system 200. Host 310 represents logic to control operations in a system in which the memory is included. Host 310 includes processor 316, which can include one or more processing resources that generate requests for access to data stored in memory. Memory controller 318 represents hardware and logic to control access to memory in response to the data needs of processor 316. In one embodiment, memory controller 318 is part of processor 316. Host 310 includes interface 312, which

represents hardware such as pins, balls, pads, and/or other hardware to couple host 310 to the memory.

Host connector **314** represents hardware in system **300** to mount host **310** to a PCB or other substrate to interconnect host **310** with the memory resources of primary module **330** 5 and secondary module **350**. In one embodiment, host **310** includes discrete components coupled to mounting locations on a PCB. In one embodiment, host **310** is incorporated in an SOC that mounts into a socket, and interface **312** can provide electrical and communicative coupling to the socket 10 connector.

Host connector 314 connects to primary module connector 334 with W command and write signal lines 322 (which can also be referred to as a command/write link) and with R read signal lines **324** (which can also be referred to as a read 15 link). Primary module 330 couples to primary module connector 334. Primary module 330 includes memory devices 336, which can be considered a first group of memory devices. Memory devices 336 represent memory resources to be accessed by requests from host 310. In one 20 embodiment, primary module 330 includes buffer 338, which represents logic to enable a point-to-point connection from primary module connector 334 to host connector 314, and a point-to-point connection from primary module connector 334 to secondary module connector 354. Buffer 338 25 includes hardware components to provide the interconnections. In one embodiment, buffer 338 includes firmware and/or software logic to provide an interconnection.

In one embodiment, buffer 338 includes primary interface 332A with a bandwidth of W command/write signal lines 30 and R read signal lines for the primary channel connection to host 310. In one embodiment, buffer 338 includes secondary interface 332B with a bandwidth of W/2 command/ write signal lines and R/2 read signal lines for the secondary channel connection to secondary module 350. Interface 35 332B can represent a repeater circuit of buffer 338. It will be understood that in a practical implementation of a memory subsystem, there are limitations on interconnection based on the pin counts of connectors. Thus, it would impractical with traditional systems to repeat the memory channel from 40 primary module 330 to secondary module 350, at least because there would not be a high enough pin count available to support the connection. Thus, buffered DIMMs can repeat the signal within a DIMM, but traditionally memory channels are not repeated as point-to-point connections from 45 one DIMM to another at least because of physical pin count limitations.

As provided in system 300, the repeated channel from primary module 330 to secondary module 350 has fewer signal lines, which can enable a point-to-point connection 50 without having to increase the connection pin count on current industry-standard connectors. Such a repeated channel includes fewer signal lines, which reduces the bandwidth of the channel. However, the reduced bandwidth can be compensated by increasing the signaling speed on the channel.

Thus, host connector 314 connects to secondary module connector 354 via buffer 338 with W/2 command and write signal lines 342 (which can also be referred to as a command/write link) and with R/2 read signal lines 344 (which 60 can also be referred to as a read link). Secondary module 350 includes memory devices 356, which can be considered a second group of memory devices. Memory devices 356 represent memory resources to be accessed by requests from host 310. In one embodiment, secondary module 350 65 includes buffer 358, which can be the same as or similar to buffer 338. Thus, buffer 358 can include primary interface

**18**

352A and secondary interface 352B. In one embodiment, buffer 358 includes a repeater similar to buffer 338, which would enable buffer 358 to support a repeated channel to a next DIMM (not shown).

In one configuration in accordance with system 300, a single DIMM can be manufactured that can be placed in either primary module connector 334 or in secondary module connector **354**. The advantage to such an implementation is that the same type of DIMM can be connected in any available DIMM slot. Such a configuration may require the DIMM to be aware of its connection type. In one embodiment, secondary module 350 discovers that it is connected to the memory channel with W/2 signal lines for the command/write link and R/2 signal lines for the read link. In one embodiment, secondary module 350 configures internal routing and connections for use of the reduced bandwidth channel, which can include buffering read data to be sent on more UIs. Based on being connected to the lower bandwidth interface, at least some of primary interface 352A and/or secondary interface 352B will not be used by secondary module 350.

In one embodiment, a practical implementation of system 300 can include a circuit board or circuit that includes host connector 314, primary module connector 334, and secondary module connector 354. The signal lines for connection between host connector 314 and primary module connector **334**, and the signal lines for connection between primary module connector 334 and secondary module connector 354 can exist in the circuit even prior to connection of host 310, primary module 330, and/or secondary module 350. Assume for a first configuration (e.g., a 1DPC (one DIMM per channel)) that host 310 and primary module 330 are connected. In such a configuration, in one embodiment, primary module 330 can utilize all bandwidth to host 310. Assume then that a user connects secondary module 350 into system **300**. In such a case (e.g., a 2DPC (two DIMM per channel)), in one embodiment, buffer 338 can share the bandwidth between primary module 330 and secondary module 350 to host 310. In one embodiment, in the 2DPC configuration, system 300 can generate a higher throughput to host 310 based on shared utilization of the separate command/write link and read link. For example, host 310 can coordinate a write to one module while reading from the other.