#### US010235045B2

# (12) United States Patent

## Matsuda

## (10) Patent No.: US 10,235,045 B2

### (45) **Date of Patent:** Mar. 19, 2019

# (54) STORAGE SYSTEM AND CONTROL APPARATUS

## (71) Applicant: FUJITSU LIMITED, Kawasaki-shi,

Kanagawa (JP)

(72) Inventor: Shinnosuke Matsuda, Kawasaki (JP)

(73) Assignee: FUJITSU LIMITED, Kawasaki (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 330 days.

(21) Appl. No.: 15/297,654

(22) Filed: Oct. 19, 2016

#### (65) Prior Publication Data

US 2017/0139598 A1 May 18, 2017

#### (30) Foreign Application Priority Data

Nov. 13, 2015 (JP) ...... 2015-223045

(51) **Int. Cl.**

$G06F 3/06 \qquad (2006.01)$

G06F 11/20 (2006.01)

(52) **U.S. Cl.**

sh

#### (58) Field of Classification Search

CPC ...... G06F 3/0604; G06F 11/20; G06F 3/068; G06F 3/0653

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,928,367 A * | 7/1999                    | Nelson G06F 11/1666              |

|---------------|---------------------------|----------------------------------|

|               | <b>=</b> ( <b>=</b> 0 0 5 | 714/6.3                          |

| 7,055,057 B2* | 5/2006                    | Achiwa                           |

| 7 356 581 B2* | 4/2008                    | 711/162<br>Hashimoto G06F 3/0613 |

| 7,550,501 B2  | 1,2000                    | 709/224                          |

| 8,201,020 B2* | 6/2012                    | Cagno G06F 11/2089               |

|               |                           | 714/11                           |

#### FOREIGN PATENT DOCUMENTS

| JP | 7-244642 | 9/1995 |

|----|----------|--------|

| JP | 8-241173 | 9/1996 |

\* cited by examiner

Primary Examiner — Hashim S Bhatti

(74) Attorney, Agent, or Firm — Fujitsu Patent Center

#### (57) ABSTRACT

A first control apparatus includes a first communication port that satisfies, among execution conditions about predetermined management processing, a neighboring port condition about a communication port connected to an execution apparatus that performs the management processing. The first control apparatus satisfies, among the executions conditions, a neighboring apparatus condition about a neighboring apparatus that neighbors the execution apparatus. A second control apparatus includes a second communication port that satisfies, among the execution conditions, a connection port condition about a communication port connected to the neighboring apparatus. The second control apparatus satisfies, among the execution conditions, an execution apparatus condition about the execution apparatus. The first and second communication ports of the first and second control apparatuses are connected to each other via (Continued)

MASTER CONDITIONS EXECUTION DEVICE CONDITION, NEIGHBORING DEVICE CONDITION. MASTER NEIGHBORING PORT CONDITION CONNECTION PORT CONDITION LEVELS CONTROL DEVICE (#0), COMMUNICATION PORT (#1) CONTROL DEVICE (#1), MASTER 1 COMMUNICATION PORT (#0) CONTROL DEVICE (#1), COMMUNICATION PORT (#1) MASTER 2 CONTROL DEVICE (#0), COMMUNICATION PORT (#0) (MONITORING) 4d MANAGEMENT . MANAGEMENT MANAGEMENT CIRCUIT MANAGEMENT MANAGEMENT MANAGEMENT CIRCUIT CIRCUIT CIRCUIT CIRCUIT CIRCUIT 14c CONTROL DEVICE (#1) CONTROL CONTROL CONTROL DEVICE (#0) CONTROL CONTROL DEVICE (#1) DEVICE (#0) DEVICE (#0) DEVICE (#1) MASTER 2 16 MASTER 1 **ENGLOSURE** ENCLOSURE **ENCLOSURE** STORAGE 10c STORAGE 10b 10a STORAGE DEVICE DEVICE DEVICE

## US 10,235,045 B2

Page 2

a communication cable. The second control apparatus performs the management processing when the second communication port is connected to the first communication port.

6 Claims, 30 Drawing Sheets

| SIGNAL<br>NAME | COMMUNICATION DIRECTION | DESCRIPTION       |

|----------------|-------------------------|-------------------|

| TXCLK          | Out                     | CLOCK TRANSMITTED |

| TXDATA         | Out                     | DATA TRANSMITTED  |

| RXCLK          | In                      | CLOCK RECEIVED    |

| RXDATA         | Ιm                      | DATA RECEIVED     |

FIG. 5

FIG. 7

|              |                    | 115cb                 |

|--------------|--------------------|-----------------------|

| MA           | STER CONDITION TAI | BLE                   |

| MASTER LEVEL | CPD IN CPD PACKET  | CPD OF RECEIVING PORT |

| MASTER 1     | 100                | 011                   |

| MASTER 2     | 000                | 111                   |

FIG. 8

| PID           |                                        | SID                                  |                                       | TID_CNT                 |       | TIDSET                  |                | TID VAL    |                                         |

|---------------|----------------------------------------|--------------------------------------|---------------------------------------|-------------------------|-------|-------------------------|----------------|------------|-----------------------------------------|

| type          | value                                  | type                                 | ∨a≹ue                                 | type                    | value | type                    | value          | type       | value                                   |

|               |                                        |                                      | ֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓ | subtraction<br>transfer | 0xFE  | target initial<br>value | 0xFF~0x00      | rent       |                                         |

|               | **********                             | data<br>Cata                         | <u>`</u>                              | addition transfer       | 0xFD  | المهاد                  | 0xFF~0x00      | atue       |                                         |

|               | *******                                |                                      |                                       | specified target        | OXFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                              |

| transmitted   | Ç                                      | master notification<br>communication | OXFE                                  | specified target        | 0xFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                              |

|               | <u>-</u><br>                           | WatchDog<br>communication 1          | OXED                                  | specified target        | 0xFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                              |

|               |                                        | WatchDog<br>communication 2          | 0xFC                                  | specified target        | OxFC  | master CM<br>numbers    | 0x02,0x03,0x04 |            | Don't care                              |

|               | *******                                | WatchDog<br>communication 3          | OxFB                                  | specified target        | OXFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                              |

|               |                                        | WatchDog<br>communication 4          | OxFA                                  | specified target        | OXFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                              |

|               |                                        |                                      |                                       | subtraction<br>transfer | OXFE  | target initial<br>Value | 0xFF~0x00      | rent       | いつろいつごコンと                               |

|               |                                        |                                      | ج<br>ج ک                              | addition transfer       | OXFD  | ديد.                    | OXFF~0x00      | value      | つつくつ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |

|               |                                        |                                      | かんぐひ                                  | specified target        | OXFC  | 7. 0                    | 0x02,0x03,0x04 | Don't care | Don't care                              |

| transmitted   | 2,5                                    | master notification<br>communication | 0×FE                                  | specified target        | OXFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                              |

| STON Master Z | \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ | WatchDog<br>communication 1          | 0×FD                                  | specified target        | OxFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                              |

|               | *******                                | WatchDog<br>communication 2          | 0×FC                                  | specified target        | OxFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                              |

|               |                                        | WatchDog<br>communication 3          | 0×FB                                  | specified target        | OXFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                              |

|               |                                        | WatchDog<br>communication 4          | 0xFA                                  | specified target        | OXF.C | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                              |

| DID         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 212                                  |                     | TID CNT                 |       | TIDISET                 |                | TIDVAL     |                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------|-------------------------|-------|-------------------------|----------------|------------|----------------------------|

| type        | value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | type                                 | value               | type                    | value | type                    | value          | type       | value                      |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      | i<br>c              | subtraction<br>transfer | OXFE  | target initial<br>value | 0xFF~0x00      | current    |                            |

|             | <del>13337727233</del> 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D<br>Q                               |                     | addition transfer       | 0xFD  | ge<br>Leet              | 0xFF~0x00      | 70         | DOXO LIXO                  |

|             | 10000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      | )<br>)<br>)         | specified target        | 0xFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

| transmitted | \frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac}\frac{\frac{\frac{\frac{\frac{\fir}{\fint}}}}}}}}{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac}}}}}}{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac}}}}}}}}}{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac}}}}}}}{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\fir}}}}}}}}{\frac{\frac{\frac{\frac{\frac{\frac{\frac{\frac | master notification<br>communication | OXFE                | specified target        | OXFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

|             | )<br>}<br>}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | WatchDog<br>communication 1          | 0×FD                | specified target        | OXFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

|             | ~~~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | WatchDog<br>communication 2          | OxFC                | specified target        | OxFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WatchDog<br>communication 3          | OxFB                | specified target        | 0xFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WatchDog<br>communication 4          | OxFA                | specified target        | 0xFC  | master GM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      | <br> -<br> -        | subtraction<br>transfer | OXFE  | target initial<br>value | OXFF~0x00      | current    |                            |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>0</u>                             | ر<br>کر کر<br>کر کر | addition transfer       | OXED  | target final<br>Value   | 0xFF~0x00      | ~~         | 3<br>3<br>3<br>4<br>5<br>5 |

|             | ********                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      | )<br>)<br>()        | specified target        | OXFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

| transmitted | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | master notification<br>communication | OXFE                | specified target        | OXFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

|             | <b>5</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | WatchDog<br>communication 1          | OXFD                | specified target        | 0xFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

|             | *********************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | WatchDog<br>communication 2          | OXFC                | specified target        | OxFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

|             | Night Street and August Street Street                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | WatchDog<br>communication 3          | OXFB                | specified target        | OXFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WatchDog<br>communication 4          | OxFA                | specified target        | OxFC  | master CM<br>numbers    | 0x02,0x03,0x04 | Don't care | Don't care                 |

| MASTER NAME | MONITORING<br>TARGET |

|-------------|----------------------|

| MASTER 1    | MASTER 2             |

| MASTER 2    | MASTER 1             |

| MASTER 3    | MASTER 1             |

| MASTER 4    | MASTER 2             |

FIG. 19

| MASTER   |                        | MALFUNCTIONIN        | NING MASTER |                        |

|----------|------------------------|----------------------|-------------|------------------------|

| LEVEL    | MASTER                 | MASTER 2             | MASTER 3    | MASTER 4               |

| MASTER 1 | Degrade                | , keep               | жеер        | жеер                   |

| MASTER 2 | Failover →<br>MASTER 1 | Degrade              | кеер        | رة<br>م<br>م<br>ت<br>ت |

| MASTER 3 | Failover →<br>MASTER 2 | Кеер                 | Degrade     | Keed                   |

| MASTER 4 | Fa‱ver —><br>MASTER 3  | Fa‱ver →<br>MASTER 2 | фаэ         | Degrade                |

| MASTER   |                                   | TWO MALFUNCTI                       | TWO MALFUNCTIONING MASTERS |                 |

|----------|-----------------------------------|-------------------------------------|----------------------------|-----------------|

| LEVEL    | MASTERS 1 AND 3                   | MASTERS 2 AND 4                     | MASTERS 1 AND 2            | MASTERS 3 AND 4 |

| MASTER   | Degrade                           | цеер                                | Degrade                    | Keep            |

| MASTER 2 | Failover —<br>MASTER 1            | Degrade                             | Degrade                    | XeeD.           |

| MASTER 3 | Degrade                           | Failover —  MASTER 2—  (B) MASTER 2 | Failover →<br>MASTER 1     | Degrade         |

| MASTER 4 | Failover — MASTER 2— (A) MASTER 2 | Degrade                             | Failover →<br>MASTER 2     | Degrade         |

FIG. 29

FIG. 30

# STORAGE SYSTEM AND CONTROL APPARATUS

# CROSS-REFERENCE TO RELATED APPLICATION

This application is based upon and claims the benefit of priority of the prior Japanese Patent Application No. 2015-223045, filed on Nov. 13, 2015, the entire contents of which are incorporated herein by reference.

#### **FIELD**

The embodiments discussed herein relate to a storage system and a control apparatus.

#### **BACKGROUND**

When the memory capacity or performance of a storage system becomes insufficient, for example, a scale-out architecture is applied to the storage system. For example, a device enclosure (DE) including a plurality of hard disks and a controller enclosure (CE) are added to the storage system. The CE includes a plurality of controller modules (CMs). Each of the CMs is connected to the hard disks. When a host 25 device requests access to one of the hard disks, a corresponding CM controls the access to the hard disk.

Among the storage systems, there is a scale-out-type storage system to which a storage device is easily added. In this scale-out-type storage system, for example, an individual service controller (SVC) provided in a device called a front end controller (FE) manages CMs. For example, each of the CMs is connected to an SVC via a management bus. The SVC communicates with each of the CMs via a management bus, so as to manage operations of the CMs. For 35 example, the SVC controls power supplies of the CMs, monitors statuses of the CMs, and acquires logs from the CMs. In addition, the SVC performs reset control and turns on and off light emitting diodes (LED), for example.

Various techniques are used to manage a storage system. 40 For example, there is a system that is configured to maintain consistency of file management information. In this system, a master secondary storage control device per file is selected and determined from a plurality of secondary storage control devices by using a random number and a modulo operation. 45 There is also a system that promptly performs accurate failure recovery when a control device or a memory in a disk storage system malfunctions. In this system, the failure recovery is performed by using mirror-type memories that synchronize with each other in real time in two control 50 devices.

See, for example, Japanese Laid-open Patent Publication Nos. 07-244642 and 08-241173.

In a conventional scale-out-type storage system, an SVC manages CMs. Thus, when this SVC malfunctions, the system cannot be operated properly. Thus, to improve reliability, two SVCs are included in an FE. If there are two SVCs, even when one of the SVCs malfunctions, the other SVC can properly manage the CMs. However, if two SVCs are used, the size of the FE is increased. As a result, more space is needed to install the FE, and the cost is also increased.

FIG. 3 illustrates an of an individual CM; FIG. 5 illustrates are nication between CMs FIG. 6 illustrates a FIG. 7 is a block functions of an FPGA

One possible solution to this problem is to eliminate the SVCs and allow one of the plurality of CMs to manage all the CMs. If one of the CMs is allowed to manage all the 65 mined; CMs, no SVCs are needed in a scale-out-type storage FIG. system. Consequently, less space is needed for the installapacket;

2

tion of the system. However, even when each of the CMs is provided with the same management function as that of an SVC, it has conventionally been impossible to determine which one of the plurality of CMs needs to be the management CM. Thus, it is difficult to eliminate the SVCs and allow one of the plurality of CMs to manage all the CMs.

Each of the CMs in the above description is an example of a control device that controls storage devices. Regarding general control devices, as is the case with the CMs, it is impossible to determine which one of a plurality of control devices needs to be allowed to manage all the control devices.

#### **SUMMARY**

According to one aspect, there is provided a storage system including: a storage apparatus; a first control apparatus which controls the storage apparatus, which includes a first communication port satisfying, among execution conditions about predetermined management processing, a neighboring port condition about a communication port connected to an execution apparatus that performs the management processing, and which satisfies, among the execution conditions, a neighboring apparatus condition about a neighboring apparatus that neighbors the execution apparatus; a second control apparatus which controls the storage apparatus, which includes a second communication port that satisfies, among the execution conditions, a connection port condition about a communication port connected to the neighboring apparatus, which satisfies, among the execution conditions, an execution apparatus condition about the execution apparatus, and which determines that the execution conditions are satisfied and performs the management processing when the second communication port is connected to the first communication port; and a communication cable that connects the first communication port of the first control apparatus and the second communication port of the second control apparatus.

The object and advantages of the invention will be realized and attained by means of the elements and combinations particularly pointed out in the claims.

It is to be understood that both the foregoing general description and the following detailed description are exemplary and explanatory and are not restrictive of the invention.

#### BRIEF DESCRIPTION OF DRAWINGS

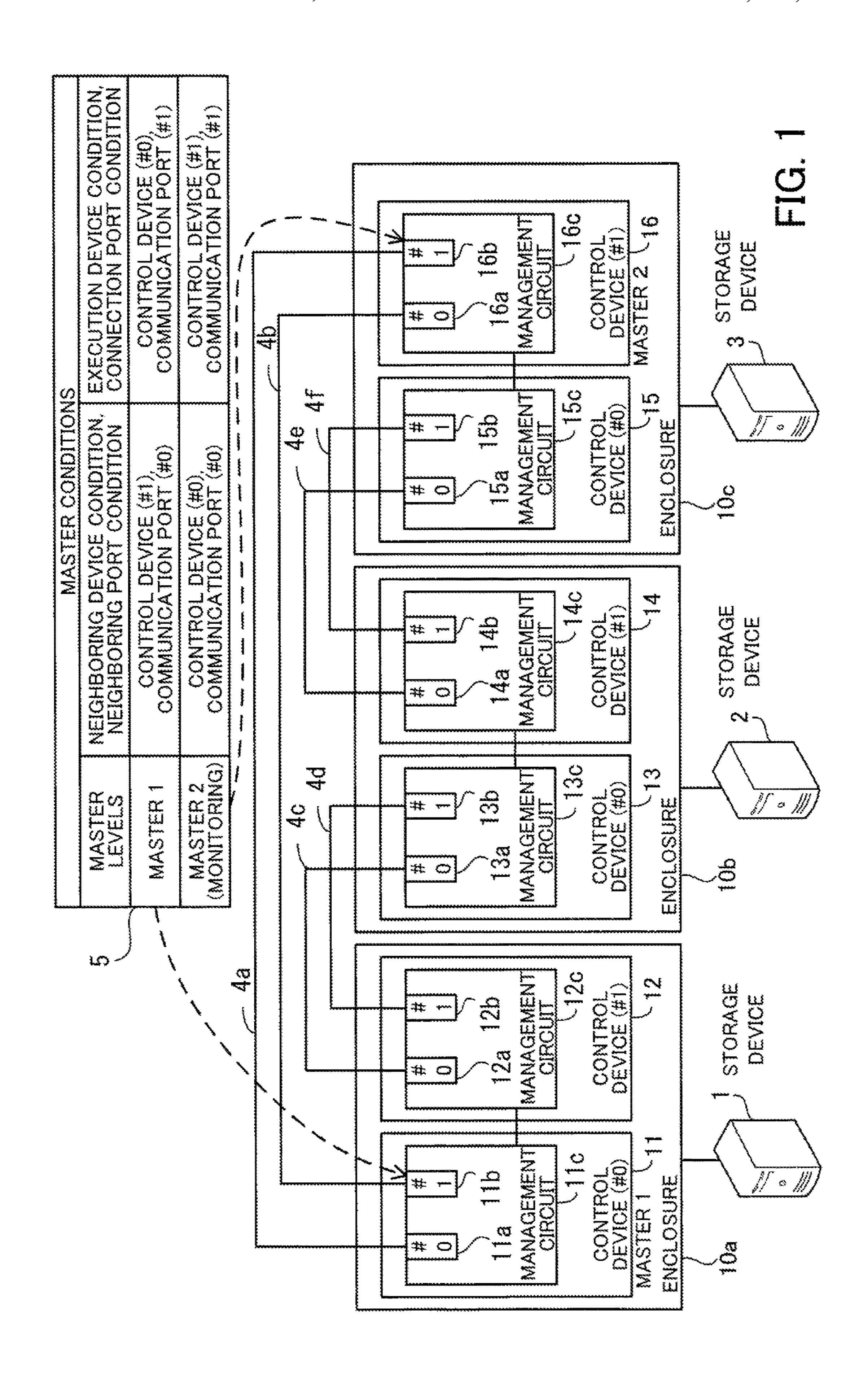

- FIG. 1 illustrates an example of a configuration of a storage system according to a first embodiment;

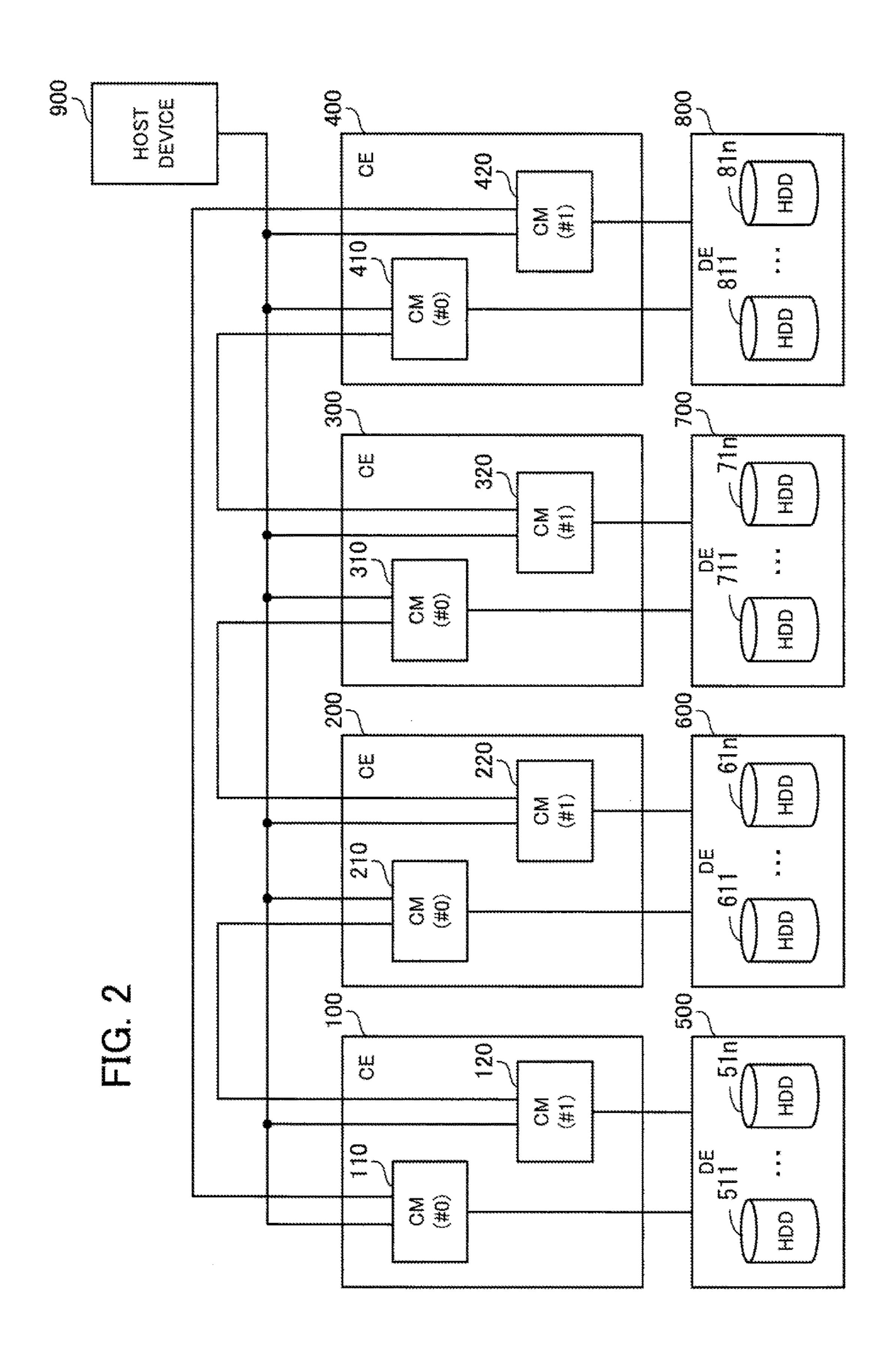

- FIG. 2 illustrates an example of a configuration of a storage system according to a second embodiment;

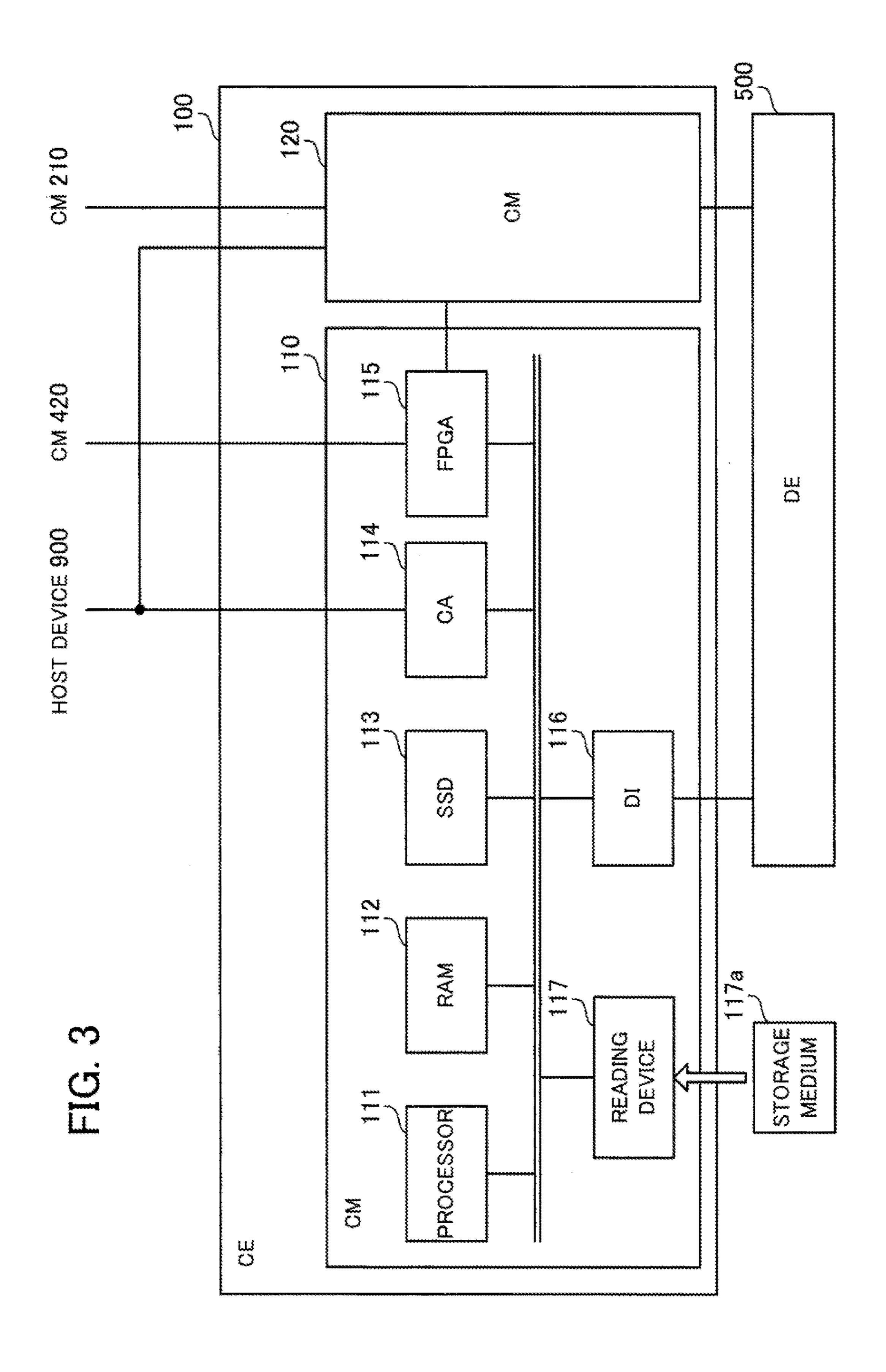

- FIG. 3 illustrates an example of a hardware configuration of an individual CM;

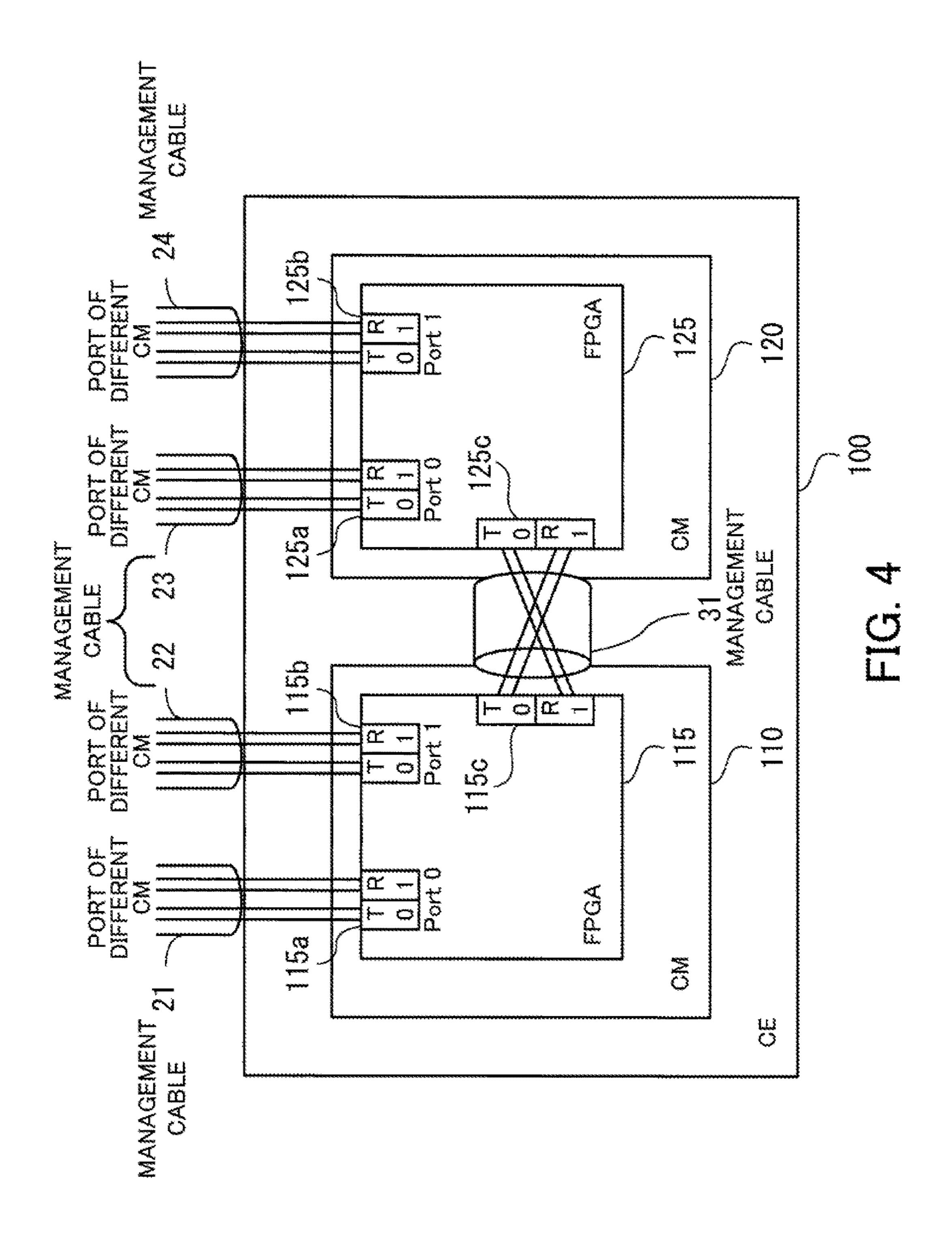

- FIG. 4 illustrates an example of communication ports in an individual field programmable gate array (FPGA);

- FIG. 5 illustrates an example of signals used in communication between CMs;

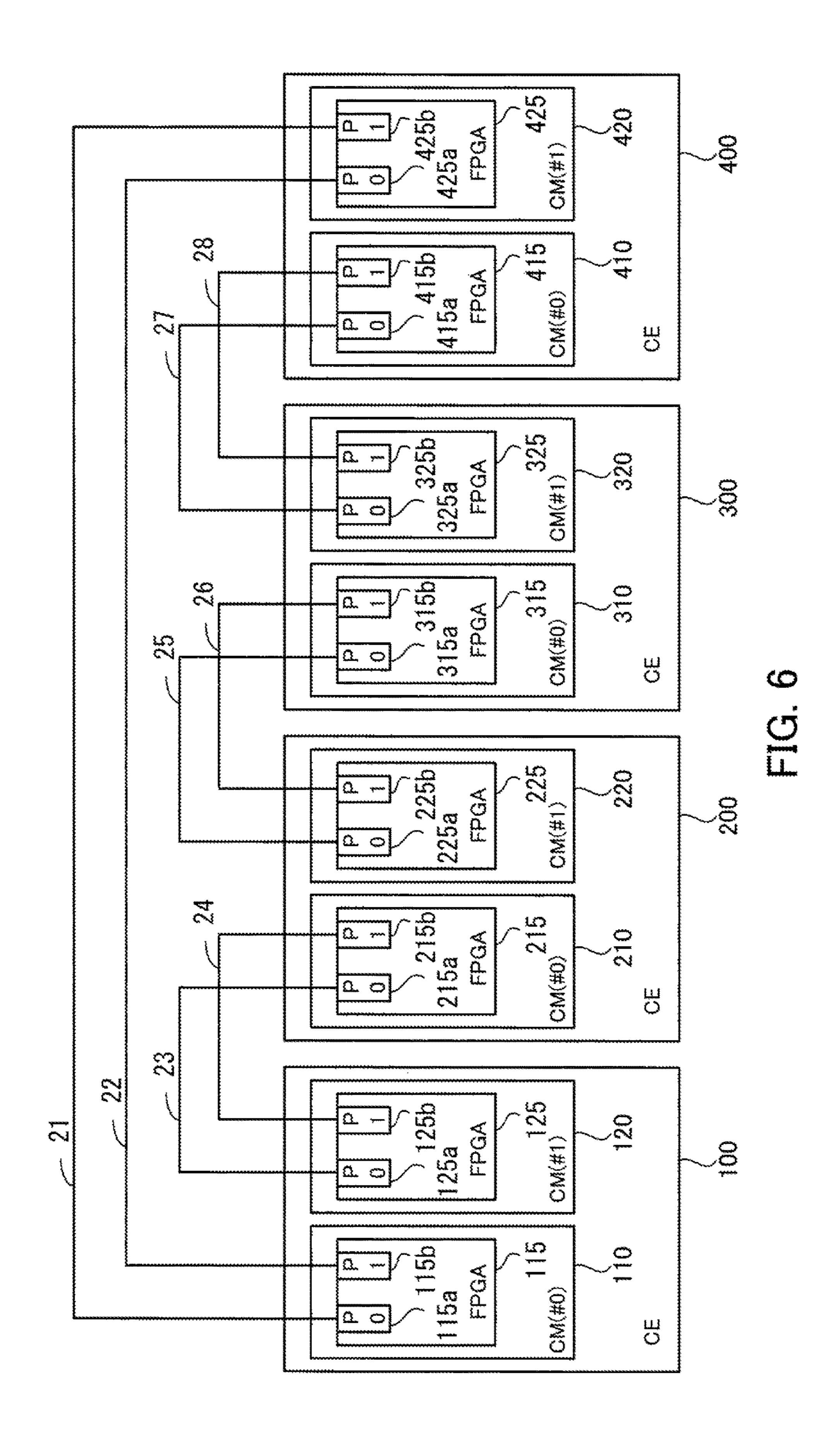

- FIG. 6 illustrates a connection mode among CMs;

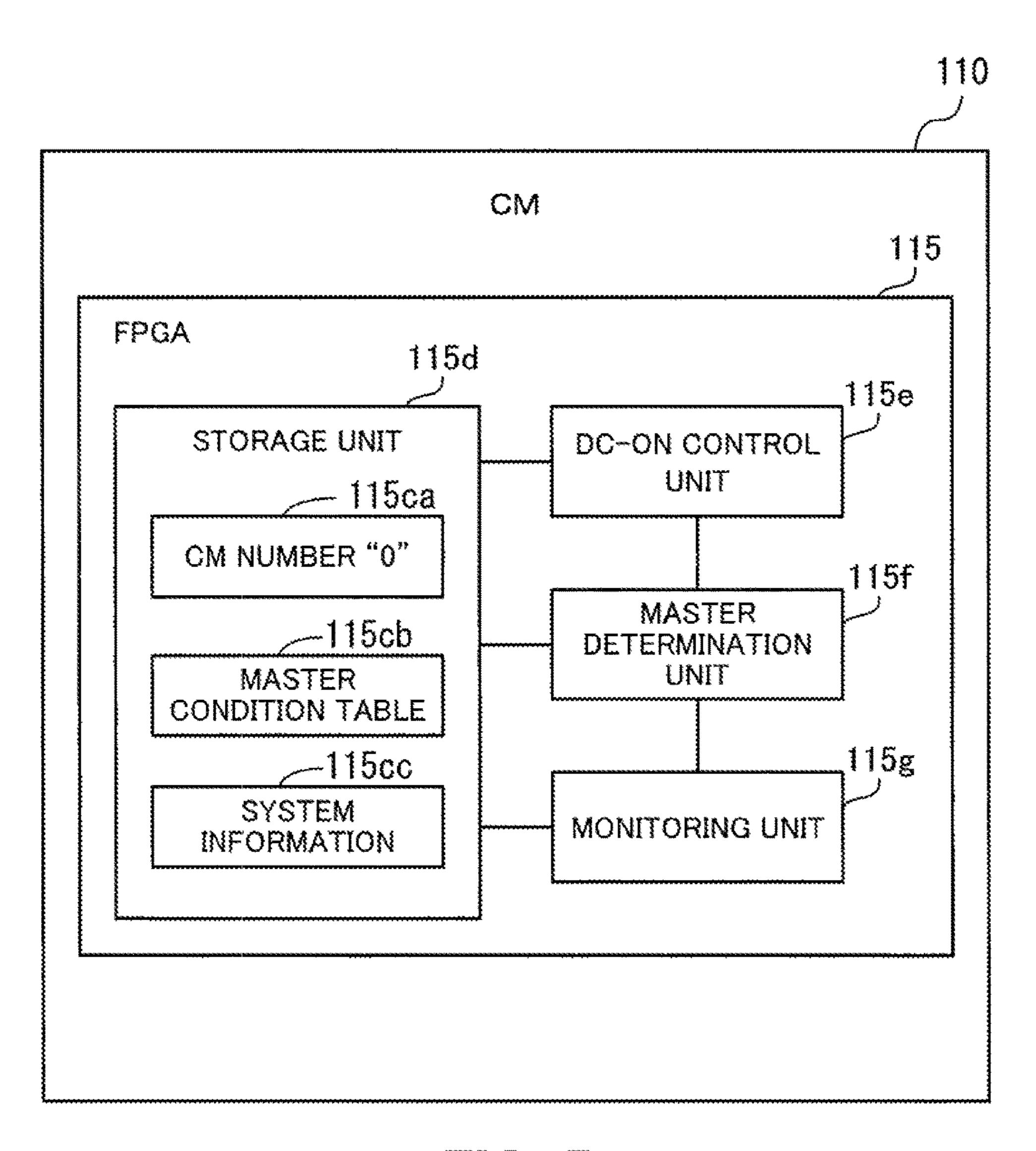

- FIG. 7 is a block diagram illustrating an example of functions of an FPGA;

- FIG. 8 illustrates an example of a master condition table;

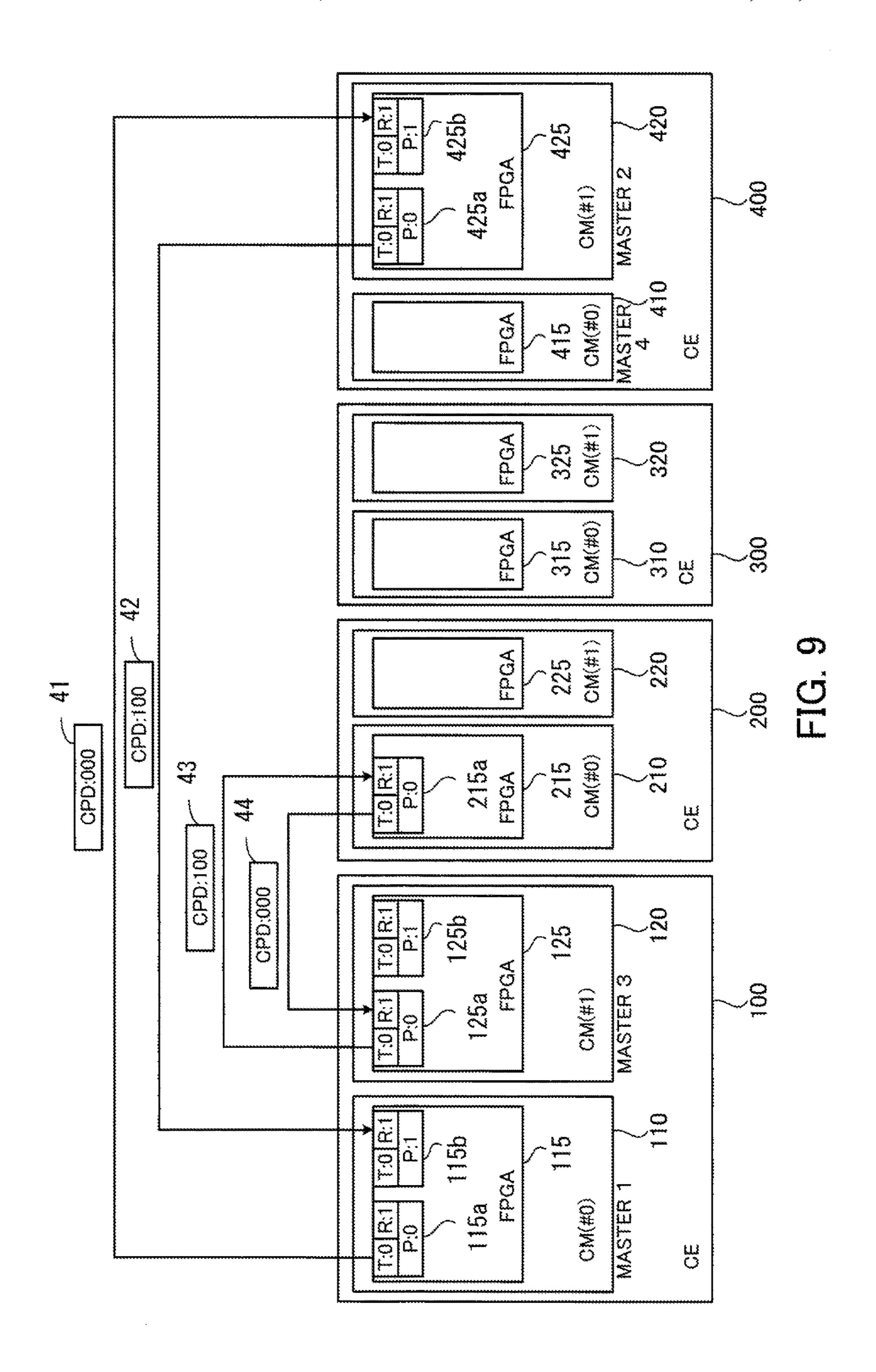

- FIG. 9 illustrates an example of how masters are determined;

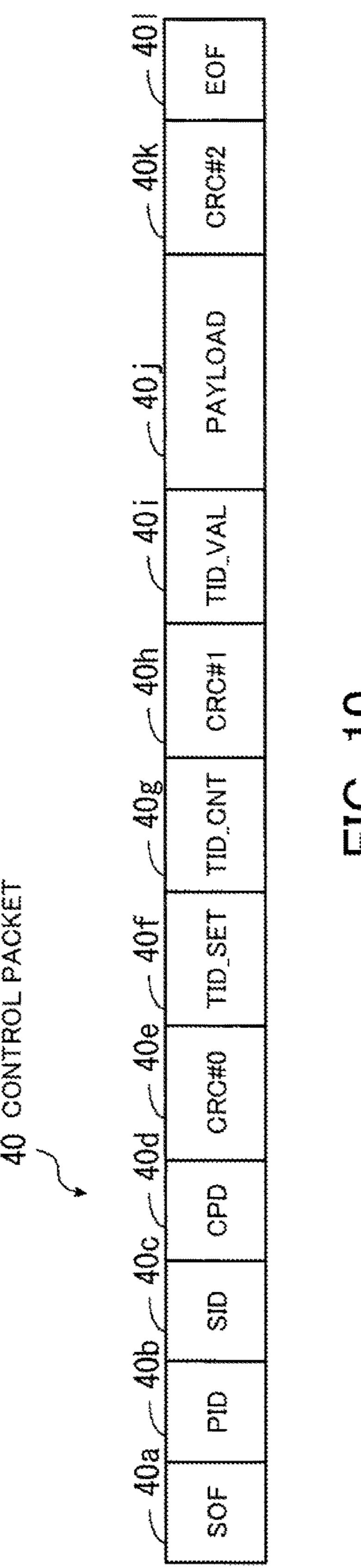

- FIG. 10 illustrates an example of a format of a control packet;

FIG. 11 illustrates examples of data in control packets transmitted by "master 1" and "master 2";

FIG. 12 illustrates examples of data in control packets transmitted by "master 3" and "master 4";

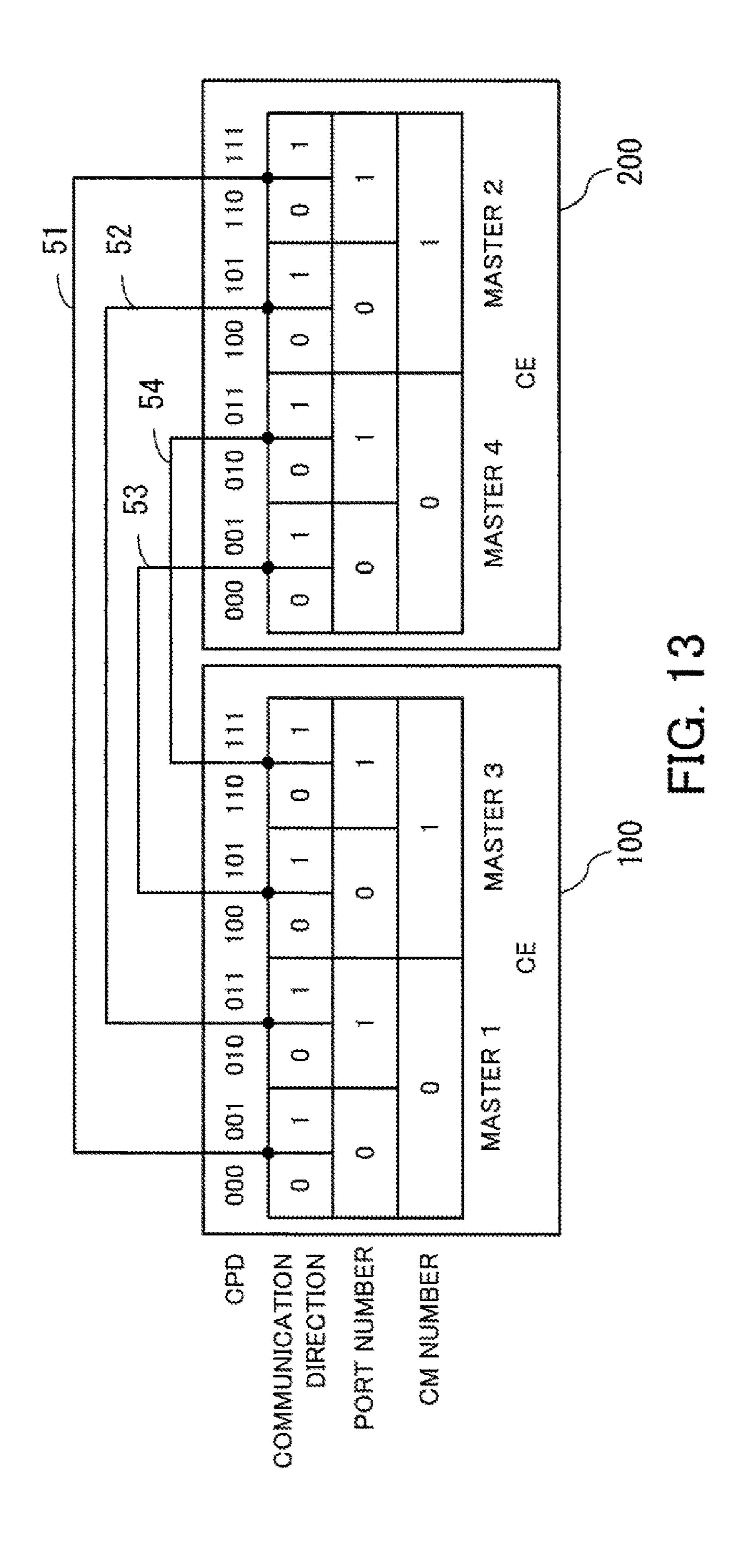

FIG. 13 illustrates a connection example of two CEs;

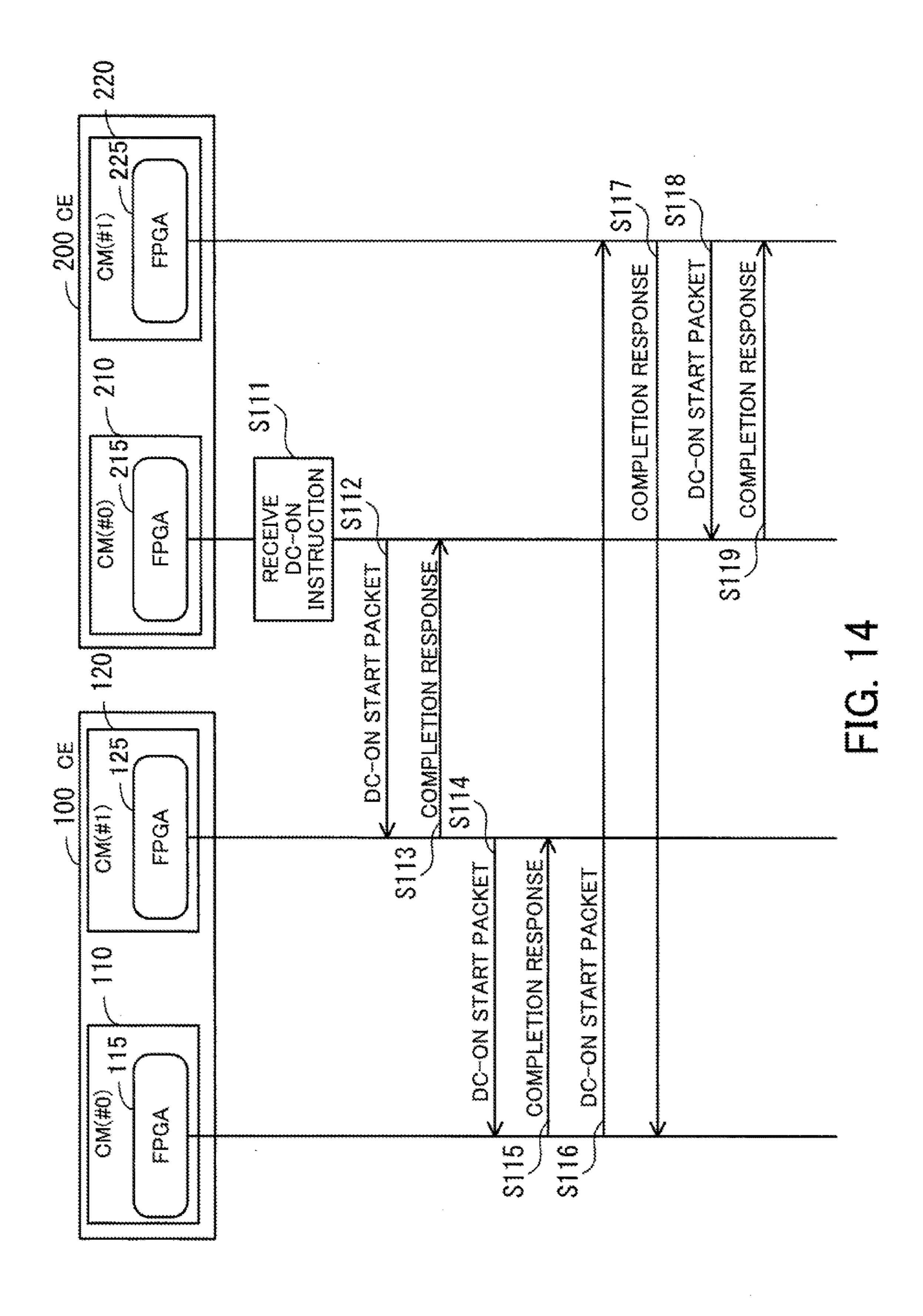

FIG. 14 is a first sequence diagram illustrating a procedure of DC-ON processing;

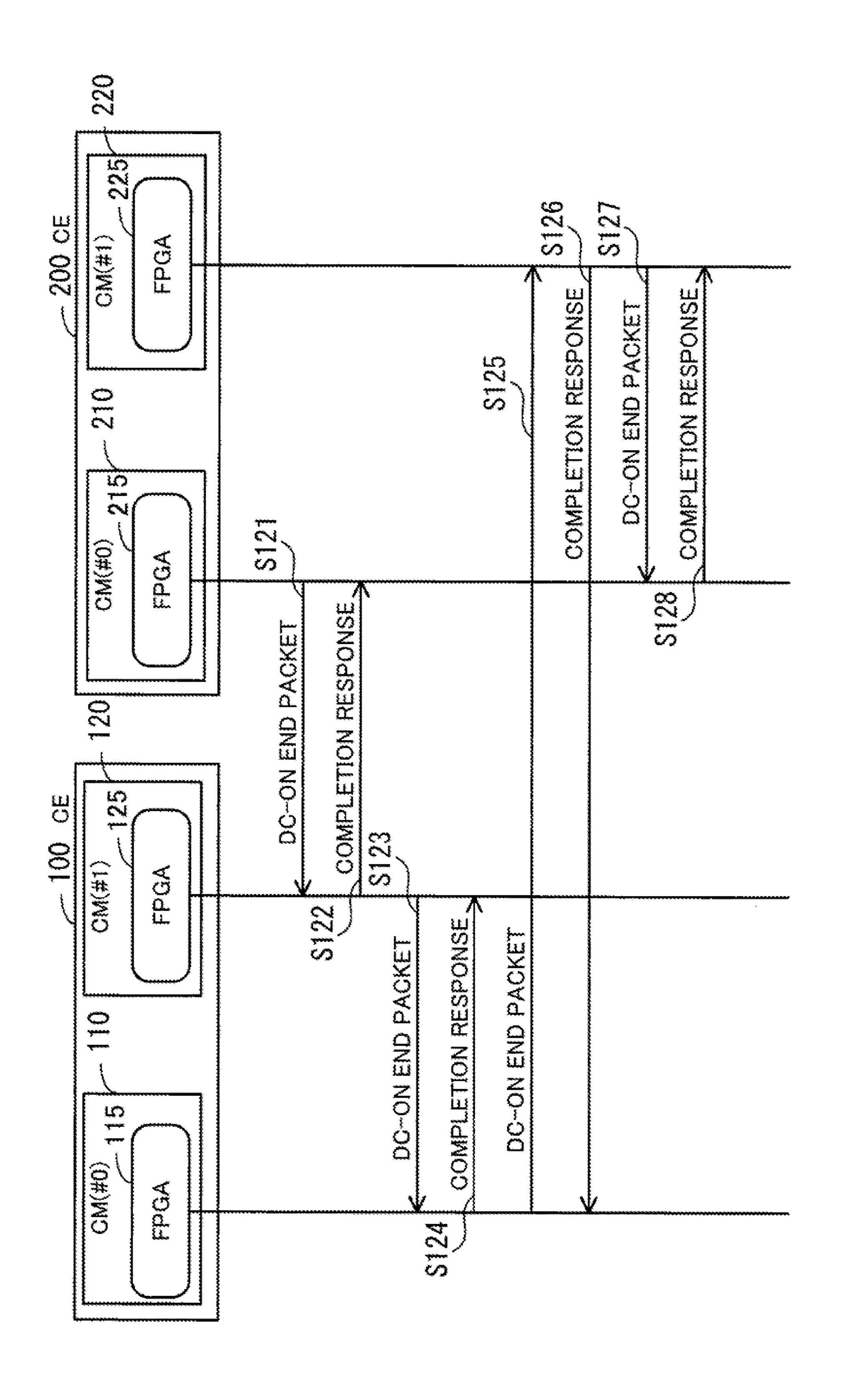

FIG. 15 is a second sequence diagram illustrating the procedure of DC-ON processing;

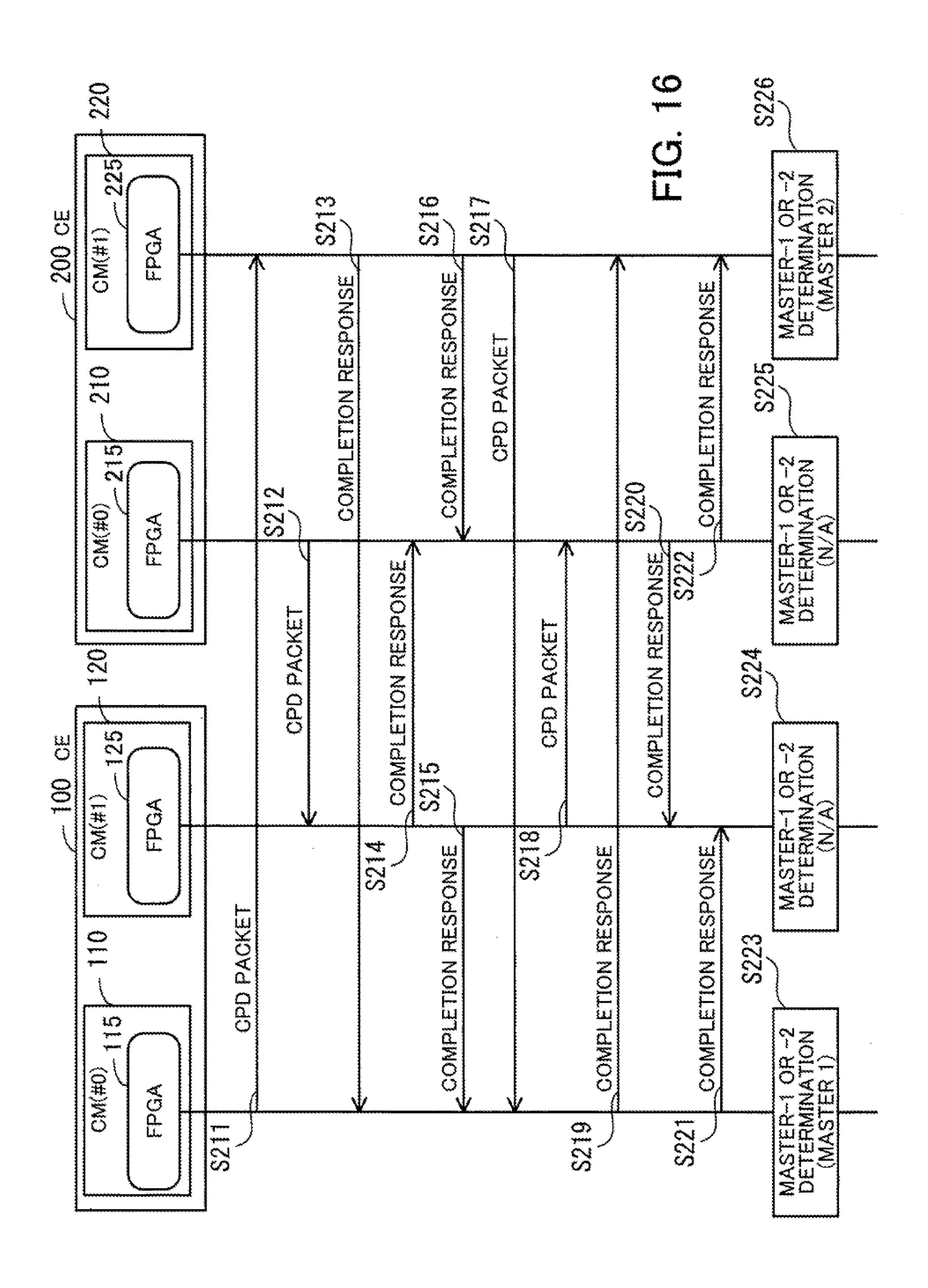

FIG. **16** is a first sequence diagram illustrating a procedure of master determination processing;

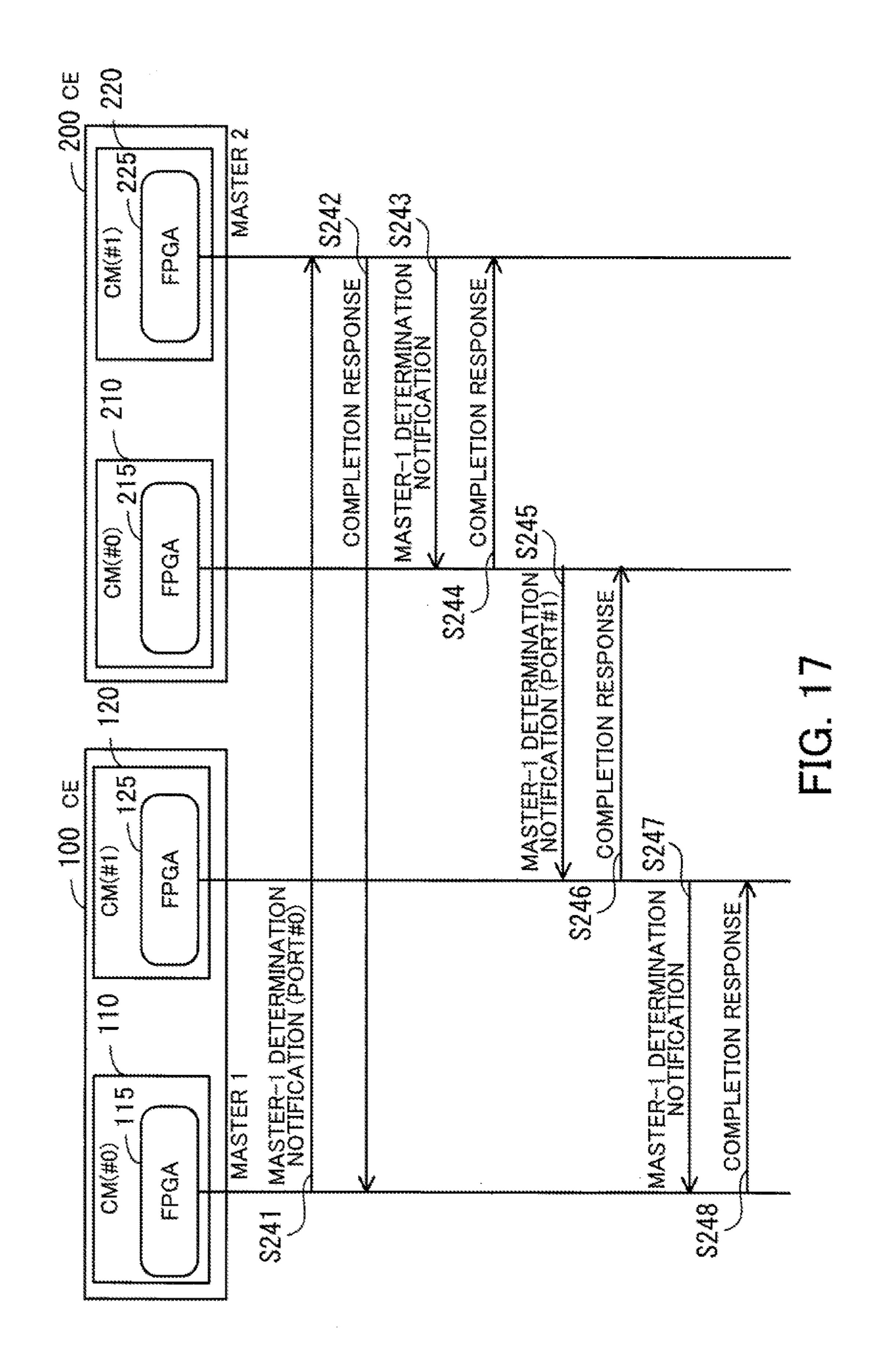

FIG. 17 is a second sequence diagram illustrating the procedure of master determination processing;

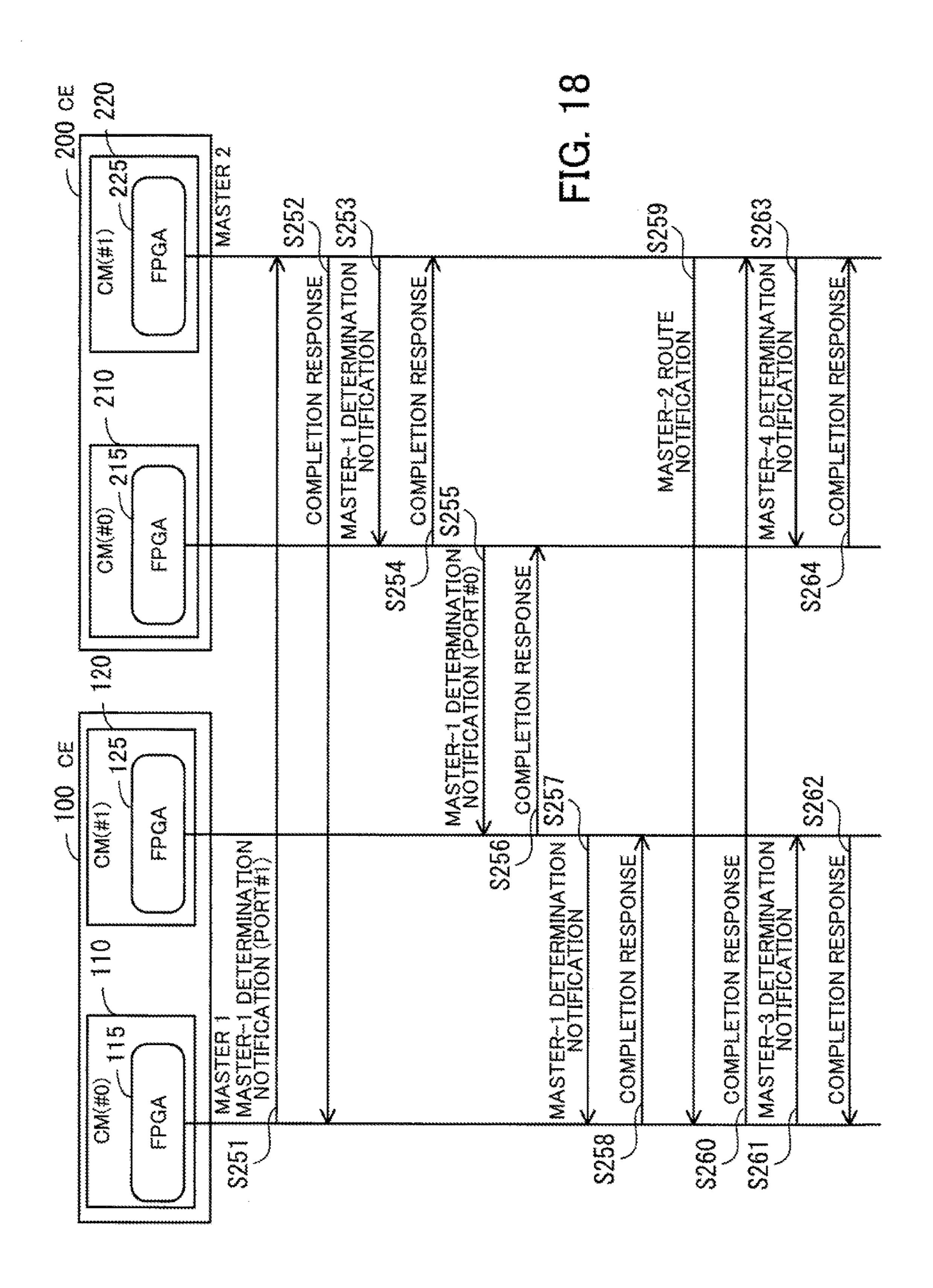

FIG. 18 is a third sequence diagram illustrating the procedure of master determination processing;

FIG. 19 illustrates an example of monitoring targets;

FIG. 20 illustrates an example of failover processing performed when a master CM malfunctions;

FIG. 21 illustrates an example of failover processing performed when two master CMs malfunction;

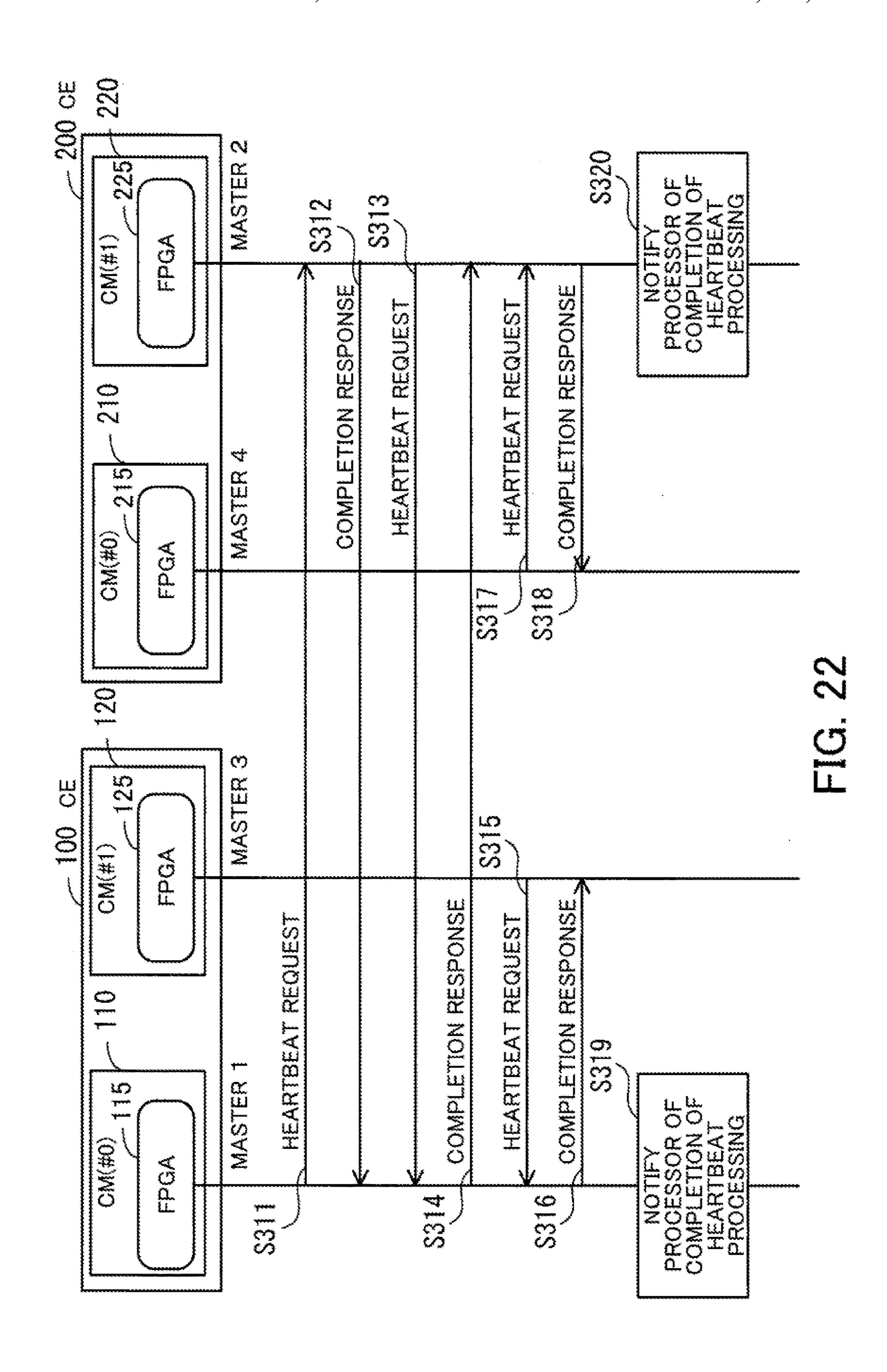

FIG. 22 is a sequence diagram illustrating an example of the monitoring processing performed by the master CMs;

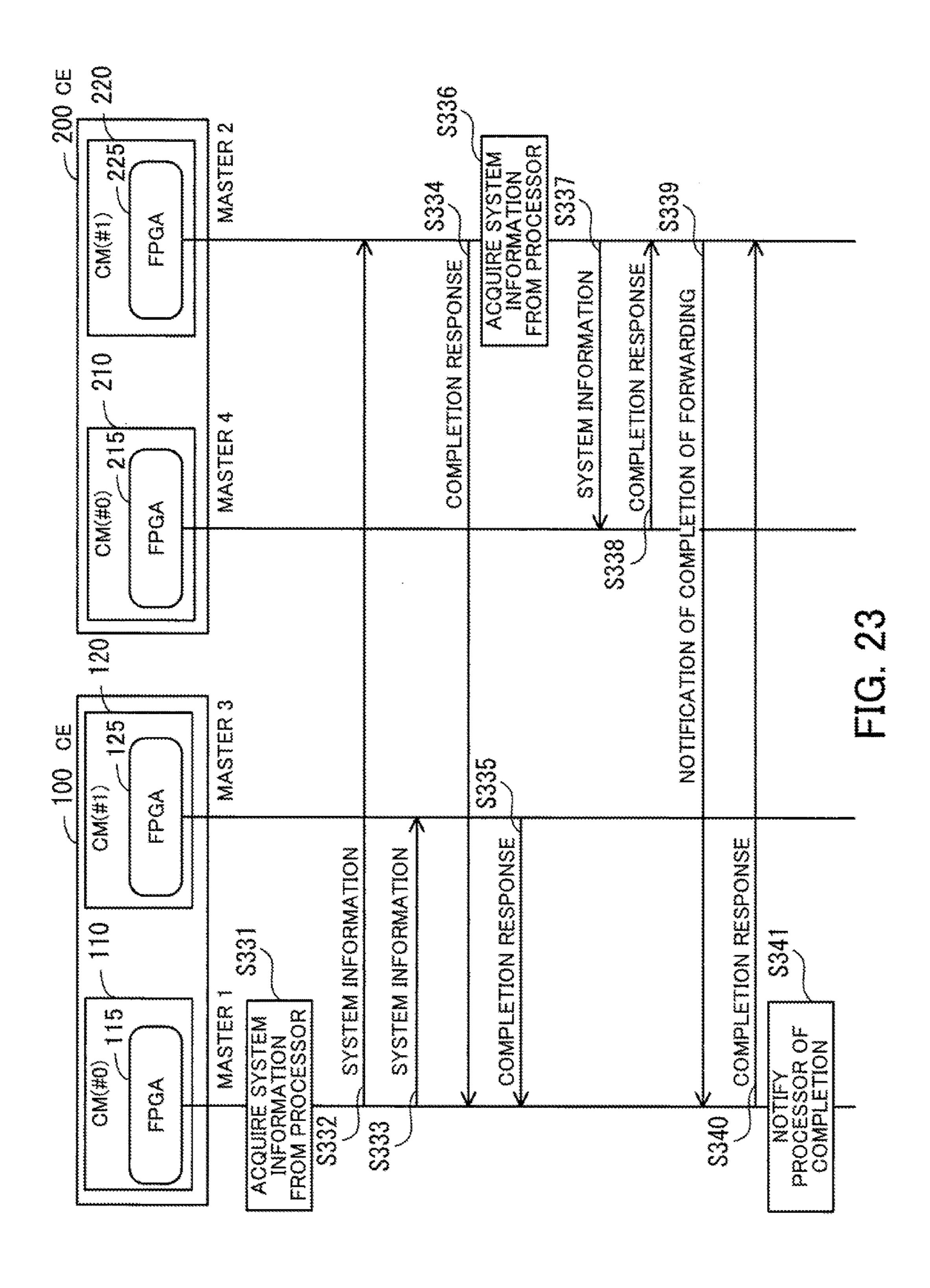

FIG. 23 is a sequence diagram illustrating an example of mirroring processing in the system information;

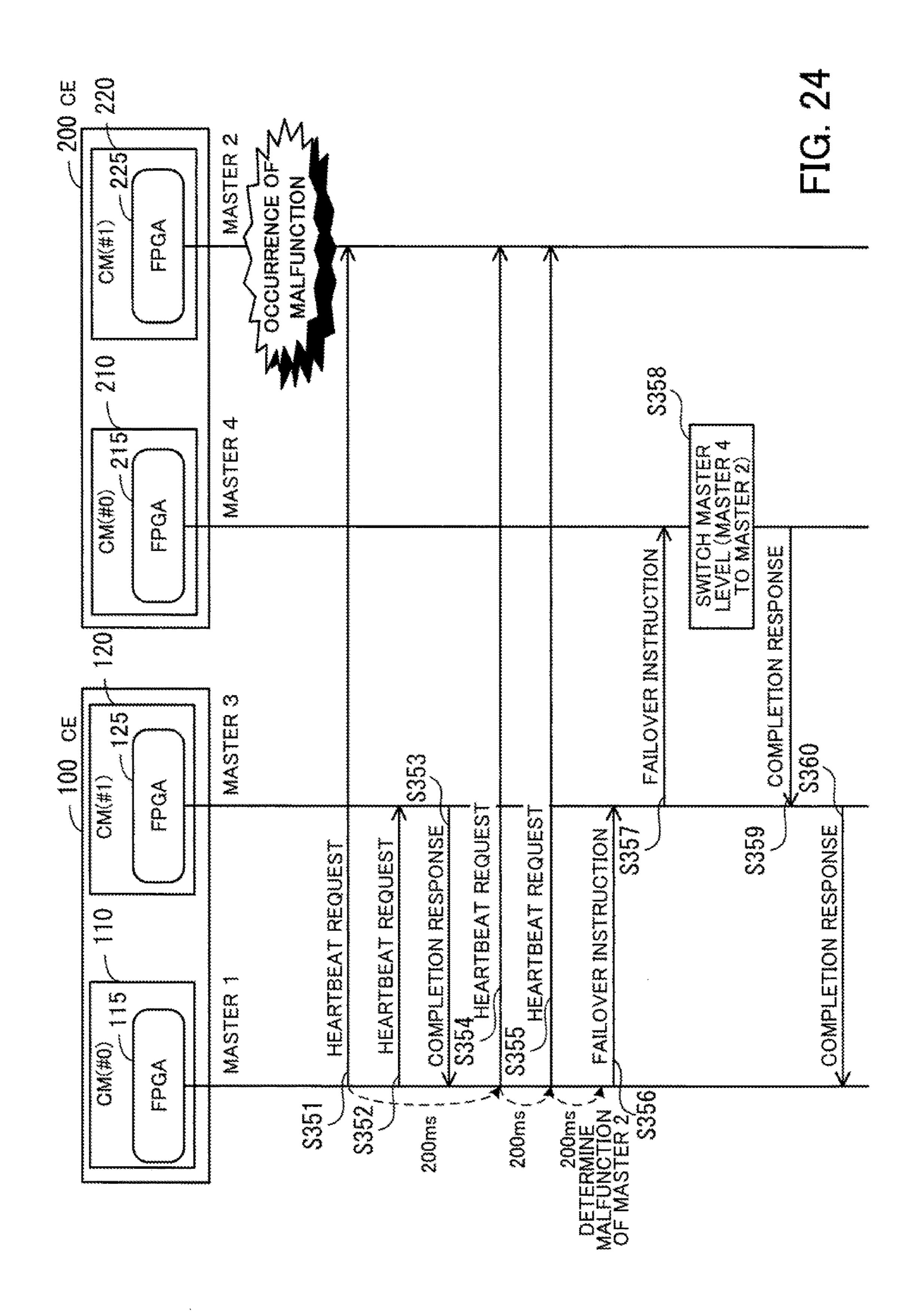

FIG. 24 is a sequence diagram illustrating an example of a procedure of failover processing;

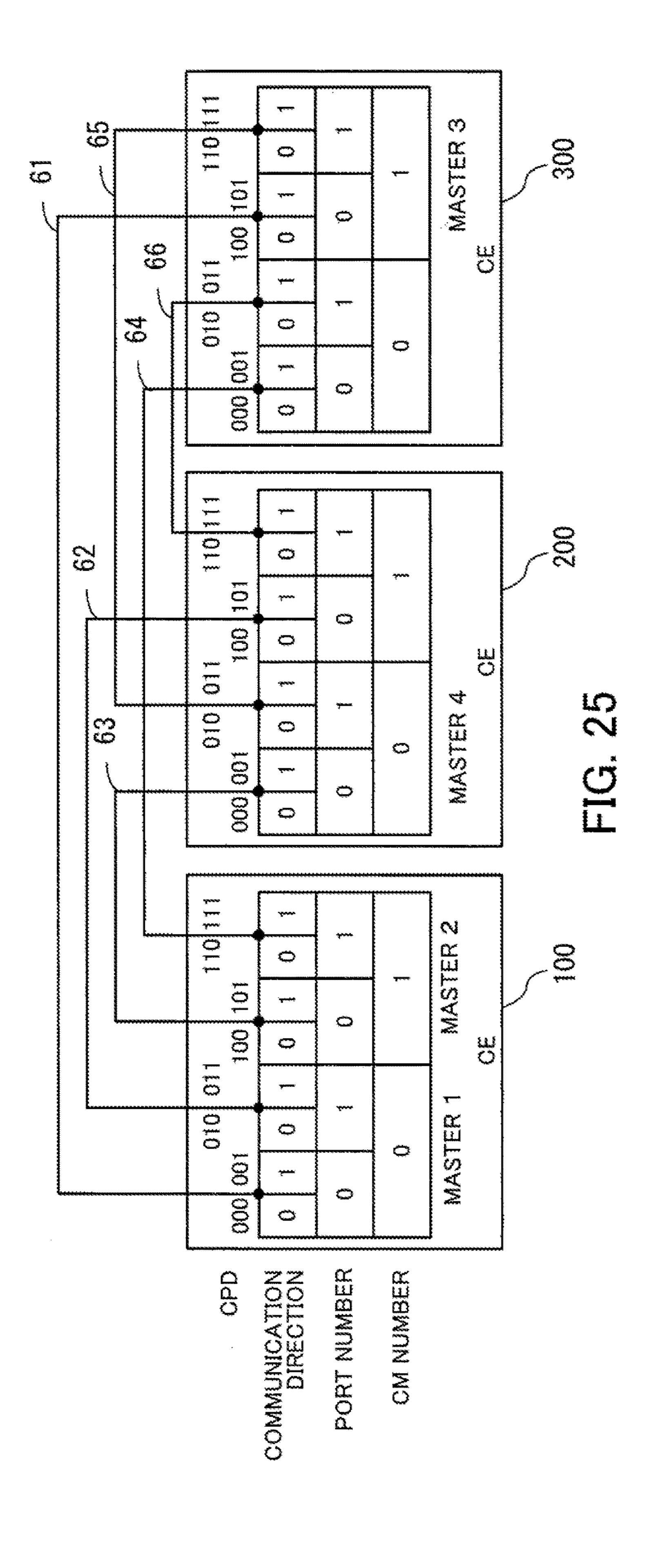

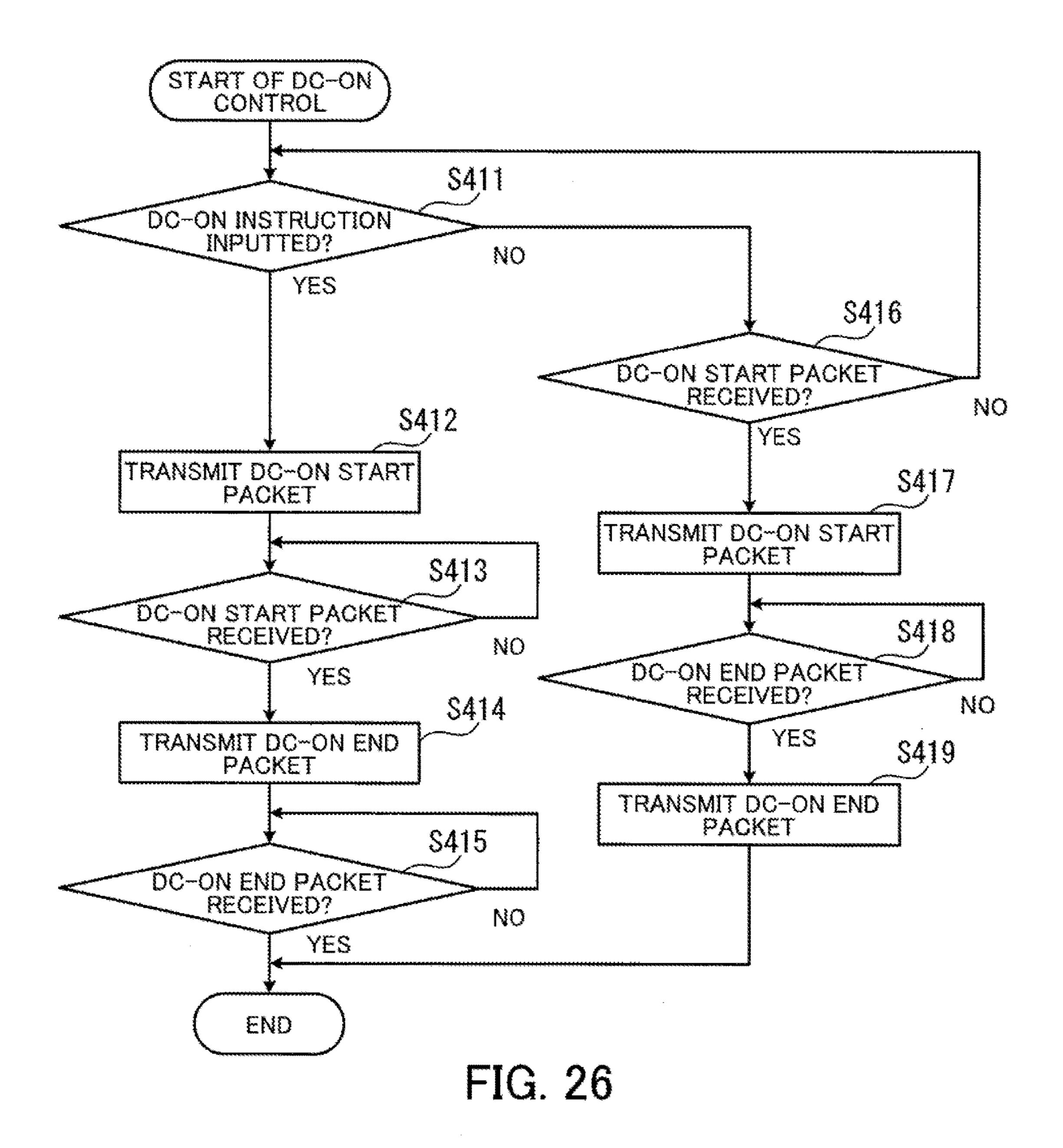

FIG. **25** illustrates another connection mode among CMs; FIG. **26** is a flowchart illustrating an example of a

procedure of DC-ON control processing performed by an FPGA;

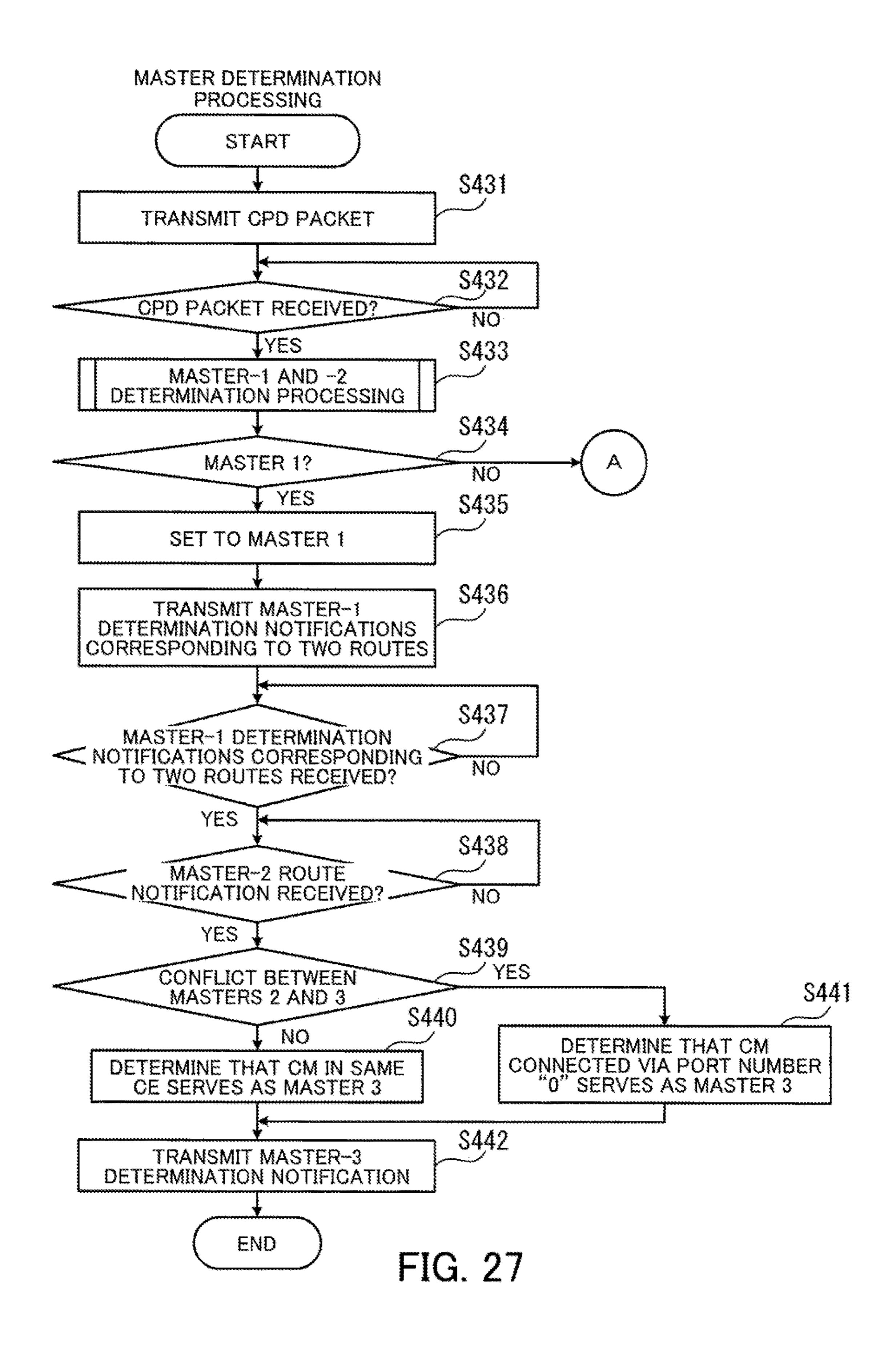

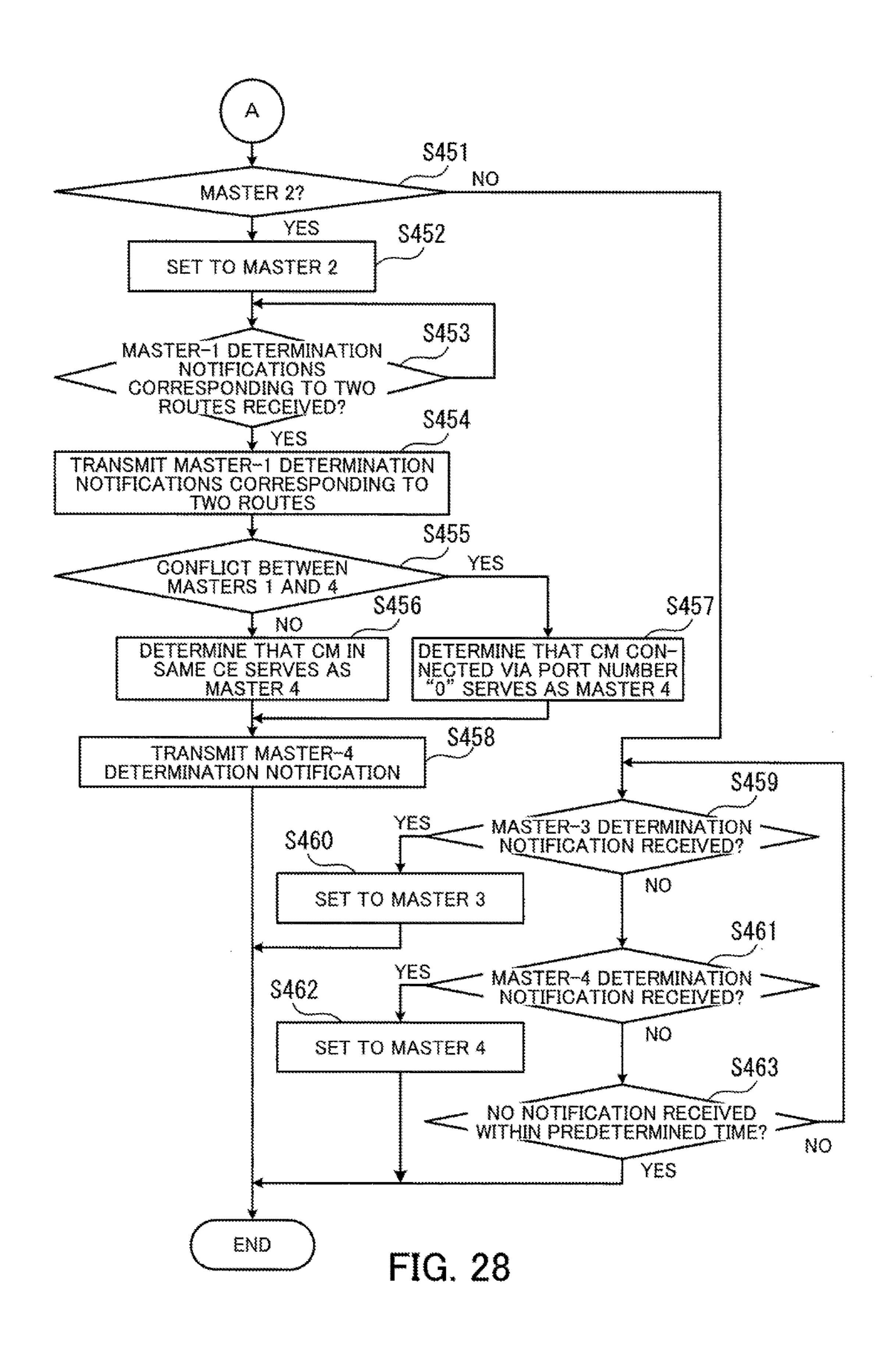

FIG. 27 is a first flowchart illustrating an example of a procedure of master determination processing performed by an FPGA;

FIG. 28 is a second flowchart illustrating the example of the procedure of master determination processing performed by the FPGA;

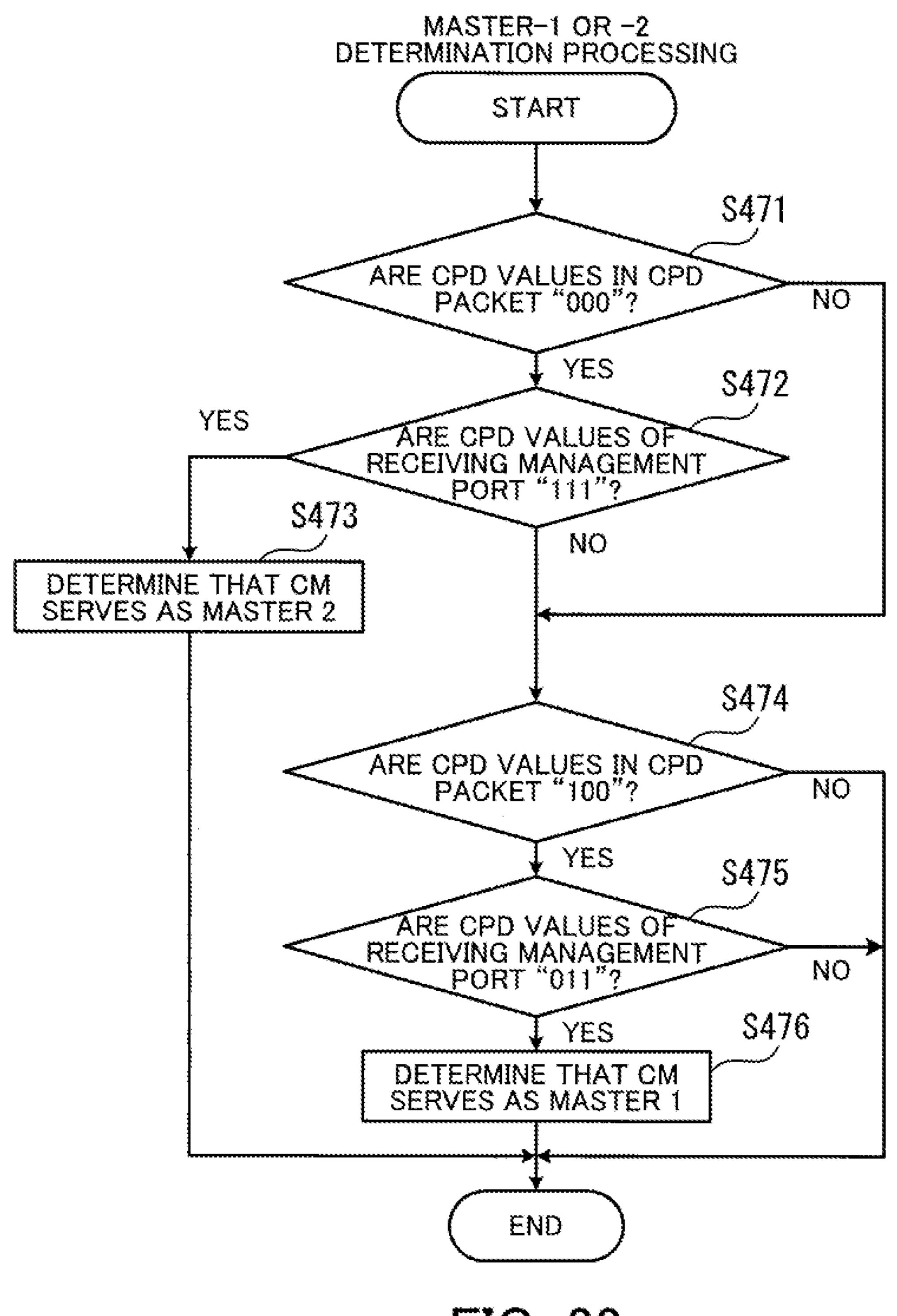

FIG. 29 is a flowchart illustrating an example of a procedure of master-1 and -2 determination processing performed by an FPGA; and

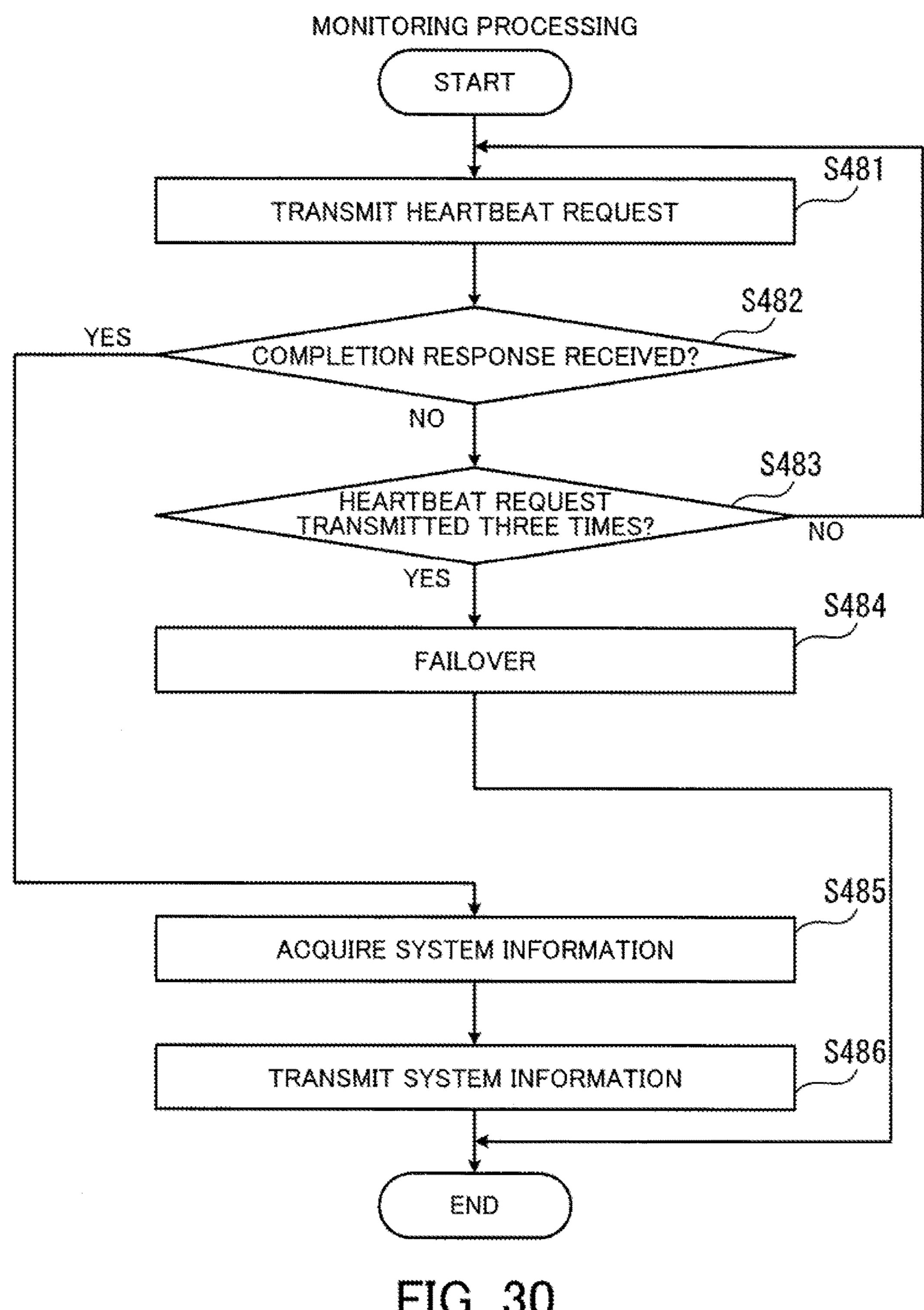

FIG. 30 is a flowchart illustrating an example of a procedure of monitoring processing performed by an FPGA.

#### DESCRIPTION OF EMBODIMENTS

Embodiments will be described below in detail with 45 reference to the accompanying drawings, wherein like reference characters refer to like elements throughout.

#### First Embodiment

First, a first embodiment will be described.

FIG. 1 illustrates an example of a configuration of a storage system according to a first embodiment. The storage system includes a plurality of storage devices 1 to 3 and enclosures 10a to 10c connected to the storage devices 1 to 55 3, respectively.

The enclosure 10a includes a control device 11 whose device number is "0" and a control device 12 whose device number is "1." The control device 11 includes a management circuit 11c including a communication port 11a whose port number is "0" and a communication port 11b whose port number is "1." The control device 12 includes a management circuit 12c including a communication port 12a whose port number is "0" and a communication port 12b whose port number is "1." The management circuit 11c and the 65 management circuit 12c are connected to each other via a signal line in the enclosure 10a.

4

The enclosure 10b includes a control device 13 whose device number is "0" and a control device 14 whose device number is "1." The control device 13 includes a management circuit 13c including a communication port 13a whose port number is "0" and a communication port 13b whose port number is "1." The control device 14 includes a management circuit 14c including a communication port 14a whose port number is "0" and a communication port 14b whose port number is "1." The management circuit 13c and the management circuit 14c are connected to each other via a signal line in the enclosure 10b.

The enclosure 10c includes a control device 15 whose device number is "0" and a control device 16 whose device number is "1." The control device 15 includes a management circuit 15c including a communication port 15a whose port number is "0" and a communication port 15b whose port number is "1." The control device 16 includes a management circuit 16c including a communication port 16b whose port number is "0" and a communication port 16b whose port number is "1." The management circuit 15c and the management circuit 16c are connected to each other via a signal line in the enclosure 10c.

Each of the control devices 11 to 16 controls access to a corresponding one of the storage devices 1 to 3. The device number of a control device (any one of the control devices 11 to 16) is an identifier used in the corresponding enclosure (the corresponding one of the enclosures 10a to 10c) in which this control device is included.

Each of the communication ports 11a to 16b is a port connected to a corresponding one of communication cables 4a to 4f, each of which is used for communication between control devices in different enclosures. The port number of a communication port (any one of the communication ports 11a to 16b) is an identifier used in the corresponding control device (the corresponding one of the control devices 11 to 16) in which this communication port is included.

The communication cable 4a connects the communication port 11a of the control device 11 and the communication port 16b of the control device 16. The communication cable 4b connects the communication port 11b of the control device 11 and the communication port 16a of the control device 16. The communication cable 4c connects the communication port 12a of the control device 12 and the communication port 13a of the control device 13. The communication cable 4d connects the communication port 12b of the control device 12 and the communication port 13bof the control device 13. The communication cable 4e connects the communication port 14a of the control device 50 **14** and the communication port **15***a* of the control device **15**. The communication cable 4f connects the communication port 14b of the control device 14 and the communication port 15b of the control device 15.

The control devices 11 to 16 include a storage device holding master conditions 5. The master conditions 5 include execution conditions about a device that performs predetermined management processing and monitoring execution conditions about a device that monitors the device that performs the management processing.

For example, the execution conditions include a neighboring port condition, a neighboring device condition, a connection port condition, and an execution device condition. The neighboring port condition is about a communication port connected to the execution device that performs the management processing. The neighboring device condition is about a neighboring device that neighbors the execution device. The connection port condition is about a

communication port connected to the neighboring device. The execution device condition is about the execution device.

For example, the monitoring execution conditions include a monitoring neighboring port condition, a monitoring 5 neighboring device condition, a monitoring connection port condition, and a monitoring device condition. The monitoring neighboring port condition is about a communication port connected to the monitoring device that executes the monitoring processing. The monitoring neighboring device that neighbors the monitoring device. The monitoring connection port condition is about a communication port connected to the monitoring neighboring device. The monitoring device condition is about the monitoring device.

For example, each of the neighboring port condition and the monitoring neighboring port condition is about a port number that identifies a communication port within a device. For example, each of the neighboring device condition and monitoring neighboring device condition is about an identification number that identifies a device within an enclosure. For example, each of the connection port condition and the monitoring connection port condition is about a port number that identifies a communication port within a device. For example, each of the execution device condition and the monitoring device condition is about an identification number that identifies a device within an enclosure.

Hereinafter, the control device that performs the management processing will be referred to as "master 1" and the control device that monitors the management device will be 30 referred to as "master 2." In the example in FIG. 1, the conditions (execution conditions) to serve as the master-1 control device are defined. Namely, the device number of a control device that neighbors the master-1 control device needs to be "1," and the communication port number of a 35 communication port of the neighboring device connected to the master-1 control device needs to be "0." In addition, the device number of the master-1 control device needs to be "0," and the port number of a communication port of the master-1 control device connected to the neighboring control device needs to be "1."

In addition, the conditions (monitoring execution conditions) to serve as the master-2 control device are defined. Namely, the device number of the control device that neighbors the monitoring control device needs to be "0," and 45 the communication port number of the communication port of the neighboring device connected to the monitoring control device needs to be "0." In addition, the device number of the monitoring control device needs to be "1," and the port number of the communication port connected to 50 the neighboring control device needs to be "1."

The communication cables 4a to 4f are connected in such a manner that one of the plurality of control devices 11 to 16 serves as the master-1 control device, and another control device serves as the master-2 control device. In the example 55 in FIG. 1, the control device 11 serves as the master-1 control device, and the control device 16 serves as the master-2 control device.

According to the first embodiment, each of the control devices 11 to 16 is able to determine whether to serve one 60 of the masters by itself. For example, each of the control devices 11 to 16 determines, per communication port, whether a combination of its device number and the port number of a communication port and a combination of the device number of the control device to which the communication port is connected and the port number of the destination communication port satisfy the conditions to

6

serve as the master-1 control device. If a control device determines that the control device has a communication port satisfying the conditions to serve as the master-1 control device, this control device determines to manage all the control devices 11 to 16. This determination of whether to serve as the master-1 control device is made by each of the management circuits 11c to 16c in the control devices 11 to 16, for example.

Likewise, each of the control devices 11 to 16 determines, per communication port, whether a combination of its device number and the port number of a communication port and a combination of the device number of the control device to which the communication port is connected and the port number of the destination communication port satisfy the conditions to serve as the master-2 control device. If a control device determines that the control device has a communication port satisfying the conditions to serve as the master-2 control device, this control device determines to monitor the master-1 control device. If the master-1 control device switches to serve as the master-1 control device and manages all the control devices 11 to 16.

The communication cables 4a to 4f are connected in such a manner that a control device to which an end of only one of the communication cables 4a to 4f is connected satisfies the conditions to serve as the master-1 control device. The other cables are connected so as not to satisfy the conditions to serve as the master-1 control device.

In this way, in the first embodiment, on the basis of the connection state of the communication cables 4a to 4f, a single master-1 control device and a single master-2 control device are determined. In addition, each of the control devices 11 to 16 is able to easily determine whether to serve as the master-1 or master-2 control device by itself, on the basis of the connection state of the communication cables 4a to 4f. As a result, since external management devices such as SVCs are not needed, downsizing of the entire system is achieved.

In addition, if the master-1 control device malfunctions, since the master-2 control device promptly switches to serve as the master-1 control device and starts managing the control devices 11 to 16, the reliability of the system is maintained at a high level.

#### Second Embodiment

Next, a second embodiment will be described. In a scale-out-type storage system according to a second embodiment, a management FPGA is arranged in an individual CM, and an individual management FPGA manages its corresponding CM without involving an SVC or a processor in the CM. Since SVCs are not needed, downsizing of the storage system is achieved.

FIG. 2 illustrates an example of a configuration of a storage system according to the second embodiment. The storage system illustrated in FIG. 2 includes CEs 100, 200, 300, and 400, DEs 500, 600, 700, and 800, and a host device 900. The host device 900 performs data input and output operations on hard disk drives (HDDs) in the DEs 500, 600, 700, and 800 via the CEs 100,200, 300, and 400.

The CE 100 includes CMs 110 and 120. The CE 200 includes CMs 210 and 220. The CE 300 includes CMs 310 and 320. The CE 400 includes CMs 410 and 420. Each of the CMs 110, 120, 210, 220, 310, 320, 410, and 420 is provided with an identification number (CM number) used in the corresponding one of the CEs 100, 200, 300, and 400. The

CM number of the CMs 110, 210, 310, and 410 is "0," and the CM number of the CMs 120, 220, 320, and 420 is "1."

The CM 110 and the CM 420 are connected to each other.

The CM 120 and the CM 210 are connected to each other.

The CM 220 and the CM 310 are connected to each other.

The CM 320 and the CM 410 are connected to each other.

For example, two CMs are connected to each other via serial cables.

In addition, the CMs 110, 120, 210, 220, 310, 320, 410, and 420 are connected to the host device 900. For example, the CM 110, 120, 210, 220, 310, 320, 410, and 420 are connected to the host device 900 via a storage area network (SAN) using Fibre Channel (FC) or Internet Small Computer System Interface (iSCSI). In FIG. 2, as an example, the single host device 900 is connected to the CMs 110, 120, 210, 220, 310, 320, 410, and 420. However, for example, each of a plurality of host devices may be connected to one or more CMs.

Each of the DEs **500**, **600**, **700**, and **800** is a disk array device including a plurality of storage devices. For example, the DE **500** includes HDDs **511** to **51***n*. The DE **600** includes HDDs **611** to **61***n*. The DE **700** includes HDDs **711** to **71***n*. The DE **800** includes HDDs **811** to **81***n*. In the example in FIG. **2**, the DEs **500**, **600**, **700**, and **800** include HDDs as the 25 storage devices. However, the DEs **500**, **600**, **700**, and **800** may include a different kind of storage devices such as solid state drives (SSDs).

The CMs 110 and 120 are connected to the DE 500. The CMs 110 and 120 control access to the HDDs 511 to 51n 30 included in the DE 500, in response to a request from the host device 900 or another CM. The CMs 210 and 220 are connected to the DE 600. The CMs 210 and 220 control access to the HDDs 611 to 61n included in the DE 600, in response to a request from the host device 900 or another 35 CM. The CMs 310 and 320 are connected to the DE 700. The CMs 310 and 320 control access to the HDDs 711 to 71n included in the DE 700, in response to a request from the host device 900 or another CM. The CMs 410 and 420 control access to the HDDs 811 to 81n included in the DE 40 800, in response to a request from the host device 900 or another CM.

For example, the CE 100 and the DE 500 are realized as a storage apparatus included in a single enclosure. The same applies to the CE 200 and the DE 600, the CE 300 and the 45 DE 700, and the CE 400 and the DE 800. The storage system in FIG. 2 can be expanded by adding a storage apparatus as a unit.

In addition, the number of CEs included in the storage system is not limited to 4. The number of CMs included in 50 an individual CE is not limited to 2, either. For example, the storage system may include more than four CEs each including more than two CMs.

FIG. 3 illustrates an example of a hardware configuration of the CM 110. The CM 110 includes a processor 111, a 55 random access memory (RAM) 112, an SSD 113, a channel adapter (CA) 114, an FPGA 115, a device interface (DI) 116, and a reading device 117.

The processor 111 controls information processing of the CM 110. Examples of the processor 111 include a central 60 processing unit (CPU), a digital signal processor (DSP), and an application specific integrated circuit (ASIC). The processor 111 may be a multiprocessor that includes a plurality of processing elements.

The RAM 112 is a main storage device of the CM 110. 65 The RAM 112 temporarily holds at least a part of a program of an operating system (OS) or an application program

8

executed by the processor 111. In addition, the RAM 112 holds various types of data used in processing performed by the processor 111.

The SSD 113 is an auxiliary storage device of the CM 110. The SSD 113 is a non-volatile semiconductor memory. The SSD 113 holds an OS program, a firmware program, an application program, and various types of data. The CM 110 may include an HDD in place of the SSD 113 as the auxiliary storage device.

The CA 114 is an interface for communicating with the host device 900. When the host device 900 transmits an access request, the CA 114 receives and transfers the access request to the processor 111.