#### US010199484B2

## (12) United States Patent

#### Nagata

### (10) Patent No.: US 10,199,484 B2

#### (45) **Date of Patent:** \*Feb. 5, 2019

## (54) SEMICONDUCTOR DEVICE AND MANUFACTURING METHOD THEREOF

(71) Applicant: Renesas Electronics Corporation,

Koutou-ku, Tokyo (JP)

(72) Inventor: Nao Nagata, Tokyo (JP)

(73) Assignee: RENESAS ELECTRONICS

CORPORATION, Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 15/411,268

(22) Filed: **Jan. 20, 2017**

(65) Prior Publication Data

US 2017/0133483 A1 May 11, 2017

#### Related U.S. Application Data

(62) Division of application No. 15/005,195, filed on Jan. 25, 2016, now Pat. No. 9,818,851.

#### (30) Foreign Application Priority Data

(51) Int. Cl.

H01L 29/06 (2006.01)

H01L 21/768 (2006.01)

(Continued)

(52) U.S. Cl.

CPC .... *H01L 29/7397* (2013.01); *H01L 21/76895* (2013.01); *H01L 23/535* (2013.01); (Continued)

#### (58) Field of Classification Search

None

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

7,633,122 B2 12/2009 Otsuki 8,633,510 B2 1/2014 Matsuura et al.

(Continued)

#### FOREIGN PATENT DOCUMENTS

EP 2613356 A2 7/2013 JP 2003-142689 A 5/2003 (Continued)

#### OTHER PUBLICATIONS

Extended European search report for European Patent Application No. 16150746.2, dated Jul. 7, 2016.

(Continued)

Primary Examiner — Shaun M Campbell (74) Attorney, Agent, or Firm — Shapiro, Gabor and Rosenberger, PLLC

#### (57) ABSTRACT

An improvement is achieved in the performance of a semiconductor device. The semiconductor device includes a first trench gate electrode and second and third trench gate electrodes located on both sides of the first trench gate electrode interposed therebetween. In each of a semiconductor layer located between the first and second trench gate electrodes and the semiconductor layer located between the first and third trench gate electrodes, a plurality of p<sup>+</sup>-type semiconductor regions are formed. The p<sup>+</sup>-type semiconductor regions are arranged along the extending direction of the first trench gate electrode in plan view to be spaced apart from each other.

#### 11 Claims, 57 Drawing Sheets

# US 10,199,484 B2 Page 2

| (51) | Int. Cl.                                               |                                             | 2010/0                                                                              | 193836 A1           | 8/2010 | Okuno et al.           |  |

|------|--------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------|---------------------|--------|------------------------|--|

| . ,  | H01L 23/535                                            | (2006.01)                                   | 2011/0                                                                              | 018029 A1           | 1/2011 | Pfirsch et al.         |  |

|      | H01L 27/082                                            | (2006.01)                                   | 2011/0                                                                              | 233684 A1           | 9/2011 | Matsushita             |  |

|      | H01L 29/739                                            | (2006.01)                                   | 2013/0                                                                              | 001638 A1           | 1/2013 | Yoshikawa              |  |

|      | H01L 29/40                                             | (2006.01)                                   | 2013/0                                                                              | 175574 A1*          | 7/2013 | Matsuura H01L 29/66348 |  |

|      |                                                        |                                             |                                                                                     |                     |        | 257/139                |  |

|      | H01L 29/66                                             | (2006.01)                                   | 2017/0                                                                              | 012551 A1*          | 1/2017 | Kondo H02M 5/458       |  |

|      | H01L 29/10                                             | (2006.01)                                   | 2017/0                                                                              | 054010 A1*          | 2/2017 | Matsuura H01L 29/7397  |  |

|      | H01L 29/08                                             | (2006.01)                                   | 2017/0                                                                              | 092750 A1*          | 3/2017 | Nagata H01L 21/761     |  |

|      | H01L 29/36                                             | (2006.01)                                   | 2018/0                                                                              | 053838 A1*          | 2/2018 | Matsuura H01L 29/0696  |  |

|      | H01L 29/423                                            | (2006.01)                                   | 2018/0                                                                              | 069109 A1*          | 3/2018 | Nagata H02M 7/537      |  |

| (52) | U.S. Cl.                                               |                                             | 2018/0                                                                              | 0083130 A1*         | 3/2018 | Matsuura H01L 29/0696  |  |

|      | CPC <i>H01L 27/0823</i> (2013.01); <i>H01L 29/0619</i> |                                             |                                                                                     |                     |        |                        |  |

|      | (2013.01); <b>H01L 29/0696</b> (2013.01); <b>H01L</b>  |                                             | FOREIGN PATENT DOCUMENTS                                                            |                     |        |                        |  |

|      | 29/0804                                                | # (2013.01); <b>H01L 29/0821</b> (2013.01); | ***                                                                                 | 2006 240            |        | 0/000                  |  |

|      | H01L 29/1095 (2013.01); H01L 29/36                     |                                             | JP<br>JP                                                                            | 2006-210            |        | 8/2006                 |  |

|      | (2013.01); <i>H01L 29/407</i> (2013.01); <i>H01L</i>   |                                             |                                                                                     | 2012-256            |        | 12/2012                |  |

|      | `                                                      | (2013.01); H01L 29/46/348 (2013.01)         | JP                                                                                  | 2013-140            | 1885 A | 7/2013                 |  |

|      | 27/4230                                                | (2015.01), <b>HOIL</b> 27/00540 (2015.01)   |                                                                                     |                     |        |                        |  |

| (56) | 756) References Cited                                  |                                             | OTHER PUBLICATIONS                                                                  |                     |        |                        |  |

| (50) |                                                        |                                             |                                                                                     |                     |        |                        |  |

|      | U.S. PATENT DOCUMENTS                                  |                                             | Office Action, dated Sep. 11, 2018, in Japanese Patent Application No. 2015-063339. |                     |        |                        |  |

|      | 9,041,050 B2 5/2015 Matsuura                           |                                             |                                                                                     |                     |        |                        |  |

|      | 9,818,851 B2 * 11/2017 Nagata                          |                                             |                                                                                     | * cited by examiner |        |                        |  |

FIG. 3

F/G. 4

F/G. 5

F/G. 6

FIG. 7

FIG. 8

F/G. 9

F/G. 10

F/G. 17

F/G. 18

F/G. 19

F/G. 20

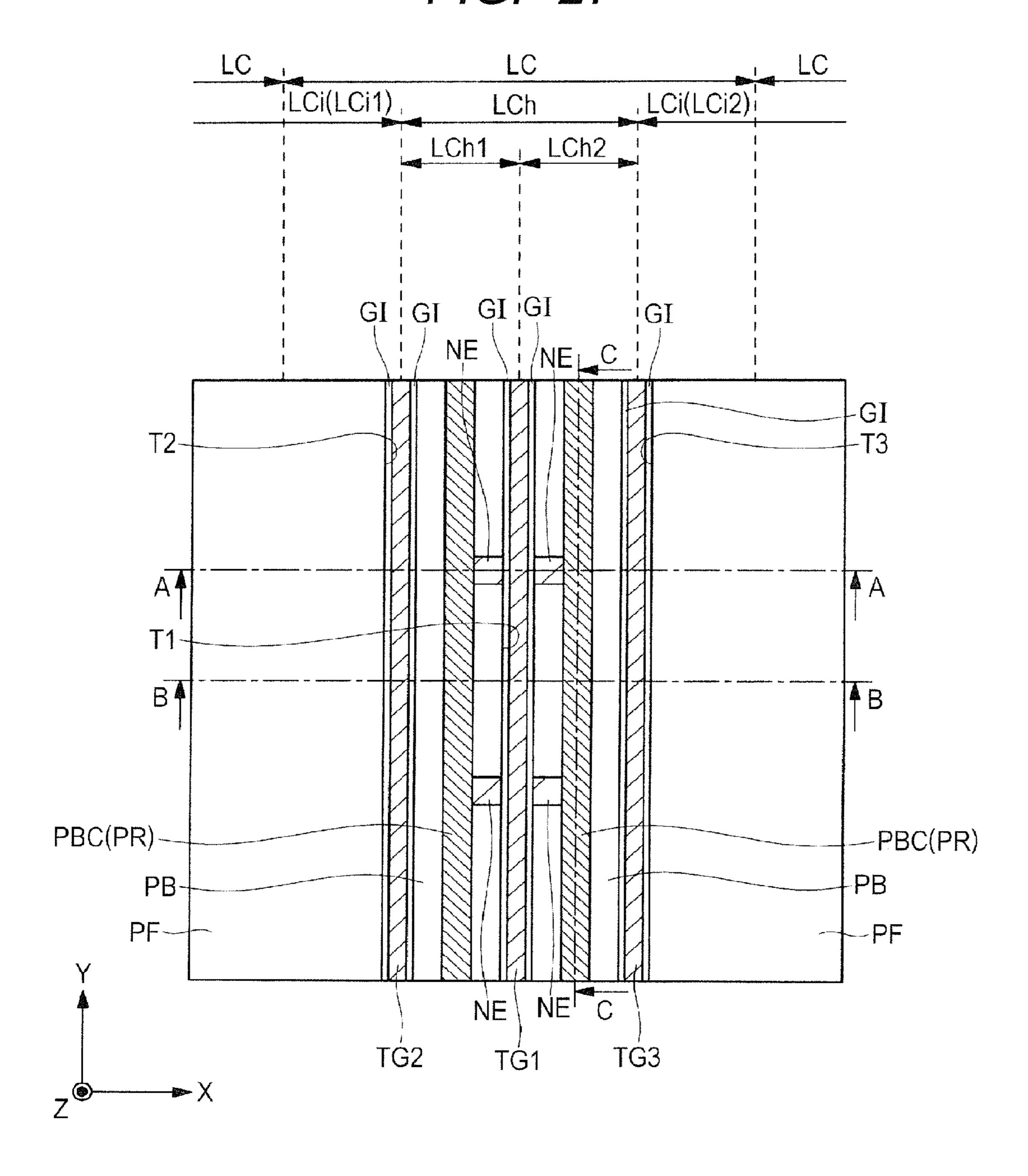

F/G. 21

F/G. 22

F/G. 23

FIG. 24

F/G. 25

F/G. 27

F/G. 28

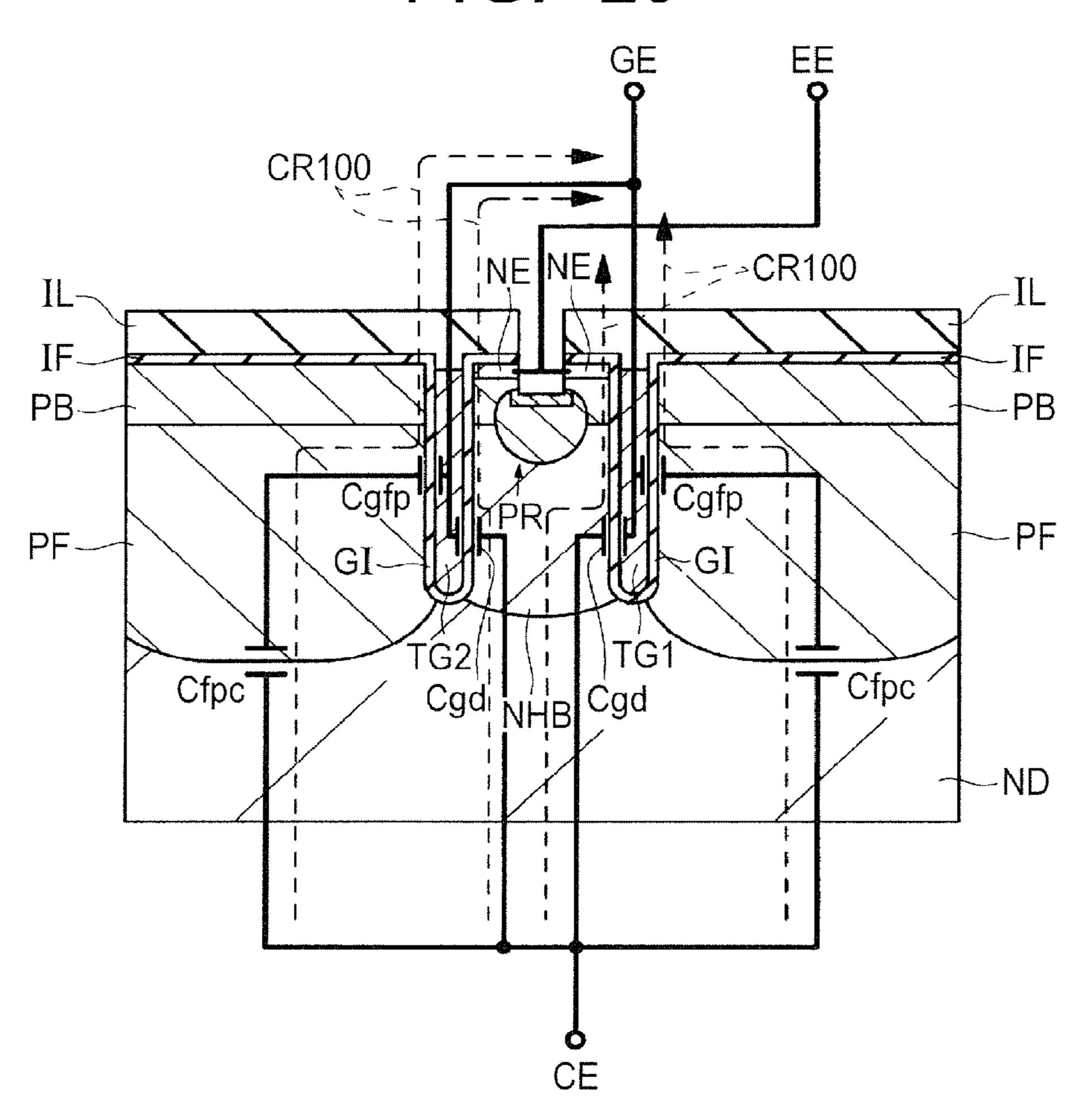

F/G. 29

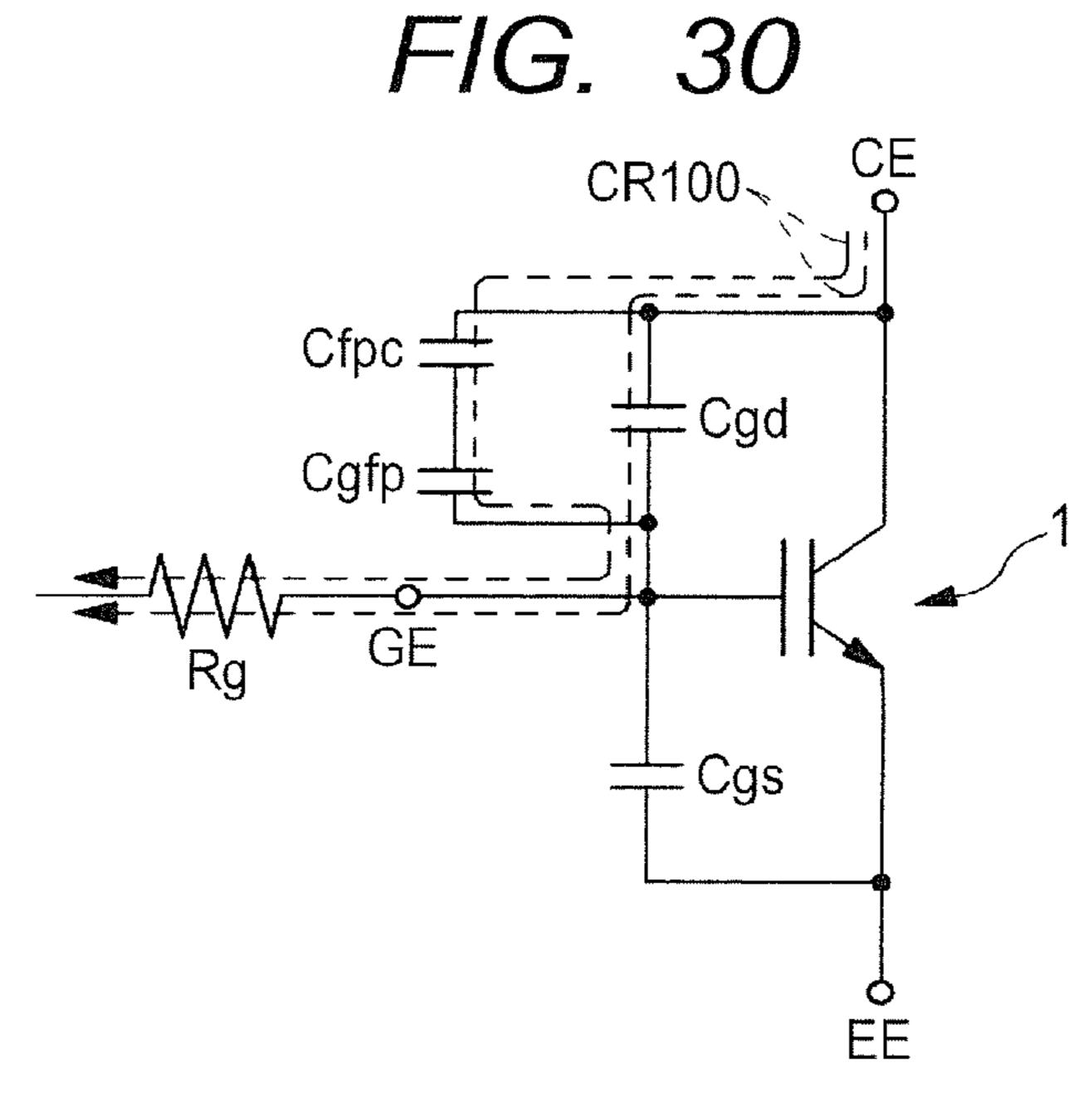

F/G. 33

F/G. 34

F/G. 35

F/G. 36

F/G. 37

TIME (a.u.)

F/G. 38

FIG. 39

--- COMPARATIVE EXAMPLE 1

— COMPARATIVE EXAMPLE 2

VOLTAGE VCE (a.u.)

F/G. 41

FIG. 42

F/G. 43

F/G. 44

F/G. 45

F/G. 46

F/G 47

FIG. 48

F/G. 49

F/G. 50

F/G. 51

F/G. 52

F/G. 53

FIG. 57

NOLLAGE (a.u.)

F/G. 58

F/G. 59

F/G. 60

F/G. 61

F/G. 63

FIG. 64

F/G. 65

F/G. 66

F/G. 67

F/G. 68

# SEMICONDUCTOR DEVICE AND MANUFACTURING METHOD THEREOF

## CROSS-REFERENCE TO RELATED APPLICATIONS

The disclosure of Japanese Patent Application No. 2015-063339 filed on Mar. 25, 2015 including the specification, drawings and abstract is incorporated herein by reference in its entirety.

#### **BACKGROUND**

The present invention relates to a semiconductor device, which can be used appropriately as, e.g., a semiconductor device including an insulated gate bipolar transistor (IGBT). <sup>15</sup>

As an IGBT having a low ON resistance, a trench-gate-type IGBT has been used widely. There has been developed an IE-type IGBT in which, in a cell formation region, active cell regions each coupled to an emitter electrode and inactive cell regions each including a floating region are alternately arranged to allow an IE (Injection Enhancement) effect to be used. The IE effect reduces the likelihood of discharging of holes from the emitter electrode when the IGBT is in an ON state and thus increases the density of the charges stored in a drift region.

Japanese Unexamined Patent Publication No. 2012-256839 (Patent Document 1) discloses a technique in which, in an IE-type trench-gate IGBT, each of linear unit cell regions provided in a cell formation region includes a linear active cell region and linear inactive cell regions provided on both sides of the linear active cell region such that the linear active cell region is interposed therebetween.

Japanese Unexamined Patent Publication No. 2013-140885 (Patent Document 2) discloses a technique in which, in an IE-type trench-gate IGBT, each of linear unit cell regions provided in a cell formation region includes a linear hybrid cell region and, in the linear hybrid cell region, a first linear hybrid sub-cell region and a second linear hybrid sub-cell region are provided.

Japanese Unexamined Patent Publication No. 2006-210547 (Patent Document 3) discloses a technique in which, in an insulated-gate-type semiconductor device, a second semiconductor layer having a second conductivity type and provided over a first semiconductor layer having a first conductivity type, a plurality of striped trenches formed in a top surface of the second semiconductor layer, and a 45 plurality of third semiconductor regions each having the first conductivity type and formed selectively in a longitudinal direction between the trenches are provided.

## RELATED ART DOCUMENTS

### Patent Documents

[Patent Document 1]

Japanese Unexamined Patent Publication No. 2012- 55 256839

[Patent Document 2]

Japanese Unexamined Patent Publication No. 2013-140885

[Patent Document 3]

Japanese Unexamined Patent Publication No. 2006-210547

## **SUMMARY**

There has been known a semiconductor device including an IGBT having a GG-type (gate-gate-type) active cell 2

region as an IE-type trench-gate IGBT, such as, e.g., the IE-type trench-gate IGBT disclosed in Patent Document 1 mentioned above. There has also been known a semiconductor device including an IGBT having an EGE-type (emitter-gate-emitter-type) active cell region as an IE-type trench gate IGBT, such as, e.g., the IE-type trench-gate IGBT disclosed in Patent Document 2 mentioned above.

In the semiconductor device including the IGBT having the EGE-type active region, in a switching operation when an inductance is coupled as a load, a gate potential is less affected by a displacement current generated in the active cell region than in the semiconductor device including the IGBT having the GG-type active cell region.

However, in the semiconductor device including the IGBT having the EGE-type active cell region, it is desirable to further improve the performance of the semiconductor device such as, e.g., the IE effect.

Other problems and novel features of the present invention will become apparent from a statement in the present specification and the accompanying drawings.

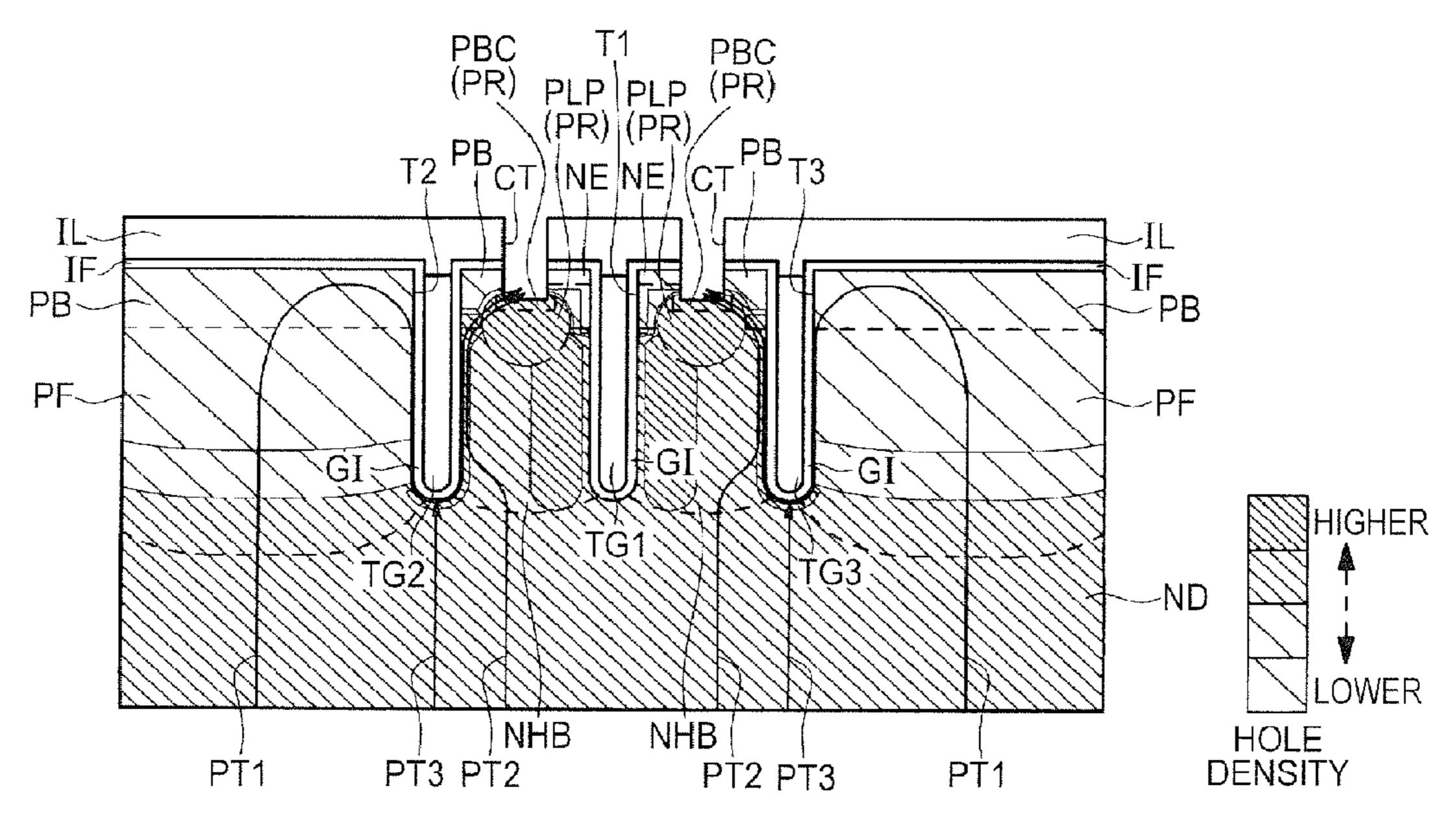

According to an embodiment, a semiconductor device includes a first trench gate electrode and second and third trench gate electrodes located on both sides of the first trench gate electrode interposed therebetween. The first trench gate electrode is coupled to a gate electrode. The second and third trench gate electrodes are coupled to an emitter electrode. In a semiconductor layer between the first and second trench gate electrodes, a plurality of p<sup>+</sup>-type semiconductor regions are formed. In a semiconductor layer between the first and third trench gate electrodes, a plurality of p<sup>+</sup>-type semiconductor regions are formed. Either between the first and second trench gate electrodes or between the first and third trench gate electrodes, the plurality of p<sup>+</sup>-type semiconductor regions are arranged along an extending direction of the first trench gate electrode in plan view to be spaced apart from each other.

According to another embodiment, in a method of manufacturing a semiconductor device, a first trench gate electrode and second and third trench gate electrodes located on both sides of the first trench gate electrode interposed therebetween are formed. The first trench gate electrode is coupled to a gate electrode. The second and third trench gate electrodes are coupled to an emitter electrode. Next, in a semiconductor layer between the first and second trench gate electrodes, a plurality of p<sup>+</sup>-type semiconductor regions are formed and, in a semiconductor layer between the first and third trench gate electrodes, a plurality of p<sup>+</sup>-type semiconductor regions are formed. Either between the first and second trench gate electrodes or between the first and third trench gate electrodes, the plurality of p<sup>+</sup>-type semiconductor regions are arranged along an extending direction of the first trench gate electrode in plan view to be spaced apart from each other.

According to the embodiment, the performance of the semiconductor device can be improved.

### BRIEF DESCRIPTION OF THE DRAWINGS

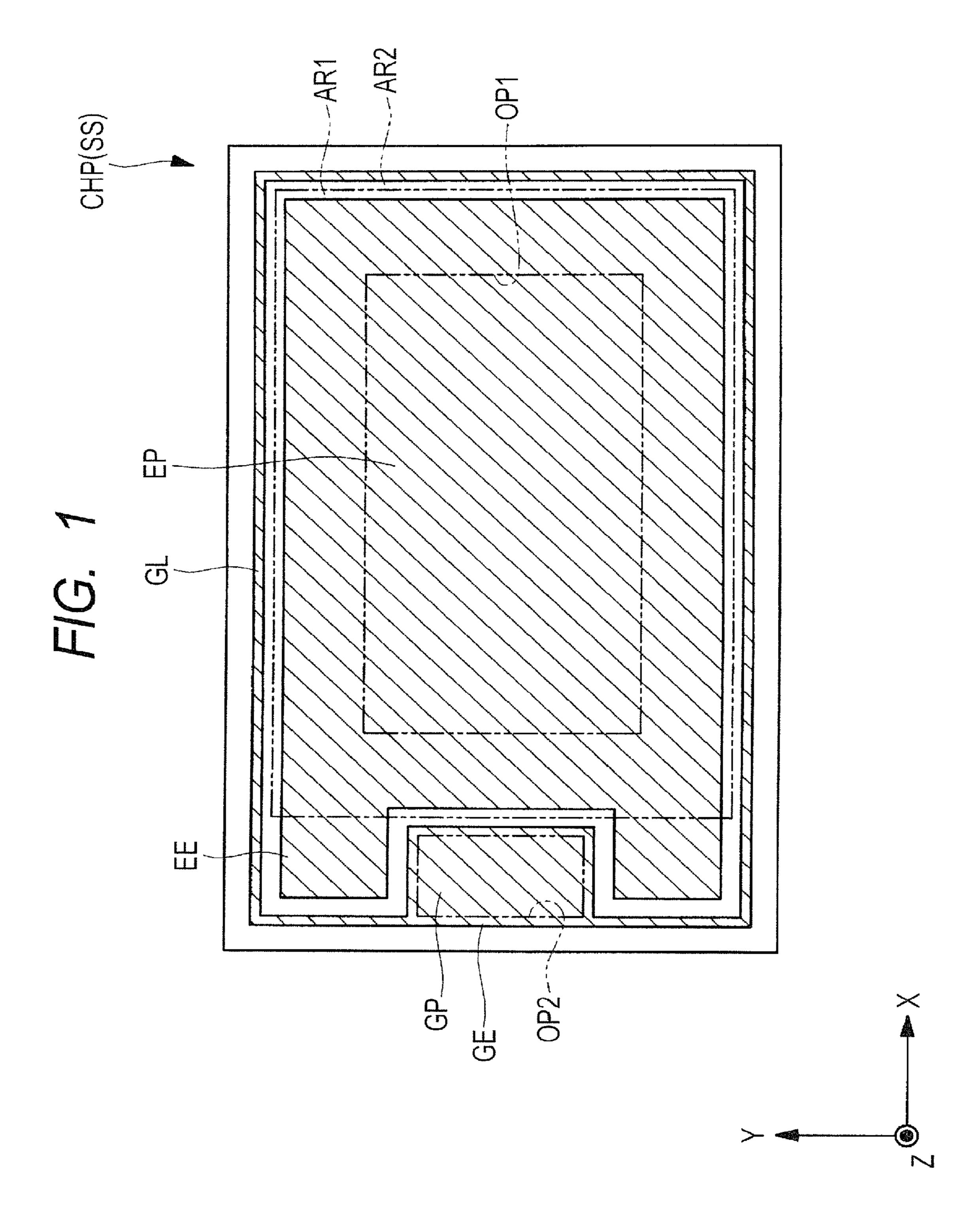

FIG. 1 is a plan view of a semiconductor chip as a semiconductor device in Embodiment 1;

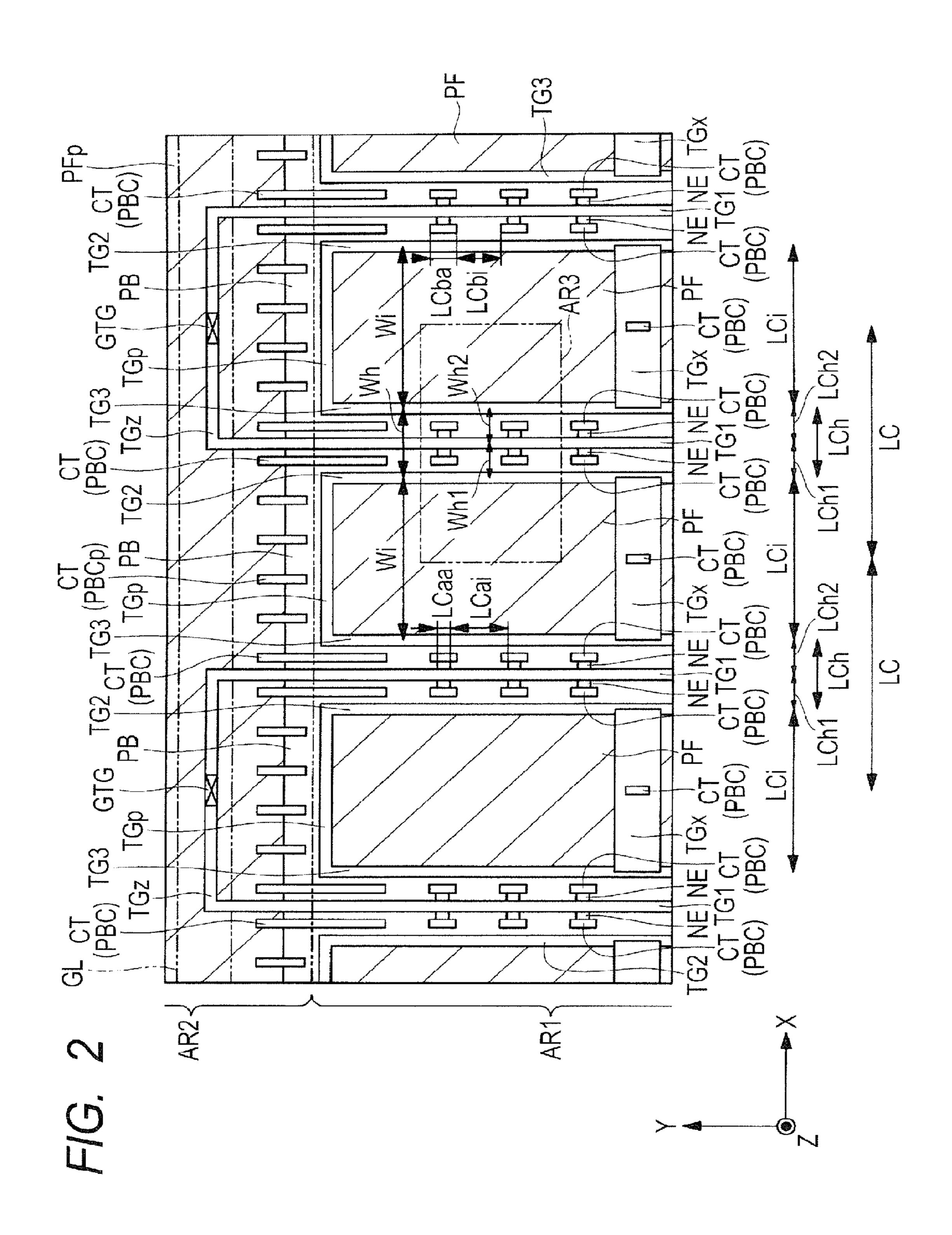

FIG. 2 is a main-portion plan view of the semiconductor device in Embodiment 1;

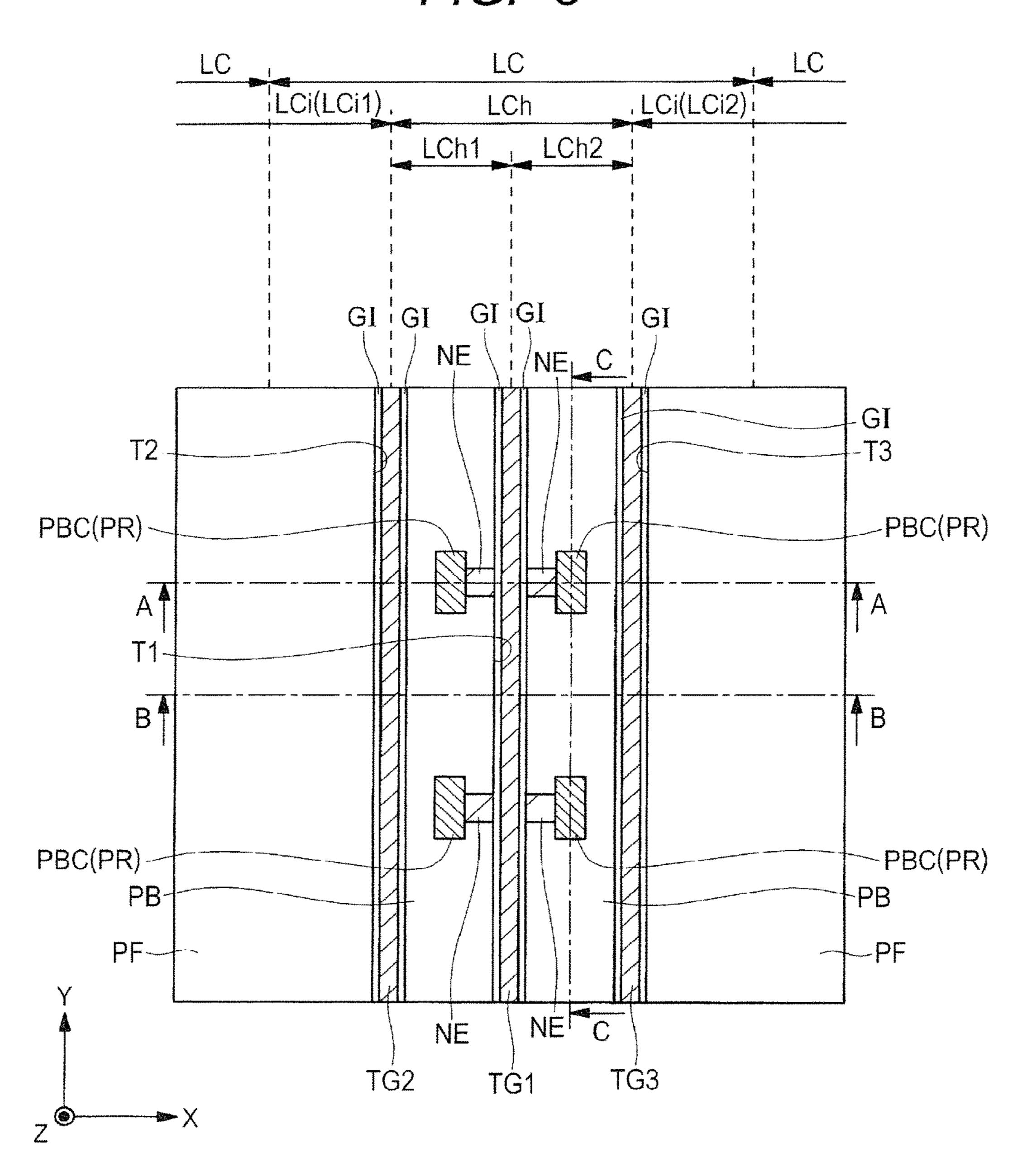

FIG. 3 is a main-portion plan view of the semiconductor device in Embodiment 1;

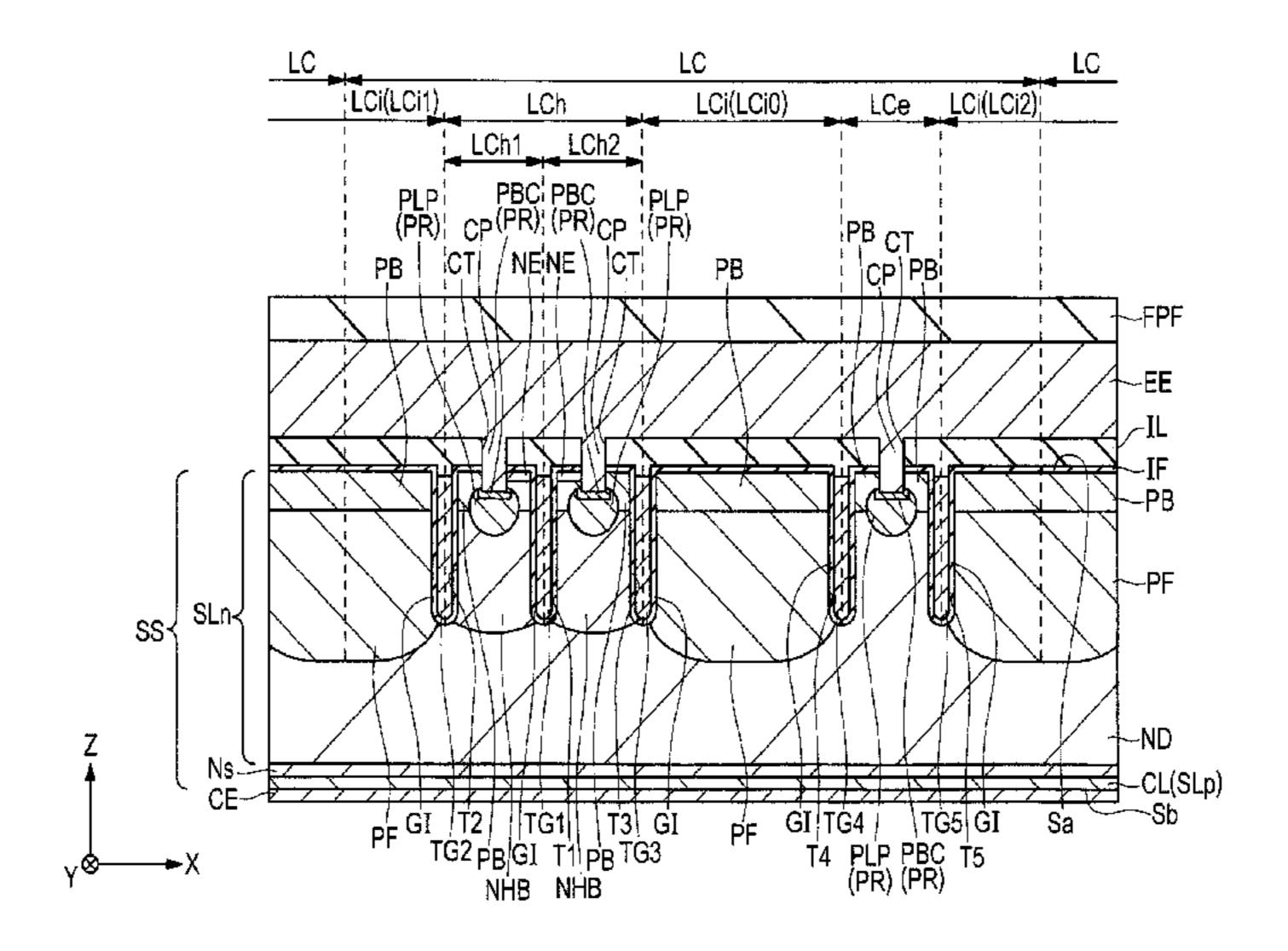

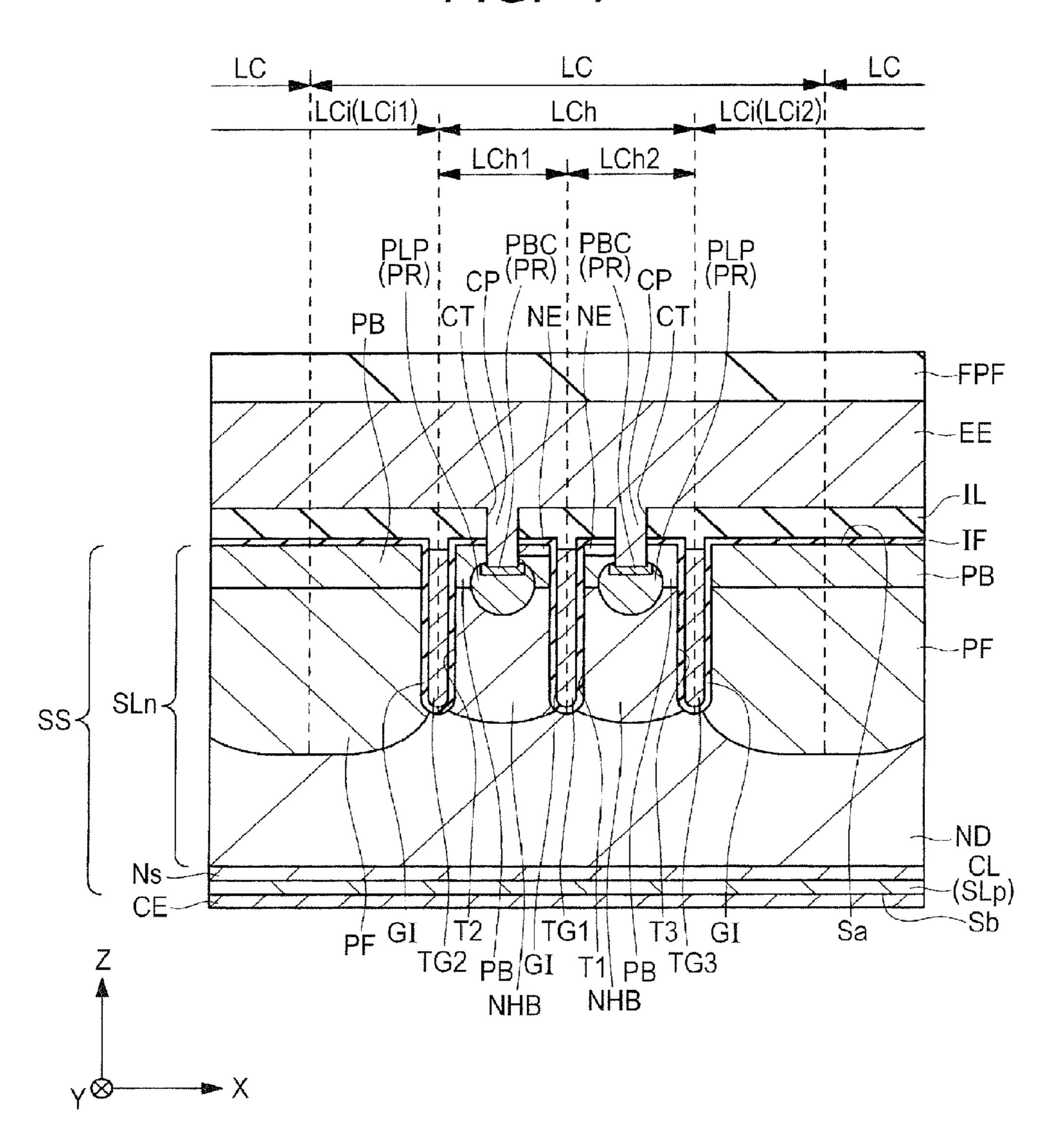

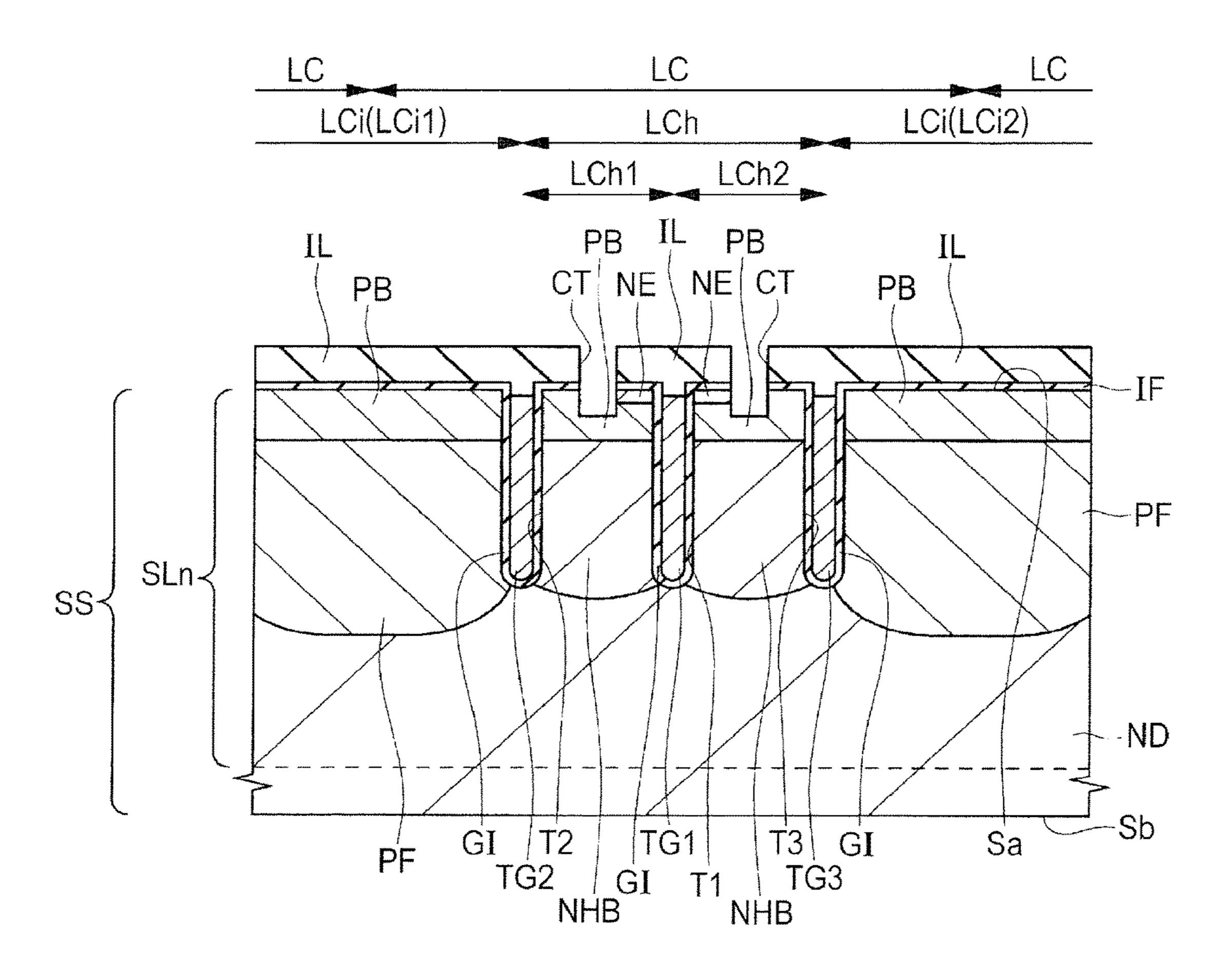

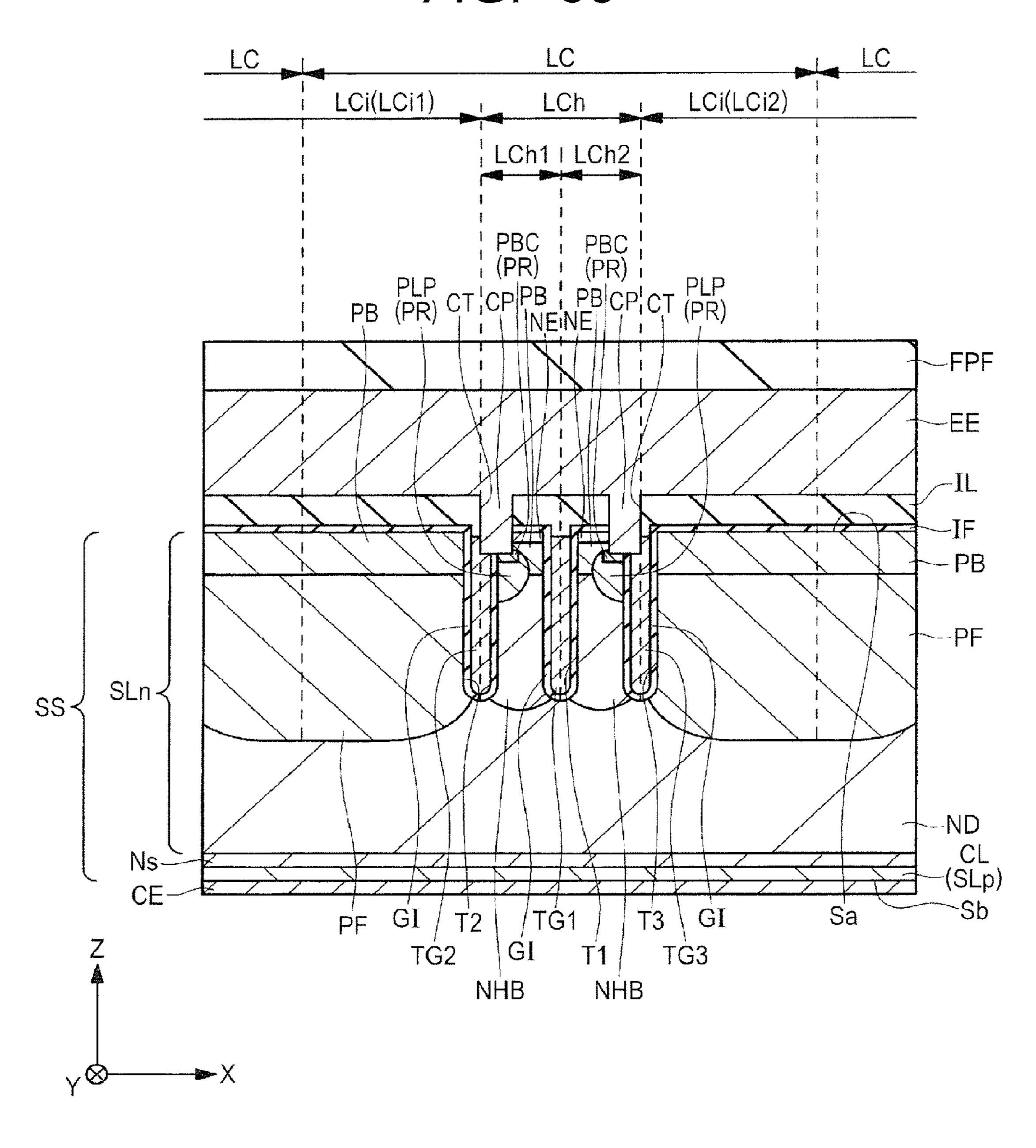

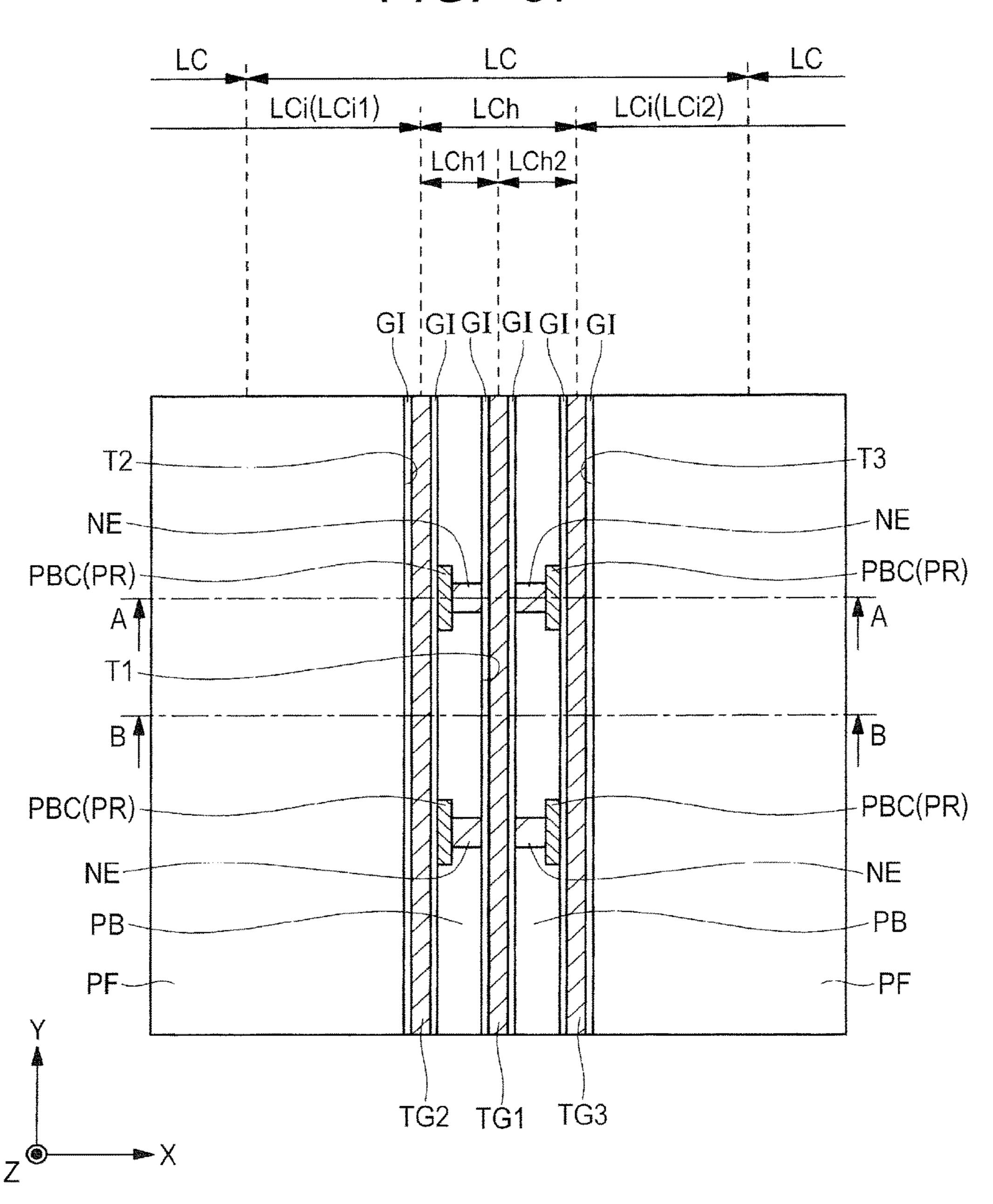

FIG. 4 is a main-portion cross-sectional view of the semiconductor device in Embodiment 1;

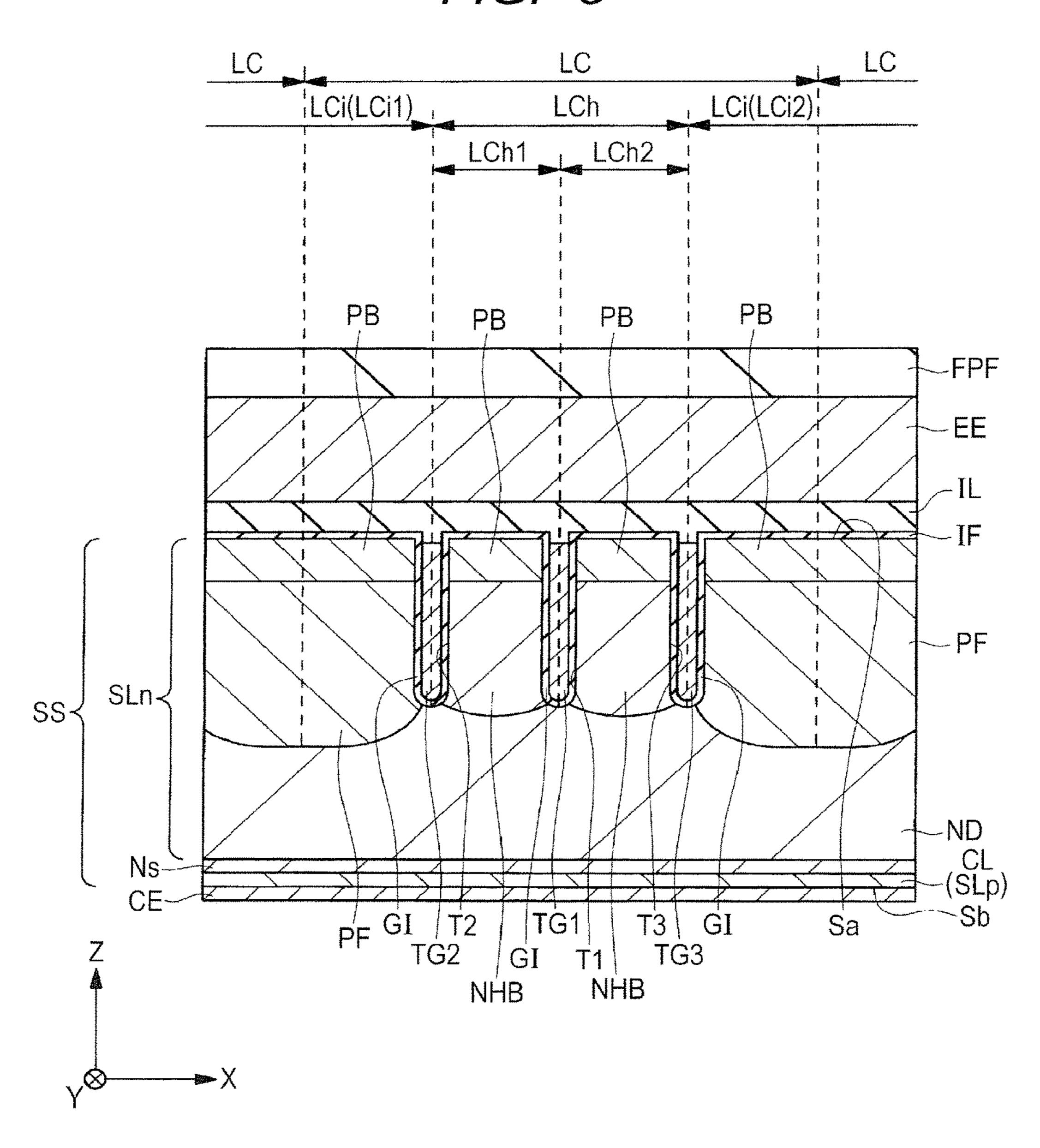

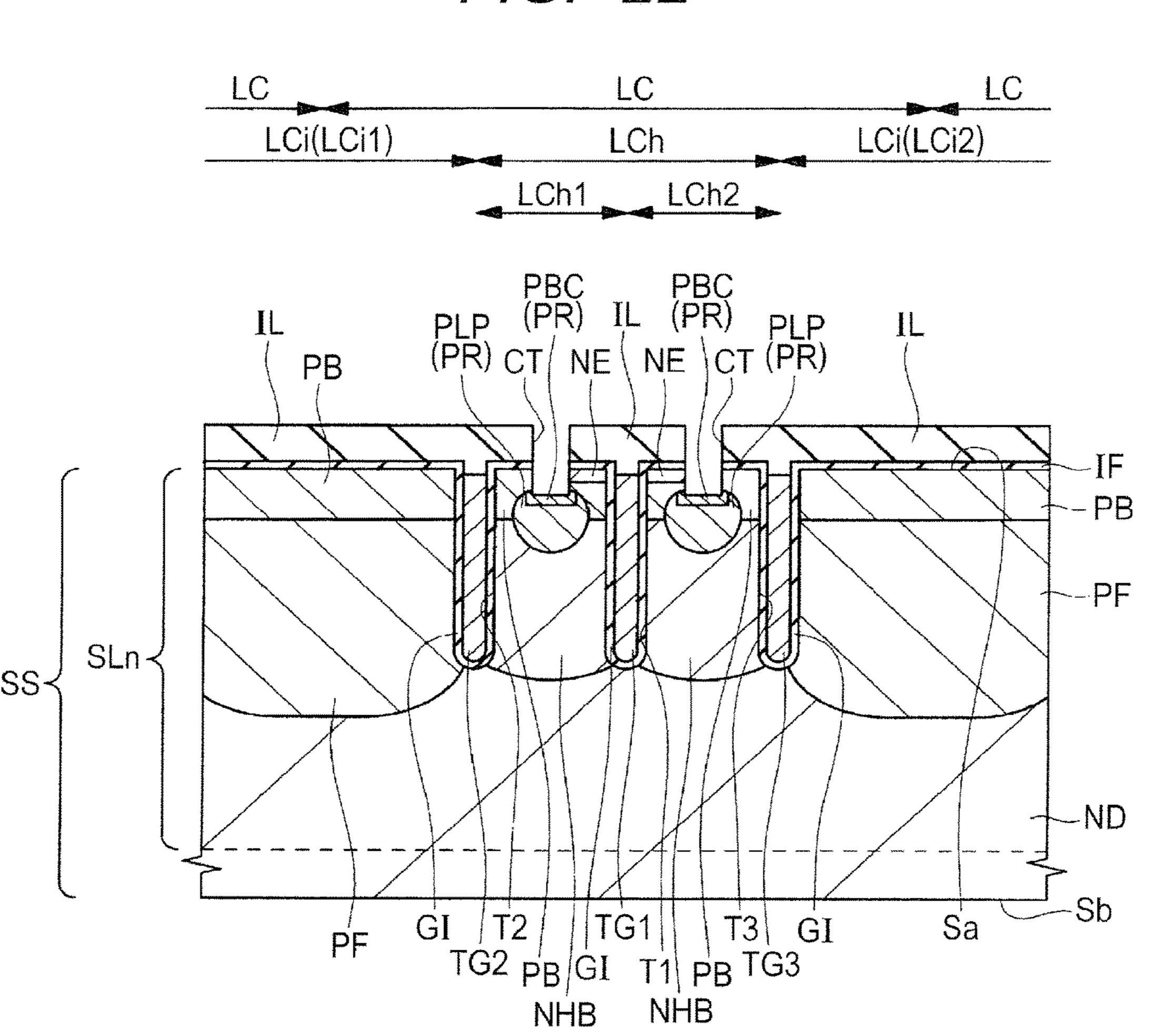

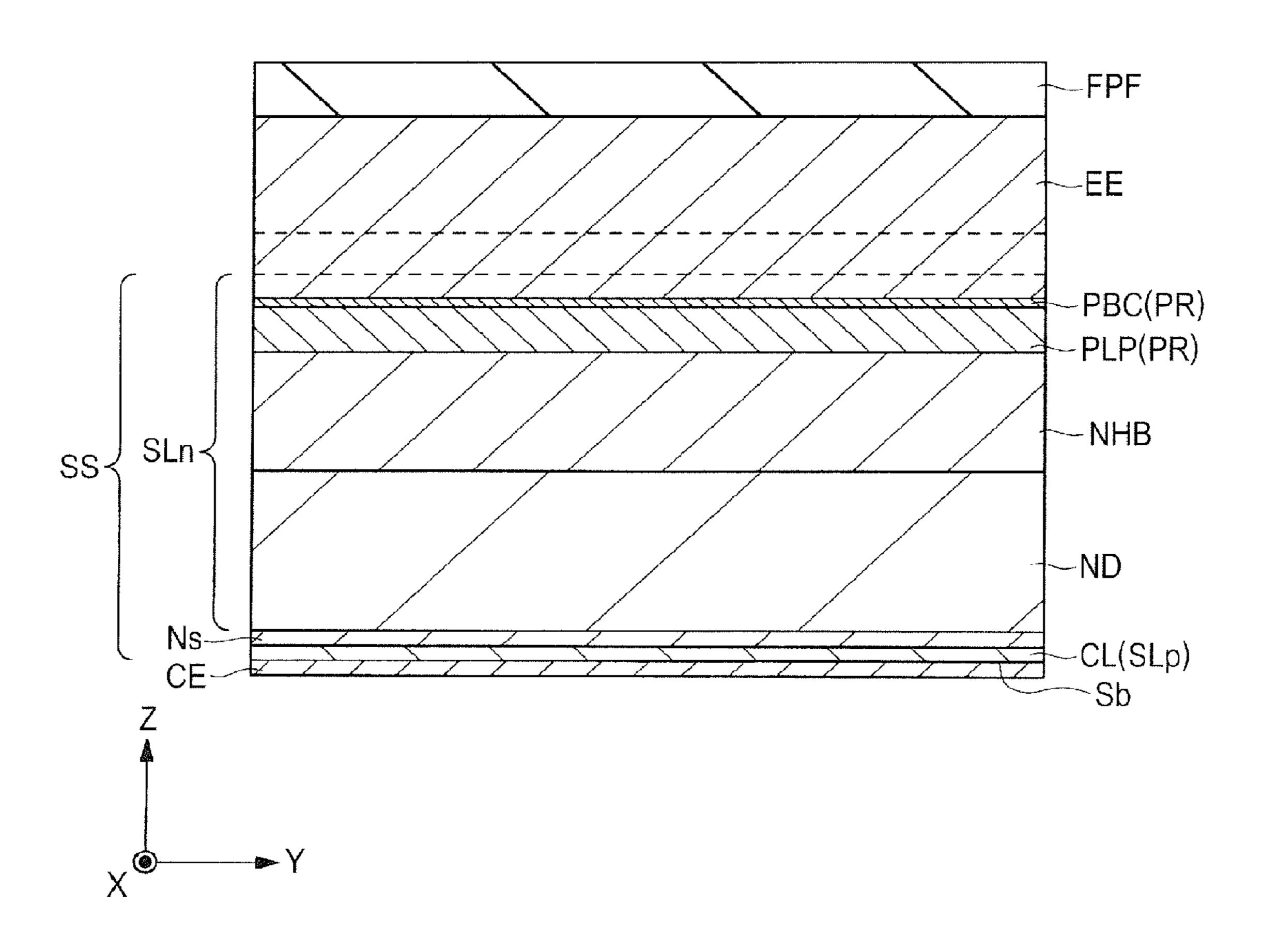

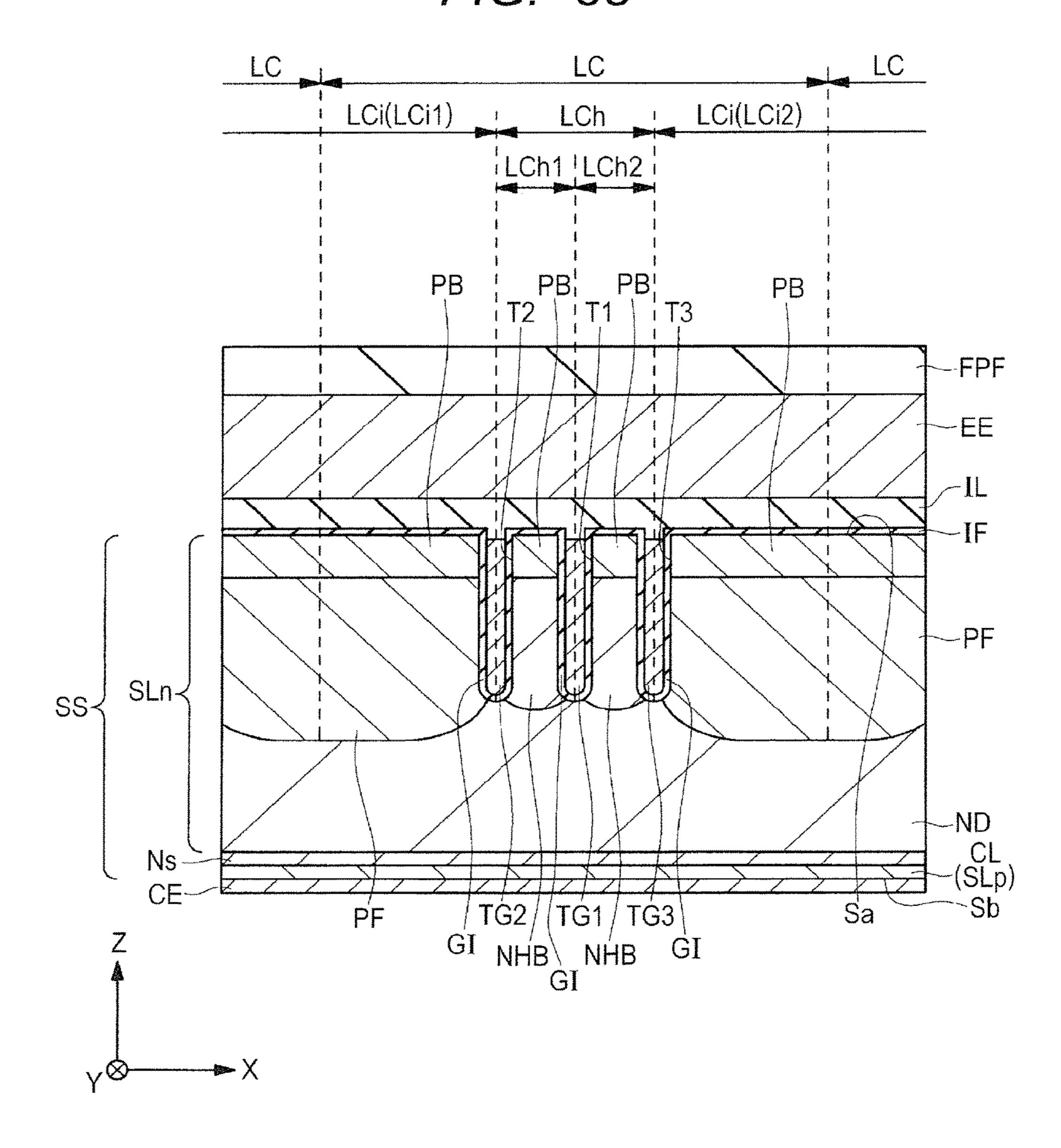

- FIG. 5 is a main-portion cross-sectional view of the semiconductor device in Embodiment 1;

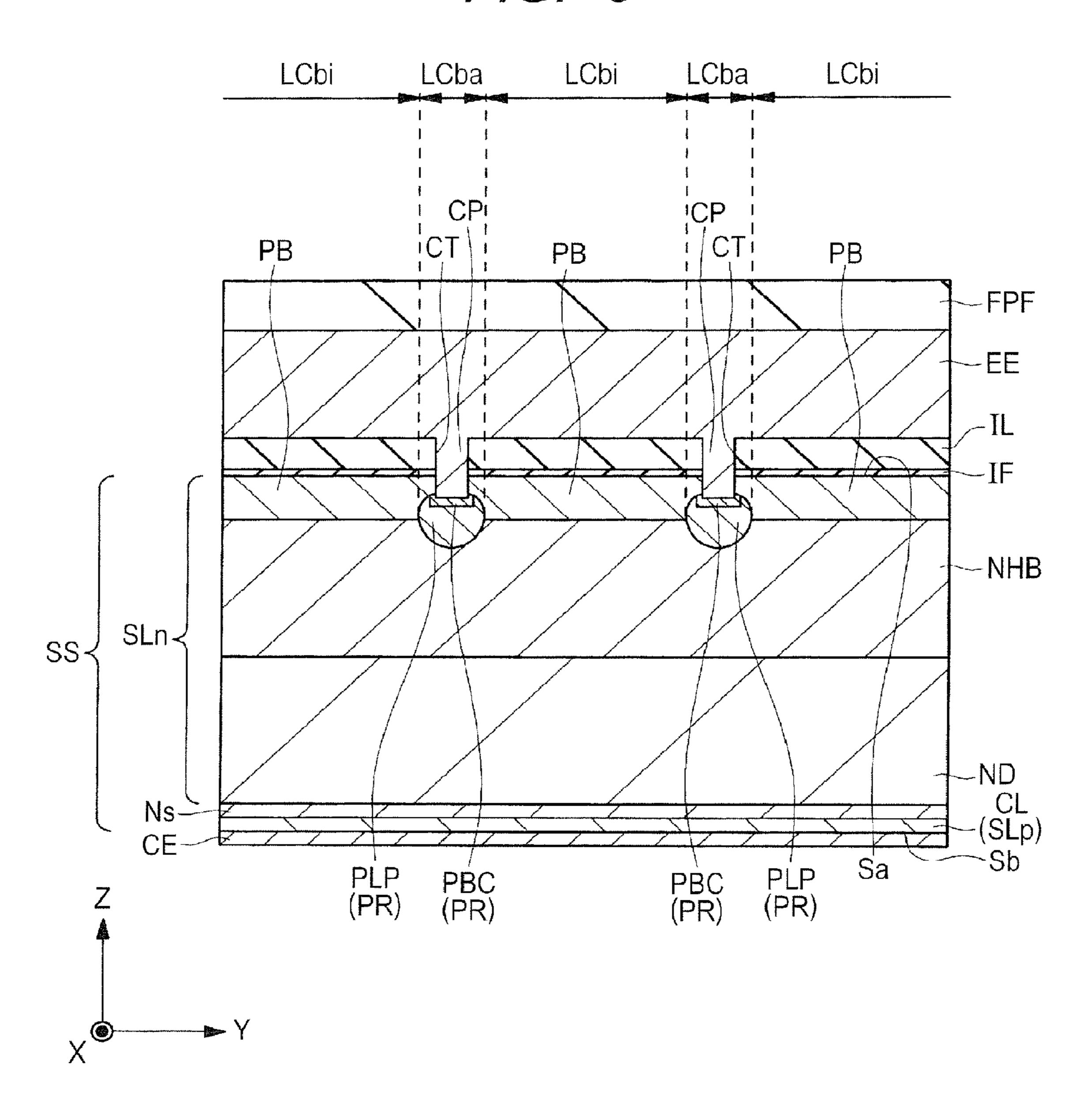

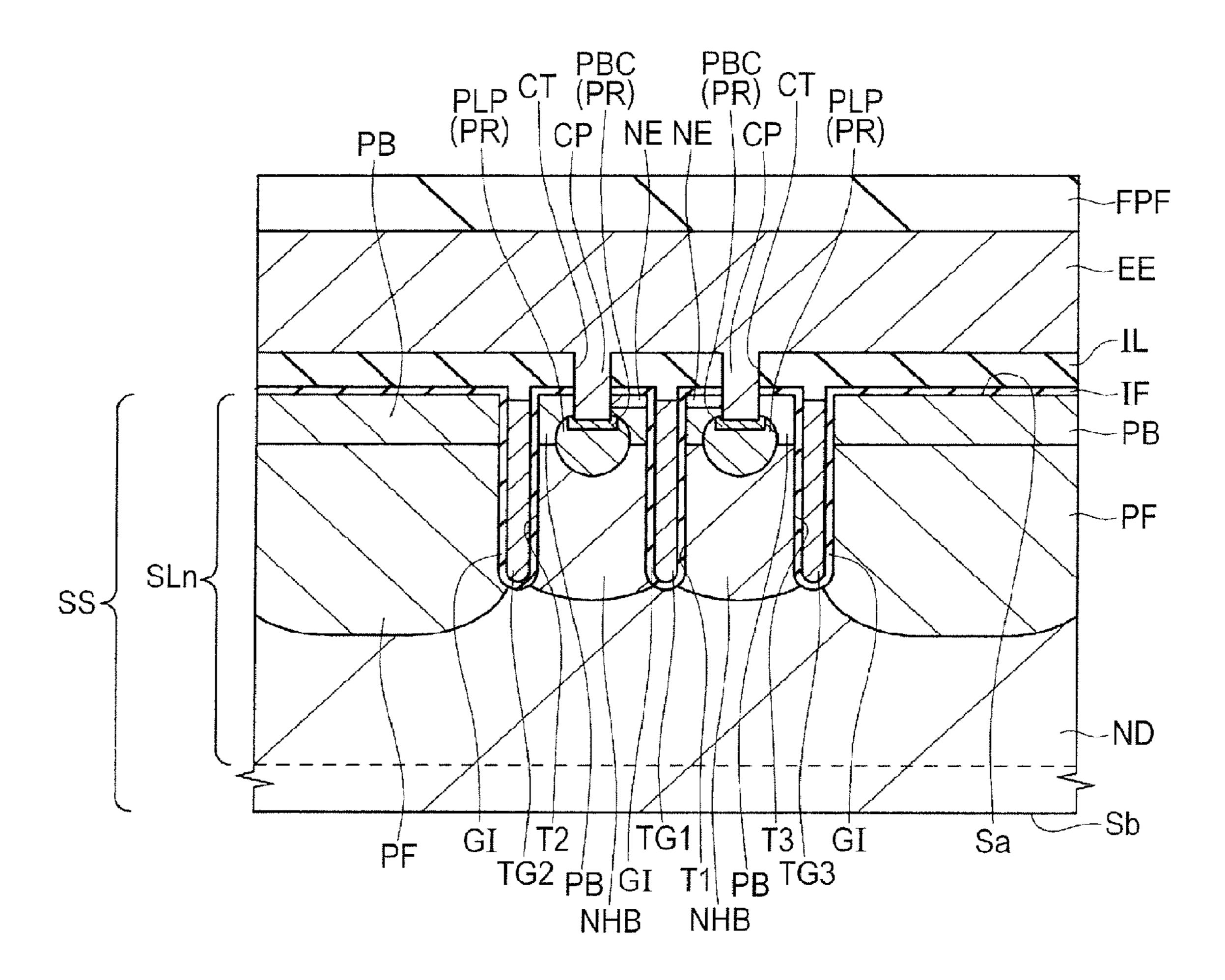

- FIG. 6 is a main-portion cross-sectional view of the semiconductor device in Embodiment 1;

- FIG. 7 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

- FIG. 8 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

- FIG. 9 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

- FIG. 10 is a main-portion cross-sectional view showing 15 parative Example 2; the manufacturing process of the semiconductor device in Embodiment 1;

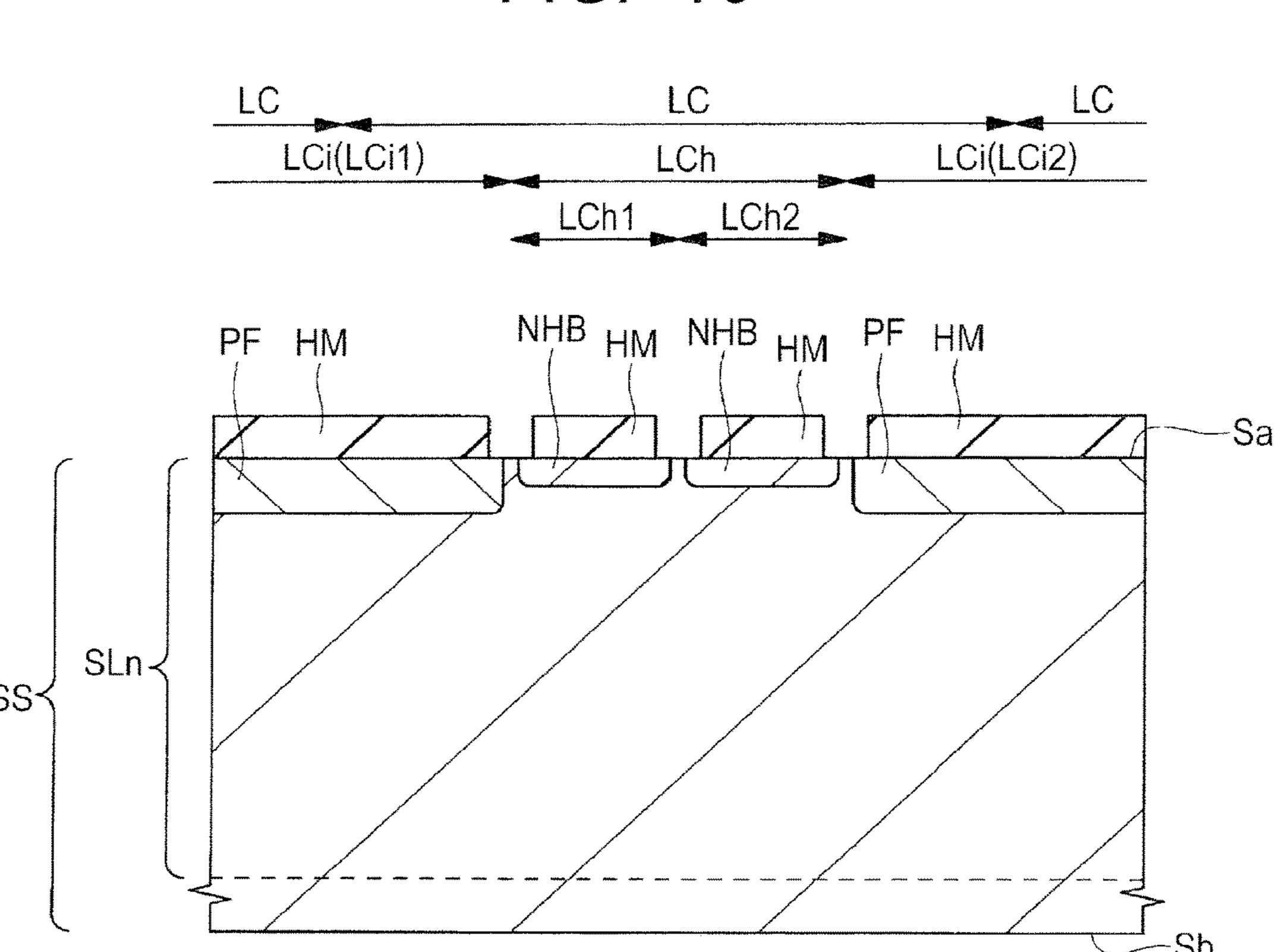

- FIG. 11 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

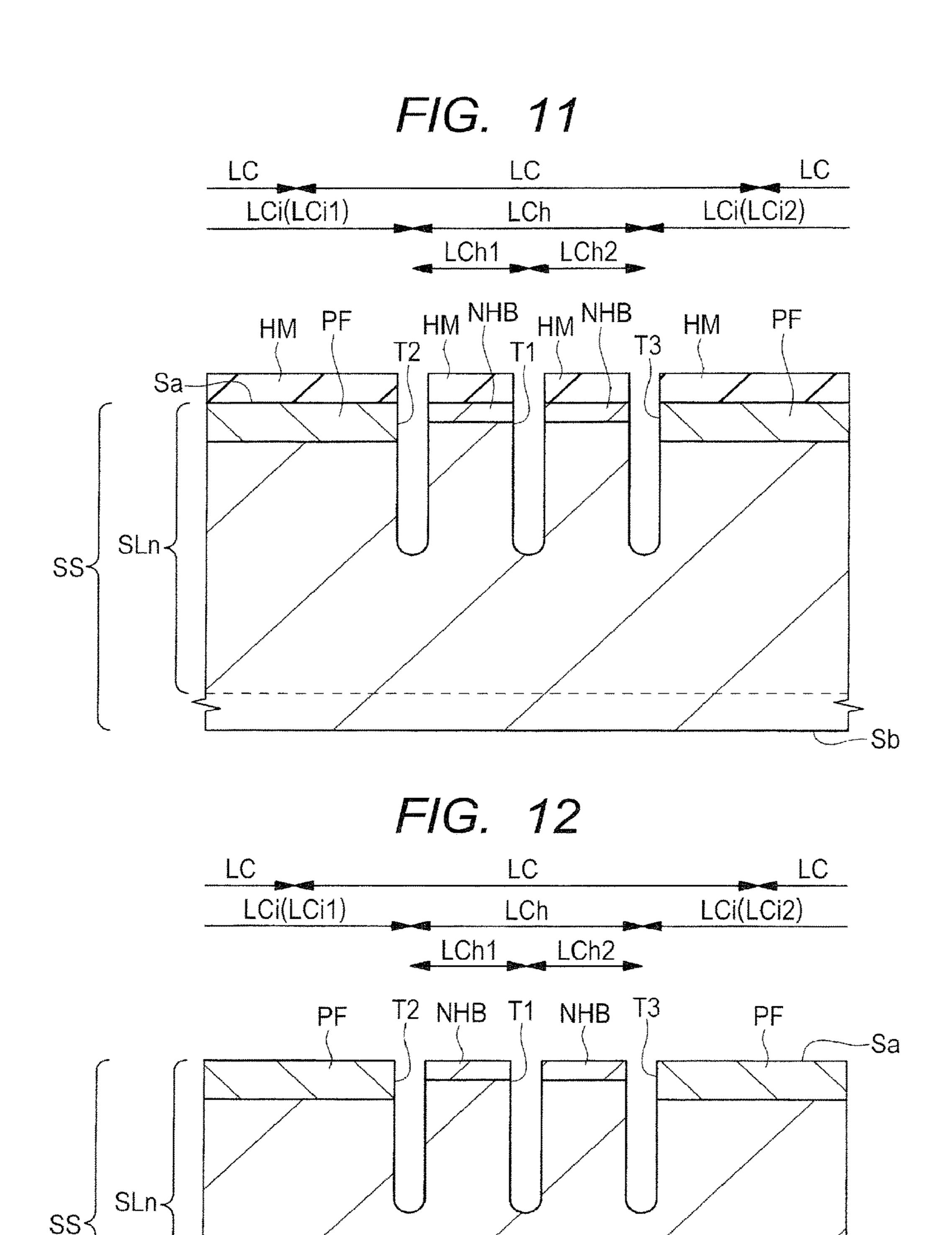

- FIG. 12 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

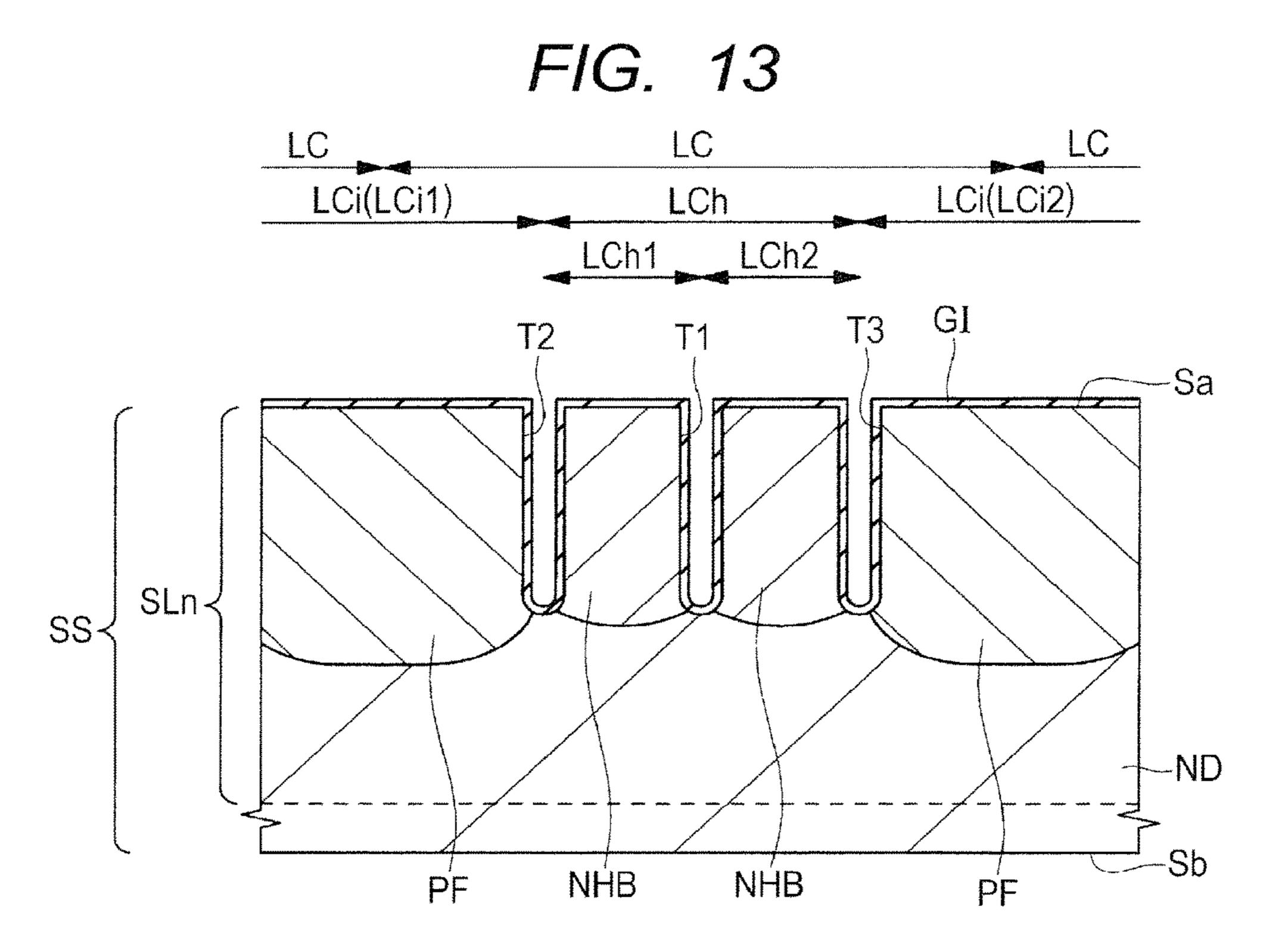

- FIG. 13 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in 25 Embodiment 1;

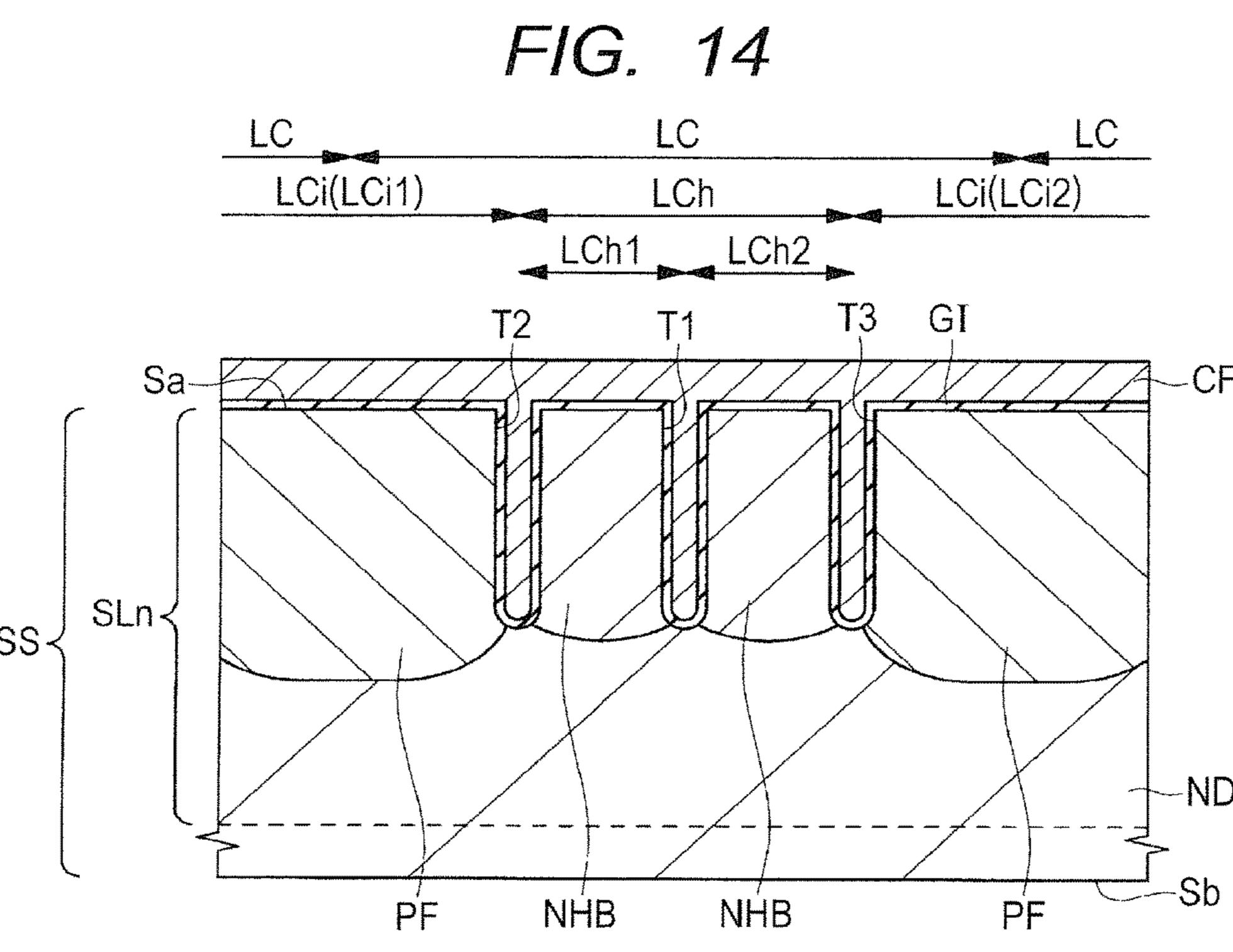

- FIG. 14 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

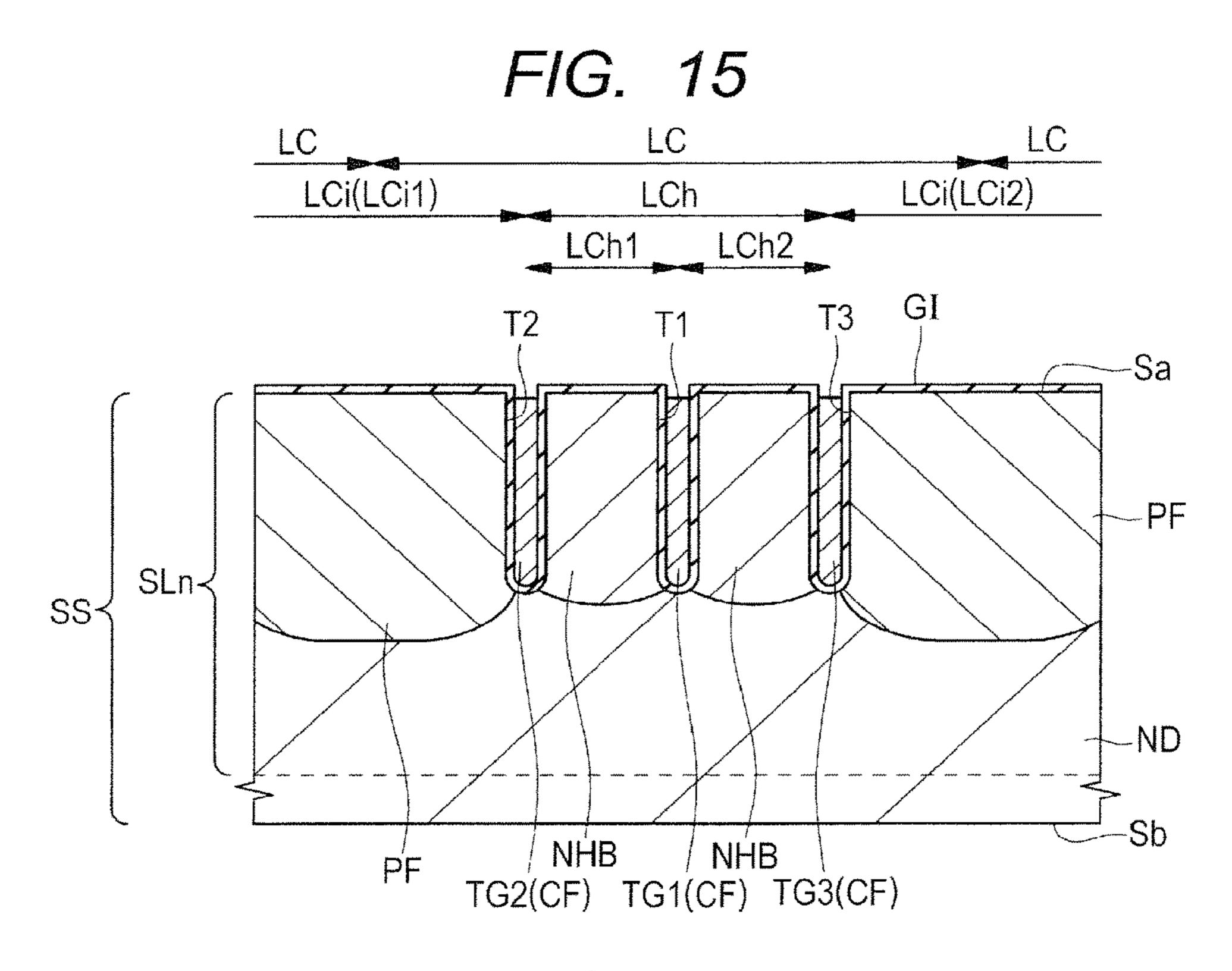

- FIG. 15 is a main-portion cross-sectional view showing 30 the manufacturing process of the semiconductor device in Embodiment 1;

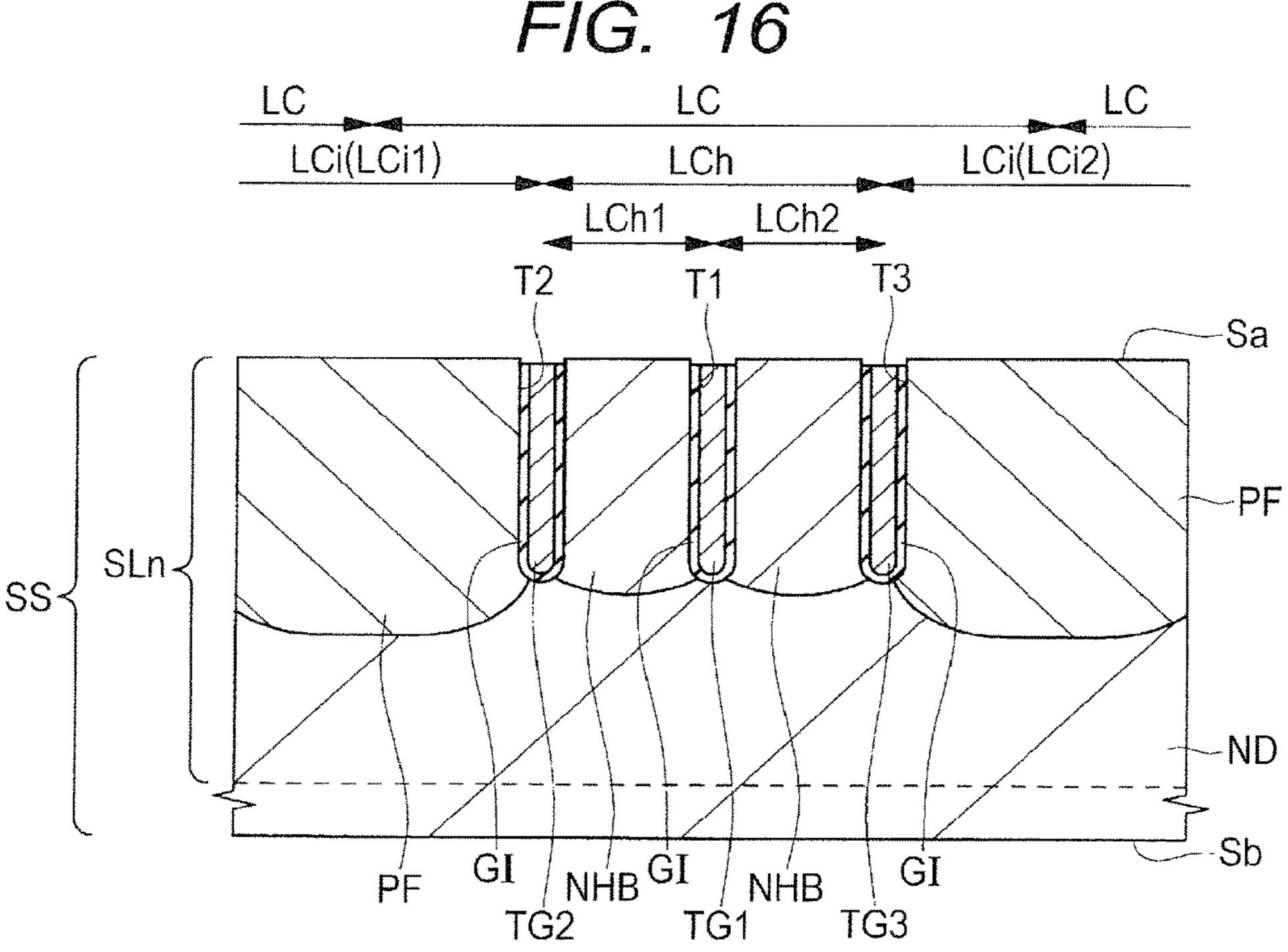

- FIG. 16 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

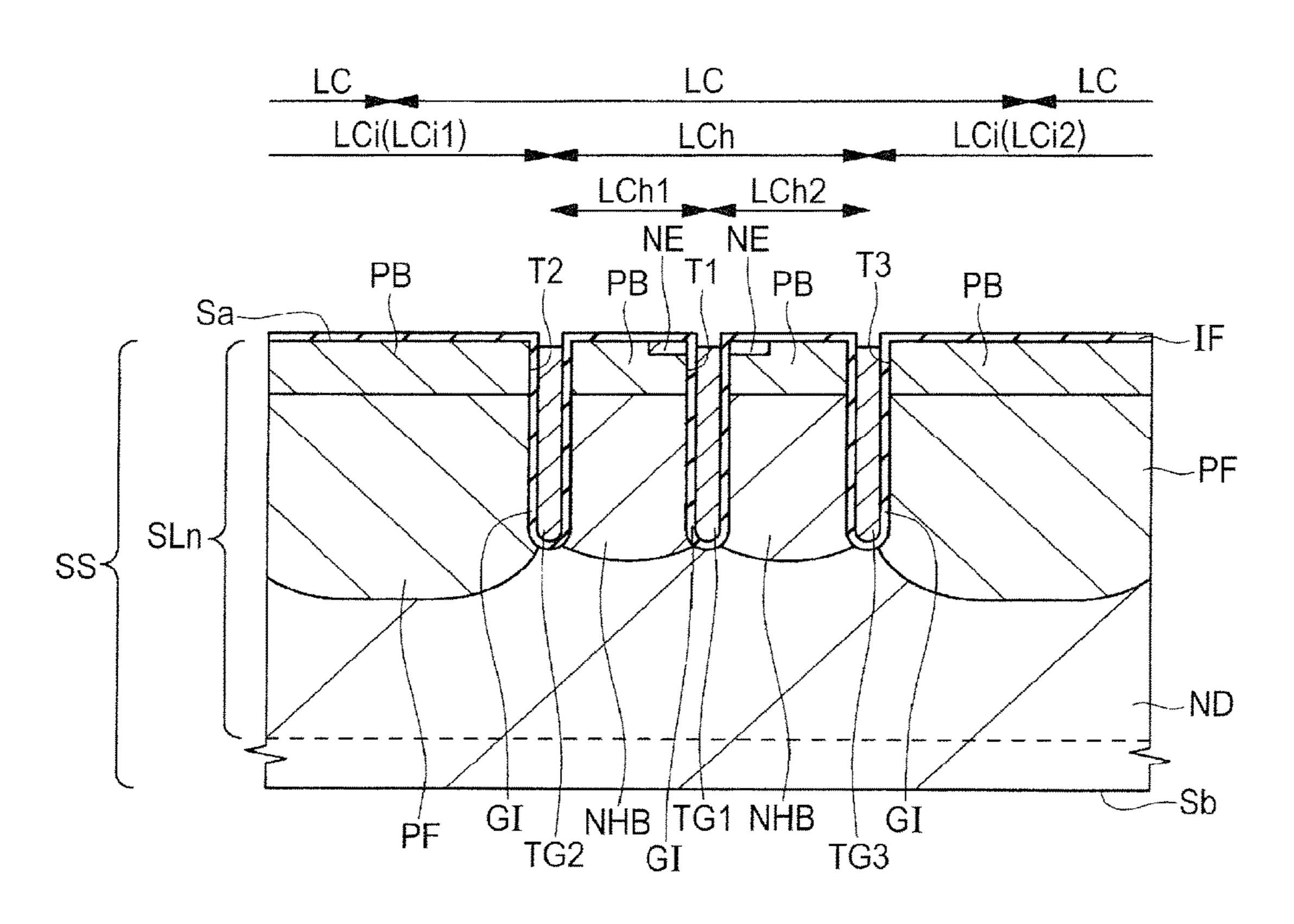

- FIG. 17 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

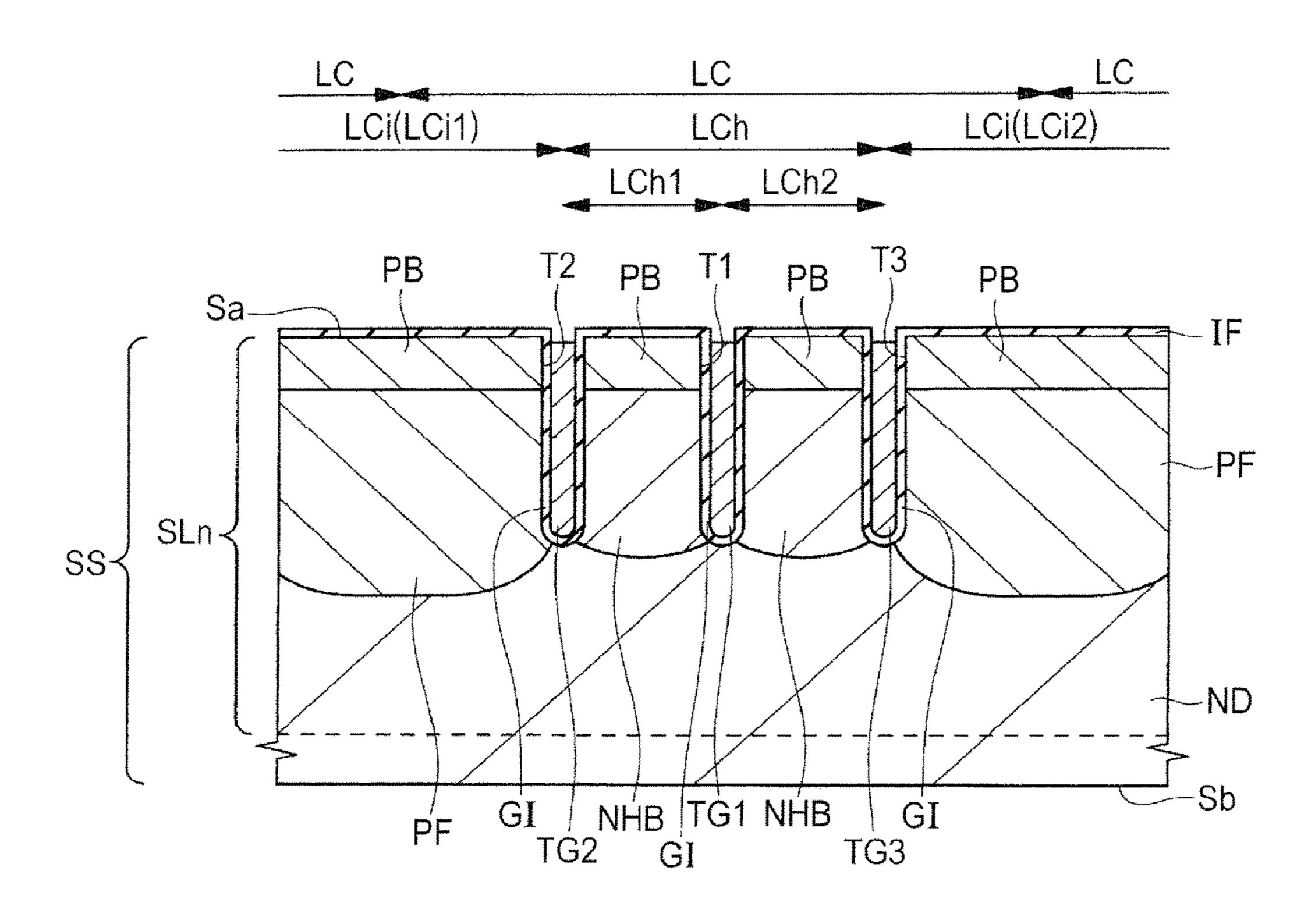

- FIG. 18 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in 40 Embodiment 1;

- FIG. 19 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

- the manufacturing process of the semiconductor device in Embodiment 1;

- FIG. 21 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

- FIG. 22 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

- FIG. 23 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in 55 Comparative Example 2 in the ON state; Embodiment 1;

- FIG. 24 is a main-portion cross-sectional view showing the manufacturing process of the semiconductor device in Embodiment 1;

- semiconductor device in Comparative Example 1;

- FIG. 26 is a main-portion plan view of a semiconductor device in Comparative Example 2;

- FIG. 27 is a main-portion plan view of the semiconductor device in Comparative Example 2;

- FIG. 28 is a main-portion cross-sectional view of the semiconductor device in Comparative Example 2;

- FIG. 29 is a cross-sectional view showing displacement current paths when the semiconductor device in Comparative Example 1 is turned ON in overlapping relation;

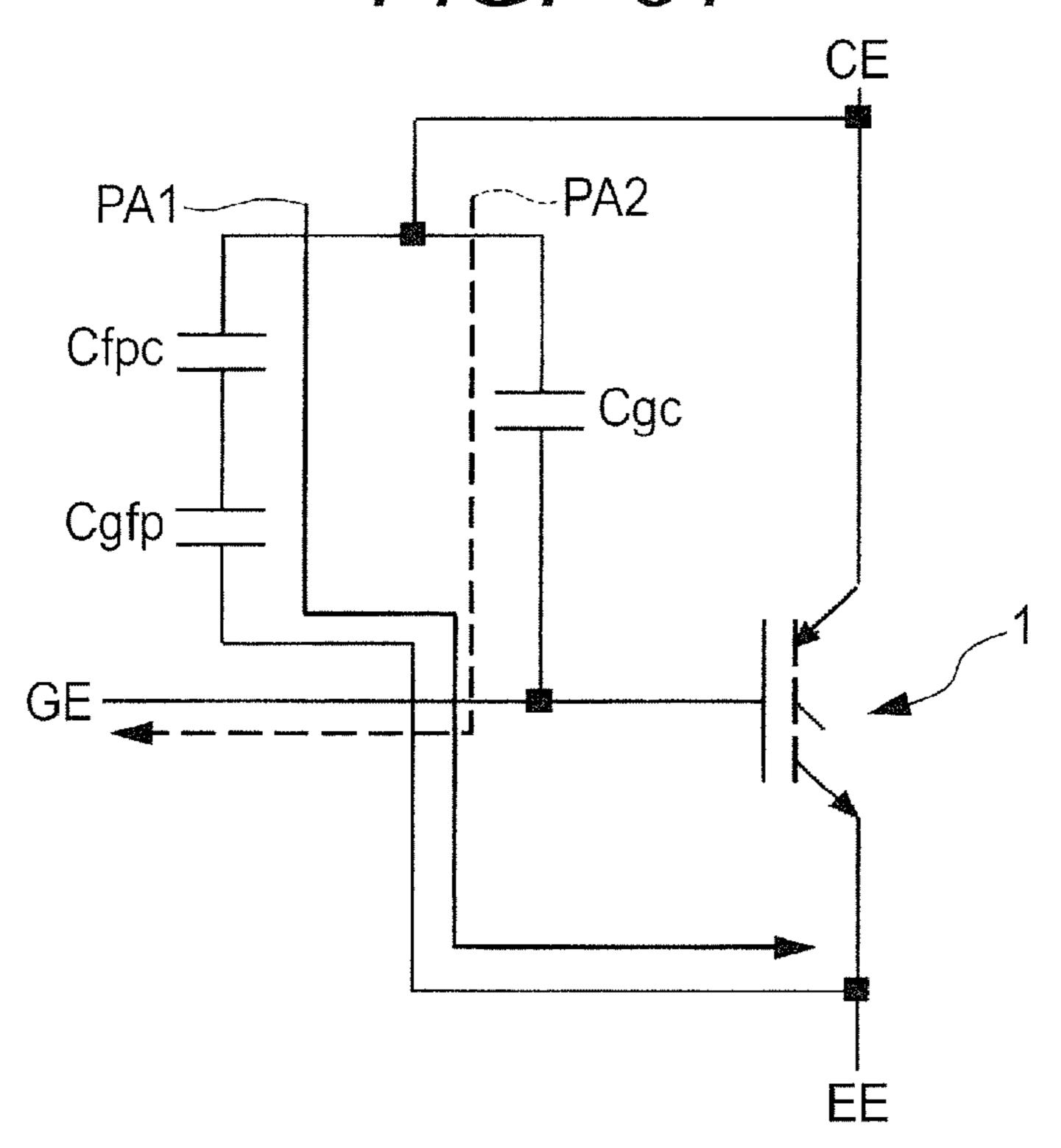

- FIG. 30 is an equivalent circuit diagram showing the displacement current paths when the semiconductor device in Comparative Example 1 is turned ON;

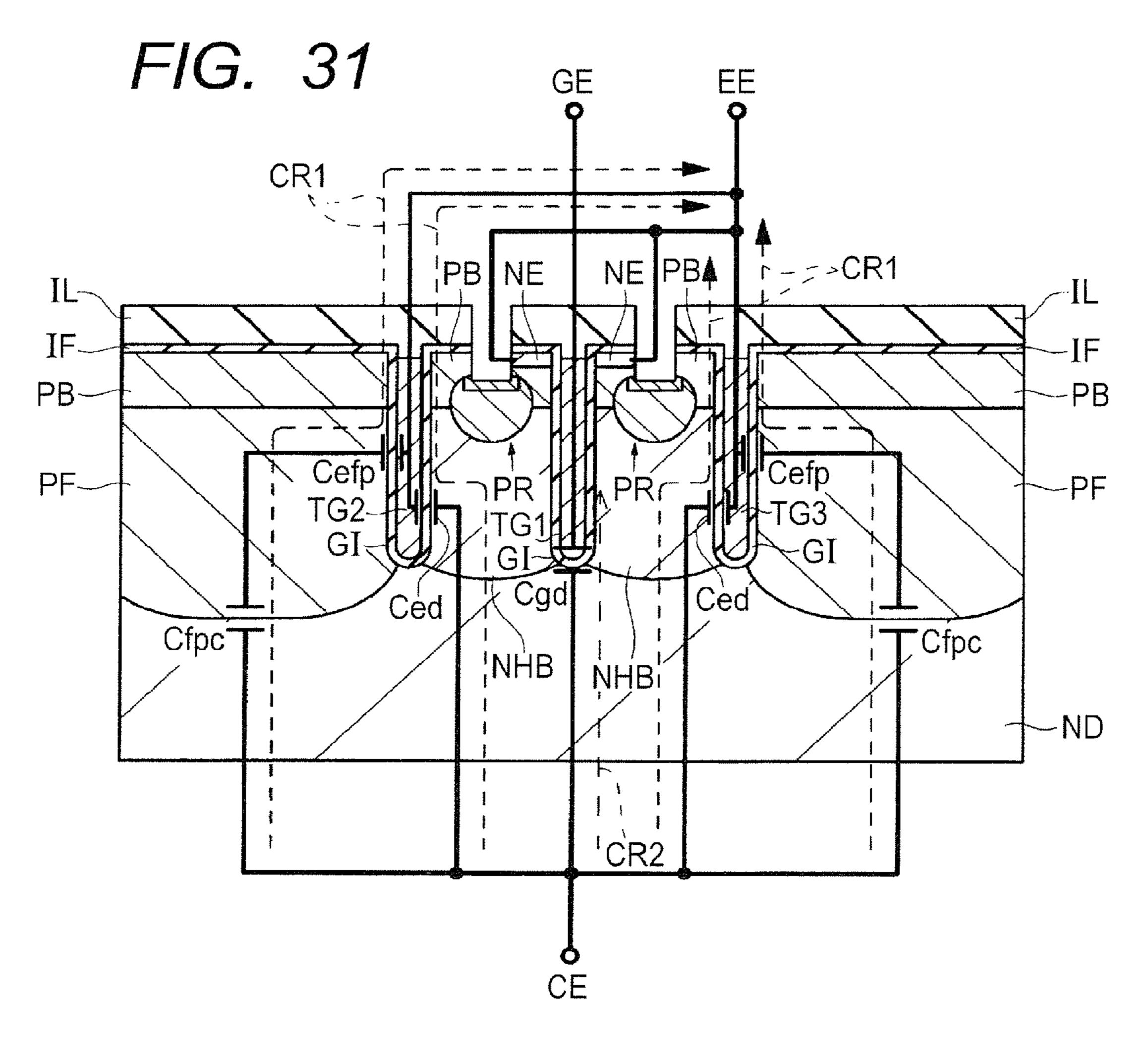

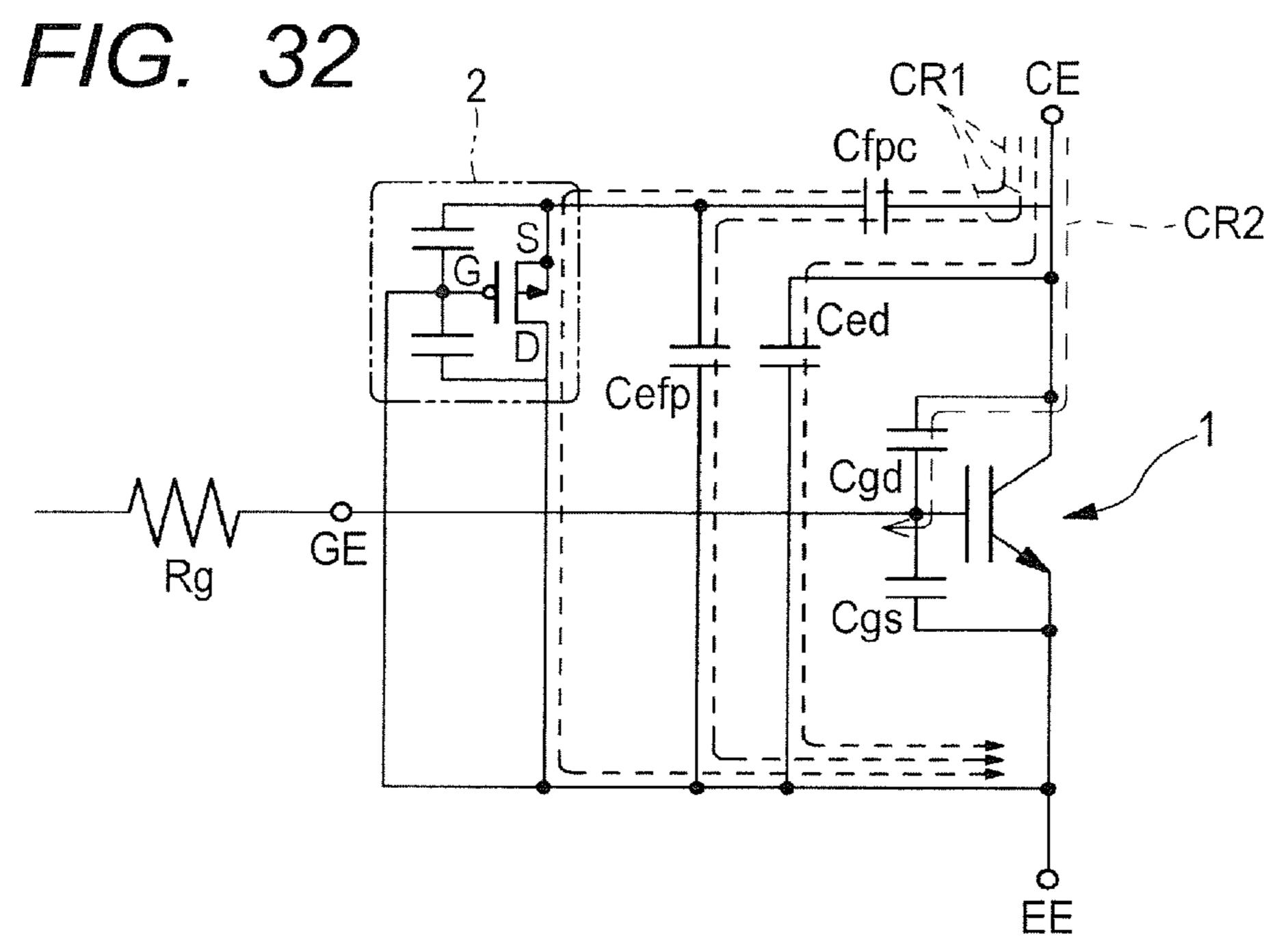

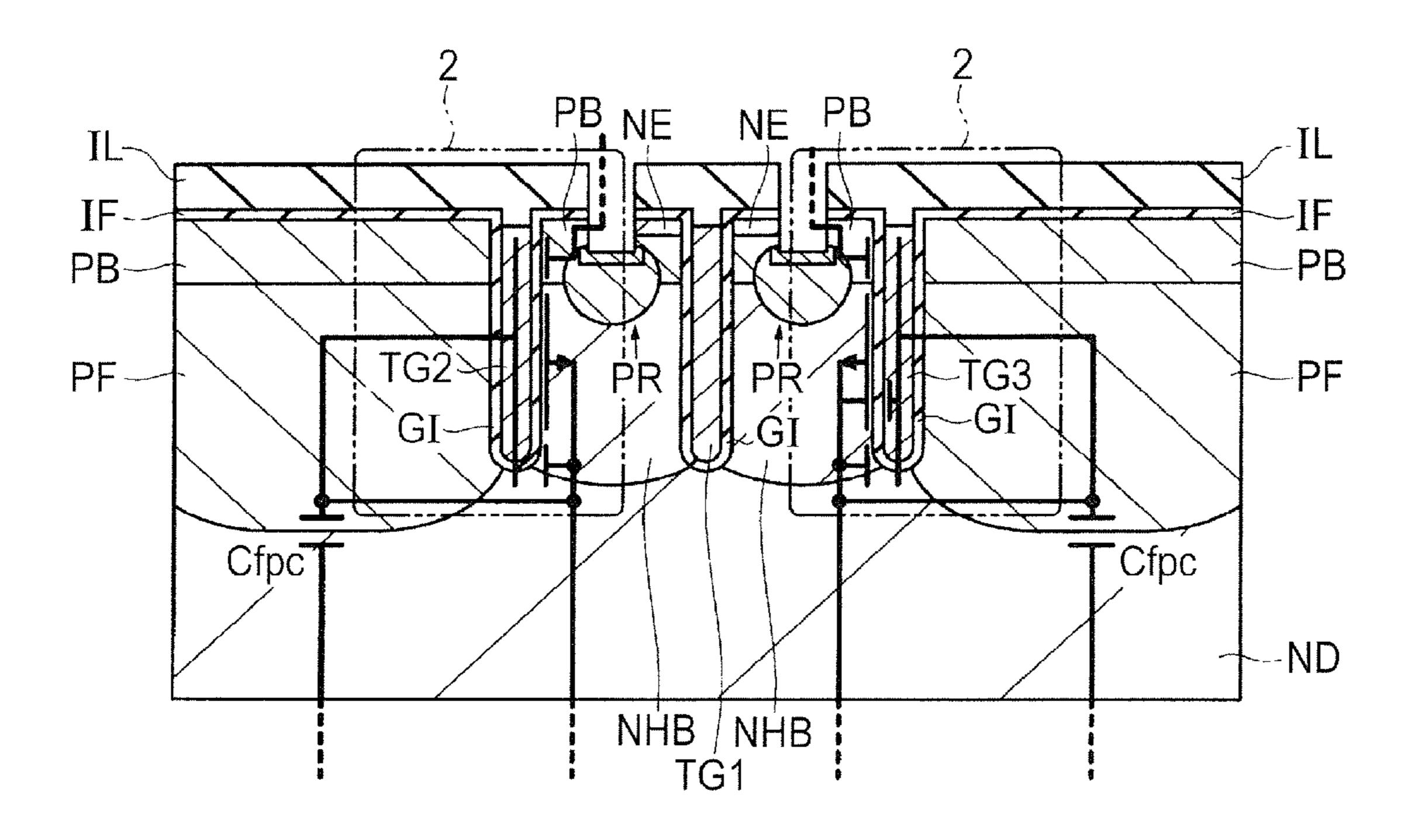

- FIG. 31 is a cross-sectional view showing displacement current paths when the semiconductor device in Comparative Example 2 is turned ON in overlapping relation;

- FIG. 32 is an equivalent circuit diagram showing the displacement current paths when the semiconductor device in Comparative Example 2 is turned ON;

- FIG. 33 is a cross-sectional view showing a p-channel parasitic MOSFET in the semiconductor device in Com-

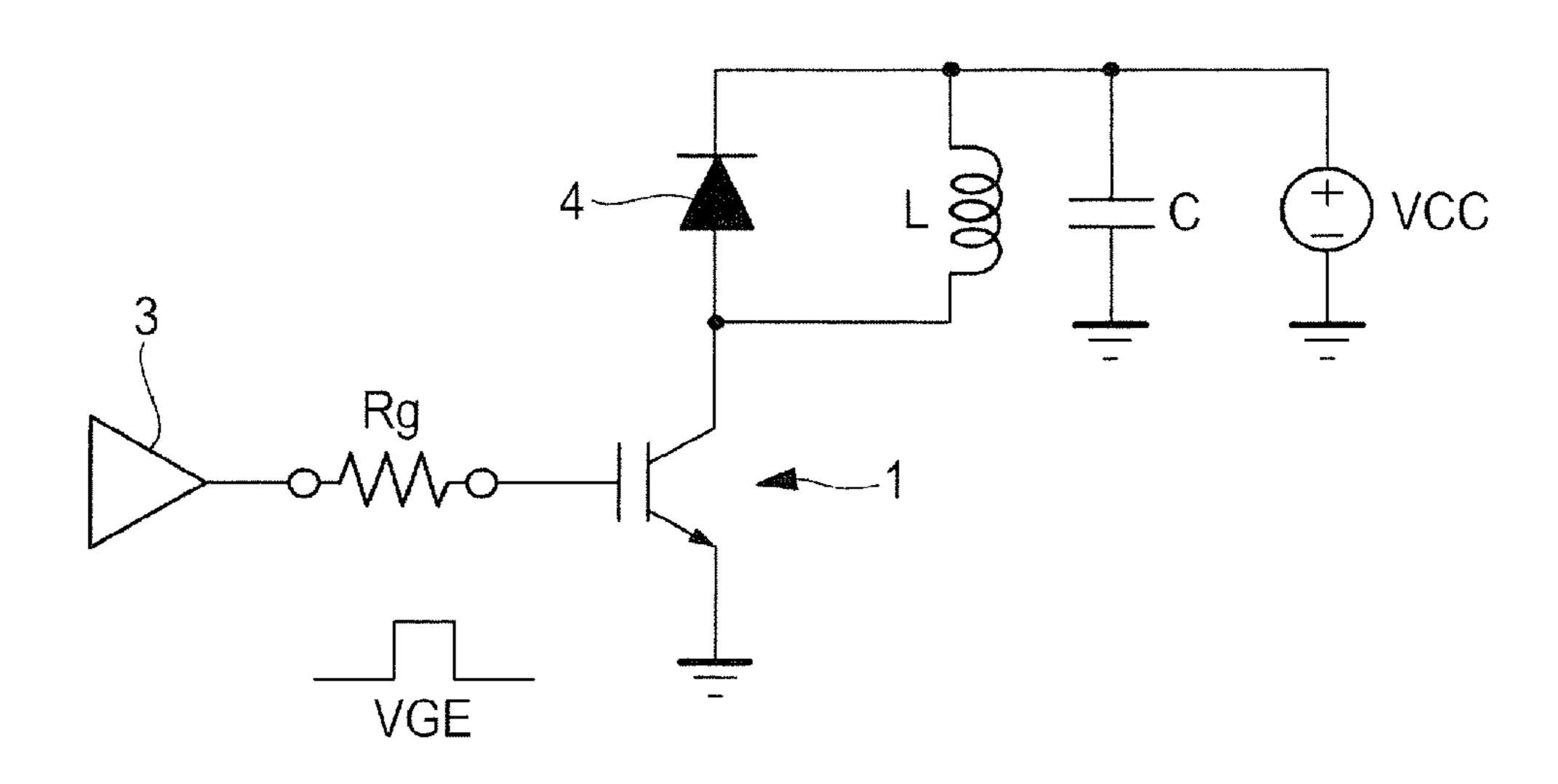

- FIG. 34 is a circuit diagram showing an equivalent circuit in an L-load switching test;

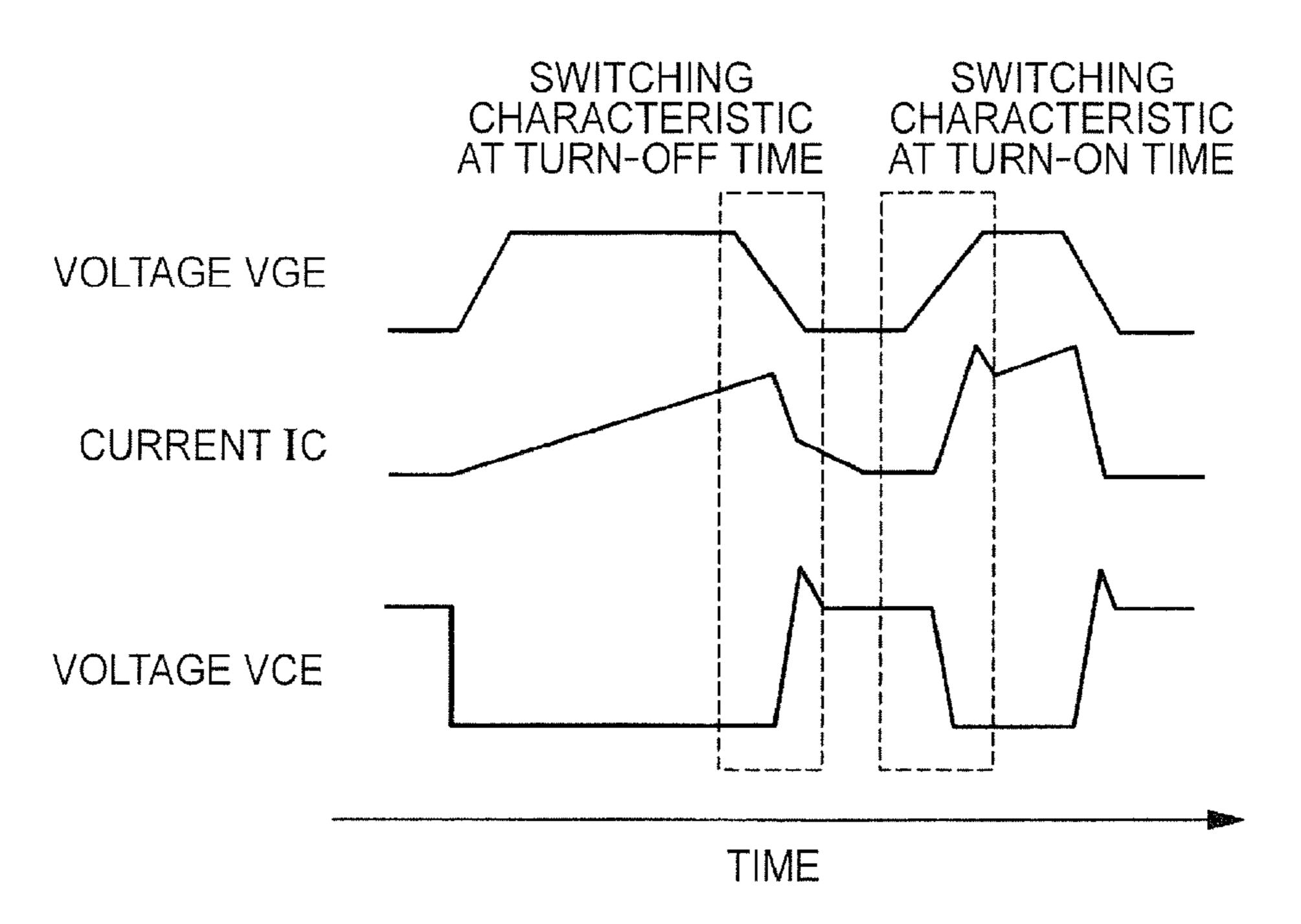

- FIG. 35 is a view schematically showing a switching waveform in the L-load switching test;

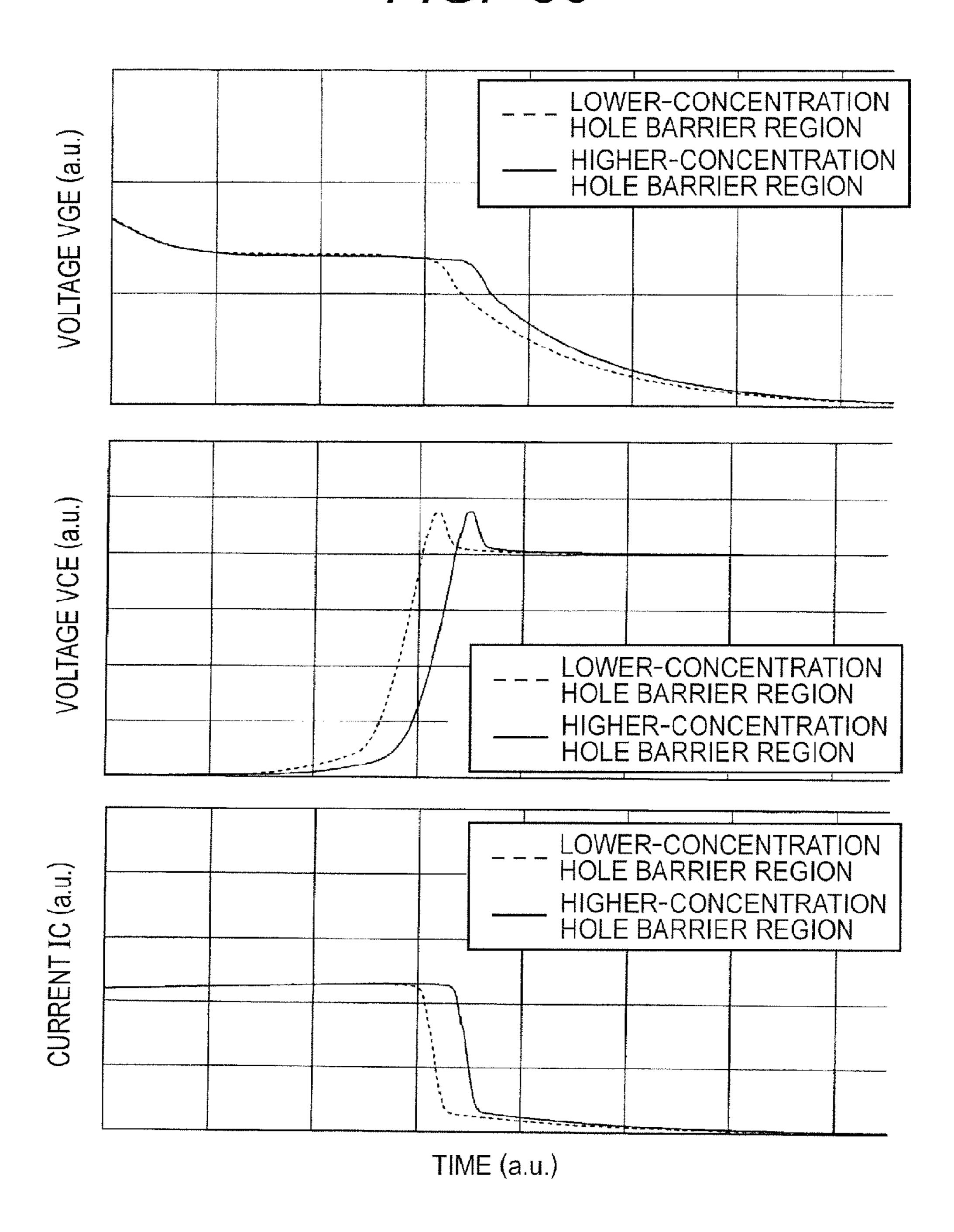

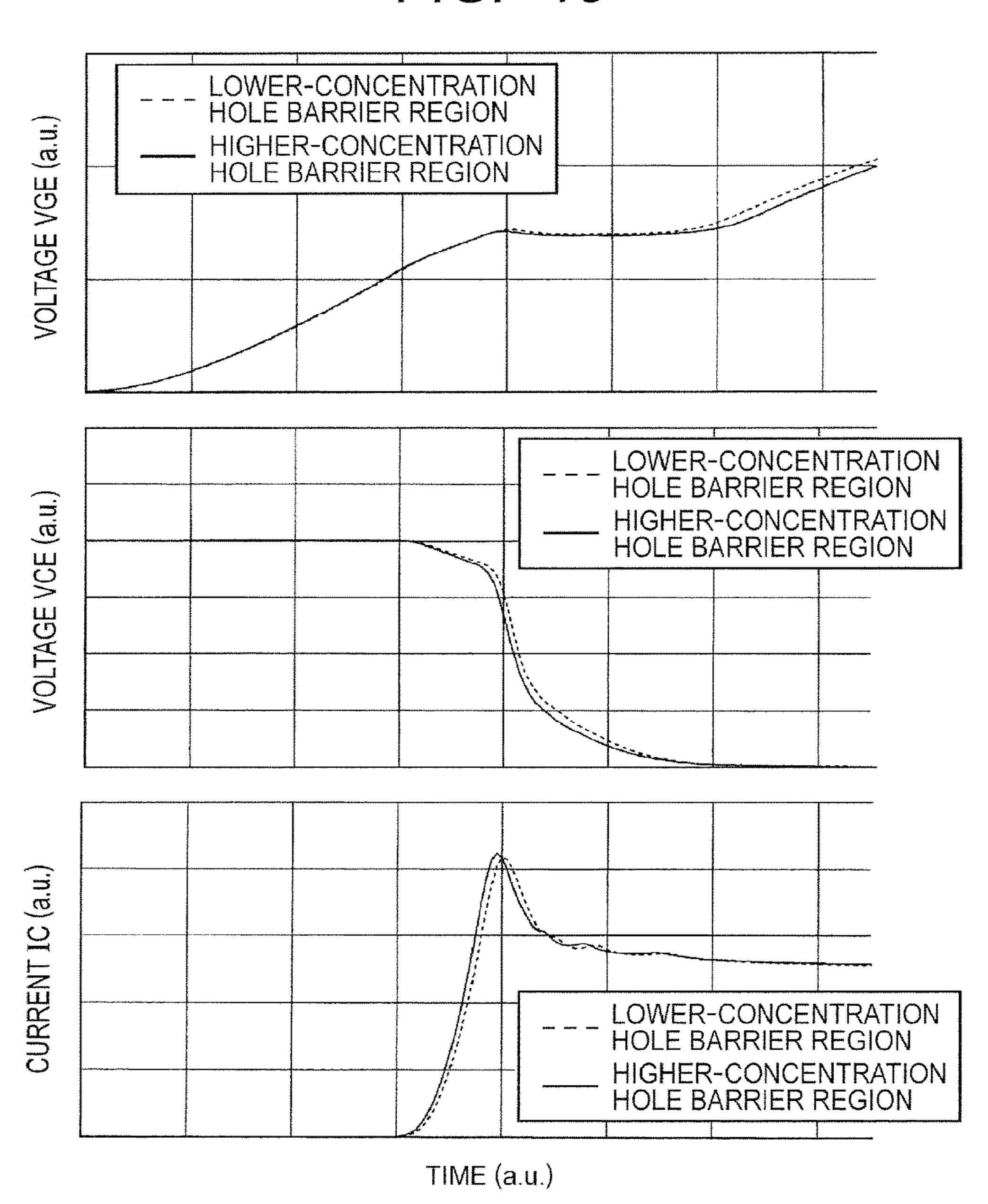

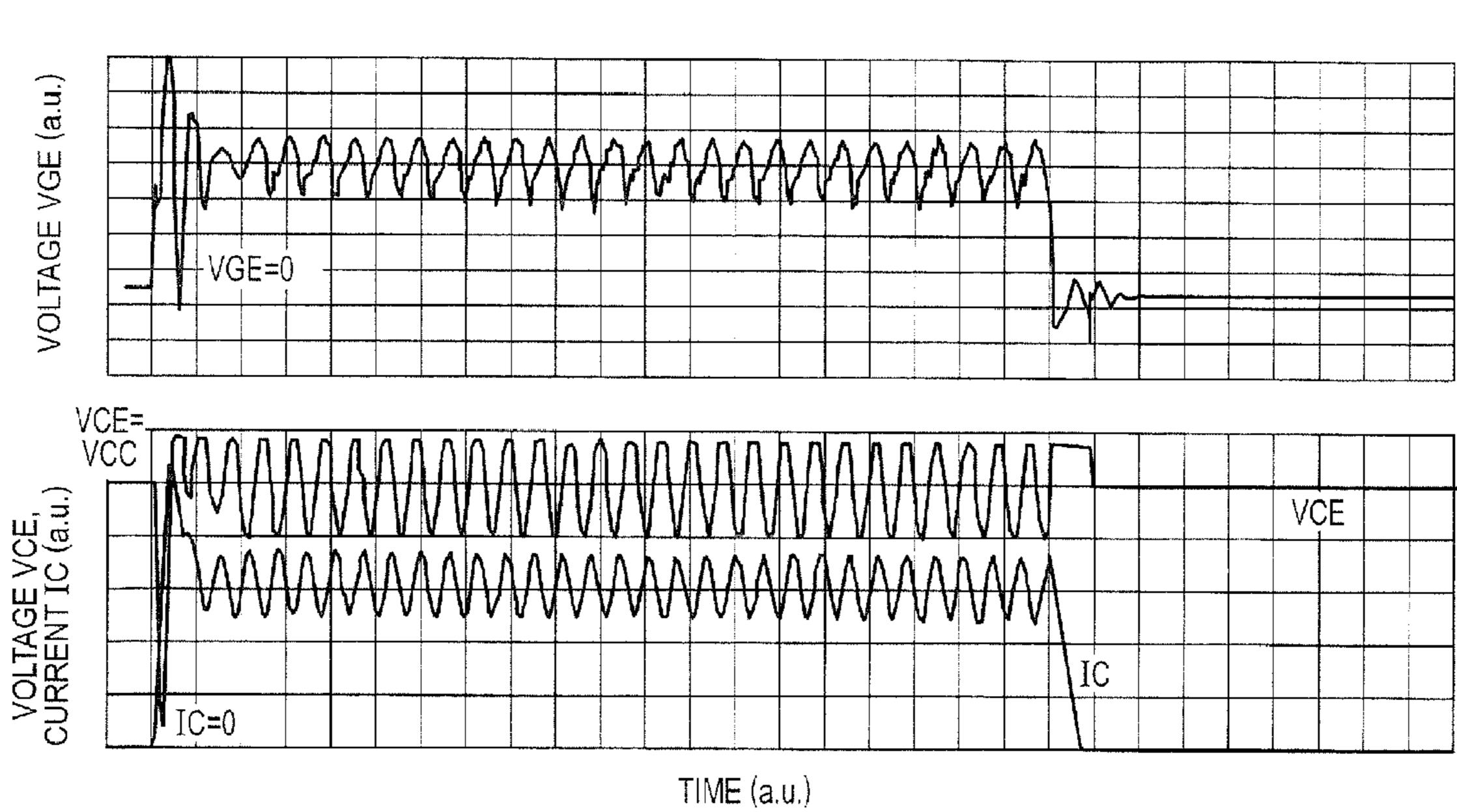

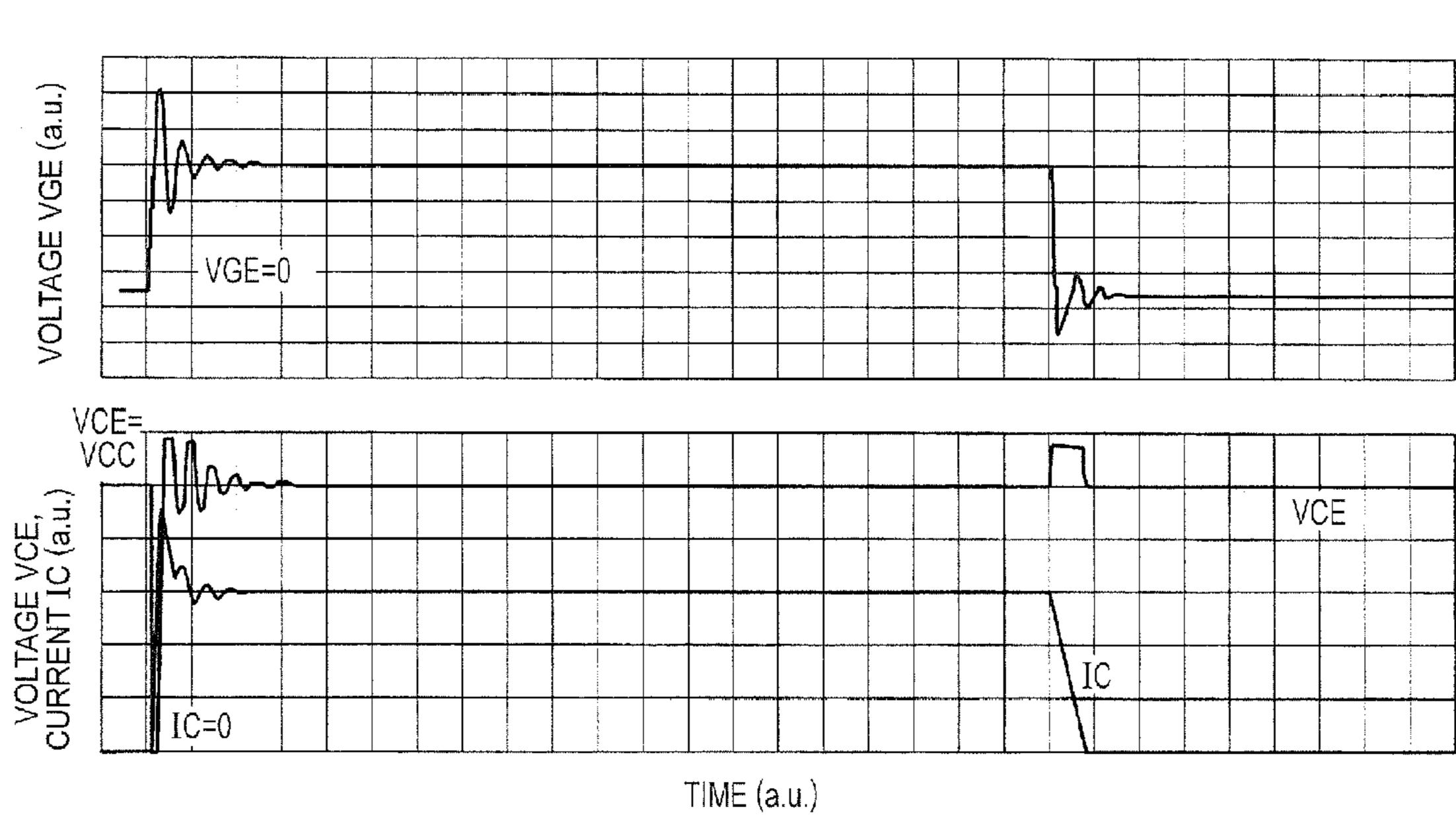

- FIG. 36 is a graph showing a switching waveform when the semiconductor device in Comparative Example 2 is turned OFF;

- FIG. 37 is a graph showing a switching waveform when the semiconductor device in Comparative Example 2 is turned OFF;

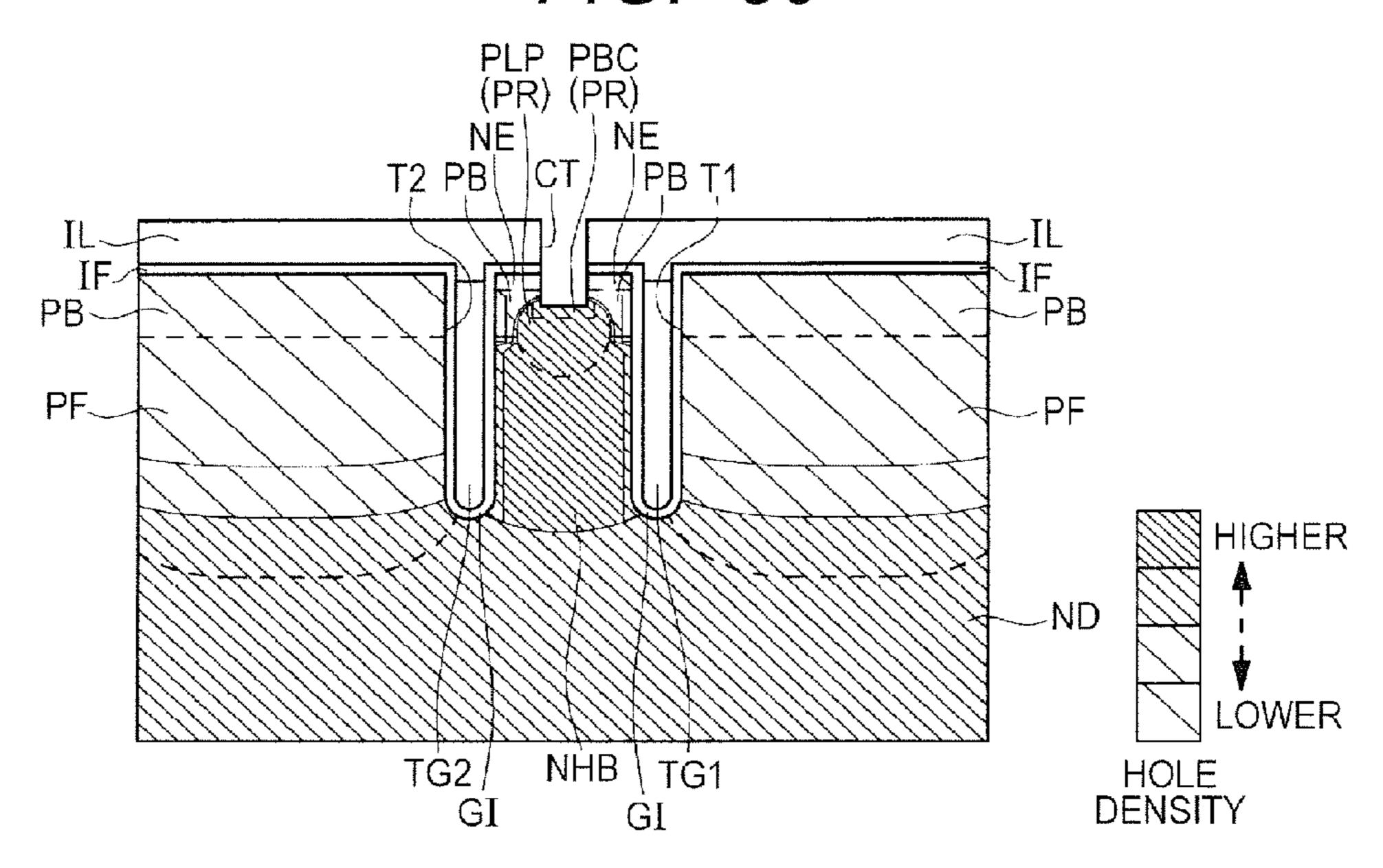

- FIG. 38 is a cross-sectional view showing a hole density distribution when the semiconductor device in Comparative Example 2 is turned OFF;

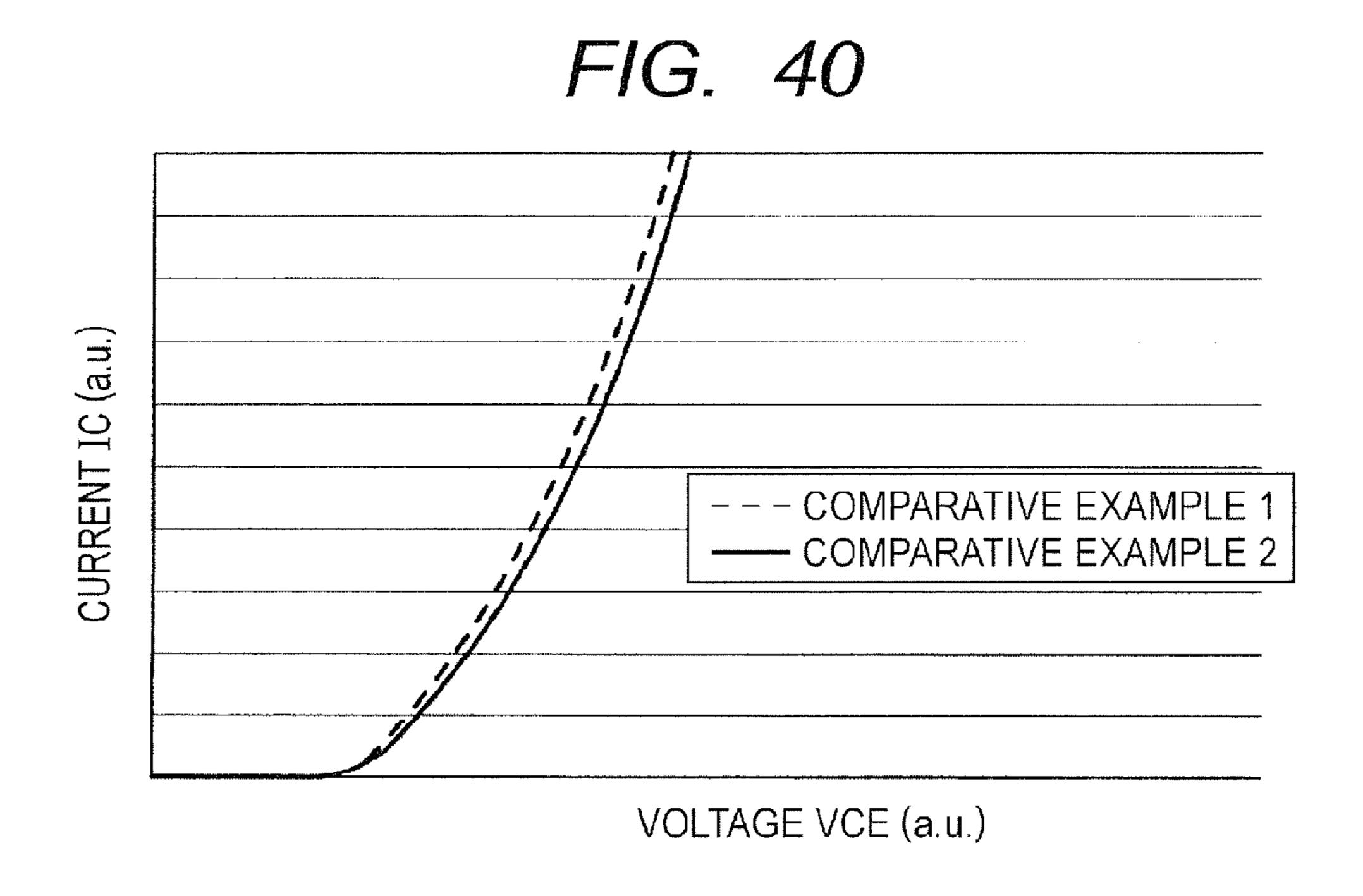

- FIG. 39 is a graph showing the dependence of a collector current on a collector-emitter voltage in each of the semiconductor devices in Comparative Examples 1 and 2 in an ON state;

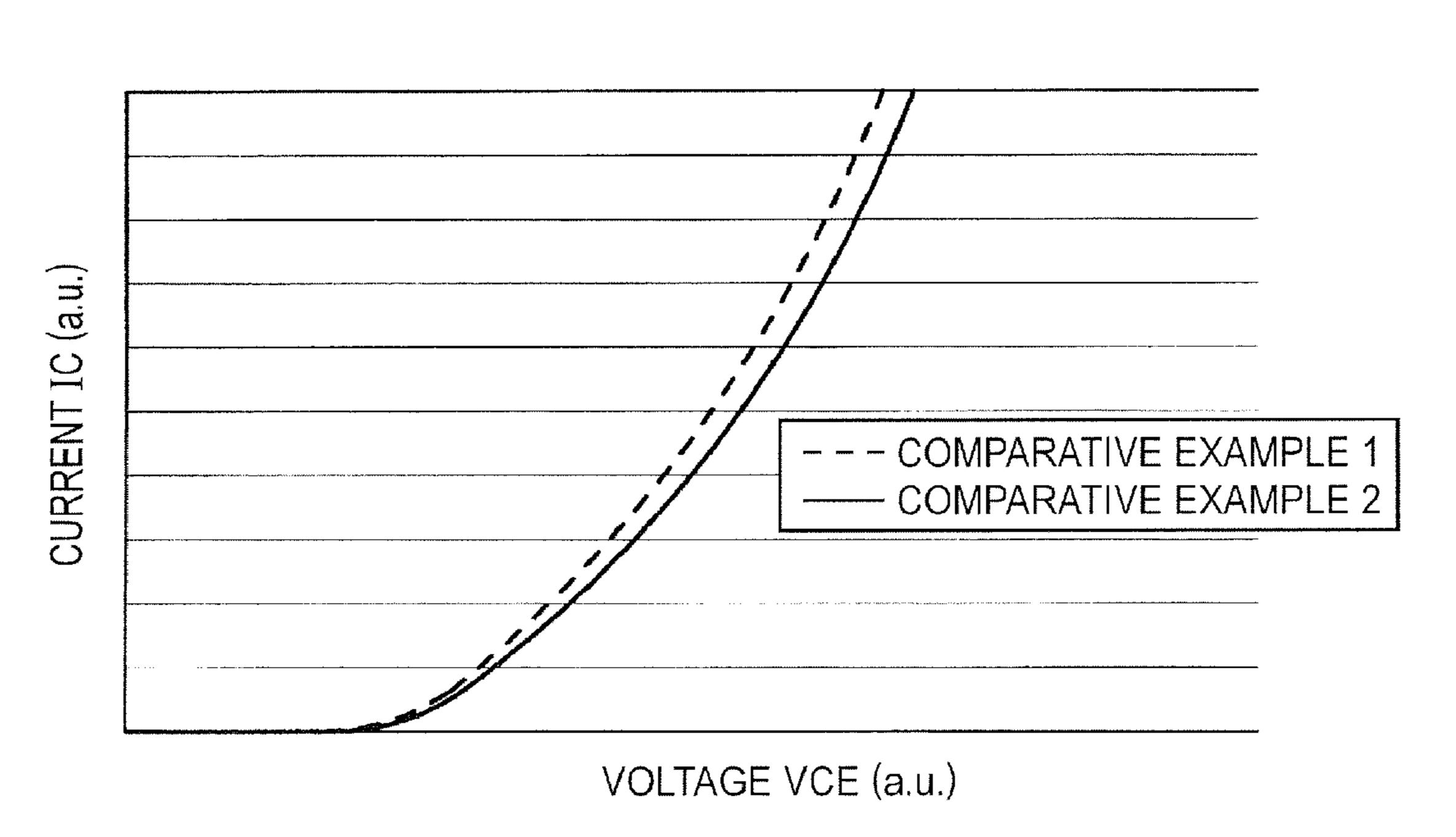

- FIG. 40 is a graph showing the dependence of the collector current on the collector-emitter voltage in each of 35 the semiconductor devices in Comparative Examples 1 and 2 in the ON state;

- FIG. 41 is a graph showing the dependence of the collector current on the collector-emitter voltage in each of the semiconductor devices in Comparative Examples 1 and 2 in the ON state;

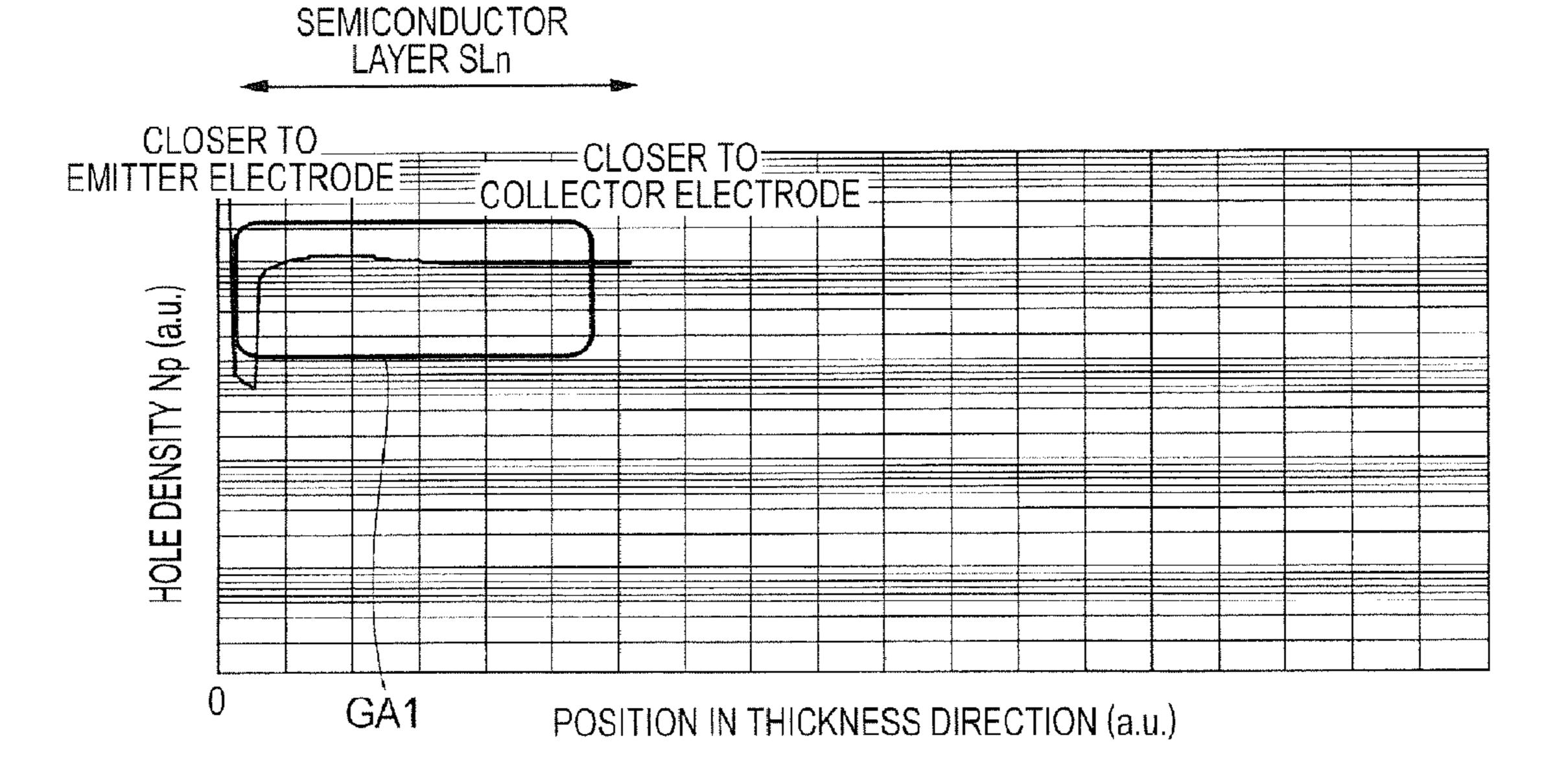

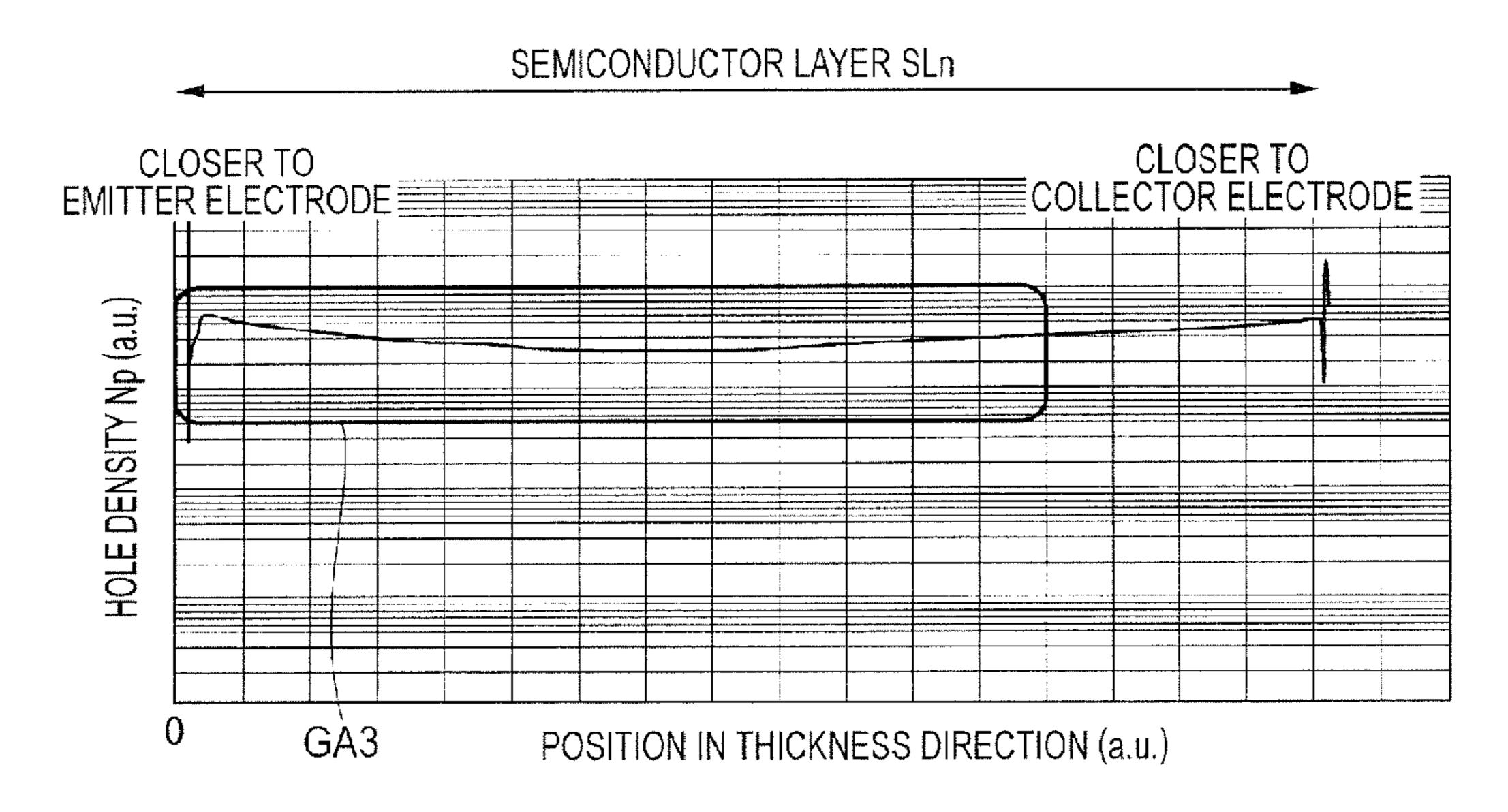

- FIG. **42** is a graph showing a hole density distribution in a thickness direction in the semiconductor device in Comparative Example 1 in the ON state;

- FIG. 43 is a graph showing the hole density distribution FIG. 20 is a main-portion cross-sectional view showing 45 in the thickness direction in the semiconductor device in Comparative Example 1 in the ON state;

- FIG. 44 is a graph showing the hole density distribution in the thickness direction in the semiconductor device in Comparative Example 1 in the ON state;

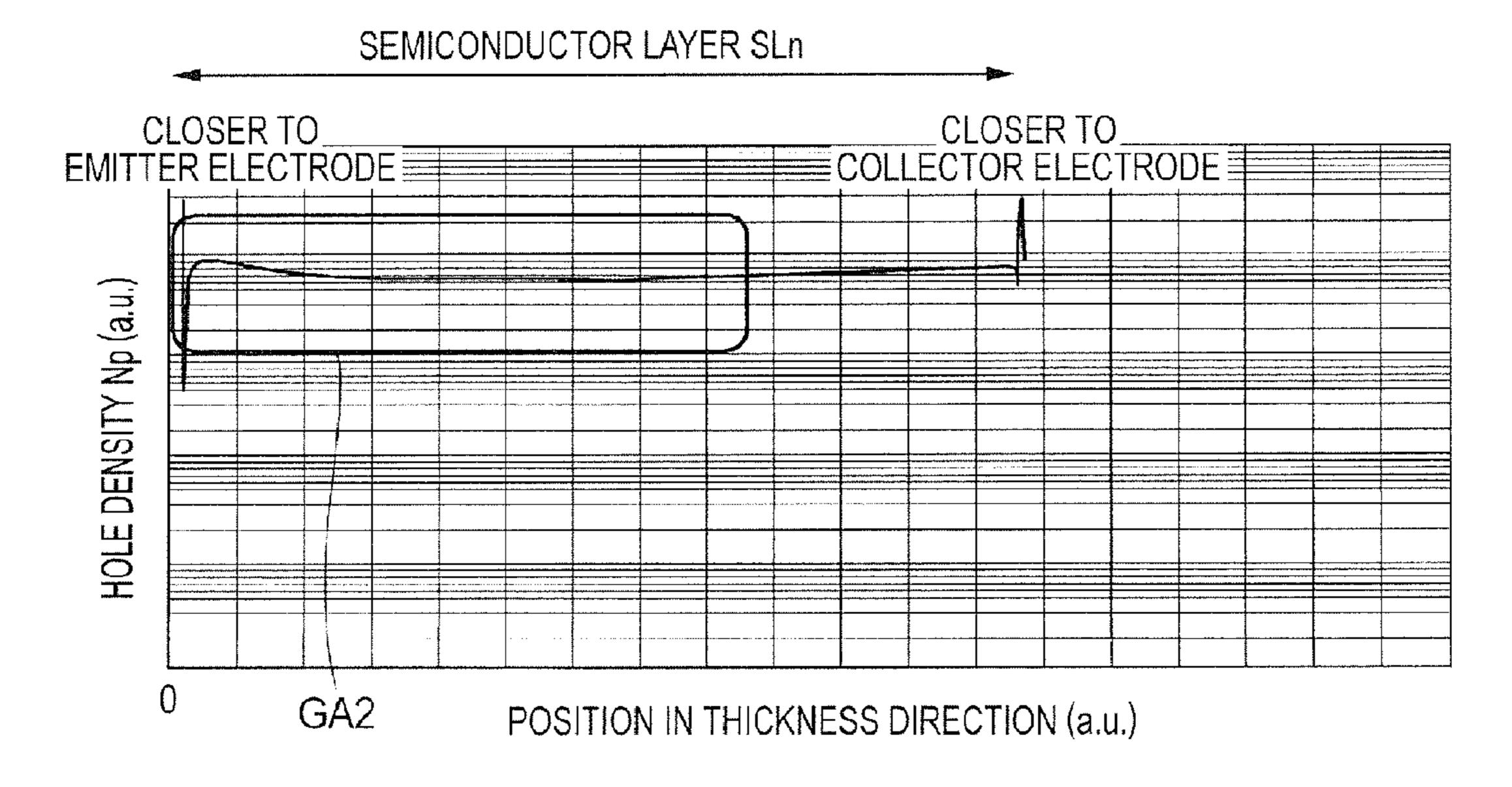

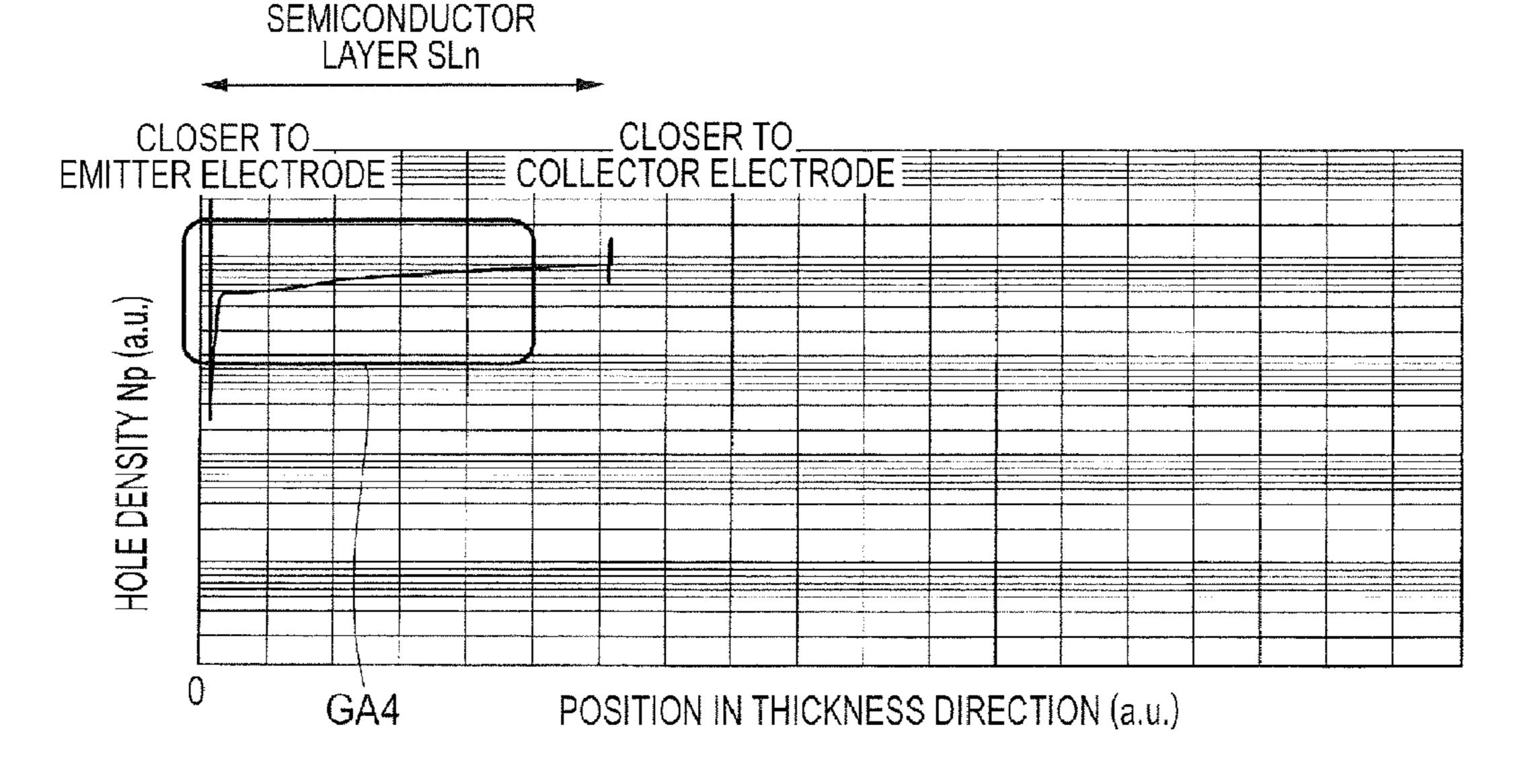

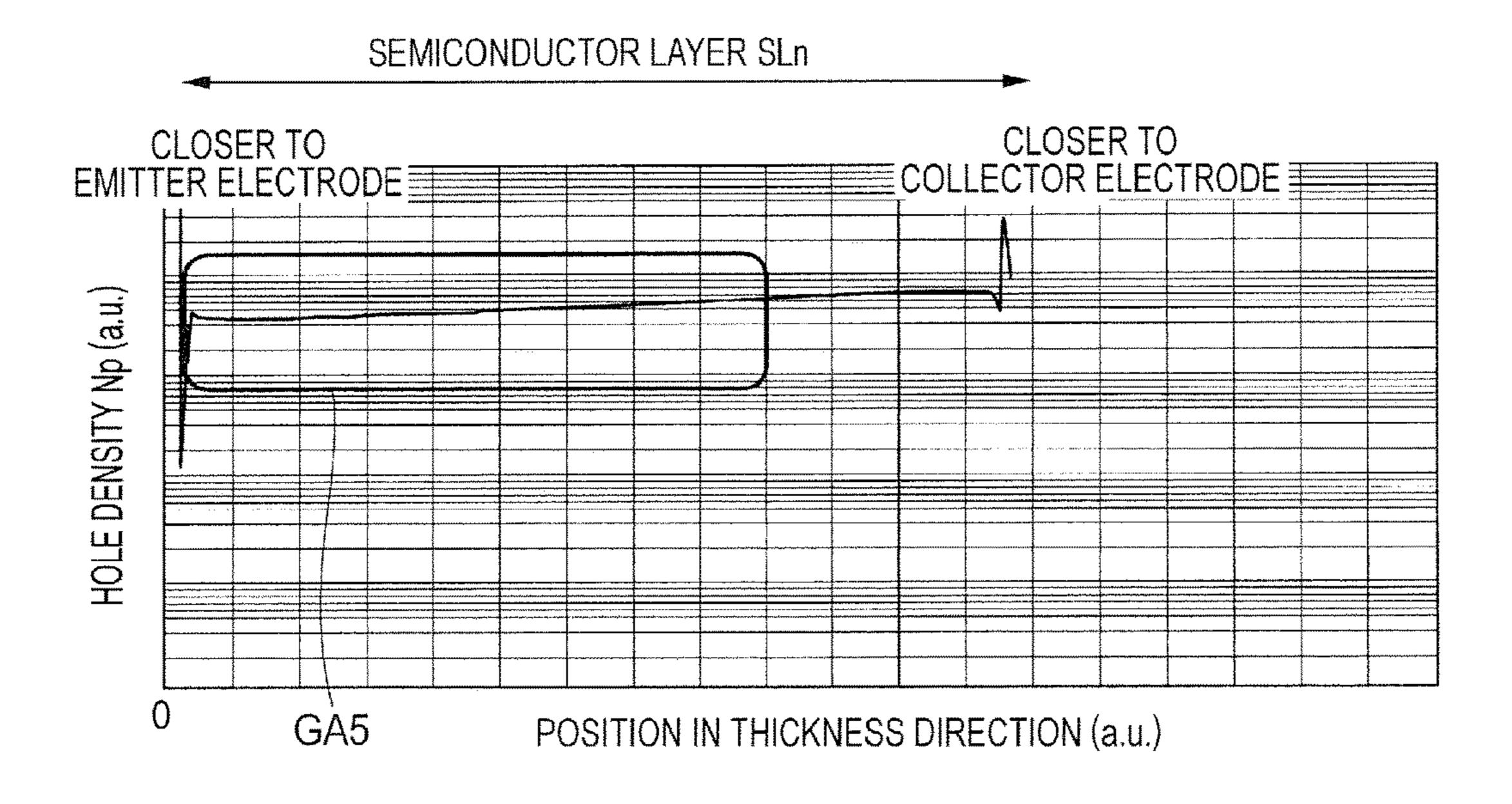

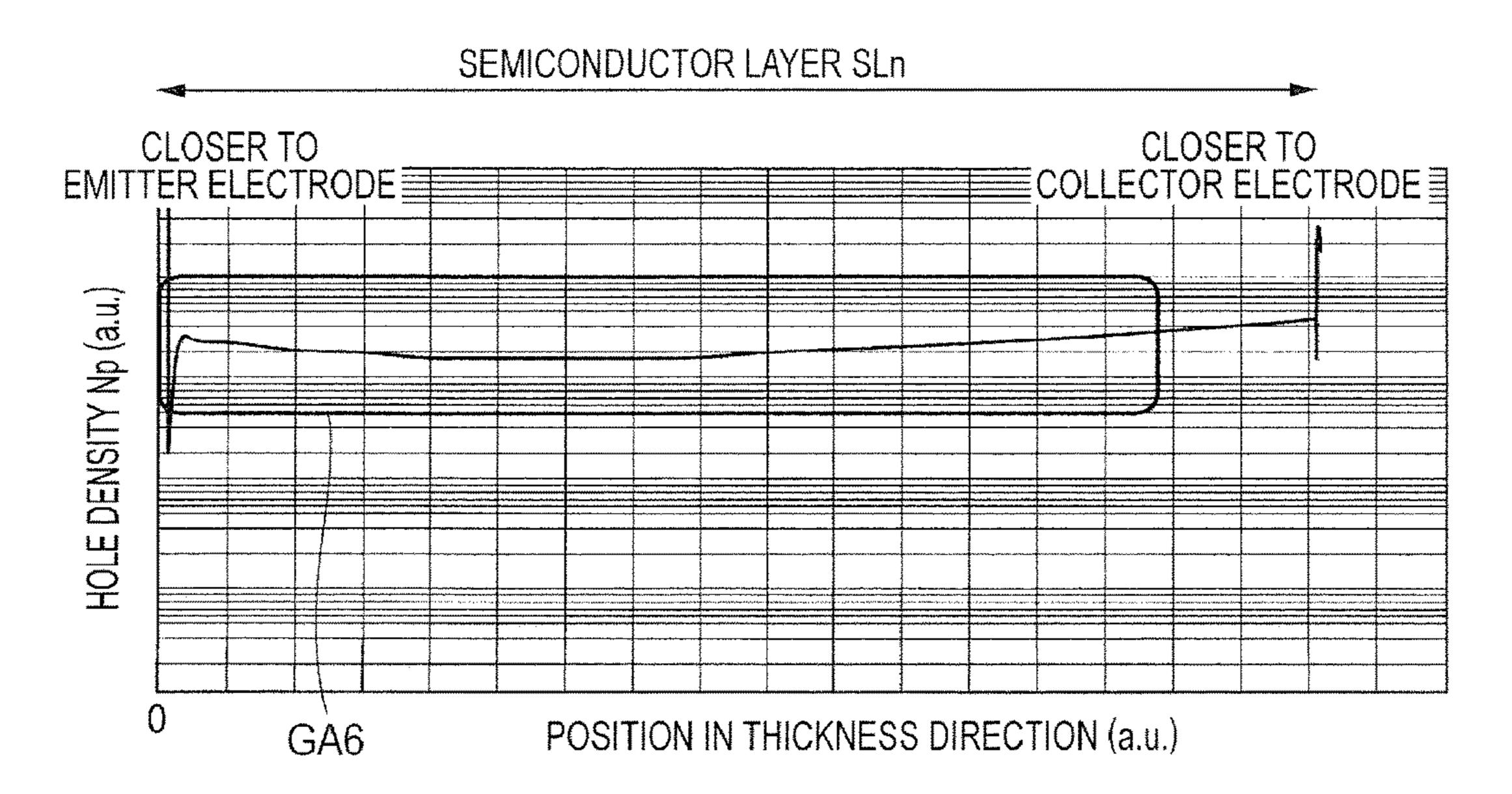

- FIG. **45** is a graph showing a hole density distribution in a thickness direction in the semiconductor device in Comparative Example 2 in the ON state;

- FIG. **46** is a graph showing the hole density distribution in the thickness direction in the semiconductor device in

- FIG. 47 is a graph showing the hole density distribution in the thickness direction in the semiconductor device in Comparative Example 2 in the ON state;

- FIG. 48 is a graph showing a switching waveform when FIG. 25 is a main-portion cross-sectional view of a 60 the semiconductor device in Comparative Example 2 is turned ON;

- FIG. 49 is a graph showing a switching waveform when the semiconductor device in Comparative Example 2 is turned ON;

- FIG. **50** is a cross-sectional view showing a hole density distribution in the semiconductor device in Comparative Example 1 in the ON state;

FIG. **51** is a cross-sectional view showing a hole density distribution in the semiconductor device in Comparative Example 2 in the ON state;

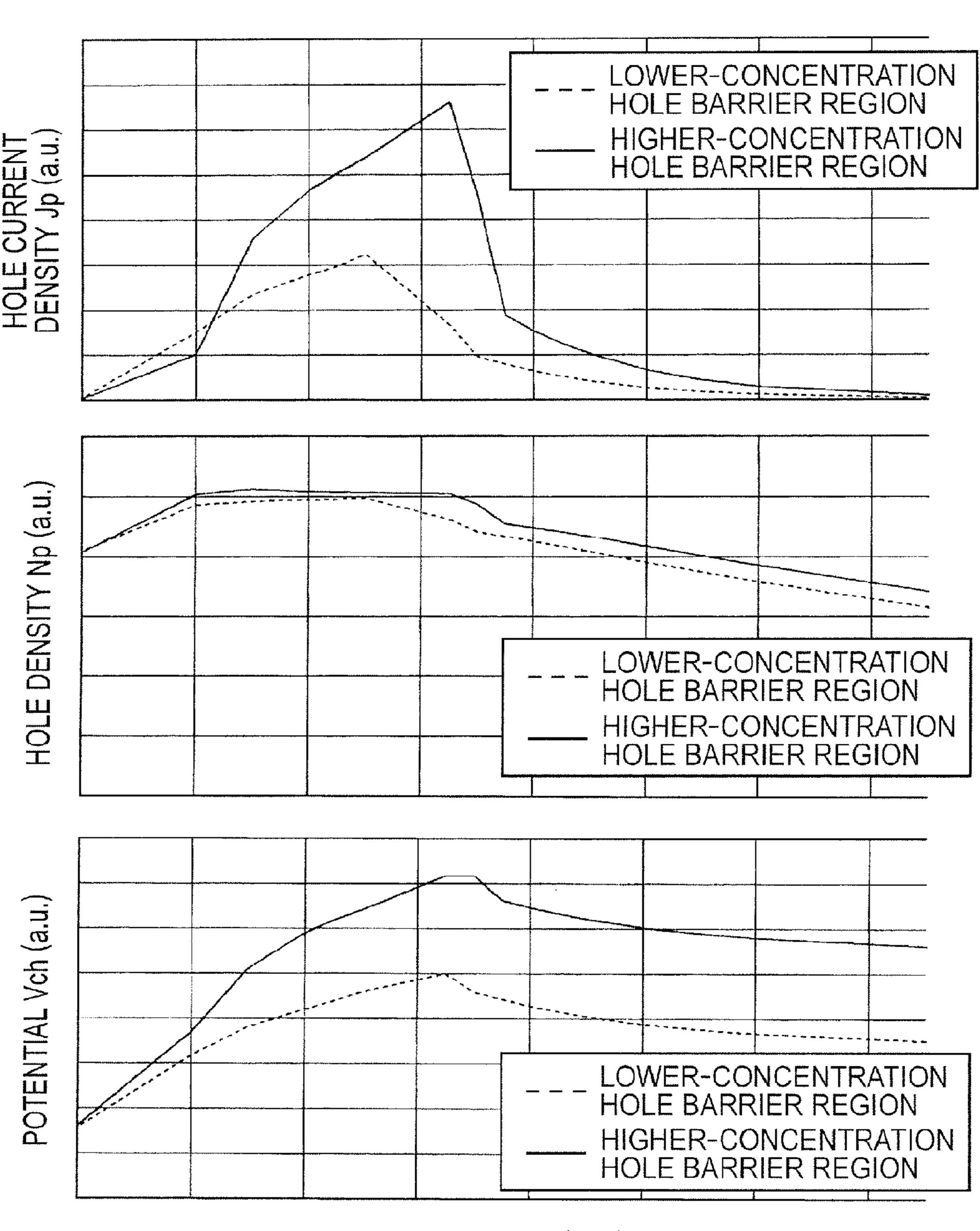

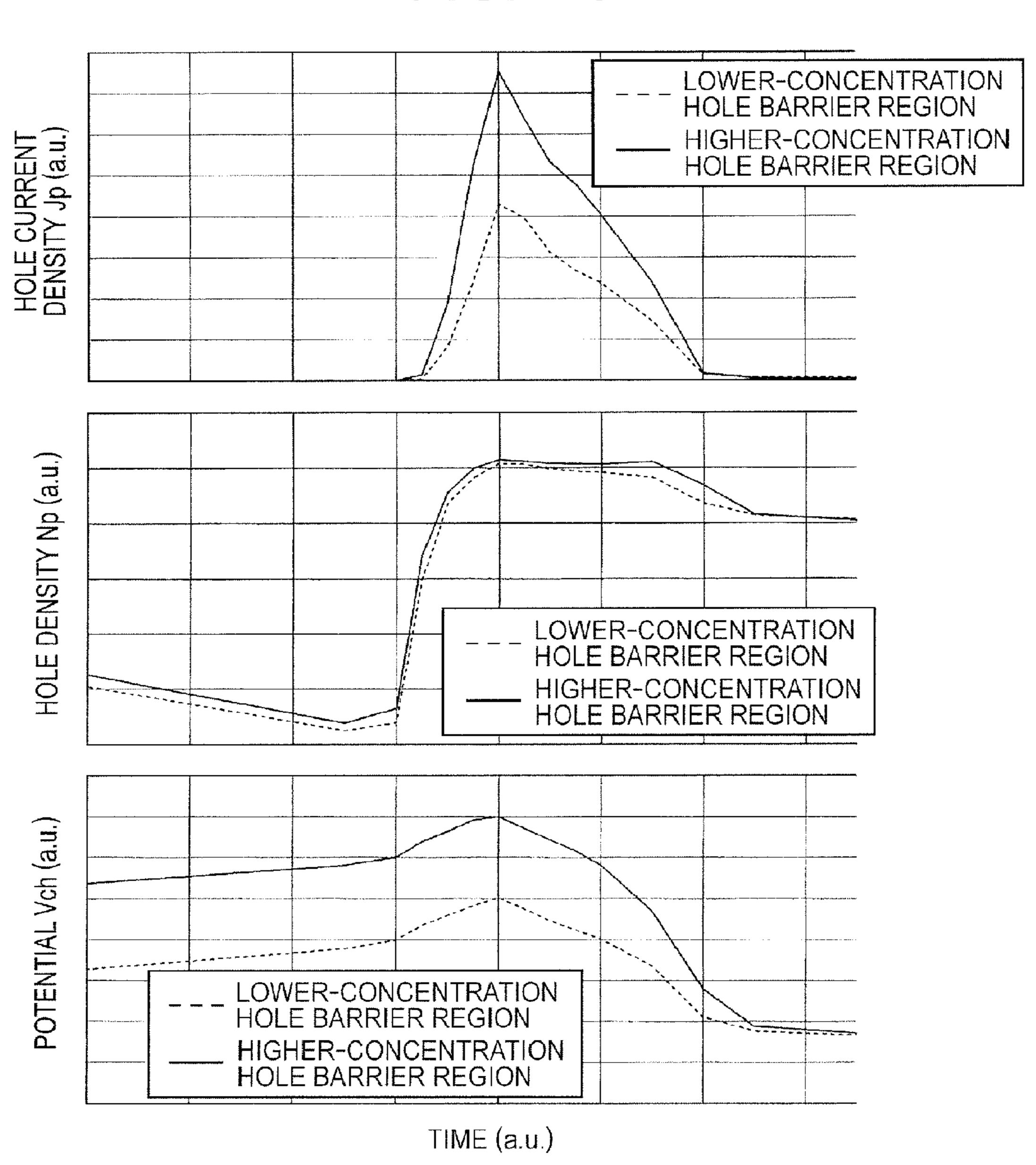

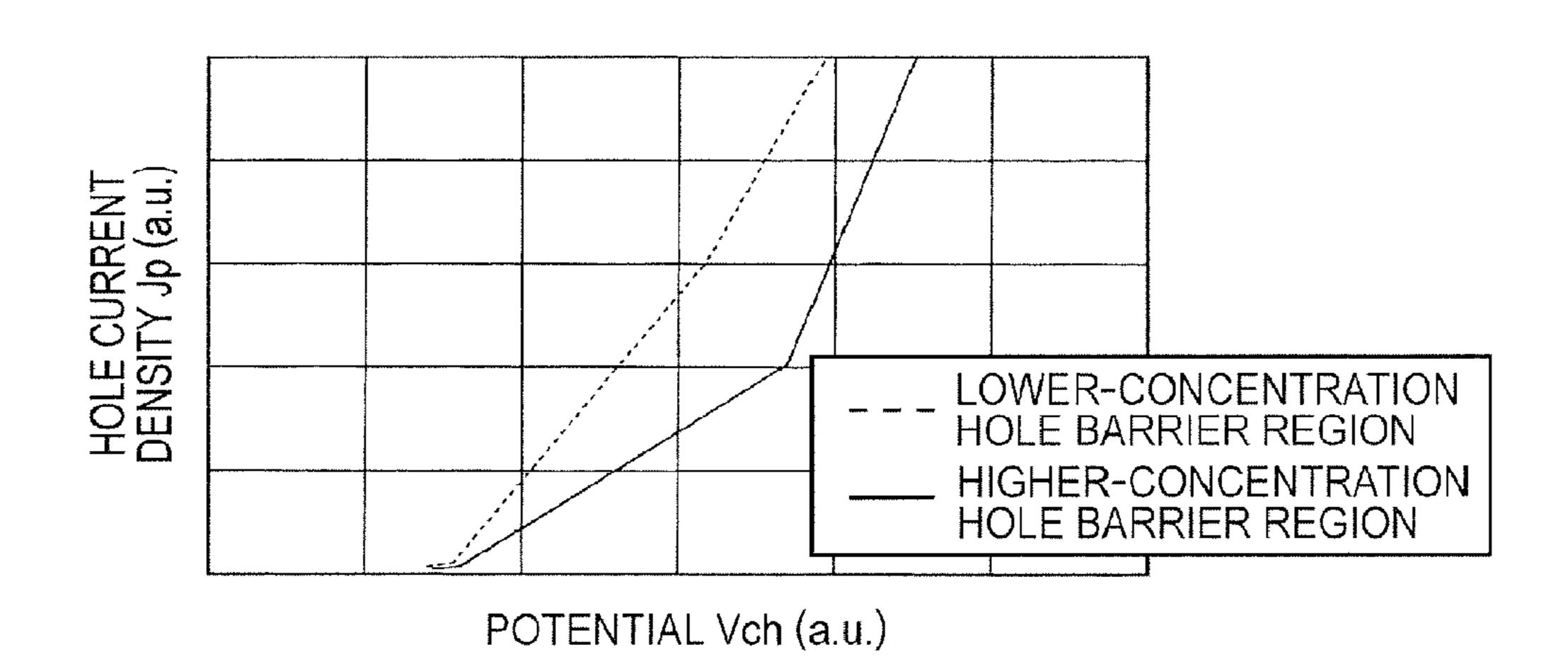

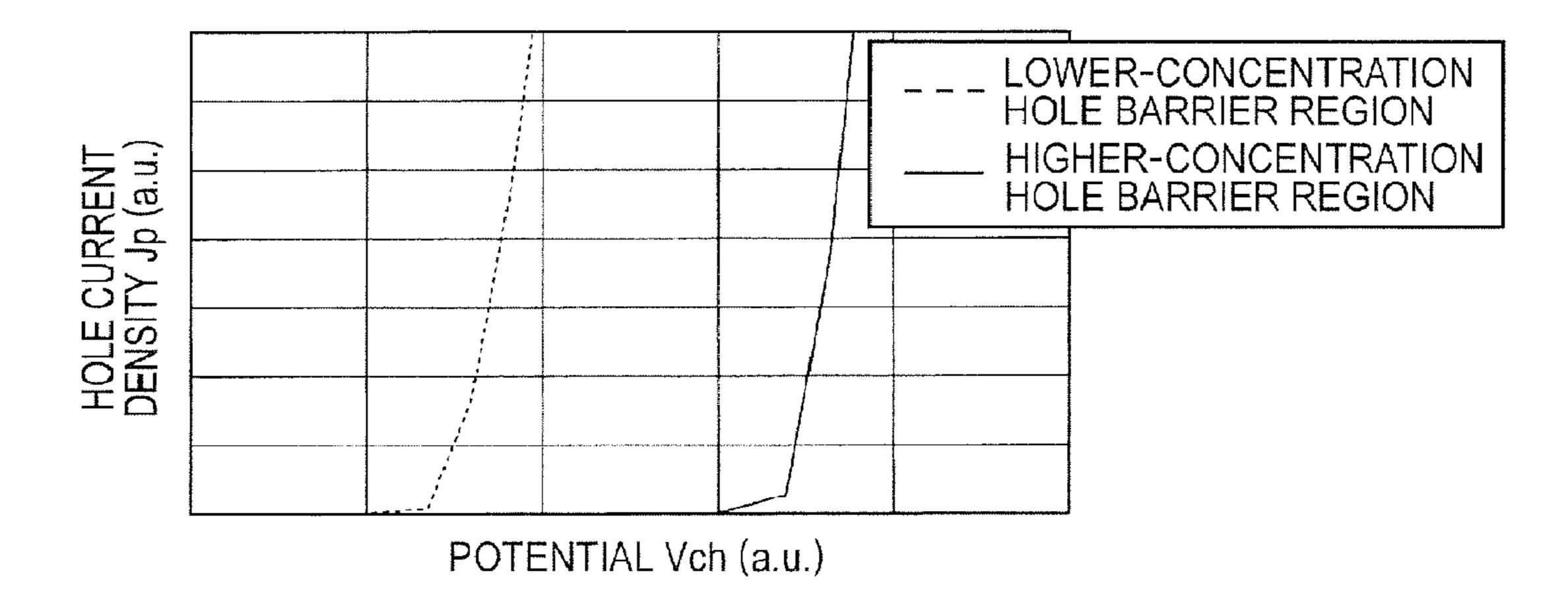

FIG. **52** is a graph showing the potential dependence of a hole current density when the semiconductor device in 5 Comparative Example 2 is turned OFF;

FIG. 53 is a graph showing the potential dependence of the hole current density when the semiconductor device in Comparative Example 2 is turned ON;

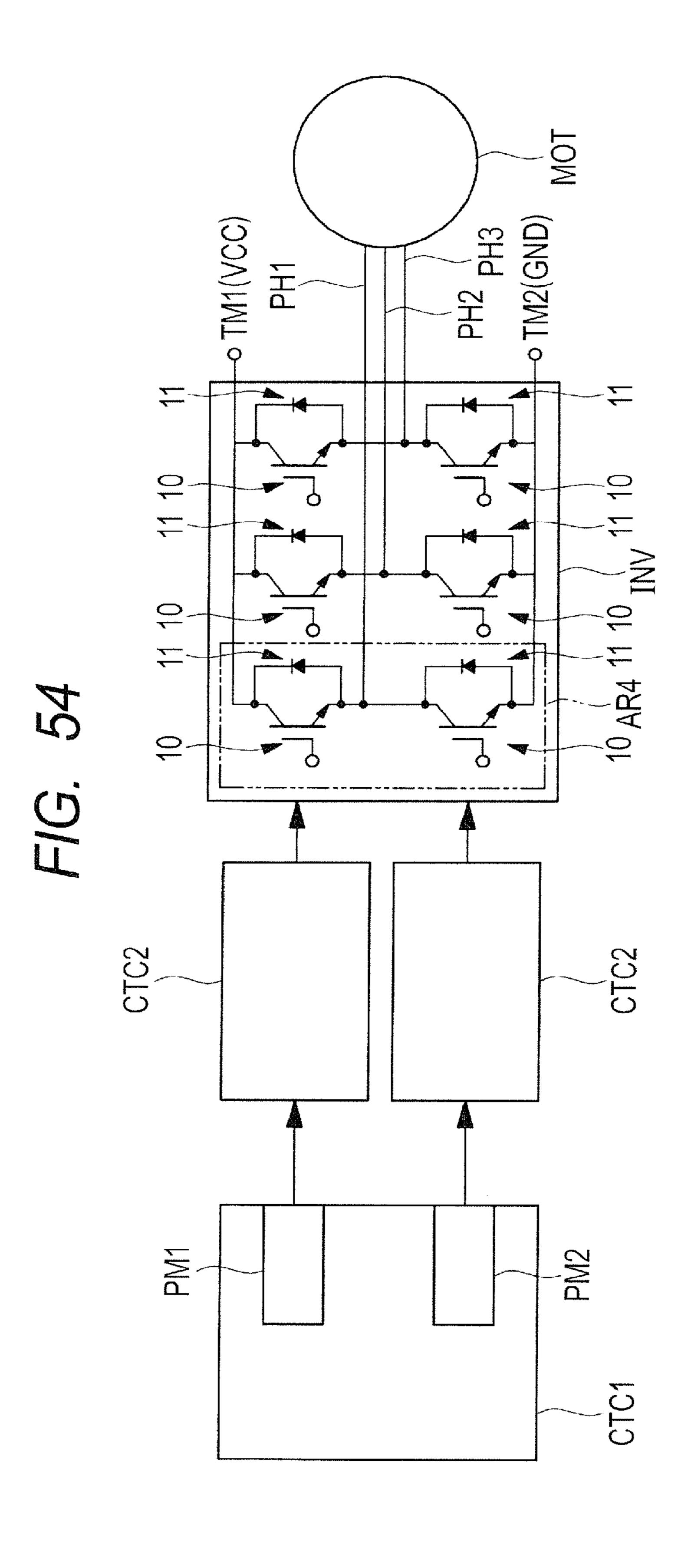

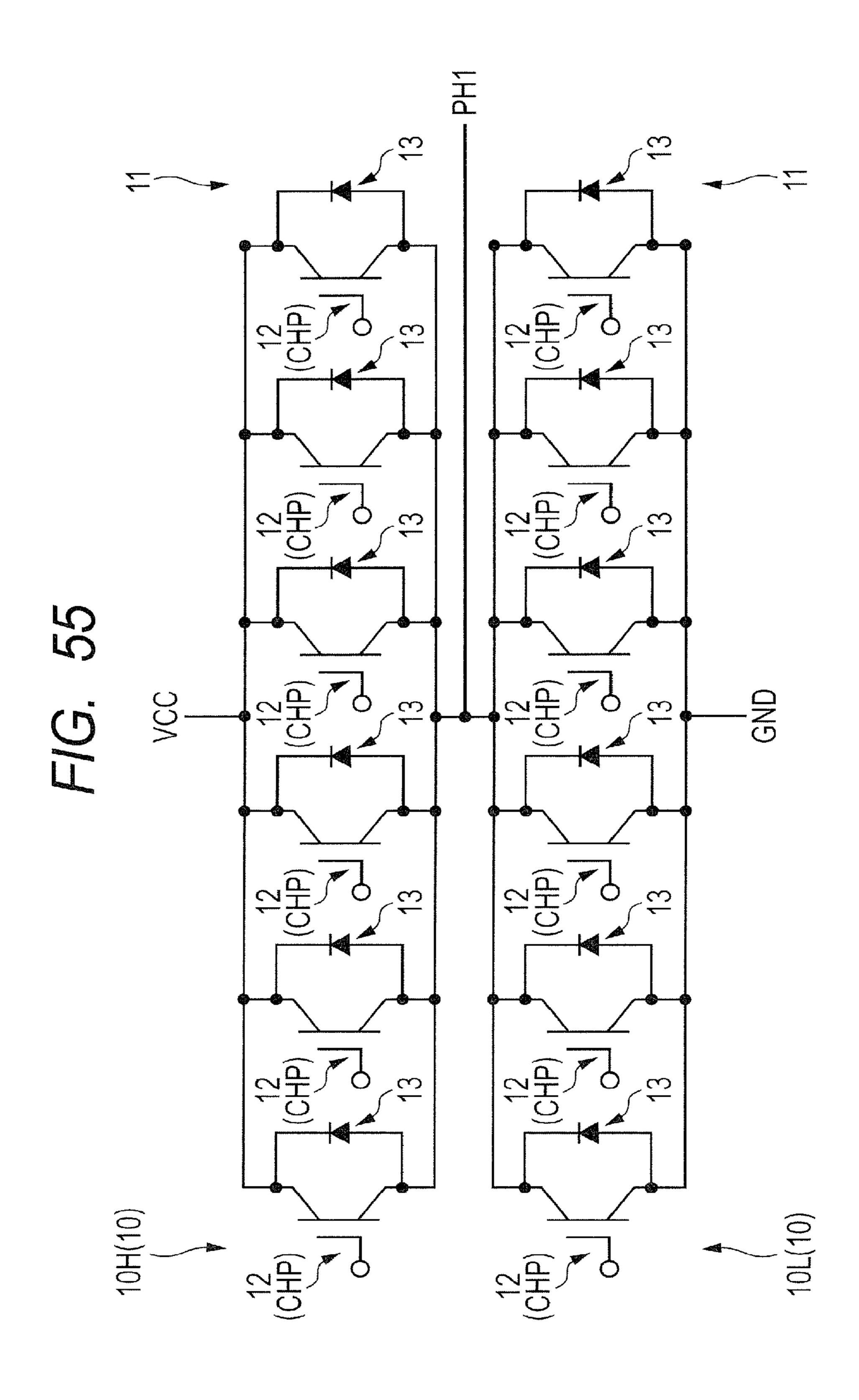

FIG. **54** is a circuit block diagram showing an example of 10 an electronic system in which a semiconductor device in Embodiment 2 is used;

FIG. 55 is an equivalent circuit diagram showing a module as the semiconductor device in Embodiment 2;

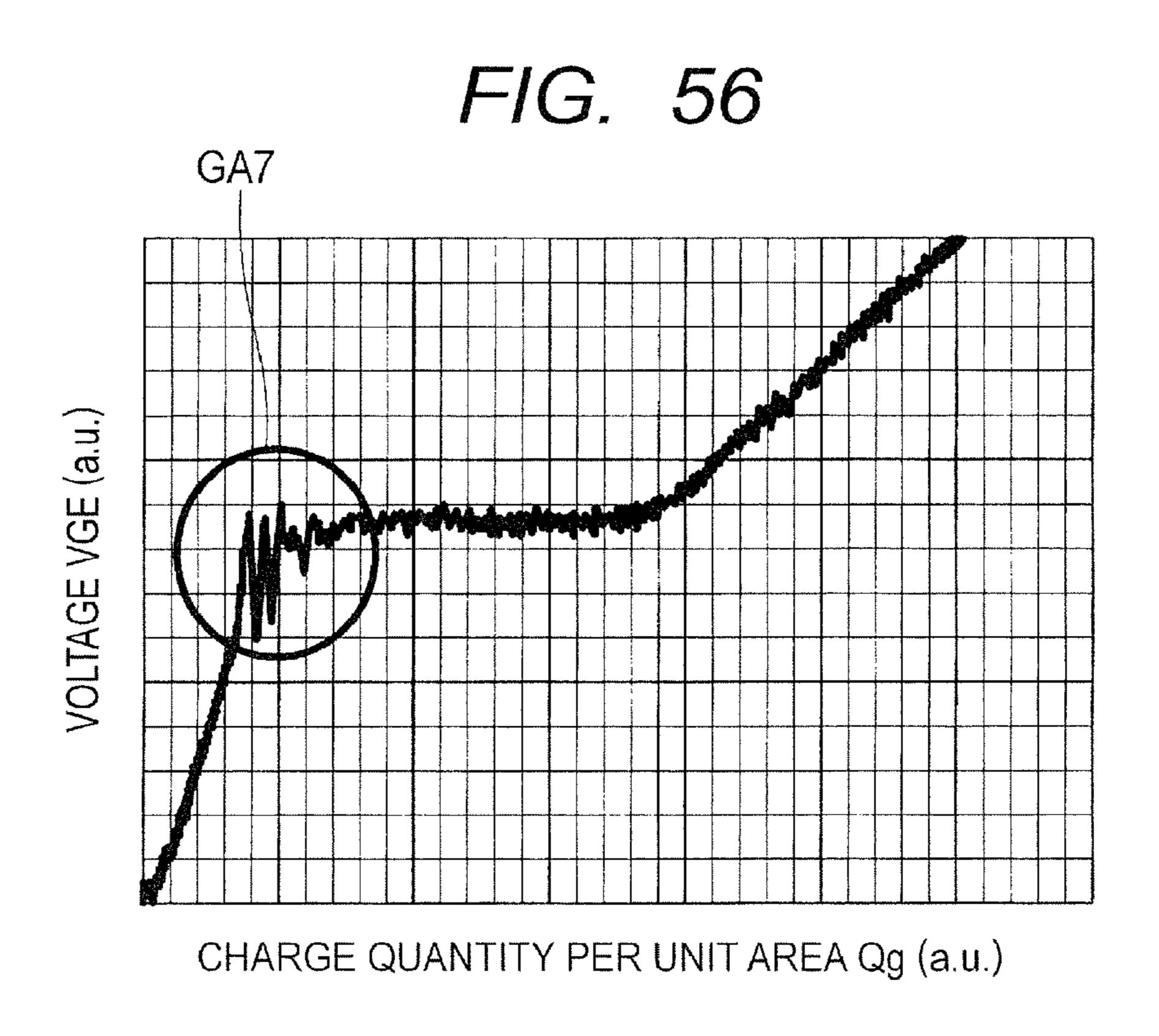

FIG. **56** is a graph showing the gate charge quantity 15 dependence of a gate-emitter voltage in a semiconductor device in Comparative Example 3;

FIG. 57 is a graph showing the gate charge quantity dependence of a gate-emitter electrode in the semiconductor device in Embodiment 2;

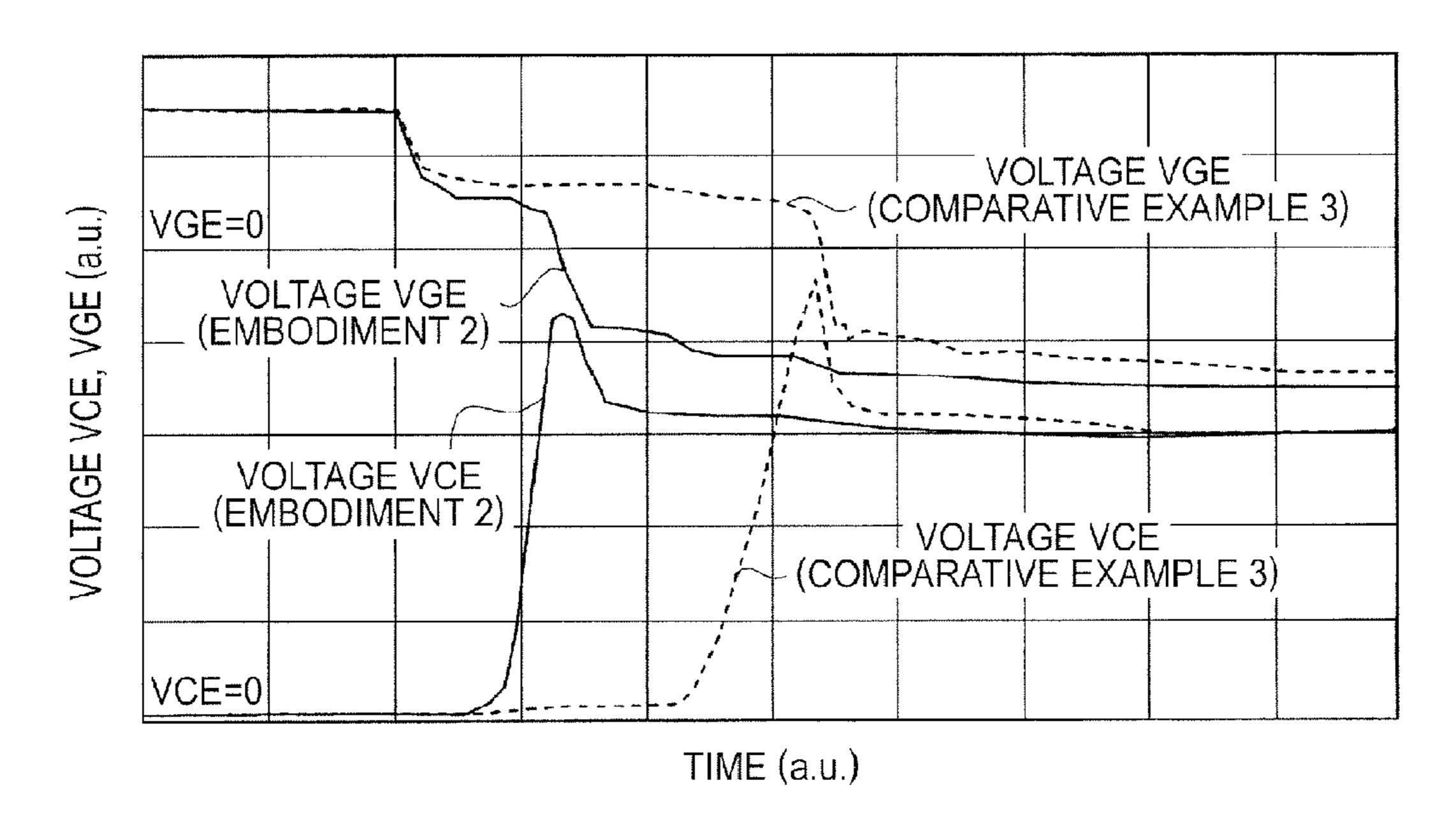

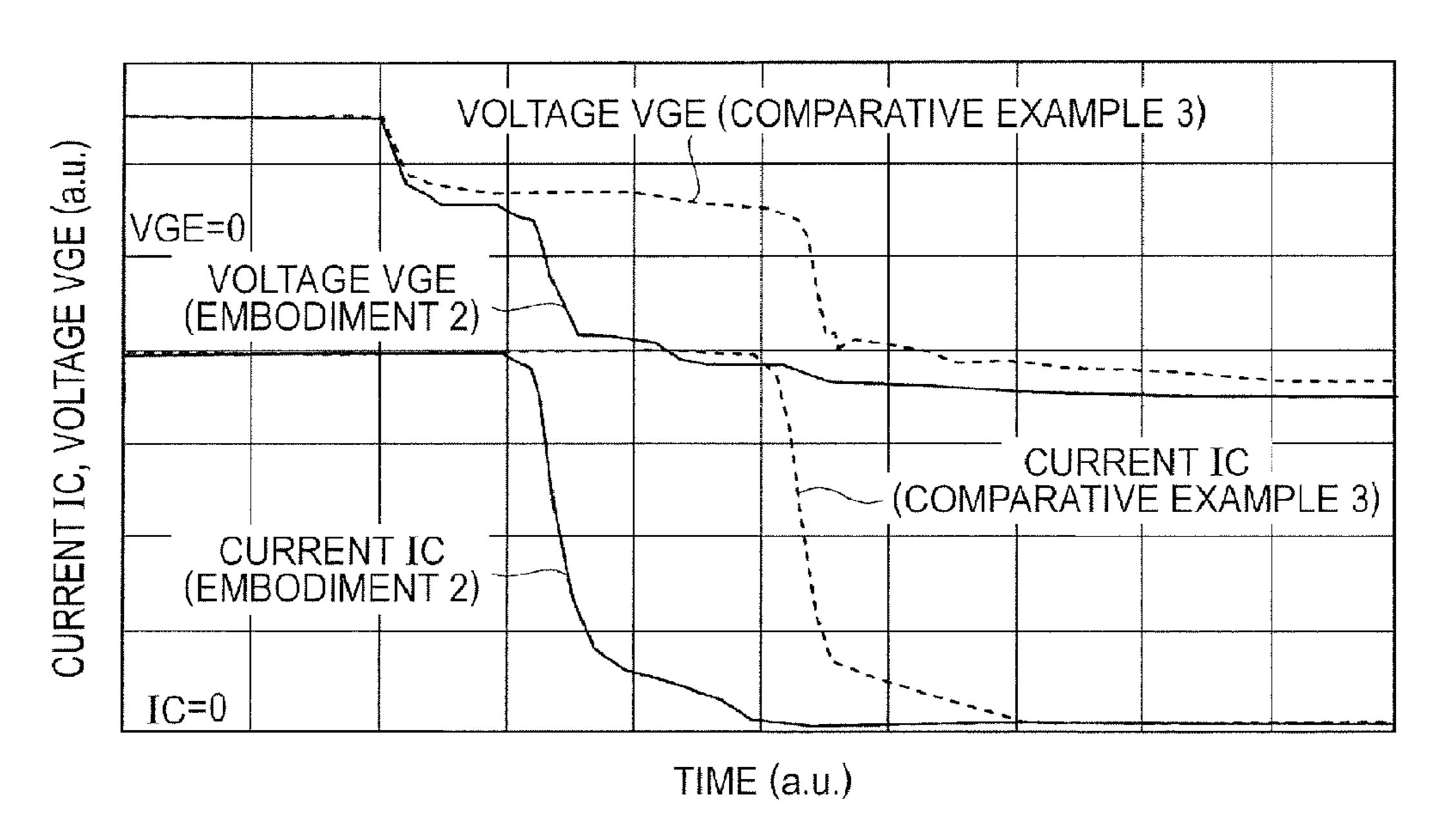

FIG. **58** is a graph showing switching waveforms when the semiconductor device in Comparative Example 3 and the semiconductor device in Embodiment 2 are turned OFF by L-load switching;

FIG. **59** is a graph showing switching waveforms when 25 the semiconductor device in Comparative Example 3 and the semiconductor device in Embodiment 2 are turned OFF by L-load switching;

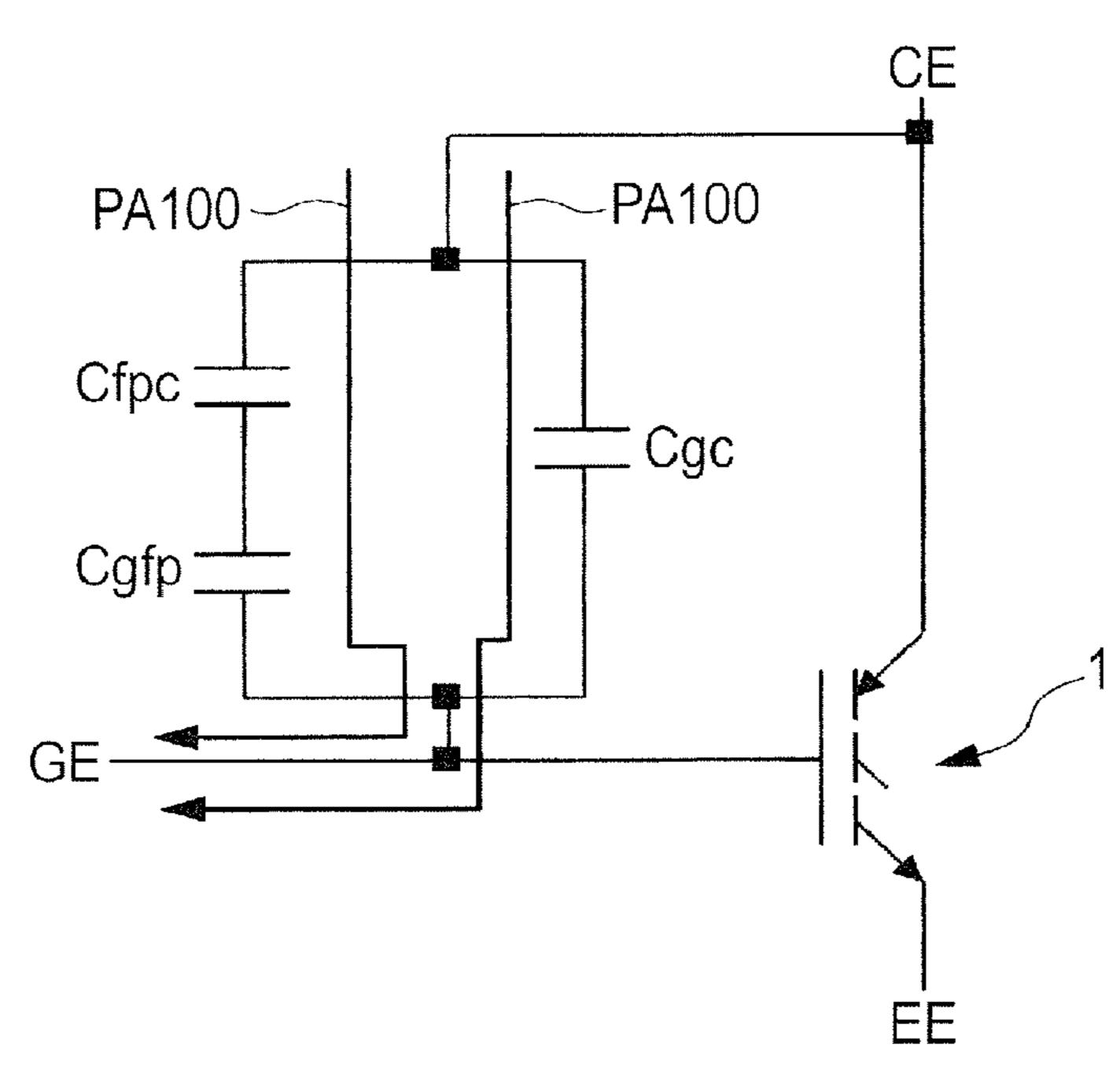

FIG. **60** is an equivalent circuit diagram showing a pseudo device model of each of the IGBT chips included in the 30 semiconductor device in Comparative Example 3;

FIG. **61** is an equivalent circuit diagram showing a pseudo device model of each of the IGBT chips included in the semiconductor device in Embodiment 2;

FIG. **62** is a circuit diagram for circuit simulation in each <sup>35</sup> improved clarity of illustration. of the semiconductor devices in Comparative Example 3 and Embodiment 2;

FIG. 63 is a graph showing the result of the circuit simulation in the semiconductor device in Comparative Example 3;

FIG. **64** is a graph showing the result of the circuit simulation in the semiconductor device in Embodiment 2;

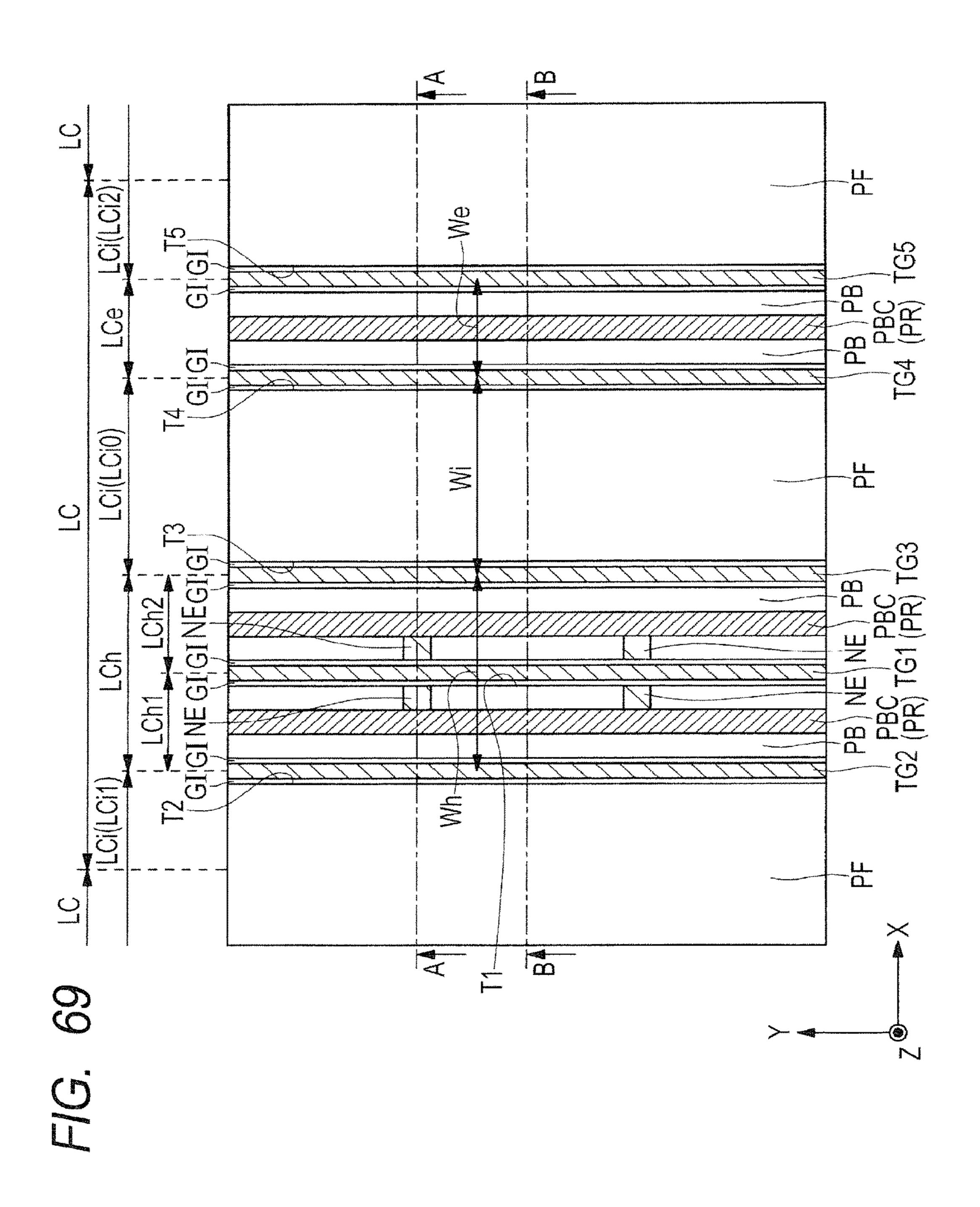

FIG. **65** is a main-portion plan view of a semiconductor device in Embodiment 3;

FIG. 66 is a main-portion cross-sectional view of the 45 semiconductor device in Embodiment 3;

FIG. 67 is a main-portion plan view of a semiconductor device in a modification of Embodiment 3;

FIG. 68 is a main-portion cross-sectional view of the semiconductor device in the modification of Embodiment 3; 50

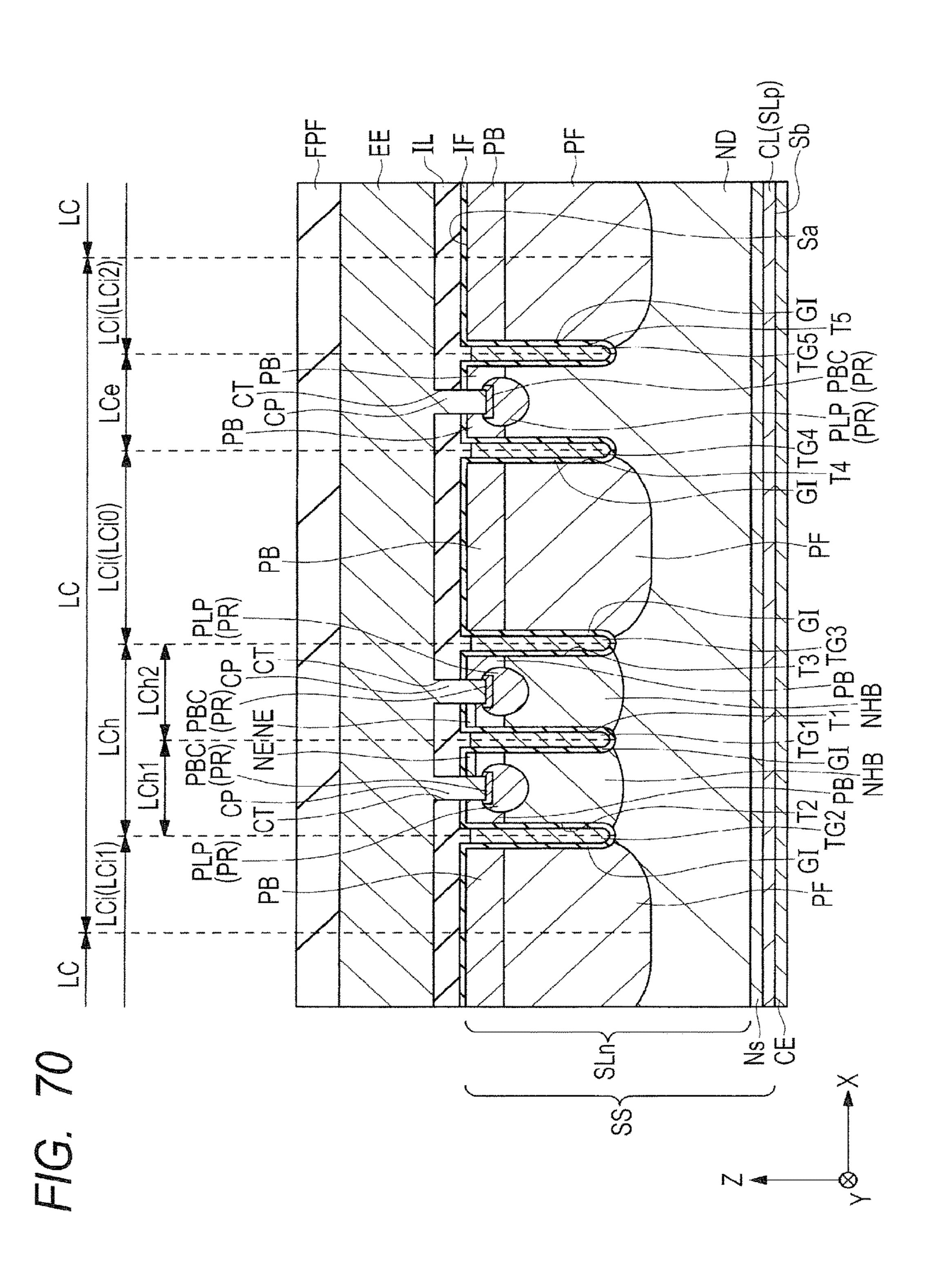

FIG. 69 is a main-portion plan view of a semiconductor

device in Embodiment 4; FIG. 70 is a main-portion cross-sectional view of the

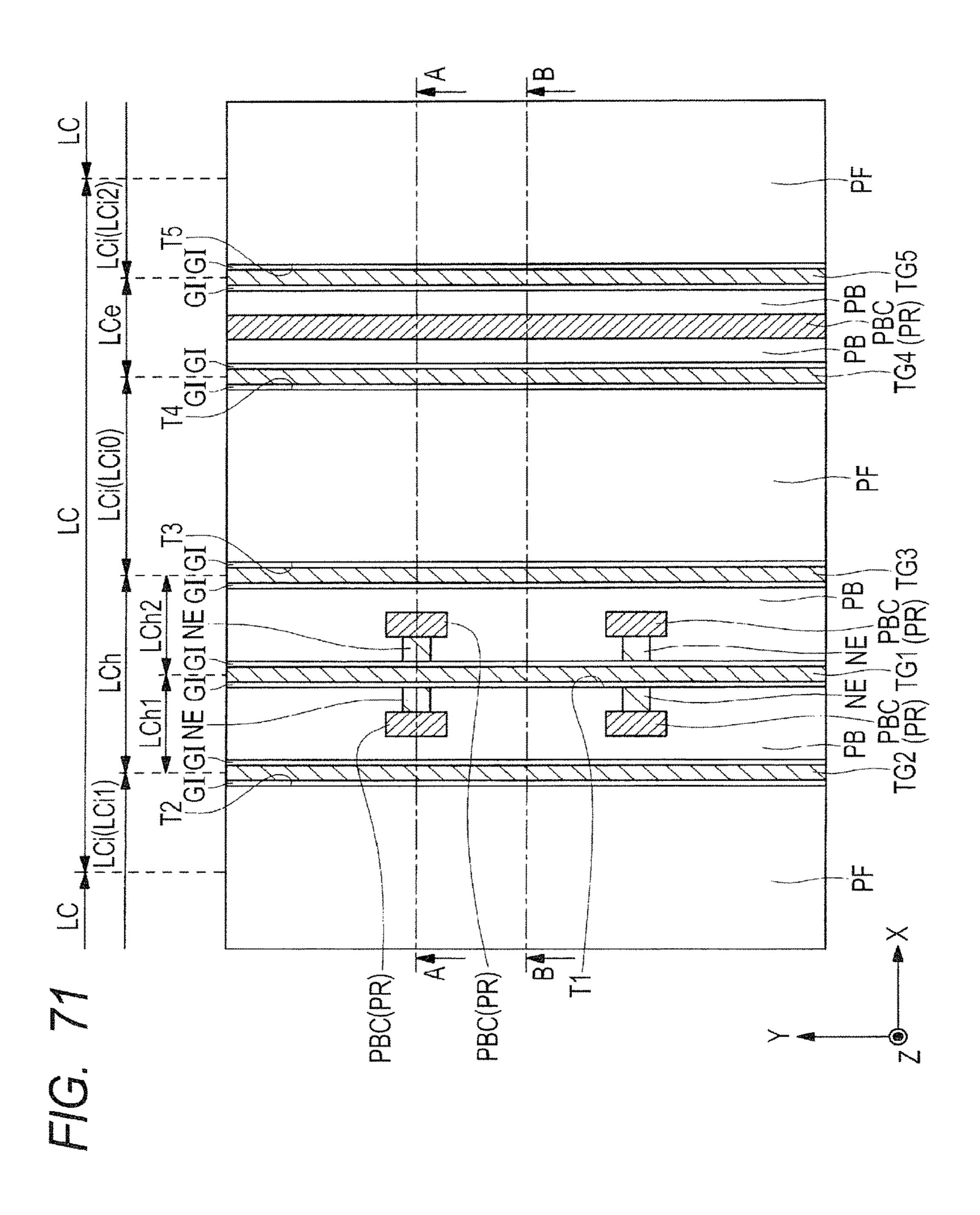

semiconductor device in Embodiment 4; FIG. 71 is a main-portion plan view of a semiconductor 55

device in a modification of Embodiment 4; and

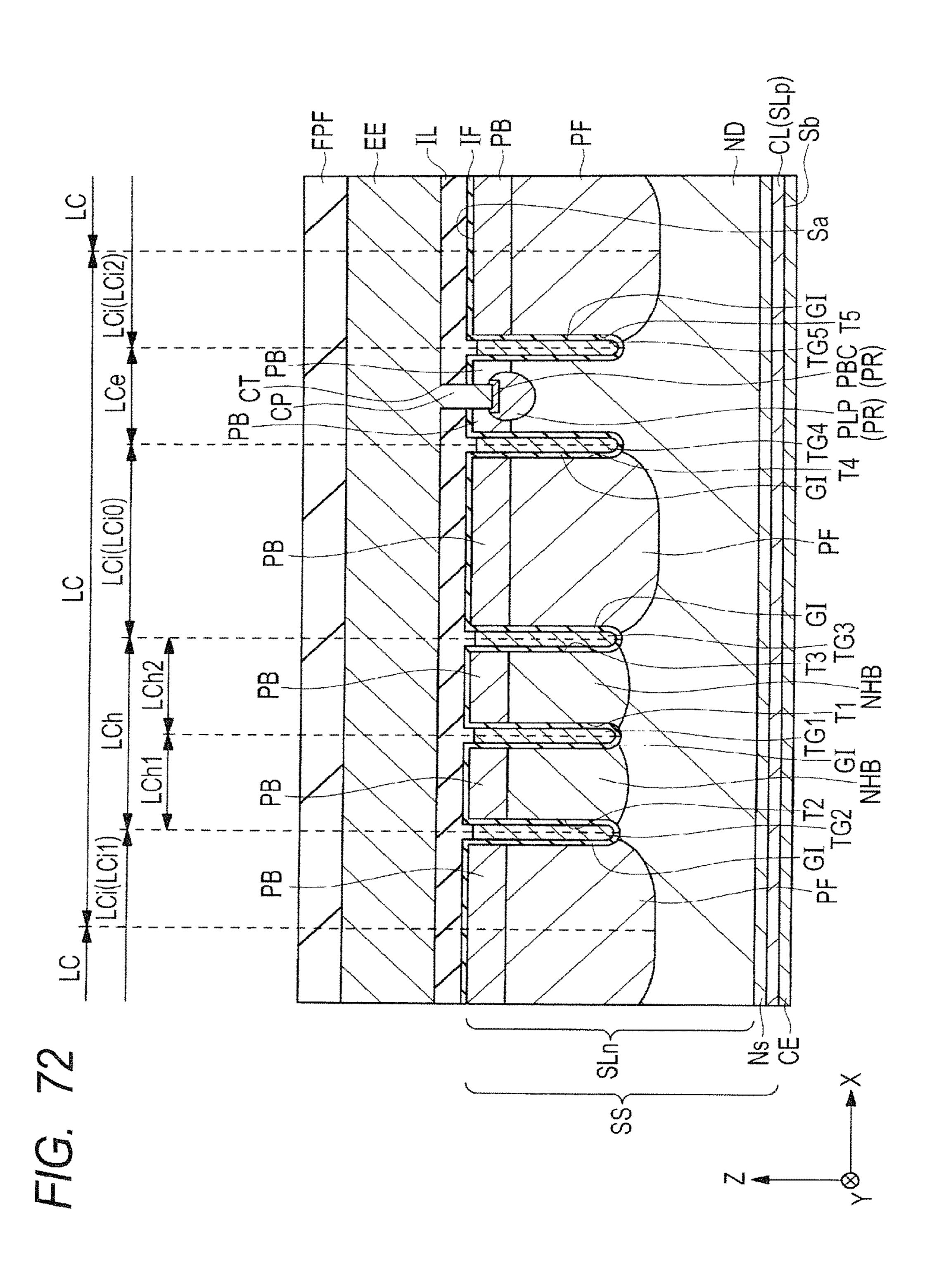

FIG. 72 is a main-portion cross-sectional view of the semiconductor device in the modification of Embodiment 4.

## DETAILED DESCRIPTION

In the following embodiments, if necessary for the sake of convenience, the embodiments will be each described by being divided into a plurality of sections or embodiments. However, they are by no means irrelevant to each other 65 unless particularly explicitly described otherwise, but are in relations such that one of the sections or embodiments is a

modification, details, supplementary explanation, and so forth of part or the whole of the others.

Also, in the following embodiments, when the number and the like (including the number, numerical value, amount, range, and the like) of elements are mentioned, they are not limited to specific numbers unless particularly explicitly described otherwise or unless they are obviously limited to specific numbers in principle. The number and the like of the elements may be not less than or not more than specific numbers.

Also, in the following embodiments, it goes without saying that the components thereof (including also elements, steps, and the like) are not necessarily indispensable unless particularly explicitly described otherwise or unless the components are considered to be obviously indispensable in principle. Likewise, if the shapes, positional relationships, and the like of the components and the like are mentioned in the following embodiments, the shapes and the like are assumed to include those substantially proximate or similar 20 thereto and the like unless particularly explicitly described otherwise or unless it can be considered that they obviously do not in principle. The same shall apply in regard to the foregoing numerical value and range.

The following will describe representative embodiments in detail on the basis of the drawings. Note that, throughout all the drawings for illustrating the embodiments, members having the same functions are designated by the same reference numerals, and a repeated description thereof is omitted. In the following embodiments, a description of the same or like parts will not be repeated in principle unless particularly necessary.

In the drawings used in the embodiments, hatching may be omitted even in a cross section for improved clarity of illustration, while even a plan view may be hatched for

### Embodiment 1

A detailed description will be given below of a semicon-40 ductor device in Embodiment 1 with reference to the drawings. The semiconductor device in Embodiment 1 includes an IGBT having an EGE-type (emitter-gate-emitter-type) active cell region. Note that the possession of the EGE-type active cell region by the IGBT means that, among three trench gate electrodes arranged in the active cell region to be spaced apart from each other, the trench gate electrode located in the middle is electrically coupled to a gate electrode and each of the two trench gate electrodes located at both ends is electrically coupled to an emitter electrode.

<Configuration of Semiconductor Device>

First, a description will be given of a configuration of a semiconductor chip as the semiconductor device in Embodiment 1.

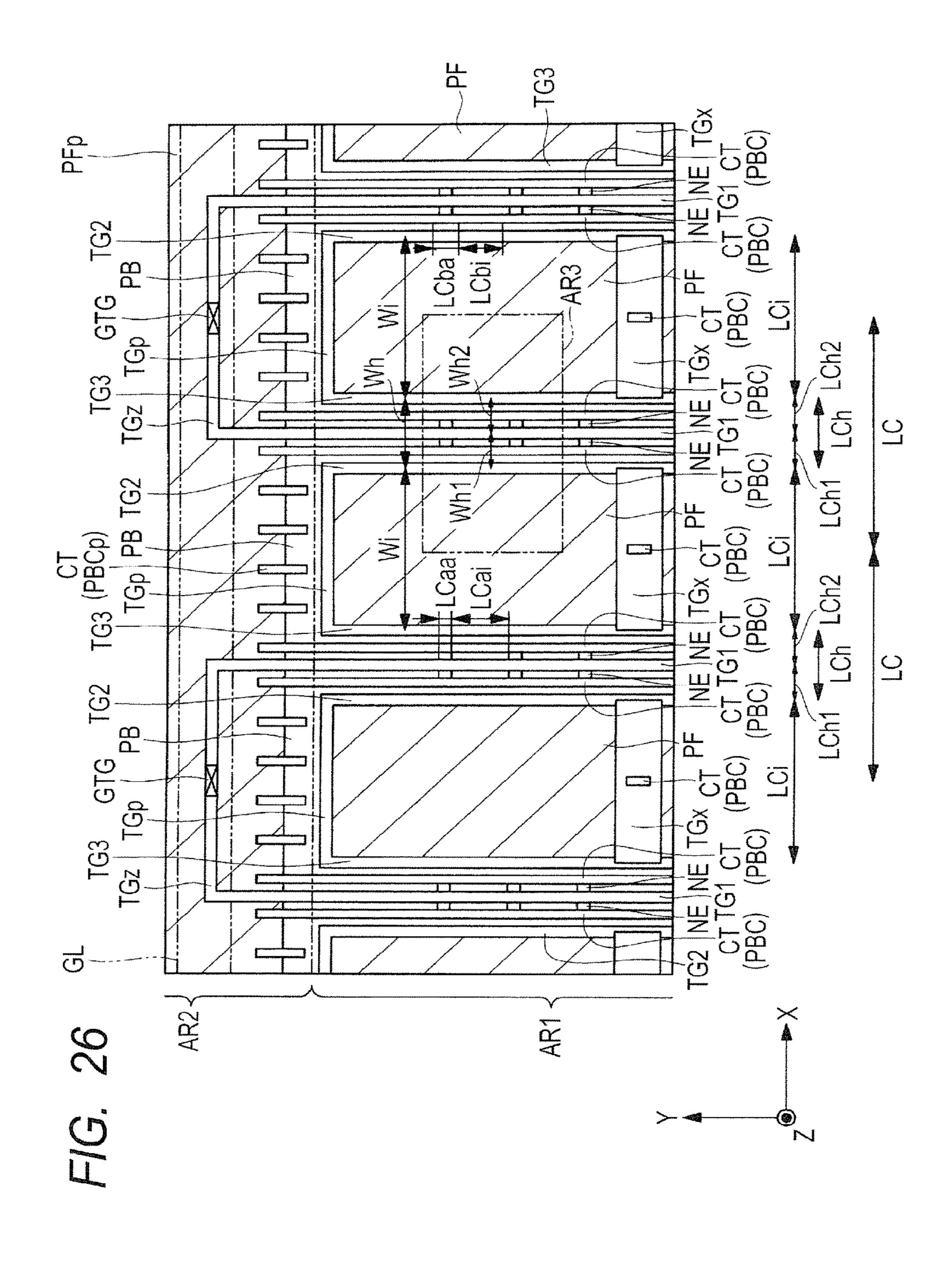

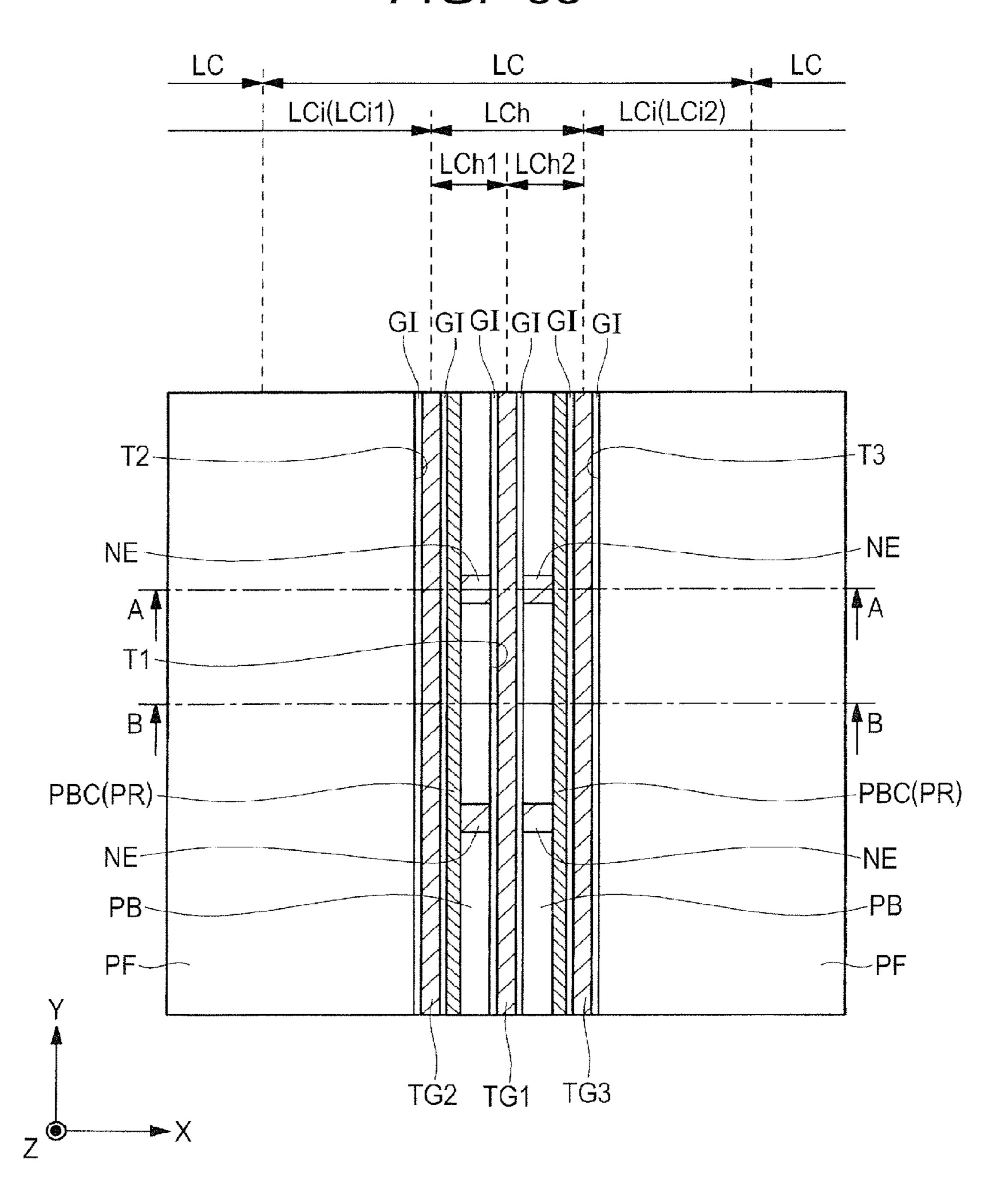

FIG. 1 is a plan view of the semiconductor chip as the semiconductor device in Embodiment 1. FIGS. 2 and 3 are main-portion plan views of the semiconductor device in Embodiment 1. FIGS. 4 to 6 are main-portion cross-sectional views of the semiconductor device in Embodiment 1. FIG. 3 shows an area AR3 enclosed by the two-dot-dash line in FIG. 2. FIG. 4 is a cross-sectional view along the line A-A in FIG. 3. FIG. 5 is a cross-sectional view along the line B-B in FIG. 3. FIG. 6 is a cross-sectional view along the line C-C in FIG. **3**.

Note that, for easier understanding, FIG. 1 shows the semiconductor device in Embodiment 1 in a see-through state where an insulating film FPF (see FIG. 4) has been removed and shows the respective outer peripheries of a cell

formation area AR1, an emitter pad EP, and a gate pad GP by the two-dot-dash lines. Also, for easier understanding, FIG. 2 shows the semiconductor device in Embodiment 1 in a see-through state where the insulating film FPF, a gate wire GL, an emitter electrode EE, an interlayer insulating film IL, and the portion of a p-type body region PB (see FIG. 4) which is formed over a p-type floating region PR have been removed and shows the respective outer peripheries of the cell formation area AR1 and the gate wire GL by the two-dot-dash lines.

As shown in FIG. 1, the semiconductor chip CHP as the semiconductor device in Embodiment 1 has a semiconductor substrate SS. The semiconductor substrate has an upper surface Sb (see FIG. 4) as the other main surface opposite to the upper surface. The semiconductor substrate SS also has the cell formation area AR1 as a local area of the upper surface Sa and a gate-wire-lead-out area AR2 as another local area of the upper surface Sa. The gate-wire-lead-out 20 area AR2 is provided closer to, e.g., the outer periphery of the semiconductor substrate SS than the cell formation area AR1.

In the cell formation area AR1, the emitter electrode EE is provided. The center portion of the emitter electrode EE 25 serves as the emitter pad EP to which bonding wires or the like are to be coupled. The emitter pad EP is made of the portion of the emitter electrode EE which is exposed from an opening OP1 formed in the insulating film FPF (see FIG. 4) formed so as to cover the emitter electrode EE. The emitter 30 electrode EE is made of a metal film containing, e.g., aluminum as a main component.

In the gate-wire-lead-out area AR2, the gate wire GL and a gate electrode GE are provided. The gate wire GL is provided closer to, e.g., the outer periphery of the semiconductor substrate SS than the emitter electrode EE. The gate wire GL is coupled to the gate electrode GE. The center portion of the gate electrode GE serves as the gate pad GP to which bonding wires or the like are to be coupled. The gate pad GP is made of the portion of the gate electrode GE 40 which is exposed from an opening OP2 formed in the insulating film FPF (see FIG. 4) formed so as to cover the gate electrode GE. Each of the gate wire GL and the gate electrode GE is made of a metal film containing, e.g., aluminum as a main component.

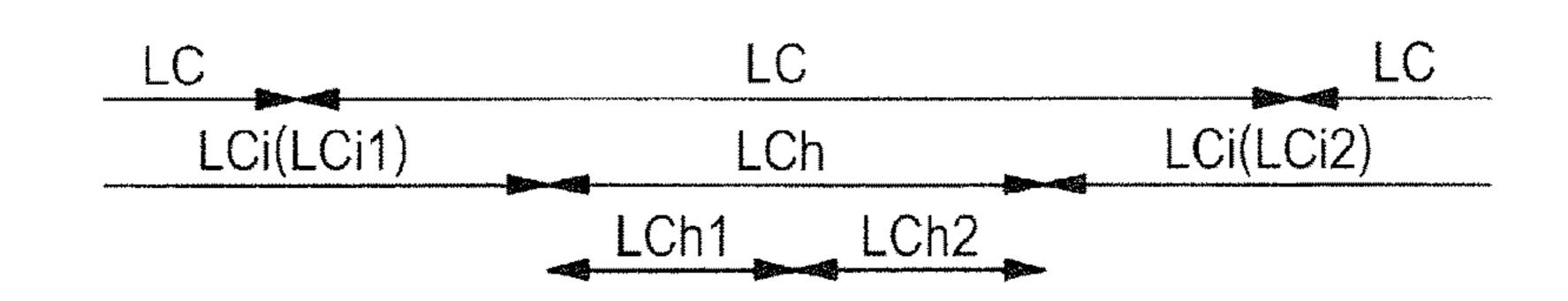

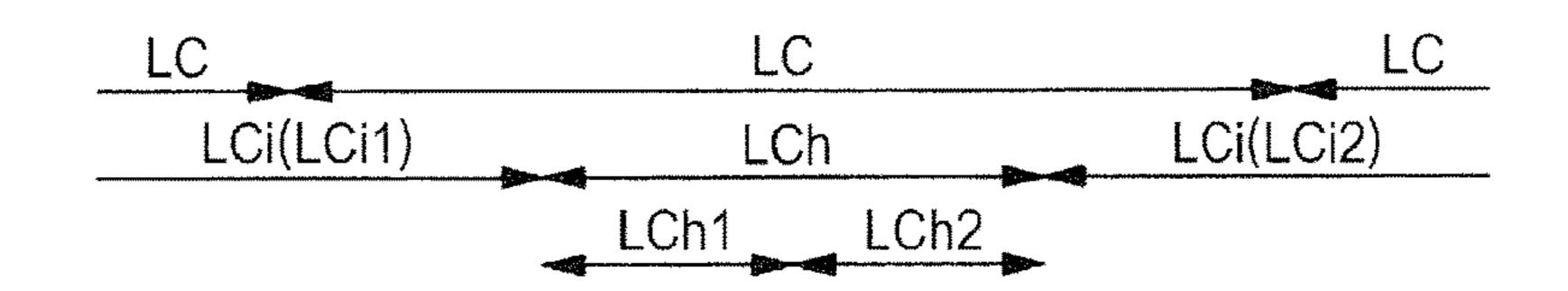

As shown in FIGS. 1 to 6, two directions crossing each other, or preferably orthogonal to each other in the upper surface of the semiconductor substrate SS are assumed to be an X-axis direction and a Y-axis direction and a direction perpendicular to the upper surface of the semiconductor 50 substrate SS, i.e., vertical direction is assumed to be a Z-axis direction. At this time, in the cell formation area AR1, as shown in FIG. 2, a plurality of unit cell regions LC are provided. In plan view, the plurality of unit cell regions LC extend in the Y-axis direction and are periodically arranged 55 in the X-axis direction.

Note that, in the present specification, the wording "in plan view" means that an object is viewed from a direction perpendicular to the upper surface Sa of the semiconductor substrate SS.

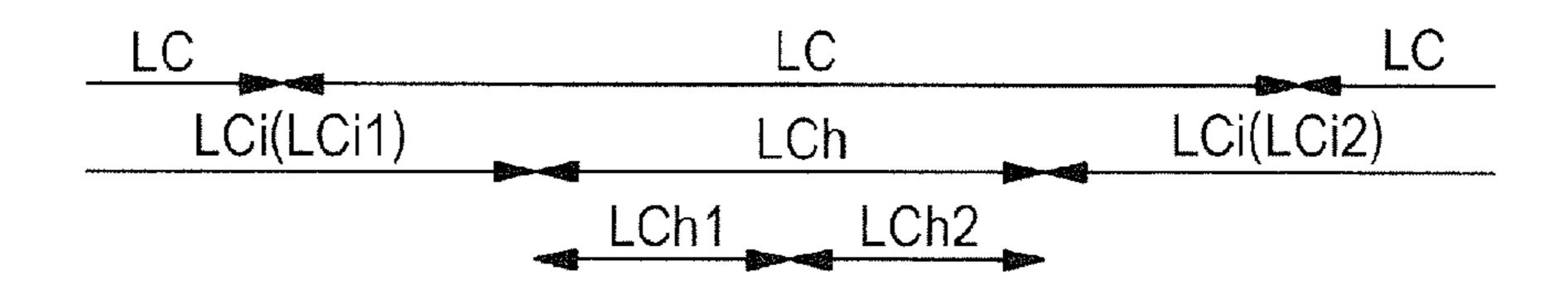

Each of the unit cell regions LC includes a hybrid cell region LCh as an EGE-type active cell region and two inactive cell regions LCi. The two inactive cell regions LCi are located on both sides of the hybrid cell region LCh interposed therebetween in the X-axis direction. Each of the 65 hybrid cell region LCh and the two inactive cell regions LCi extends in the Y-axis direction in plan view. Preferably, the

8

hybrid cell region LCh has a width Wh smaller than a width Wi of each of the inactive cell regions LCi.

The two unit cell regions LC adjacent to each other in the X-axis direction share one of the inactive cell regions LCi. Accordingly, each of the unit cell regions LC has a positive half portion LCi1 of the inactive cell region LCi which is located on the negative side of the hybrid cell region LCh in the X-axis direction to be adjacent thereto. The unit cell region LC also has a negative half portion LCi2 of the inactive cell region LCi which is located on the positive side of the hybrid cell region LCh in the X-axis direction to be adjacent thereto.

The hybrid cell region LCh includes hybrid sub-cell surface Sa (see FIG. 4) as one main surface and a lower 15 regions LCh1 and LCh2. The hybrid cell region LCh also includes a trench gate electrode TG1 located at a boundary surface between the hybrid sub-cell regions LCh1 and LCh2.

> The trench gate electrode TG1 is provided in the middle of the hybrid cell region LCh. This allows a width Wh1 of the hybrid sub-cell region LCh1 and a width Wh2 of the hybrid sub-cell region LCh2 to be equal and allows the hybrid sub-cell regions LCh1 and LCh2 to be arranged symmetrically relative to the trench gate electrode TG1.

> The hybrid cell region LCh has trench gate electrodes TG2 and TG3. The trench gate electrode TG2 is located between the hybrid sub-cell region LCh1 and the portion LCi1 of the inactive cell region LCi. The trench gate electrode TG3 is located between the hybrid sub-cell region LCh2 and the portion LCi2 of the inactive cell region LCi. The trench gate electrodes TG2 and TG3 are electrically coupled to the emitter electrode EE.

In the hybrid sub-cell region LCh1, in the portion of the p-type body region PB which is closer to the upper surface Sa of the semiconductor substrate SS, a plurality of n<sup>+</sup>-type emitter regions NE are formed. The p-type body region PB is a semiconductor region having a p-type conductivity type. The n<sup>+</sup>-type emitter regions NE are semiconductor regions each having an n-type conductivity type different from the p-type conductivity type. In the hybrid sub-cell region LCh1, the p-type body region PB is formed continuously along the Y-axis direction in plan view. In the hybrid sub-cell region LCh1, the plurality of n<sup>+</sup>-type emitter regions NE are arranged along the Y-axis direction in plan view to be spaced 45 apart from each other.

Note that, in the present specification, the fact that a semiconductor has the p-type conductivity type means that only holes or both electrons and holes may be charge carriers, the density of the holes is higher than the density of the electrons, and the holes are major charge carriers. Also, in the present specification, the fact that a semiconductor has the n-type conductivity type means that only electrons or both electrons and holes may be charge carriers, the density of the electrons is higher than the density of the holes, and the electrons are major charge carriers.

In the hybrid sub-cell region LCh2, in the portion of the p-type body region BP which is closer to the upper surface Sa of the semiconductor substrate SS, the plurality of n<sup>+</sup>-type emitter regions NE are provided. In the hybrid sub-cell region LCh2, the p-type body region PB is formed continuously along the Y-axis direction in plan view. In the hybrid sub-cell region LCh2, the plurality of n<sup>+</sup>-type emitter regions NE are arranged along the Y-axis direction to be spaced apart from each other.

In each of the hybrid sub-cell regions LCh1 and LCh2, regions where the n<sup>+</sup>-type emitter regions NE are formed along the Y-axis direction, i.e., active sections LCaa and

regions (p-type body region PB) where the n<sup>+</sup>-type emitter regions NE are not formed, i.e., inactive sections LCai are alternately arranged.

In the inactive cell regions LCi, p-type floating regions PF are provided. The end portions of the p-type floating regions 5 PF which are closer to the lower surface Sb are located closer to the lower surface Sb in the Z-axis direction than the end portions of trenches T1, T2, and T3 which are closer to the lower surface Sb. In the trenches T1, T2, and T3, the trench gate electrodes TG1, TG2, and TG3 are respectively 10 formed. In such a case, even when the width Wi of the inactive cell region LCi in the X-axis direction is larger than the width Wh of the hybrid cell region LCh in the X-axis direction, a sufficient breakdown voltage can be ensured.

Note that, in the example shown in FIG. 2, the width Wh 15 region LCh1. of the hybrid cell region LCh in the X-axis direction is set smaller than the width Wi of each of the inactive cell regions LCi in the X-axis direction. In such a case, the IE effect of the IGBT can be enhanced.

e.g., a p-type floating region PFp is provided so as to surround the cell formation area AR1. The p-type floating region PFp is electrically coupled to the emitter electrode EE via the portion of a p<sup>+</sup>-type body contact region PBCp which is exposed at the bottom surface of a contact trench CT.

In the gate-wire-lead-out area AR2, the gate wire GL is placed and the trench gate electrode TG1 extends from within the cell formation area AR1 toward the gate wire GL. In the gate-wire-lead-out area AR2, the respective end portions of the adjacent two trench gate electrodes TG1 are 30 coupled to each other by a trench gate electrode TGz. In plan view, the trench gate electrode TGz is located in the region where the gate wire GL is located. The trench gate electrode TGz is electrically coupled to the gate wire GL via a coupling electrode GTG. Note that the end portion of each 35 of the inactive cell regions LCi which is closer to the gate-wire-lead-out area AR2 is defined by an end-portion trench gate electrode TGp.

In plan view, the trench gate electrodes TG2 and TG3 are located on both sides of the inactive cell region LCi inter- 40 posed therebetween. The trench gate electrode TG3 is electrically coupled to the trench gate electrode TG2 not only by the end-portion trench gate electrode TGp, but also by an emitter coupling portion TGx made of, e.g., a polycrystalline silicon film and formed in the same layer as those of the 45 trench gate electrodes TG2 and TG3. The emitter coupling portion TGx is electrically coupled to the emitter electrode EE via the contact trench CT formed in the emitter coupling portion TGx. By thus providing such a structure, it is possible to improve the reliability of electrical coupling 50 between the trench gate electrodes TG2 and TG3 and the emitter electrode EE.

In Embodiment 1, in the hybrid sub-cell region LCh1, a plurality of p<sup>+</sup>-type semiconductor regions PR each including a type body contact region PBC and a p<sup>+</sup>-type latch-up 55 preventing region PLP are provided. In the hybrid sub-cell region LCh1, the plurality of p<sup>+</sup>-type semiconductor regions PR are formed in the respective portions of a semiconductor layer SLn which are located between the trenches T1 and T2 to be in contact with the p-type body region PB.

In the hybrid sub-cell region LCh1, the plurality of p<sup>+</sup>-type semiconductor regions PR are arranged along the Y-axis direction in plan view to be spaced apart from each other. This can reduce the ON voltage of the semiconductor chip CHP and reduce a switching loss when an IGBT in 65 which an inductor having an inductance L is coupled as a load to a collector electrode or an emitter electrode is

**10**

subjected to switching (hereinafter referred to also as "L-load switching") to be turned ON.

Note that, in the present specification, a switching operation in which the IGBT shifts from an OFF state to an ON state is referred to as "turn-ON" and a switching operation in which the IGBT shifts from the ON state to the OFF state is referred to as "turn-OFF".

Also, in the hybrid sub-cell region LCh1, in the p-type body region PB, the plurality of contact trenches CT as openings are formed in the p-type body region PB. The plurality of contact trenches CT are arranged along the Y-axis direction to be spaced apart from each other in plan view. The plurality of contact trenches CT reach the p<sup>+</sup>-type body contact region PBC located in the hybrid sub-cell

Also, in Embodiment 1, in the hybrid sub-cell region LCh2, the plurality of p<sup>+</sup>-type body contact regions PR each including the p<sup>+</sup>-type body contact region PBC and the p<sup>+</sup>-type latch-up preventing region PLP are provided. In the The gate-wire-lead-out area AR2 has a portion where, 20 hybrid sub-cell region LCh2, the plurality of p<sup>+</sup>-type semiconductor regions PR are formed in the respective portions of the semiconductor layer SLn which are located between the trenches T1 and T3 to be in contact with the p-type body region PB.

> In the hybrid sub-cell region LCh2, the plurality of p<sup>+</sup>-type semiconductor regions PR are arranged along the Y-axis direction in plan view to be spaced apart from each other. This can reduce the ON voltage of the semiconductor chip CHP and reduce the switching loss when the semiconductor chip CHP is turned ON by the L-load switching.

> Also, in the hybrid sub-cell region LCh2, in the p-type body region PB, the plurality of contact trenches CT as openings are formed. The plurality of contact trenches CT are arranged along the Y-axis direction in plan view to be spaced apart from each other. Each of the plurality of contact trenches CT reaches the p<sup>+</sup>-type body contact region PBC located in the hybrid sub-cell region LCh2.

> As shown in FIGS. 2 and 6, in each of the hybrid sub-cell regions LCh1 and LCh2, the regions where the p<sup>+</sup>-type semiconductor regions PR are formed, i.e., active sections LCba and the regions where the p<sup>+</sup>-type semiconductor regions PR are not formed, i.e., inactive sections LCbi are alternately arranged.

> In Embodiment 1, in the hybrid sub-cell region LCh1, the plurality of n<sup>+</sup>-type emitter regions NE are preferably located at the same positions as those of the plurality of p<sup>+</sup>-type semiconductor regions PR in the Y-axis direction. Also, in Embodiment 1, in the hybrid sub-cell region LCh2, the plurality of n<sup>+</sup>-type emitter regions NE are located at the same positions as those of the plurality of p<sup>+</sup>-type semiconductor regions PR in the Y-axis direction.

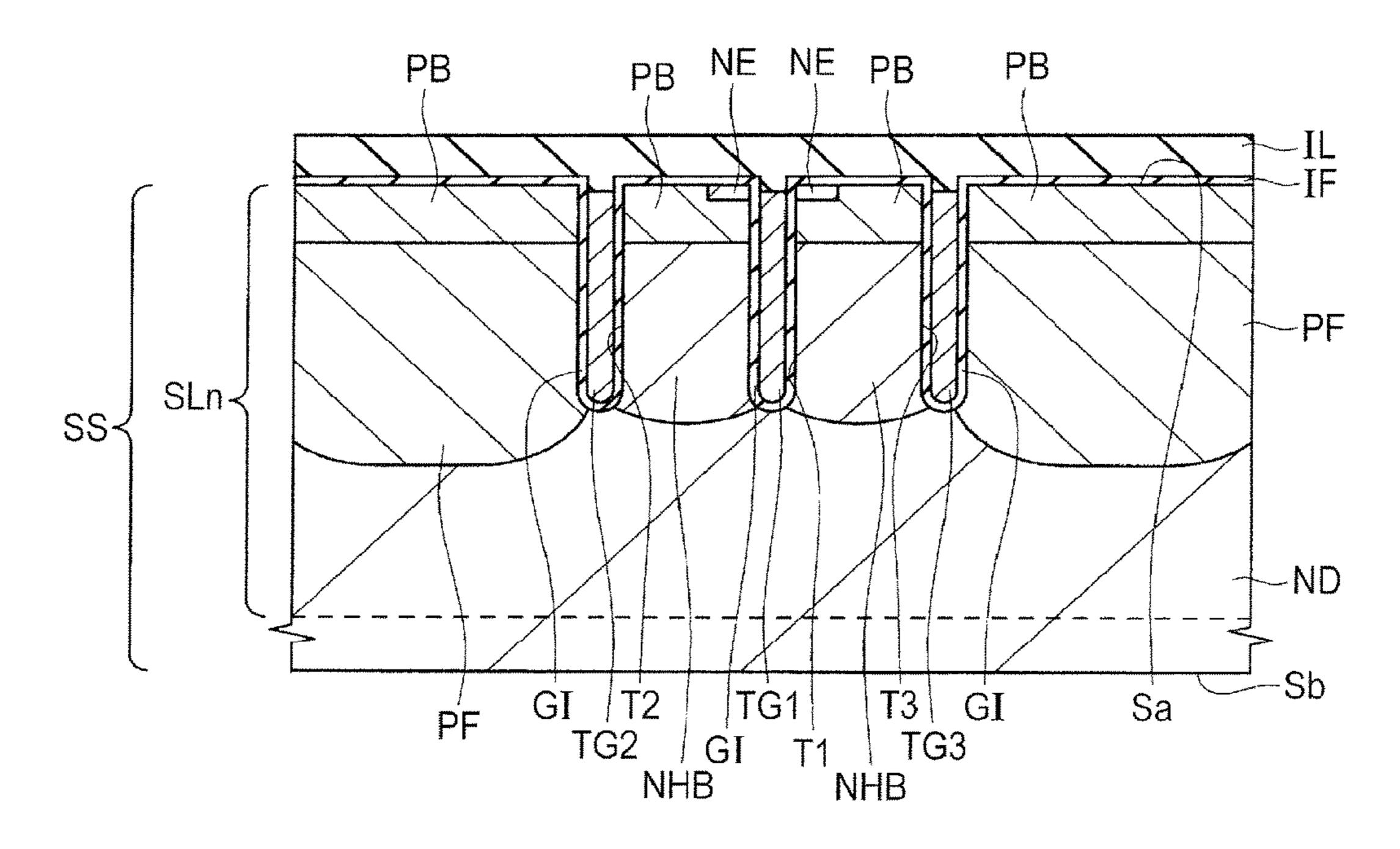

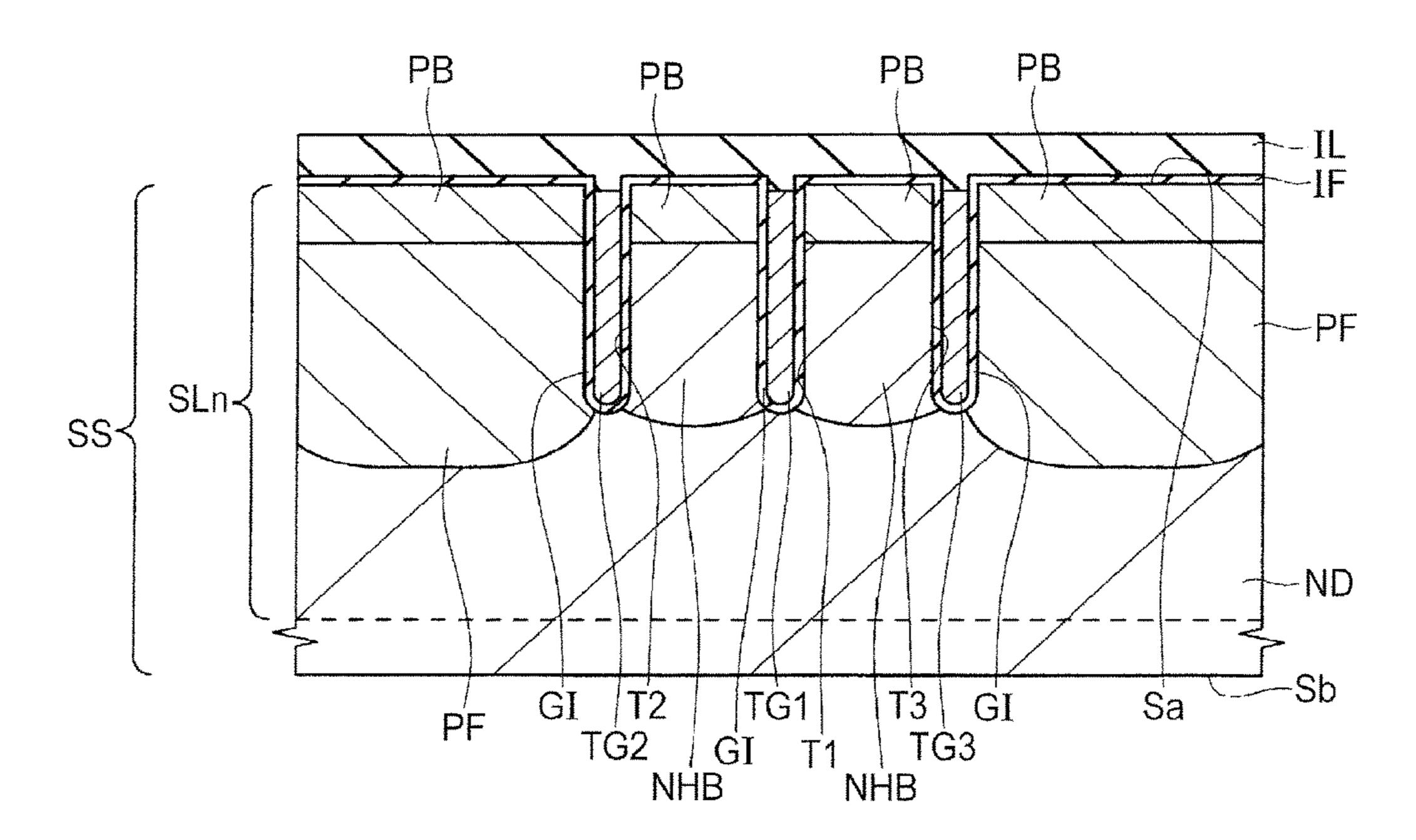

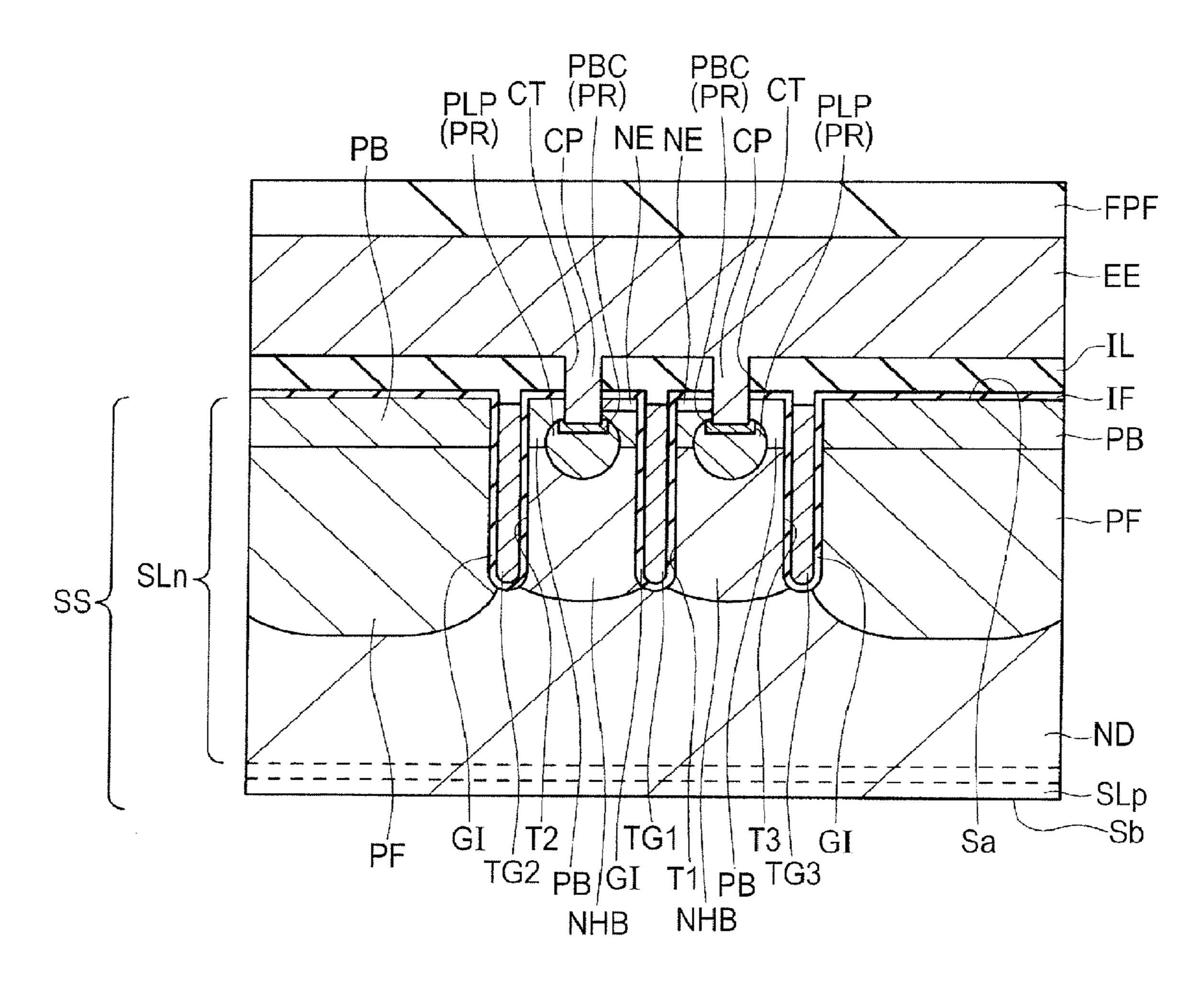

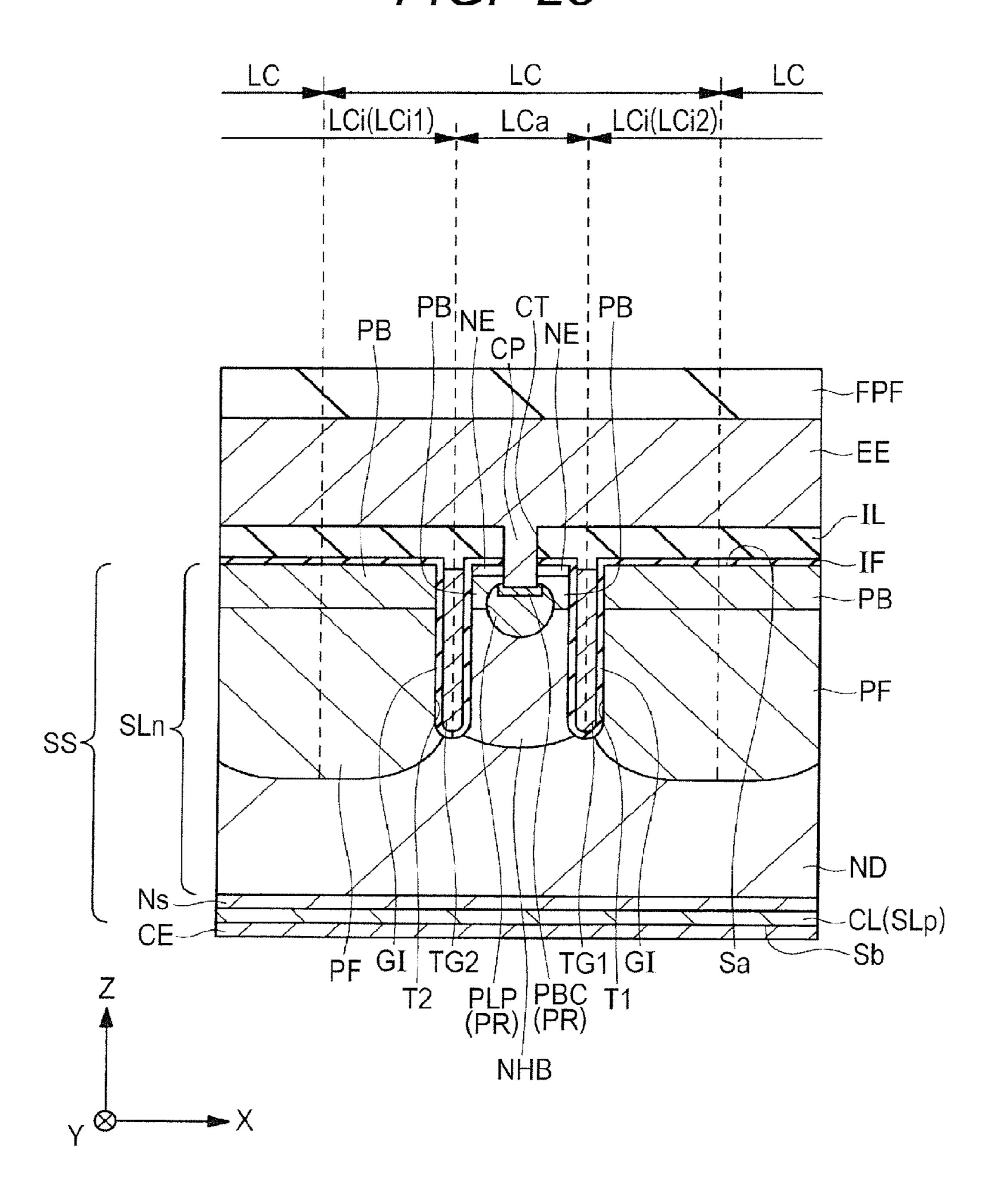

> Next, a description will be given of a configuration of the unit cell regions LC in the semiconductor chip as the semiconductor device in Embodiment 1. Specifically, using FIGS. 4 to 6, the description will be given of cross-sectional structures along the lines A-A, B-B, and C-C in FIG. 3.

As shown in FIGS. 4 to 6, the semiconductor substrate SS has the upper surface Sa as the first main surface and the lower surface Sb as the second main surface opposite to the o upper surface Sa. In the semiconductor substrate SS, the n-type semiconductor layer SLn is formed. In the portion of the semiconductor substrate SS which is located closer to the lower surface Sb than the semiconductor layer SLn, a semiconductor layer SLp is formed.

In the portion of the semiconductor layer SLn other than the upper-layer portion thereof, an n<sup>-</sup>-type drift region ND is formed as an n-type semiconductor region. Between the

semiconductor layers SLn and SLp, an n-type field stop region Ns is formed as an n-type semiconductor region. The semiconductor layer SLp forms a p<sup>+</sup>-type collector region CL as a p-type semiconductor region. Over the lower surface Sb of the semiconductor substrate SS, the collector electrode 5 CE electrically coupled to the p<sup>+</sup>-type collector region CL, i.e., the semiconductor layer SLp is formed.

On the other hand, in the cell formation area AR1, the p-type body region PB is provided closer to the upper surface Sa of the semiconductor substrate SS, i.e., in the 10 upper-layer portion of the semiconductor layer SLn.

In the upper surface Sa of the semiconductor substrate SS at the boundary portion between the hybrid sub-cell regions LCh1 and LCh2, the trench T1 is formed as a trench portion. The trench T1 extends in the Y-axis direction from the upper 15 surface Sa in plan view to reach a middle point in the semiconductor layer SLn.

Over the inner wall of the trench T1, the gate insulating film GI is formed. In the trench T1, the trench gate electrode TG1 is formed over the gate insulating film GI so as to be 20 embedded in the trench T1. The trench gate electrode TG1 is electrically coupled to the gate electrode GE (see FIG. 1). Note that the trench gate electrode TG1 is formed continuously along the Y-axis direction in plan view.

On the other hand, in the upper surface Sa of the semiconductor substrate SS in the boundary portion between the hybrid cell region LCh and the inactive cell region LCi, the trenches T2 and T3 each as the trench portion are formed. Each of the trenches T2 and T3 extends from the upper surface Sa to reach a middle point in the semiconductor layer 30 SLn. The trenches T2 and T3 are located on both sides of the trench T1 interposed therebetween to extend in the Y-axis direction in plan view.

Over the inner wall of each of the trenches T2 and T3, the gate insulating film GI is formed. In the trench T2, the trench 35 gate electrode TG2 is formed over the gate insulating film GI so as to be embedded in the trench T2. In the trench T3, the trench gate electrode TG3 is formed over the gate insulating film GI so as to be embedded in the trench T3. The trench gate electrodes TG2 and TG3 are electrically coupled to the 40 emitter electrode EE. Note that, each of the trench gate electrodes TG2 and TG3 is formed continuously along the Y-axis direction in plan view.

In the hybrid sub-cell region LCh1, the p-type body region PB is formed in the portion of the semiconductor 45 layer SLn which is located between the trenches T1 and T2 to be in contact with the gate insulating film GI formed over the inner wall of the trench T1 and with the gate insulating film GI formed over the inner wall of the trench T2. In the hybrid sub-cell region LCh2, the p-type body region PB is 50 formed in the portion of the semiconductor layer SLn which is located between the trenches T1 and T3 to be in contact with the gate insulating film GI formed over the inner wall of the trench T1 and with the gate insulating film GI formed over the inner wall of the trench T3.

As shown in FIG. 4, in the cross section along the line A-A in FIG. 3, in each of the hybrid-sub-cell regions LCh1 and LCh2, the n<sup>+</sup>-type emitter region NE is formed only in the portion of the upper surface Sa of the semiconductor substrate SS which is closer to the trench gate electrode 60 TG1. On the other hand, as shown in FIG. 5, in the cross section along the line B-B, in each of the hybrid sub-cell formation regions LCh1 and LCh2, the n<sup>+</sup>-type emitter region NE is not formed in the upper surface Sa of the semiconductor substrate SS.

As described above, in the hybrid sub-cell region LCH1, the plurality of n'-type emitter regions NE are arranged

12

along the Y-axis direction in plan view to be spaced apart from each other. In the hybrid sub-cell region LCh2, the plurality of n<sup>+</sup>-type emitter regions NE are arranged along the Y-axis direction in plan view to be spaced apart from each other.

As shown in FIG. 4, in the cross section along the line A-A in FIG. 3, in the hybrid sub-cell region LCh1, the n<sup>+</sup>-type emitter region NE is formed in the portion of the semiconductor layer SLn which is located between the trenches T1 and T2 to be in contact with the p-type body region PB and with the gate insulating film GI formed over the inner wall of the trench T1. On the other hand, in the hybrid sub-cell region LCh2, the n<sup>+</sup>-type emitter region NE is formed in the portion of the semiconductor layer SLn which is located between the trenches T1 and T3 to be in contact with the p-type body region PB and with the gate insulating film GI formed over the inner wall of the trench T1.

The plurality of n<sup>+</sup>-type emitter regions NE formed in the hybrid sub-cell region LCh1 are electrically coupled to the emitter electrode EE. The plurality of n<sup>+</sup>-type emitter regions NE formed in the hybrid sub-cell region LCh2 are electrically coupled to the emitter electrode EE.

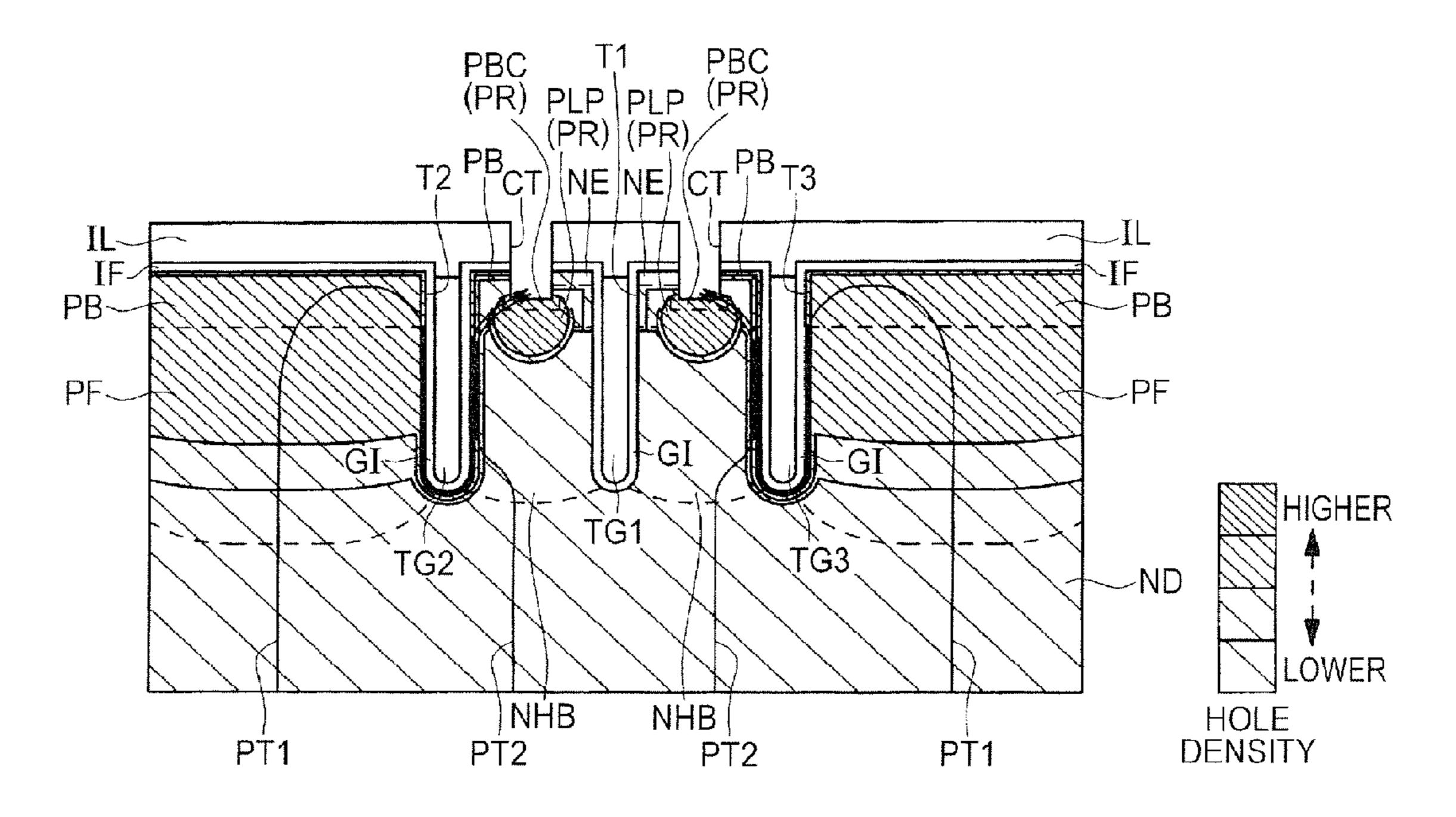

Preferably, in each of the hybrid sub-cell regions LCh1 and LCh2, under the p-type body region PB, an n-type hole barrier region NHB as an n-type semiconductor region is formed. In each of the hybrid sub-cell regions CLh1 and LCh2, the n-type impurity concentration in the n-type hole barrier region NHB is higher than the n-type impurity concentration in the portion of the semiconductor layer SLn (n-type drift region ND) which is located closer to the lower surface Sb than the n-type hole barrier region NHB and lower than the n-type impurity concentration in the type emitter region NE.

In the hybrid sub-cell region LCh1, the n-type hole barrier region NHB is formed in the portion of the semiconductor layer SLn which is located between the trenches T1 and T2. In the hybrid sub-cell region LCh2, the n-type hole barrier region NHB is formed in the portion of the semiconductor layer SLn which is located between the trenches T1 and T3.

Note that, in the hybrid sub-cell region LCh1, the n-type hole barrier region NHB may be in contact with the p-type body region PB, the gate insulating film GI formed over the inner wall of the trench T1, and the gate insulating film GI formed over the inner wall of the trench T2. Also, in the hybrid sub-cell region LCh2, the n-type hole barrier region NHB may be in contact with the p-type body region PB, the gate insulating film GI formed over the inner wall of the trench T1, and the gate insulating film GI formed over the inner wall of the trench T3. As a result, the holes stored in the n<sup>-</sup>-type drift region ND are less likely to be discharged into the emitter electrode EE in each of the hybrid sub-cell regions LCh1 and LCh2. Therefore, an IE effect can be enhanced.

In each of the inactive cell regions LCi, the p-type floating region PF as the p-type semiconductor region is provided under the p-type body region PB to be closer to the upper surface Sa of the semiconductor substrate SS. That is, in the portion LCi1 of the inactive cell region LCi, the p-type floating region PF is formed in the portion of the semiconductor layer SLn which is located opposite to the trench T1 relative to the trench T2 interposed therebetween. In the portion LCi2 of the inactive cell region LCi, the p-type floating region PF is formed in the portion of the semiconductor layer SLn which is located opposite to the trench T1 relative to the trench T3 interposed therebetween.

As described above, in the portion LCi1 of the inactive cell region LCi, the end portion of the p-type floating region PF which is closer to the lower surface Sb is located closer to the lower surface Sb in the Z-axis direction than the end portion of the trench T2 which is closer to the lower surface Sb. Also, in the portion LCi2 of the inactive cell region LCi, the end portion of the P-type floating region PF which is closer to the lower surface Sb is located closer to the lower surface Sb in the Z-axis direction than the end portion of the trench T3 which is closer to the lower surface Sb.

Also, as described above, in the portion LCi1, the p-type floating region PF is preferably in contact with the gate insulating film GI formed over the inner wall of the trench T2. Also, in the portion LCi2, the p-type floating region PF is preferably in contact with the gate insulating film GI 15 formed over the inner wall of the trench T3.

As shown in FIGS. 4 and 5, in each of the hybrid cell region LCh and the inactive cell regions LCi, the interlayer insulating film IL made of, e.g., silicon dioxide or the like is formed over the upper surface Sa of the semiconductor 20 substrate SS. The interlayer insulating film IL is formed so as to cover the p-type body region PB in each of the hybrid sub-cell regions LCh1 and LCh2. Note that, between the upper surface Sa of the semiconductor substrate SS and the interlayer insulating film IL, an insulating film IF may also 25 be formed.

In Embodiment 1, in each of the hybrid sub-cell regions LCh1 and LCh2, in the interlayer insulating film IL and the semiconductor layer SLn, the contact trenches CT are formed as a plurality of openings each extending through the interlayer insulating film IL to reach a middle point in the semiconductor layer SLn. In each of the hybrid sub-cell regions LCh1 and LCh2, the plurality of contact trenches CT are arranged to be spaced apart from each other in the Y-axis direction in plan view.

Accordingly, as shown in FIG. 4, in the cross-section along the line A-A in FIG. 3, the contact trenches CT are formed. However, as shown in FIG. 5, in the cross section along the line B-B in FIG. 3, the contact trenches CT are not formed.

As shown in FIG. **4**, in the cross section along the line A-A in FIG. **3**, in each of the hybrid sub-cell regions LCh1 and LCh2, in the portion of the p-type body region PB which is exposed at the bottom surface of each of the plurality of contact trenches CT, the p<sup>+</sup>-type body contact region PBC as 45 the p-type semiconductor region is formed. Also, under the p<sup>+</sup>-type body contact region PBC, the p<sup>+</sup>-type latch-up preventing region PLP is formed. The p<sup>+</sup>-type body contact region PBC and the p<sup>+</sup>-type latch-up preventing region PLP form each of the p<sup>+</sup>-type semiconductor regions PR.

That is, in each of the hybrid sub-cell regions LCh1 and LCh2, the p<sup>+</sup>-type semiconductor region PR includes the p<sup>+</sup>-type body contact region PBC and the p<sup>+</sup>-type latch-up preventing region PLP. In each of the hybrid sub-cell regions LCh1 and LCh2, the p-type impurity concentration in the 55 p<sup>+</sup>-type body contact region PBC is higher than the p-type impurity concentration in the p<sup>+</sup>-type latch-up preventing region PLP.

In each of the hybrid sub-cell regions LCh1 and LCh2, the plurality of p<sup>+</sup>-type semiconductor regions PR are formed in the portions of the p-type body region PB which are exposed individually in the plurality of contact trenches CT. Also, as shown in FIG. 4, in the cross section along the line A-A in FIG. 3, in the hybrid sub-cell region CLh1, the plurality of p<sup>+</sup>-type semiconductor regions PR are formed in the portion of the semiconductor layer SLn which is located between the trenches T1 and T2. On the other hand, in the hybrid sub-cell

14

region LCh2, the plurality of p<sup>+</sup>-type semiconductor regions PR are formed in the portion of the semiconductor layer SLn which is located between the trenches T1 and T3.

In the hybrid sub-cell region CLh1, the p-type impurity concentration in each of the plurality of p<sup>+</sup>-type semiconductor regions PR is higher than the p-type impurity concentration in the p-type body region PB. In the hybrid sub-cell region CLh2, the p-type impurity concentration in each of the plurality of p<sup>+</sup>-type semiconductor regions PR is higher than the p-type impurity concentration in the p-type body region PB. In the hybrid sub-cell region LCh1, the plurality of p<sup>+</sup>-type semiconductor regions PR are arranged along the Y-axis direction in plan view to be spaced apart from each other. Also, in the hybrid sub-cell region LCh2, the plurality of p<sup>+</sup>-type semiconductor regions PR are arranged along the Y-axis direction in plan view to be spaced apart from each other.

As shown in FIG. 4 which is the cross section along the line A-A in FIG. 3, in each of the hybrid sub-cell regions LCh1 and LCh2, the plurality of coupling electrodes CP are formed to be embedded individually in the plurality of contact trenches CT.

In each of the hybrid sub-cell regions LCh1 and LCh2, the coupling electrodes CP are in contact with the n<sup>+</sup>-type emitter regions NE and the p<sup>+</sup>-type semiconductor regions PR. Accordingly, in each of the hybrid sub-cell regions LCh1 and LCh2, the n<sup>+</sup>-type emitter region NE and the plurality of p<sup>+</sup>-type semiconductor regions PR are electrically coupled to the emitter electrode EE via the plurality of coupling electrodes CP.

In each of the hybrid sub-cell regions LCh1 and LCh2, in each pair of the coupling electrode CP and the p<sup>+</sup>-type semiconductor region PR which are coupled to each other, the coupling electrode CP is in contact with the p<sup>+</sup>-type body contact region PBC included in the p<sup>+</sup>-type semiconductor region PR. This can reduce the contact resistance between the coupling electrode CP and the p<sup>+</sup>-type semiconductor region PR.

As shown in FIGS. 4 and 5, over the interlayer insulating film IL, the emitter electrode EE made of a metal film containing, e.g., aluminum as a main component is provided. The emitter electrode EE is coupled to the n<sup>+</sup>-type emitter regions NE and the p<sup>+</sup>-type body contact regions PBC via the contact trenches CT. In the example shown in FIG. 4, the coupling electrodes CP and the emitter electrode EE are formed integrally.

Over the emitter electrode EE, the insulating film FPF as a passivation film made of, e.g., a polyimide-based organic insulating film or the like is further formed.

Note that, in the technique disclosed in Patent Document 3 described above, a semiconductor region equivalent to the p-type floating region PF in the semiconductor device in Embodiment 1 has not been formed. Also, in the technique disclosed in Patent Document 3 described above, unlike in Embodiment 1, a semiconductor region equivalent to the p-type body region PB in the semiconductor device in Embodiment 1 is selectively formed in a longitudinal direction between the trenches.

< Method of Manufacturing Semiconductor Device>

Next, a method of manufacturing a semiconductor device in Embodiment 1 will be described. FIGS. 7 to 24 are main-portion cross-sectional views showing the manufacturing process of the semiconductor device in Embodiment 1. FIGS. 7 to 17, 19, and 21 to 24 are cross-sectional views along the line A-A in FIG. 3, similarly to FIG. 4. FIGS. 18 and 20 are cross-sectional views along the line B-B in FIG. 3, similarly to FIG. 5.

The following will mainly describe the cell formation area AR1 (see FIG. 2). For the gate-wire-lead-out area AR2 (see FIG. 2), FIG. 2 is referred to as necessary. The following will also describe the unit cell regions LC each including the hybrid cell region LCh as the active cell region and the 5 inactive cell regions LCi. As described above, the hybrid cell region LCh includes the hybrid sub-cell regions LCh1 and LCh**2**.

Note that each of the unit cell regions CL includes the positive half portion LCi1 of the inactive cell region LCi 10 which is located on the negative side of the hybrid cell region LCh in the X-axis direction to be adjacent thereto. Also, the unit cell region LC includes the negative half portion CLi2 of the inactive cell region CLi which is located on the positive side of the hybrid cell region CLh in the 15 X-axis direction to be adjacent thereto.

First, as shown in FIG. 7, the semiconductor substrate SS made of a silicon single crystal into which an n-type impurity such as, e.g., phosphorus (P) has been introduced is provided. The semiconductor substrate SS has the upper 20 surface Sa as the first main surface and the lower surface Sb as the second main surface opposite to the upper surface Sa.

The impurity concentration of the n-type impurity in the semiconductor substrate SS can be set to, e.g., about  $2 \times 10^{14}$ cm<sup>-3</sup>. At this stage, the semiconductor substrate SS is a thin 25 plate of a semiconductor having a generally circular twodimensional shape, which is referred to as a wafer. The thickness of the semiconductor substrate SS can be set to, e.g., about 450 μm to 1000 μm.

Note that, in the semiconductor substrate SS, the semiconductor layer closer to the upper surface Sa than the semiconductor layer in which the n-type field stop region Ns (see FIG. 4) is to be formed is assumed to be the semiconductor layer SLn. The semiconductor layer SLn is an n-type semiconductor substrate SS is provided, the n-type semiconductor layer SLn is formed in the semiconductor substrate SS.

Next, over the entire upper surface Sa of the semiconductor substrate SS, a resist film R1 for introducing an 40 n-type hole barrier region is formed by coating or the like and patterned by typical lithography. Using the patterned resist film R1 as a mask, an n-type impurity is introduced into the upper surface Sa of the semiconductor substrate SS by, e.g., ion implantation to form the n-type hole barrier 45 regions NHB. At this time, as a preferred example of conditions for the ion implantation, ion implantation conditions such that, e.g., an ion species is phosphorus (P), a dose is about  $6 \times 10^{12}$  cm<sup>-2</sup>, and an implantation energy is about 80 KeV can be shown. Then, by ashing or the like, the 50 unneeded resist film R1 is removed.

Next, as shown in FIG. 8, over the upper surface Sa of the semiconductor substrate SS, a resist film R2 for introducing a p-type floating region is formed by coating or the like and patterned by typical lithography. Using the patterned resist 55 film R2 as a mask, a p-type impurity is introduced into the upper surface Sa of the semiconductor substrate SS by, e.g., ion implantation to form the p-type floating region PF. At this time, as a preferred example of conditions for the ion implantation, ion implantation conditions such that, e.g., an 60 ion species is boron (B), a dose is about  $3.5 \times 10^{13}$  cm<sup>-2</sup>, and an ion implantation energy is about 75 KeV can be shown. Then, by ashing or the like, the unneeded resist film R2 is removed. Note that, when the p-type floating region PF is formed in the cell formation area AR1 (see FIG. 2), the 65 p-type floating region PFp is formed in, e.g., the gate-wirelead-out area AR2 (see FIG. 2).

**16**

Next, as shown in FIG. 9, over the upper surface Sa of the semiconductor substrate SS, a hard mask film HM made of, e.g., silicon dioxide is deposited by, e.g., a CVD (Chemical Vapor Deposition) method or the like. The hard mask film HM has a thickness of, e.g., about 450 nm.

Next, as shown in FIG. 9, over the upper surface Sa of the semiconductor substrate SS, a resist film R3 for processing a hard mask is formed by coating or the like and patterned by typical lithography. Using the patterned resist film R3 as a mask, the hard mask film HM is patterned by, e.g., dry etching.

Then, as shown in FIG. 10, the unneeded resist film R3 is removed by ashing or the like.

Next, as shown in FIG. 11, using the patterned hard mask film HM, the trenches T1, T2, and T3 are formed by, e.g., anisotropic dry etching. At this time, the trench T1 is formed to extend from the upper surface Sa of the semiconductor substrate SS in the Y-axis direction in plan view and reach a middle point in the semiconductor layer SLn. Also, the trenches T2 and T3 are formed to extend in the Y-axis direction in plan view from the upper surface Sa of the semiconductor substrate SS, reach middle points in the semiconductor layer SLn, and be located on both sides of the trench T1 interposed therebetween. As a gas for the anisotropic dry etching, e.g., a  $Cl_2/O_2$ -based gas can be shown as a preferred example.

Then, as shown in FIG. 12, by wet etching using, e.g., a hydrofluoric-acid-based etching solution or the like, the unneeded hard mask HM is removed.

Next, as shown in FIG. 13, extension diffusion (e.g., at 1200° C. for about 30 minutes) is performed on the p-type floating regions PF and the n-type hole barrier regions NHB. At this time, the extension diffusion is performed such that the end portion of the p-type floating region PF which is semiconductor layer. It follows therefore that, when the 35 closer to the lower surface Sb is located closer to the lower surface Sb in the Z-axis direction than the respective end portions of the trenches T1, T2, and T3 which are closer to the lower surface Sb.

> Thus, in the portion of the semiconductor layer SLn which is located opposite to the trench T1 relative to the trench T2 interposed therebetween, the p-type floating region PF is formed and, in the portion of the semiconductor layer SLn which is located opposite to the trench T1 relative to the trench T3 interposed therebetween, the p-type floating regions PF are formed. Preferably, the p-type floating region PF formed opposite to the trench T1 relative to the trench T2 interposed therebetween is in contact with the gate insulating film GI formed over the inner wall of the trench T2, and the p-type floating region PF formed opposite to the trench T1 relative to the trench T3 interposed therebetween is in contact with the gate insulating film GI formed over the inner wall of the trench T3.

> Additionally, the end portion of the p-type floating region PF formed opposite to the trench T1 relative to the trench T2 interposed therebetween which is closer to the lower surface Sb is located closer to the lower surface Sb in the Z-axis direction than the end portion of the trench T2 which is closer to the lower surface Sb. Also, the end portion of the p-type floating region PF formed opposite to the trench T1 relative to the trench T3 interposed therebetween which is closer to the lower surface Sb is located closer to the lower surface Sb in the Z-axis direction than the end portion of the trench T3 which is closer to the lower surface Sb.

> In addition, in the portion of the semiconductor layer SLn which is located between the trenches T1 and T2 and the portion of the semiconductor layer SLn which is located between the trenches T1 and T3, the n-type hole barrier

regions NHB are formed. Preferably, the n-type hole barrier region NHB formed between trenches T1 and T2 is in contact with the gate insulating film GI formed over the inner wall of the trench T1 and with the gate insulating film GI formed over the inner wall of the trench T2. Preferably, the n-type hole barrier region NHB formed between the trenches T1 and T3 is in contact with the gate insulating film GI formed over the inner wall of the trench T1 and with the gate insulating film GI formed over the inner wall of the trench T3.

During the extension diffusion, the region of the n-type semiconductor substrate SS where the p-type floating regions PF and the n-type hole barrier regions NHB are not formed serves as the n<sup>-</sup>-type drift region ND. In other words, the region of the n-type semiconductor layer SLn where the 15 p-type floating regions PF and the n-type hole barrier regions NHB are not formed serves as the n-type drift region ND. Note that, in the process step shown in FIG. 13, the n-type drift region ND is formed to extend from within the semiconductor layer SLn to the lower surface Sb of the 20 semiconductor substrate SS.

Between the trenches T1 and T2, the n-type impurity concentration in the n-type hole barrier region NHB is higher than the n-type impurity concentration in the portion of the semiconductor layer SLn which is located closer to the 25 lower surface Sb than the n-type hole barrier region NHB, i.e., in the n<sup>-</sup>-type drift region ND and lower than the n-type impurity concentration in each of the n<sup>+</sup>-type emitter regions NE. What applies to the n-type impurity concentration in the n-type hole barrier region NHB between the trenches T1 and 30 T2 similarly applies to the n-type impurity concentration in the n-type hole barrier region NHB between the trenches T1 and T3.

Next, as shown in FIG. 13, by, e.g., a thermal oxidation method or the like, the gate insulating film GI made of, e.g., 35 silicon dioxide is formed over the upper surface Sa of the semiconductor substrate SS and the respective inner walls of the trenches T1, T2, and T3. The thickness of the gate insulating film GI is, e.g., about 0.12  $\mu$ m.

Next, as shown in FIG. 14, over the upper surface Sa of 40 the semiconductor substrate SS and in each of the trenches T1, T2, and T3, a conductive film CG made of polycrystal-line silicon doped with phosphorus (P) (Doped Poly-Silicon) is deposited by, e.g., a CVD method or the like. The thickness of the conductive film CF is. e.g., about 0.6 µm. 45

Next, as shown in FIG. 15, by, e.g., dry etching or the like, the conductive film CF is etched back. Thus, the trench gate electrode TG1 made of the conductive film CF embedded in the trench T1 via the gate insulating film GI is formed. Also, the trench gate electrode GT2 made of the conductive film 50 CF embedded in the trench T2 via the gate insulating film GI is formed. Also, the trench gate electrode GT3 made of the conductive film CF embedded in the trench T3 via the gate insulating film GI is formed.

In other words, over the gate insulating film GI, the trench 55 gate electrode TG1 is formed so as to be embedded in the trench T1 and, over the gate insulating film GI, the trench gate electrode TG2 is formed so as to be embedded in the trench T2 and, over the gate insulating film GI, the trench gate electrode TG3 is formed so as to be embedded in the 60 trench T3. As a preferred example of a gas for the etching, e.g., a SF<sub>6</sub> gas or the like can be shown.

Next, as shown in FIG. 16, the gate insulating film GI except for the portions thereof located in the trenches T1, T2, and T3 is removed by dry etching or the like.

Next, as shown in FIG. 17, over the upper surface Sa of the semiconductor substrate SS, the insulating film IF made

**18**

of a relatively thin silicon dioxide film (which is as thin as, e.g., the gate insulating film GI) for subsequent ion implantation is formed by, e.g., thermal oxidation or CVD. Next, over the upper surface Sa of the semiconductor substrate SS, a resist film (the depiction thereof is omitted) for introducing a p-type body region is formed by typical lithography. Using the resist film for introducing the p-type body region as a mask, a p-type impurity is introduced into the entire surface of the cell formation area AR1 and other regions into which the p-type impurity needs to be introduced to form the p-type body region PB.

Specifically, in the portion of the semiconductor layer SLn which is located between the trenches T1 and T2, the p-type body region PB is formed to be in contact with the gate insulating film GI formed over the inner wall of the trench T1 and with the gate insulating film GI formed over the inner wall of the trench T2. Also, in the portion of the semiconductor layer SLn which is located between the trenches T1 and T3, the p-type body region PB is formed to be in contact with the gate insulating film GI formed over the inner wall of the trench T1 and with the gate insulating film GI formed over the inner wall of the trench T3.

At this time, as a preferred example of conditions for the ion implantation, ion implantation conditions such that, e.g., an ion species is boron (B), a dose is about  $3\times10^{13}$  cm<sup>-2</sup>, and an implantation energy is about 75 KeV can be shown. Then, by ashing or the like, the unneeded resist film for introducing the p-type body region is removed.

Then, over the upper surface Sa of the semiconductor substrate SS, a resist film (the depiction thereof is omitted) for introducing n<sup>+</sup>-type emitter regions is formed by typical lithography. Using the resist film for introducing the n<sup>+</sup>-type emitter regions as a mask, an n-type impurity is introduced into the upper-layer portion of the p-type body region PB of the hybrid cell region LCh by, e.g., ion implantation to form the n<sup>+</sup>-type emitter regions NE.

Specifically, in the portion of the semiconductor layer SLn which is located between the trenches T1 and T2, the n<sup>+</sup>-type emitter region NE is formed to be in contact with the gate insulating film GI formed over the inner wall of the trench T1 and with the p-type body region PB. Also, in the portion of the semiconductor layer SLn which is located between the trenches T1 and T3, the n'-type emitter region NE is formed to be in contact with the gate insulating film GI formed over the inner wall of the trench T1 and with the p-type body region PB.

At this time, as a preferred example of conditions for the ion implantation, ion implantation conditions such that, e.g., an ion species is arsenic (As), a dose is about  $5 \times 10^{15}$  cm<sup>-2</sup>, and an implantation energy is about 80 KeV can be shown. Then, by asking or the like, the unneeded resist film for introducing the n<sup>+</sup>-type emitter regions is removed.

Here, the cross section shown in FIG. 17 is equivalent to the cross section along the line A-A in FIG. 3, i.e., the cross section shown in FIG. 4. On the other hand, in the cross section along the line B-B in FIG. 3, i.e., in a cross section equivalent to the cross section shown in FIG. 5, the n'-type emitter regions NE are not formed so that a state as shown in FIG. 18 is reached.

Next, as shown in FIG. **19**, over the upper surface Sa of the semiconductor substrate SS, the interlayer insulating film IL made of, e.g., a PSG (Phosphosilicate Glass) film is formed by, e.g., a CVD method or the like. The interlayer insulating film IL is formed so as to cover the p-type body region PB via the insulating film IF. The interlayer insulating film IL has a thickness of, e.g., about 0.6 μm. As preferred examples of the material of the interlayer insulating film IL,

not only the PSG film, but also a BPSG (Borophosphosilicate Glass film), an NSG (Non-doped Silicate Glass) film, a SOG (Spin-On-Glass) film, a composite film thereof, or the like can be shown.

Here, the cross section shown in FIG. 19 is equivalent to 5 the cross section along the line A-A in FIG. 3, i.e., the cross section shown in FIG. 4. On the other hand, in the cross section along the line B-B in FIG. 3, i.e., in the cross section equivalent to the cross section shown in FIG. 5, the n'-type emitter regions NE are not formed so that a state as shown 10 in FIG. 20 is reached.

Next, as shown in FIG. 21, over the interlayer insulating film IL, a resist film (the depiction thereof is omitted) for forming contact trenches is formed by typical lithography. Subsequently, the contact trenches CT are formed by, e.g., 15 anisotropic dry etching or the like. As a preferred example of a gas used for the anisotropic dry etching, a gas mixture including, e.g., an Ar gas, a CHF<sub>3</sub> gas, and a CF<sub>4</sub> gas or the like can be shown. Then, the unneeded resist film for forming the contact trenches is removed by asking or the 20 be spaced apart from each other. like.

Next, as shown in FIG. 21, the contact trenches CT are extended into the semiconductor substrate SS by, e.g., anisotropic dry etching. As a preferred example of the gas for the anisotropic dry etching, e.g., a Cl<sub>2</sub>/O<sub>2</sub> gas can be 25 shown.

Here, the cross section shown in FIG. 21 is equivalent to a cross section along the line A-A in FIG. 3, i.e., the cross section shown in FIG. 4. On the other hand, in a cross section along the line B-B in FIG. 3, i.e., a cross section 30 equivalent to the cross section shown in FIG. 5, the contact trenches CT are not formed. As a consequence, the cross section along the line B-B in FIG. 3 remains unchanged from the cross section shown in FIG. 20.

FIG. 21, the contact trenches CT are formed as a plurality of openings each extending through the interlayer insulating film IL in the hybrid sub-cell region LCh1 and reaching a middle point in the p-type body region PB. In the hybrid sub-cell region LCh1, the plurality of contact trenches CT are arranged along the Y-axis direction in plan view to be spaced apart from each other.

Also, by performing the process step shown in FIG. 21, in the hybrid sub-cell region LCh2, the contact trenches CT are formed as a plurality of openings each extending through the 45 interlayer insulating film IL and reaching a middle point in the p-type body region PB. In the hybrid sub-cell region LCh2, the plurality of contact trenches CT are arranged along the Y-axis direction in plan view to be spaced apart from each other.

Next, as shown in FIG. 22, a p-type impurity is ionimplanted through, e.g., the contact trenches CT to form the type body contact regions PBC. Here, as a preferred example of conditions for the ion implantation, ion implantation conditions such that, e.g., an ion species is boron (B), 55 a dose is about  $5 \times 10^{15}$  cm<sup>-2</sup>, and an implantation energy is about 80 KeV can be shown.

Likewise, a p-type impurity is ion-implanted through, e.g., the contact trenches CT to form the p<sup>+</sup>-type latch-up preventing regions PLP. Here, as a preferred example of 60 conditions for the ion implantation, ion implantation conditions such that, e.g., an ion species is boron (B), a dose is about  $5 \times 10^{15}$  cm<sup>-2</sup>, and an implantation energy is about 80 KeV can be shown. The p-type impurity concentration in each of the p<sup>+</sup>-type body contact regions PBC is higher than 65 the p-type impurity concentration in each of the p<sup>+</sup>-type latch-up preventing regions PLP. The p<sup>+</sup>-type body contact

**20**

region PBC and the p<sup>+</sup>-type latch-up preventing region PLP form the p<sup>+</sup>-type semiconductor region PR.