#### US010170490B2

# (12) United States Patent

# **Tanzawa**

# (10) Patent No.: US 10,170,490 B2 (45) Date of Patent: Jan. 1, 2019

#### (54) MEMORY DEVICE INCLUDING PASS TRANSISTORS IN MEMORY TIERS

- (71) Applicant: Micron Technology, Inc., Boise, ID (US)

- (72) Inventor: Toru Tanzawa, Adachi (JP)

- (73) Assignee: Micron Technology, Inc., Boise, ID (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 15/450,638

- (22) Filed: Mar. 6, 2017

### (65) Prior Publication Data

US 2018/0254282 A1 Sep. 6, 2018

Int. Cl. (51)H01L 27/11526 (2017.01)H01L 27/11524 (2017.01)H01L 27/1157 (2017.01)H01L 27/11556 (2017.01)H01L 27/11582 (2017.01)G11C 16/04 (2006.01)G11C 16/26 (2006.01)G11C 16/10 (2006.01)H01L 27/11573 (2017.01)

(52) **U.S. Cl.**

CPC ...... *H01L 27/11526* (2013.01); *G11C 16/04* (2013.01); *G11C 16/10* (2013.01); *G11C 16/26* (2013.01); *H01L 27/1157* (2013.01); *H01L 27/11556* (2013.01); *H01L 27/11573* (2013.01); *H01L 27/11582* (2013.01)

| (58) | Field of Classification Search         |              |

|------|----------------------------------------|--------------|

|      | CPC                                    | G11C 5/025   |

|      | USPC                                   | 365/230.06   |

|      | See application file for complete sear | rch history. |

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

|    | 5,818,083  | A *  | 10/1998 | Ito H01L 29/7883   |

|----|------------|------|---------|--------------------|

|    |            |      |         | 257/321            |

|    | 6,442,072  | B2 * | 8/2002  | Solimene G11C 8/08 |

|    |            |      |         | 365/185.23         |

|    | 7,936,004  | B2 * | 5/2011  | Kito H01L 21/8221  |

|    |            |      |         | 257/324            |

|    | 8,860,117  | B2   | 10/2014 | Tanzawa            |

| 20 | 08/0112209 | A1*  | 5/2008  | Cho G11C 13/0004   |

|    |            |      |         | 365/148            |

|    |            |      |         |                    |

(Continued)

#### OTHER PUBLICATIONS

Jang, J., et al., "Vertical cell array using TCAT(Terabit Cell Array Transistor) technology for ultra high density NAND flash memory", Symposium on VLSI Technology, (2009), 192-193.

(Continued)

Primary Examiner — Min Huang

(74) Attorney, Agent, or Firm — Schwegman Lundberg & Woessner, P.A.

#### (57) ABSTRACT

Some embodiments include apparatuses and methods of using such apparatuses. One of the apparatuses includes a semiconductor material, a pillar extending through the semiconductor material, a select gate located along a first portion of the pillar, memory cells located along a second portion of the pillar, and transistors coupled to the select gate through a portion of the semiconductor material. The transistors include sources and drains formed from portions of the semiconductor material. The transistors include gates that are electrically uncoupled to each other.

#### 11 Claims, 17 Drawing Sheets

# (56) References Cited

#### U.S. PATENT DOCUMENTS

| 0/2008 | Mizukami H01L 27/105                           |

|--------|------------------------------------------------|

|        | 365/185.05                                     |

| 5/2012 | Ahn G11C 16/0483                               |

|        | 365/185.02                                     |

| 8/2013 | Park G11C 16/0483                              |

|        | 365/184                                        |

| 2/2013 | Han G11C 16/04                                 |

|        | 365/185.17                                     |

| 8/2014 | Tanzawa                                        |

| 2/2015 | Lee H01L 27/11582                              |

|        | 257/324                                        |

| 9/2016 | Ikeda H01L 27/11582                            |

|        | 5/2012<br>8/2013<br>2/2013<br>8/2014<br>2/2015 |

#### OTHER PUBLICATIONS

Katsumata, R., et al., "Pipe-shaped BiCS flash memory with 16 stacked layers and multilevel-cell operation for ultra high density storage devices", Symposium on VLSI Technology, (Jun. 2009), 136-37.

Kim, J., et al., "Novel Vertical-Stacked Array-Transistor (VSAT) for ultra-high-density and cost-effective NAND Flash memory devices and SSD (Solid State Drive)", Symposium on VLSI Technology, (2009), 186-187.

Kim, W., et al, "Multi-layered Vertical Gate NAND Flash overcoming stacking limit for terabit density storage", Symposium on VLSI Technology, (2009), 188-89.

<sup>\*</sup> cited by examiner

|         | SELA             | SELB             | SELC             |

|---------|------------------|------------------|------------------|

| BLOCK 0 | SEL <sub>1</sub> | SEL2             | SEL <sub>3</sub> |

| BLOCK 1 | SEL 1            | SEL2             | SEL*3            |

| BLOCK 2 | SEL <sub>1</sub> | SEL*2            | SEL3             |

| BLOCK 3 | SEL <sub>1</sub> | SEL*2            | SEL*3            |

| BLOCK 4 | SEL*             | SEL <sub>2</sub> | SEL3             |

| BLOCK 5 | SEL*             | SEL <sub>2</sub> | SEL*3            |

| BLOCK 6 | SEL*             | SEL*2            | SEL3             |

| BLOCK 7 | SEL*             | SEL*2            | SEL*3            |

245 FIG. 2B

| SEL <sub>1</sub> | SEL* | SEL <sub>2</sub> | SEL*2      | SEL3 | SEL*3 |

|------------------|------|------------------|------------|------|-------|

| ٧i               | VO   | V1               | ۷Q         | V1   | VO    |

| VO               | V1   | VO               | <b>V</b> 1 | VO   | V1    |

FG. 20

|            |         | SELC       | SELB     | SELA       |

|------------|---------|------------|----------|------------|

| SELECTED   | BLOCK 0 | ***        | ***      |            |

| UNSELECTED | BLOCK 1 | <b>V</b> 1 | <b>V</b> | VO         |

| UNSELECTED | BLOCK 2 | <b>V</b> 1 | VO       | V1         |

| UNSELECTED | BLOCK 3 | Vį         | VO       | VO         |

| UNSELECTED | BLOCK 4 | VO         |          | <b>V</b>   |

| UNSELECTED | BLOCK 5 | VO         | V1       | VO         |

| UNSELECTED | BLOCK 6 | VO         | VO       | V1         |

| UNSELECTED | BLOCK 7 | VO         | VO       | <b>V</b> 0 |

| '          |         |            |          |            |

301 FIG. 3A

|            |         | SELC     | SELB       | SELA      |

|------------|---------|----------|------------|-----------|

| UNSELECTED | BLOCK 0 | V1       | <b>V</b>   | ۷0        |

| SELECTED   | BLOCK 1 | <b>*</b> |            |           |

| UNSELECTED | BLOCK 2 | <b>\</b> | VO         | VO        |

| UNSELECTED | BLOCK 3 | <b>V</b> | V()        | <b>V1</b> |

| UNSELECTED | BLOCK 4 | VO       | <b>V</b> 1 | V0        |

| UNSELECTED | BLOCK 5 | VO       | V1         | V1        |

| UNSELECTED | BLOCK 6 | VO       | VO         | VO        |

| UNSELECTED | BLOCK 7 | V0       | VO         | ۷1        |

302 FIG. 3B

|            |         | SELC | $SEL_{B}$ | SELA       |

|------------|---------|------|-----------|------------|

| UNSELECTED | BLOCK 0 | VO   | <b>V</b>  | <b>V</b> * |

| UNSELECTED | BLOCK 1 | VO   | V1        | VO         |

| UNSELECTED | BLOCK 2 | VO   | VO        | V1         |

| UNSELECTED | BLOCK 3 | VO   | VO        | VO         |

| SELECTED   | BLOCK 4 |      | ***       | <b>**</b>  |

| UNSELECTED | BLOCK 5 | ٧i   | V1        | VO         |

| UNSELECTED | BLOCK 6 | Vi   | VO        | V1         |

| UNSELECTED | BLOCK 7 | Vi   | VO        | VO         |

303 Fig. 3C

|          | SELA              | SELB             | SELC             | SELD             |

|----------|-------------------|------------------|------------------|------------------|

| BLOCK 0  | SEL <sub>1</sub>  | SEL <sub>2</sub> | SEL3             | SEL <sub>4</sub> |

| BLOCK 1  | SEL 1             | SEL <sub>2</sub> | SEL3             | SEL*4            |

| BLOCK 2  | SEL 1             | SEL <sub>2</sub> | SEL*5            | SEL <sub>4</sub> |

| BLOCK 3  | SEL <sub>1</sub>  | SEL <sub>2</sub> | SEL*3            | SEL*4            |

| BLOCK 4  | SEL <sub>1</sub>  | SEL*2            | SEL3             | SEL <sub>4</sub> |

| BLOCK 5  | SEL <sub>1</sub>  | SEL*2            | SEL3             | SEL*4            |

| BLOCK 6  | SEL <sub>1</sub>  | SEL*2            | SEL*3            | SEL <sub>4</sub> |

| BLOCK 7  | SEL <sub>1</sub>  | SEL*2            | SEL*3            | SEL*4            |

| BLOCK 8  | SEL*              | SEL <sub>2</sub> | SEL3             | SEL <sub>4</sub> |

| BLOCK 9  | SEL* <sub>1</sub> | SEL <sub>2</sub> | SEL <sub>3</sub> | SEL*4            |

| BLOCK 10 | SEL* <sub>1</sub> | SEL <sub>2</sub> | SEL*3            | SEL4             |

| BLOCK 11 | SEL*              | SEL <sub>2</sub> | SEL*3            | SEL*4            |

| BLOCK 12 | SEL*              | SEL*2            | SEL3             | SEL4             |

| BLOCK 13 | SEL*              | SEL*2            | SEL3             | SEL*4            |

| BLOCK 14 | SEL* <sub>1</sub> | SEL*2            | SEL*3            | SEL <sub>4</sub> |

| BLOCK 15 | SEL* <sub>1</sub> | SEL*2            | SEL*3            | SEL*4            |

445 FiG. 4B

| SEL <sub>1</sub> | SEL* <sub>1</sub> | SEL <sub>2</sub> | SEL*2 | SEL3 | SEL*3 | SEL <sub>4</sub> | SEL*4 |

|------------------|-------------------|------------------|-------|------|-------|------------------|-------|

| V1               | VO                | V1               | VO    | V1   | VO    | <b>V</b> 1       | VO    |

| VO               | ۷1                | VO               | V1    | VO   | V1    | V0               | ٧į    |

Fig. 4C

|      | NUMBER OF<br>BLOCKS | NUMBER OF<br>TRANSISTOR GATE LINES<br>IN EACH BLOCK | NUMBER OF<br>SWITCHES |

|------|---------------------|-----------------------------------------------------|-----------------------|

| 502> | $8 = 2^3$           | 3                                                   | $6 = 2 \times 3$      |

| 504> | $16 = 2^4$          | 4                                                   | $8 = 2 \times 4$      |

| 506> | $B = 2^{T}$         |                                                     | $S = 2 \times T$      |

FIG. 5

PROVIDE UNIQUE COMBINATIONS OF SIGNALS TO MEMORY CELL BLOCKS OF A MEMORY DEVICE DURING A MEMORY OPERATION OF THE MEMORY DEVICE

820

PROVIDE SIGNALS OF A PARTICULAR COMBINATION INCLUDED IN THE UNIQUE COMBINATION OF SIGNALS TO RESPECTIVE GATES OF TRANSISTORS COUPLED IN SERIES WITH EACH OTHER BETWEEN A FIRST SELECT LINE AND A SECOND SELECT LINE OF A MEMORY CELL BLOCKS

800

ric. 8

# MEMORY DEVICE INCLUDING PASS TRANSISTORS IN MEMORY TIERS

#### BACKGROUND

Memory devices are widely used in computers and many other electronic items to store information. Some conventional memory devices have memory cells that are organized in blocks with sub-blocks within each block. As storage density increases for a given device area, the number of sub-blocks in some conventional memory devices may increase. An increase in the number of sub-blocks may hinder the performance of some conventional memory devices.

#### BRIEF DESCRIPTION OF THE DRAWINGS

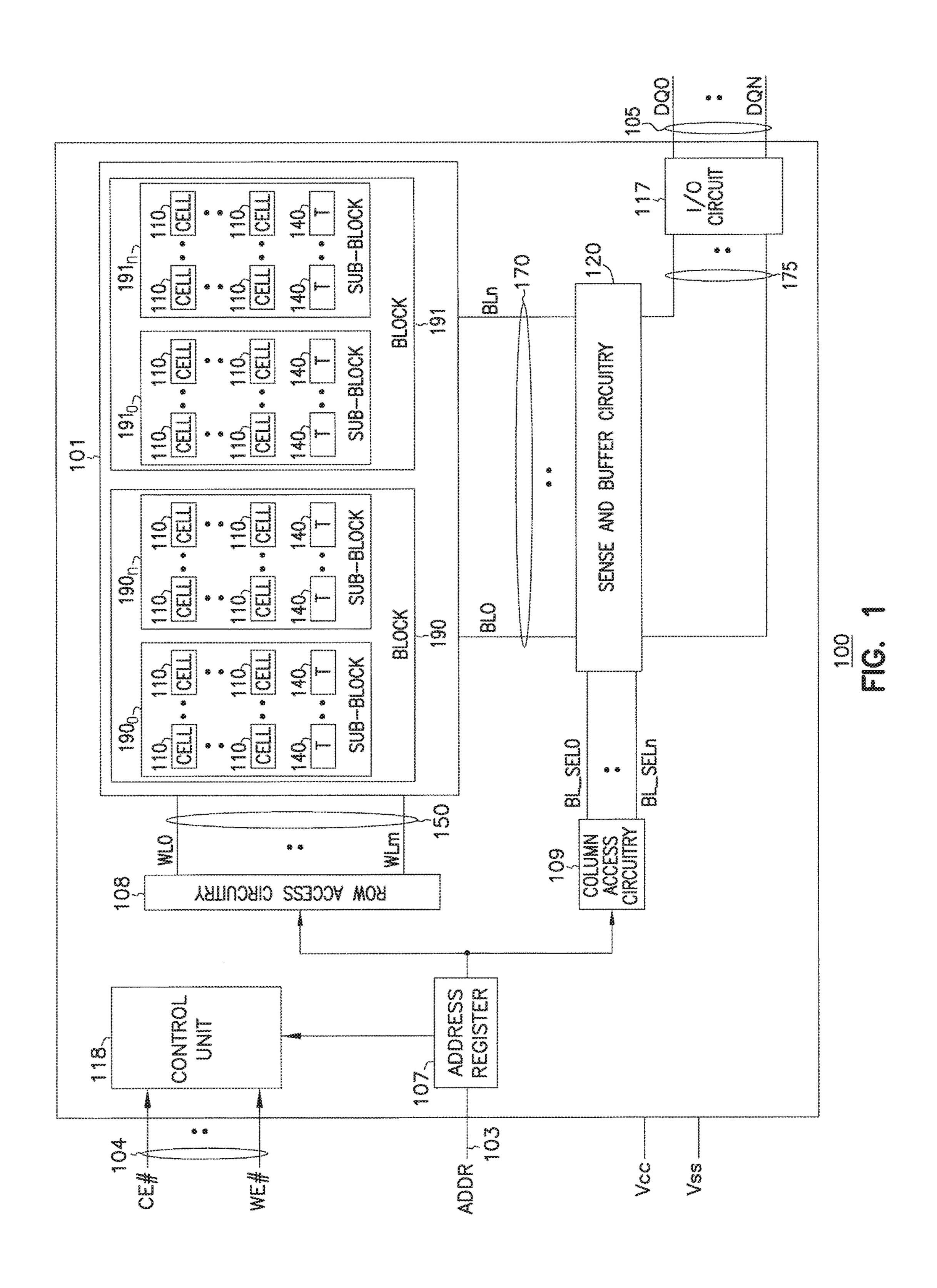

FIG. 1 shows a block diagram of an apparatus in the form of a memory device including memory cells and pass transistors formed in the same memory array, according to some embodiments described herein.

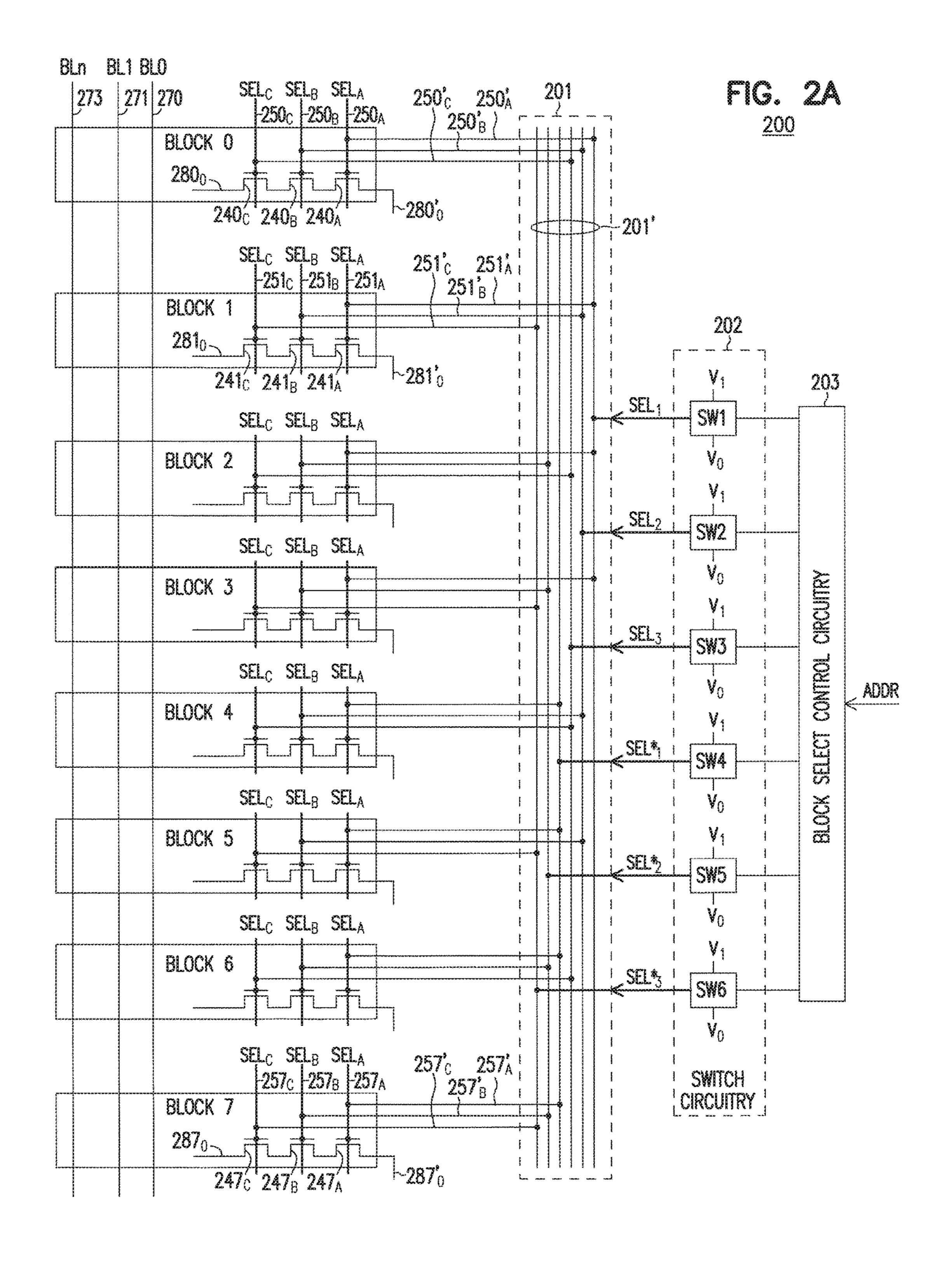

FIG. 2A shows a block diagram of a portion of a memory device including memory cell blocks and associated transistors, according to some embodiments described herein.

FIG. 2B is a chart showing unique combinations of signals based on a mapping of signals of each of the blocks of the memory device of FIG. 2A, according to some embodiments described herein.

FIG. 2C is a chart illustrating relationships between 30 voltages provided to the signals of the blocks of the memory device of FIG. 2A, according to some embodiments described herein.

FIG. 3A, FIG. 3B, and FIG. 3C are charts showing examples of different unique combinations of voltages provided to the signals of the blocks of the memory device of FIG. 2A if different blocks are selected during different example memory operations of the memory device of FIG. 2A, according to some embodiments described herein.

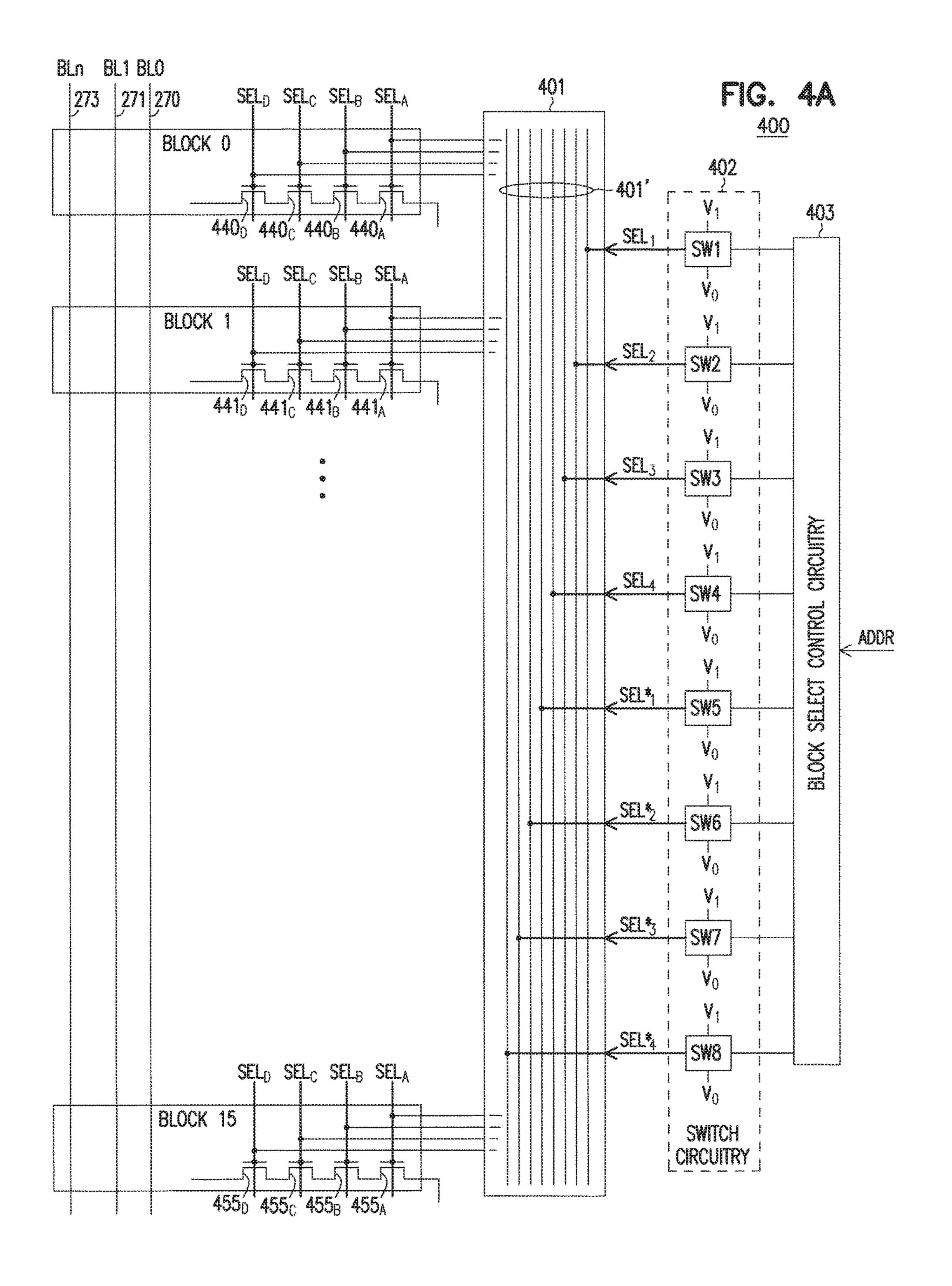

FIG. 4A shows a block diagram of a portion of another 40 memory device including a different number of blocks in comparison with the number of blocks of the memory device of FIG. 2A, according to some embodiments described herein.

FIG. 4B is a chart showing unique combinations of 45 signals based on a mapping of signals of each of the blocks of the memory device of FIG. 4A, according to some embodiments described herein.

FIG. 4C is a chart illustrating relationships between voltages provided to the signals of the blocks of the memory 50 device of FIG. 4A, according to some embodiments described herein.

FIG. **5** is a chart showing relationships between the numbers of blocks, transistor gate lines in each block, and switches in a memory device, according to some embodi- 55 ments described herein.

FIG. 6A shows a block diagram of the memory device of FIG. 2A including sub-blocks of a block of the memory device, according to some embodiments described herein.

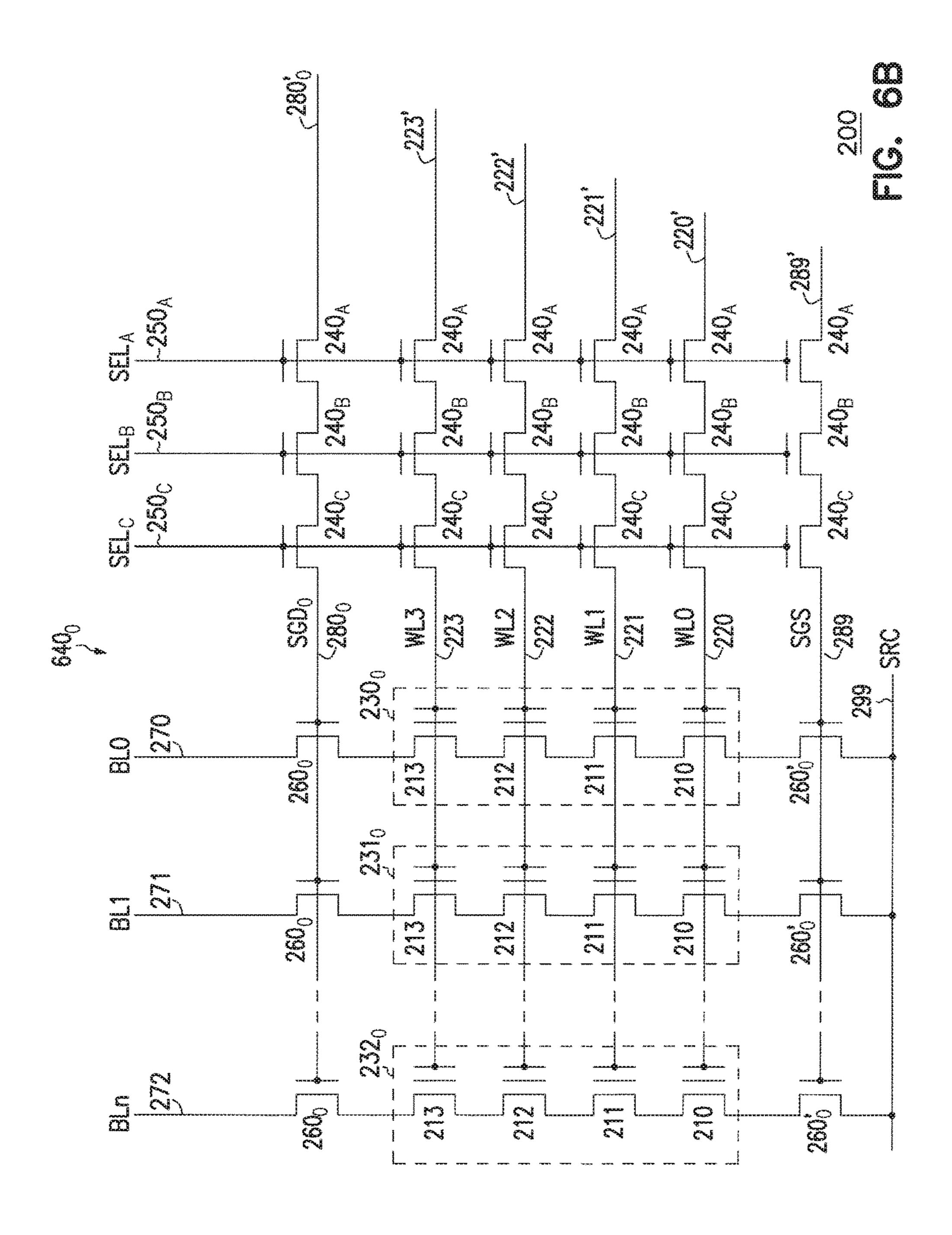

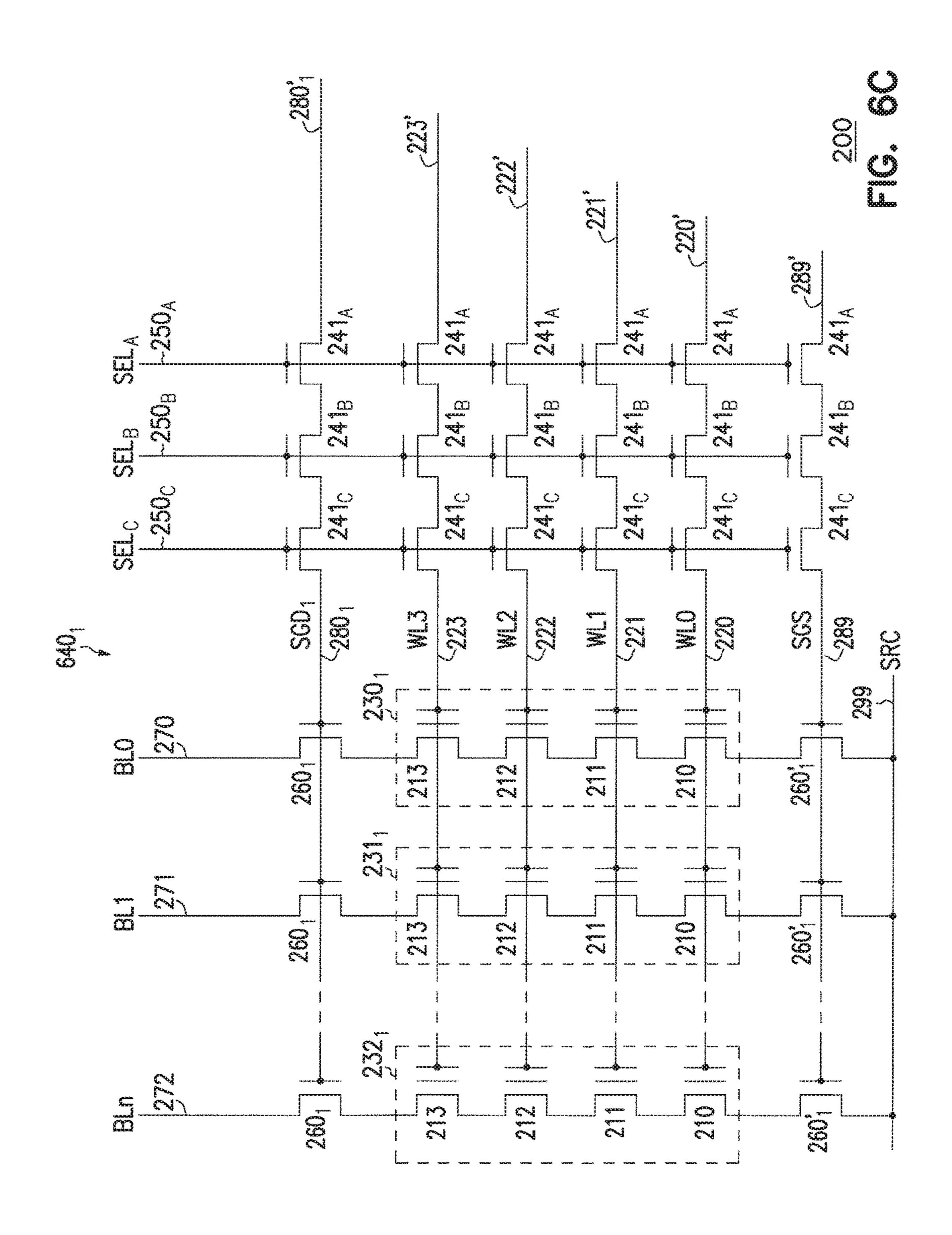

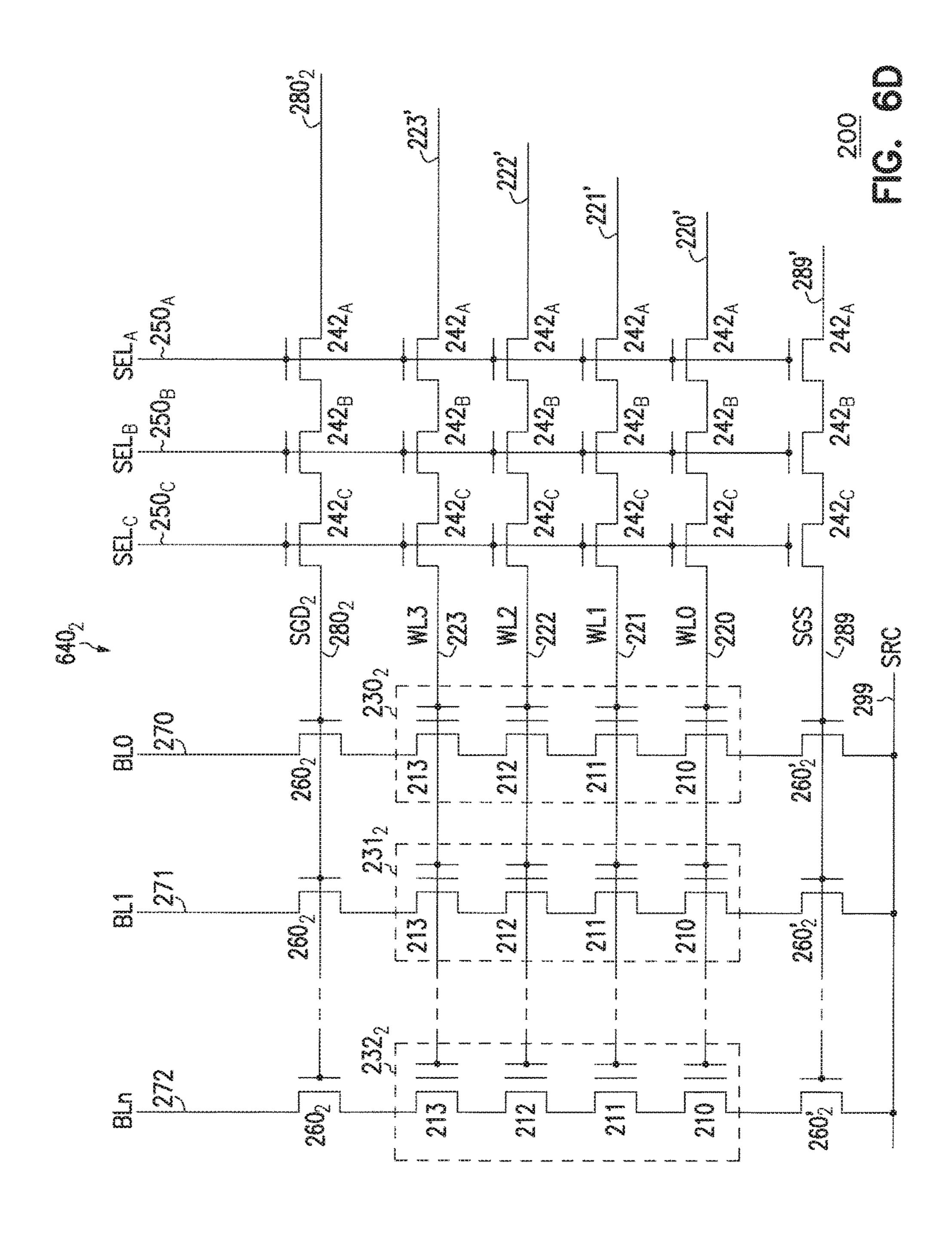

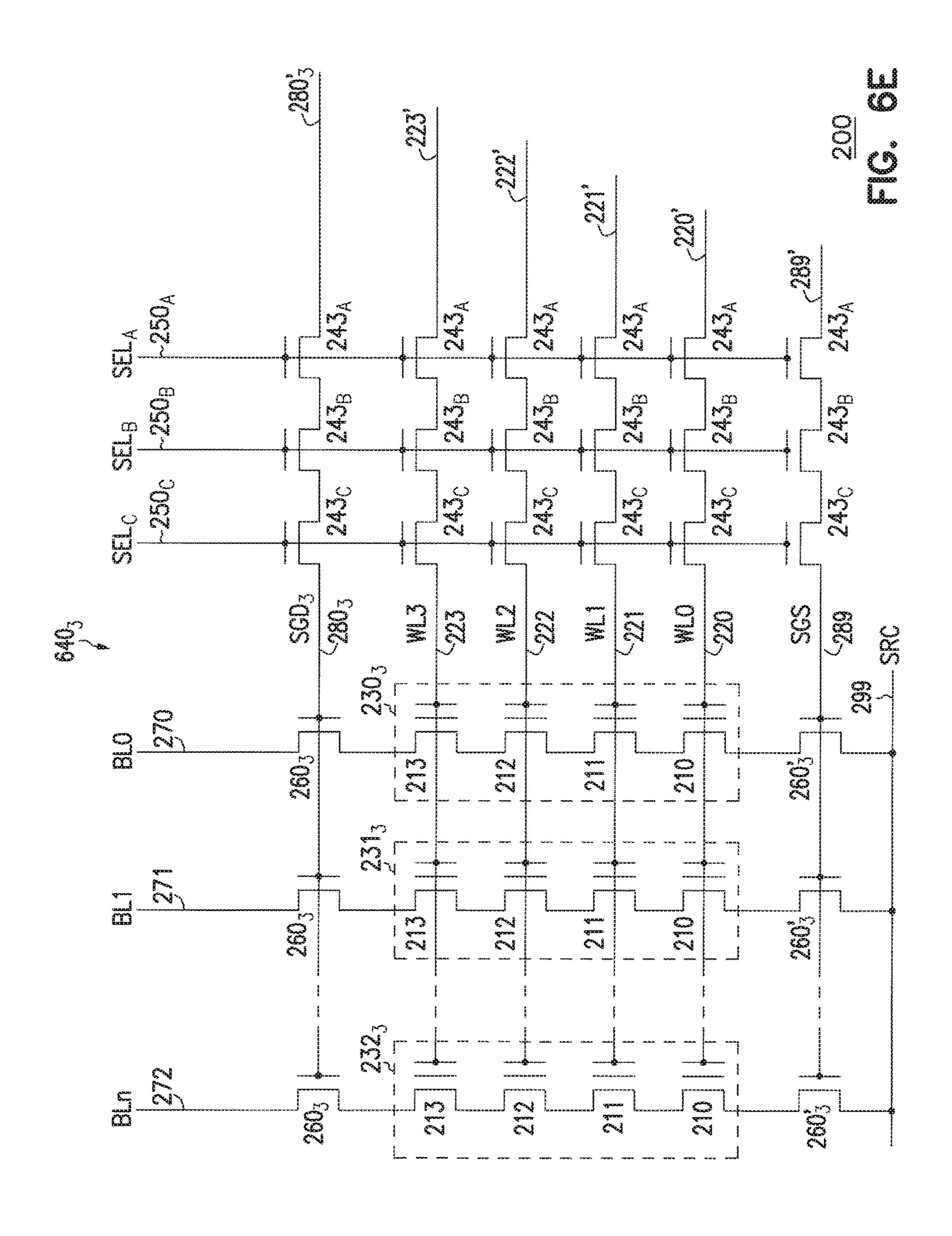

FIG. 6B, FIG. 6C, FIG. 6D, and FIG. 6E show schematic 60 diagrams of different sub-blocks of the block of the memory device of FIG. 6A, according to some embodiments described herein.

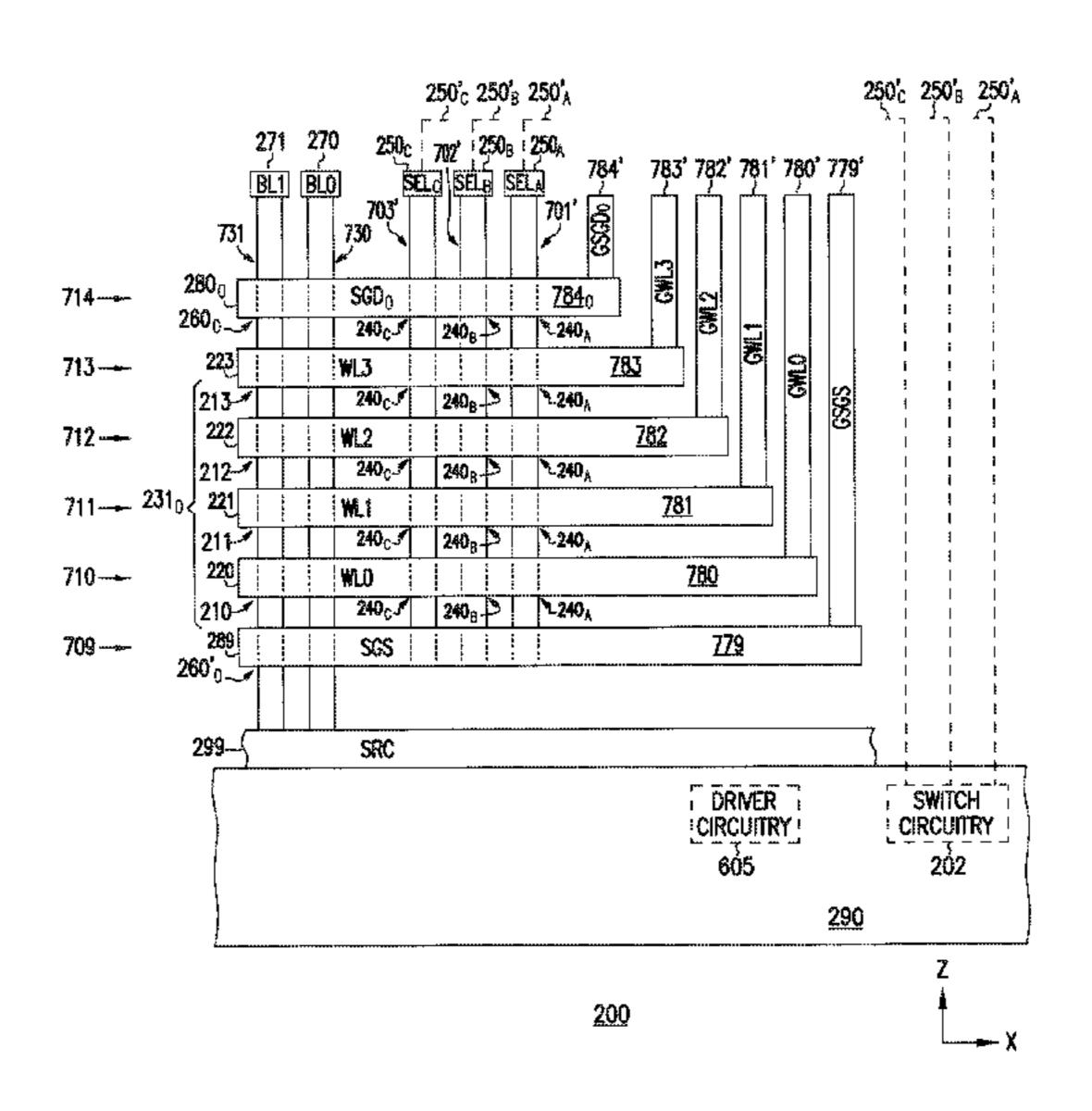

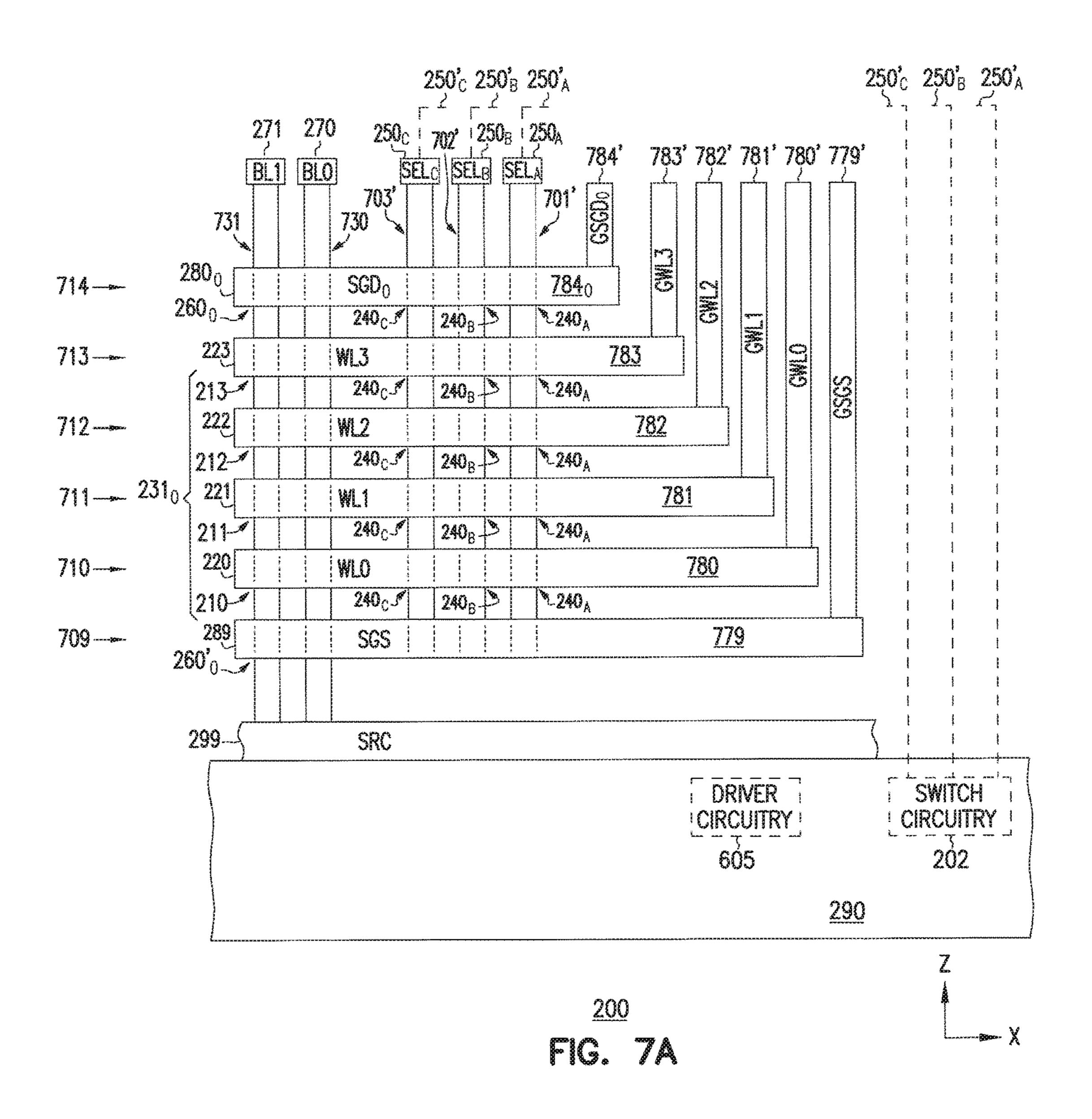

FIG. 7A shows a side view (in the x-z directions) of a structure of a portion of the memory device of FIG. 2A and 65 FIG. 6A through FIG. 6E, according to some embodiments described herein.

2

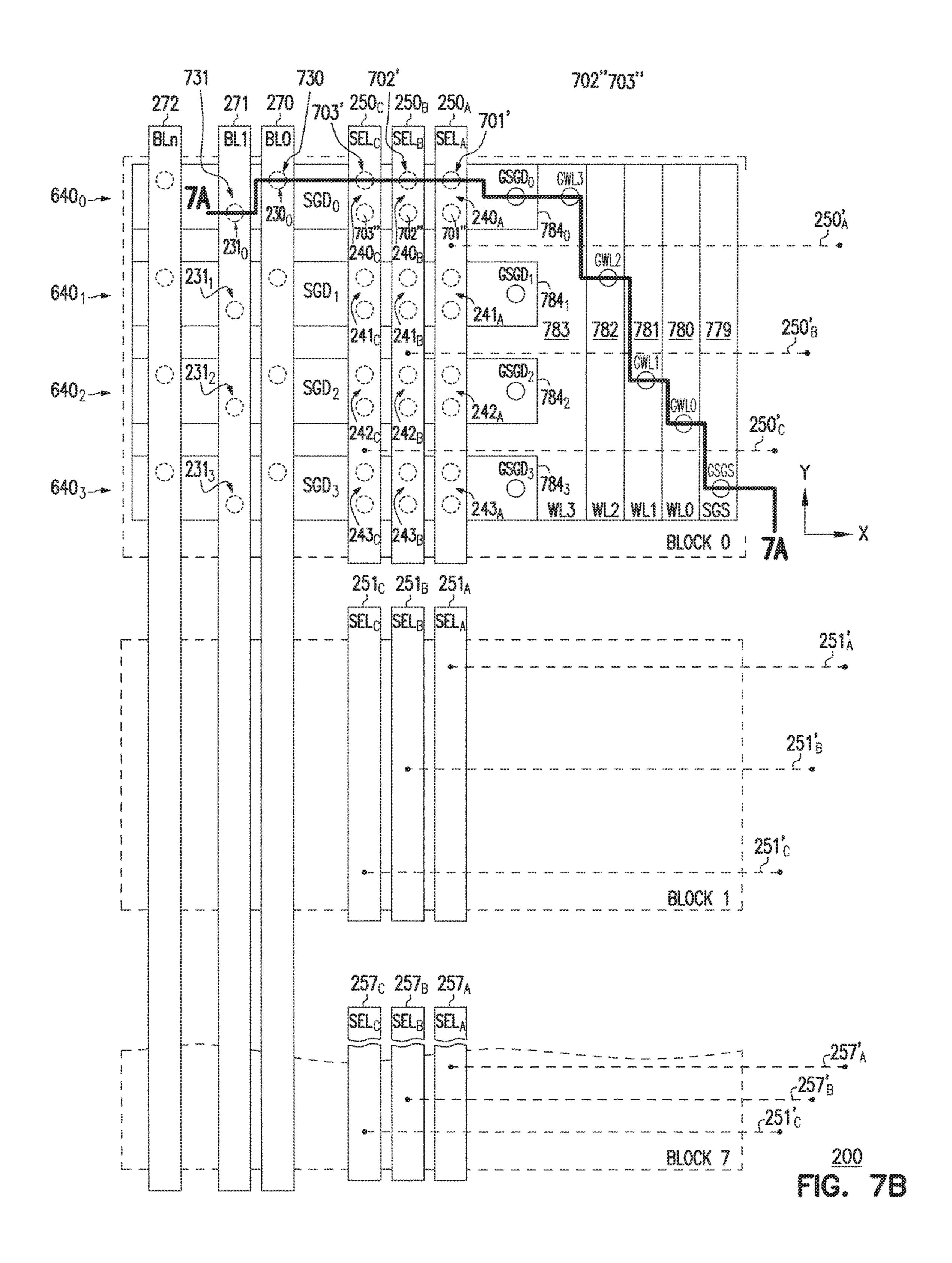

FIG. 7B shows a top view (in the x-y directions) of a structure of a portion of the memory device of FIG. 7A, according to some embodiments described herein.

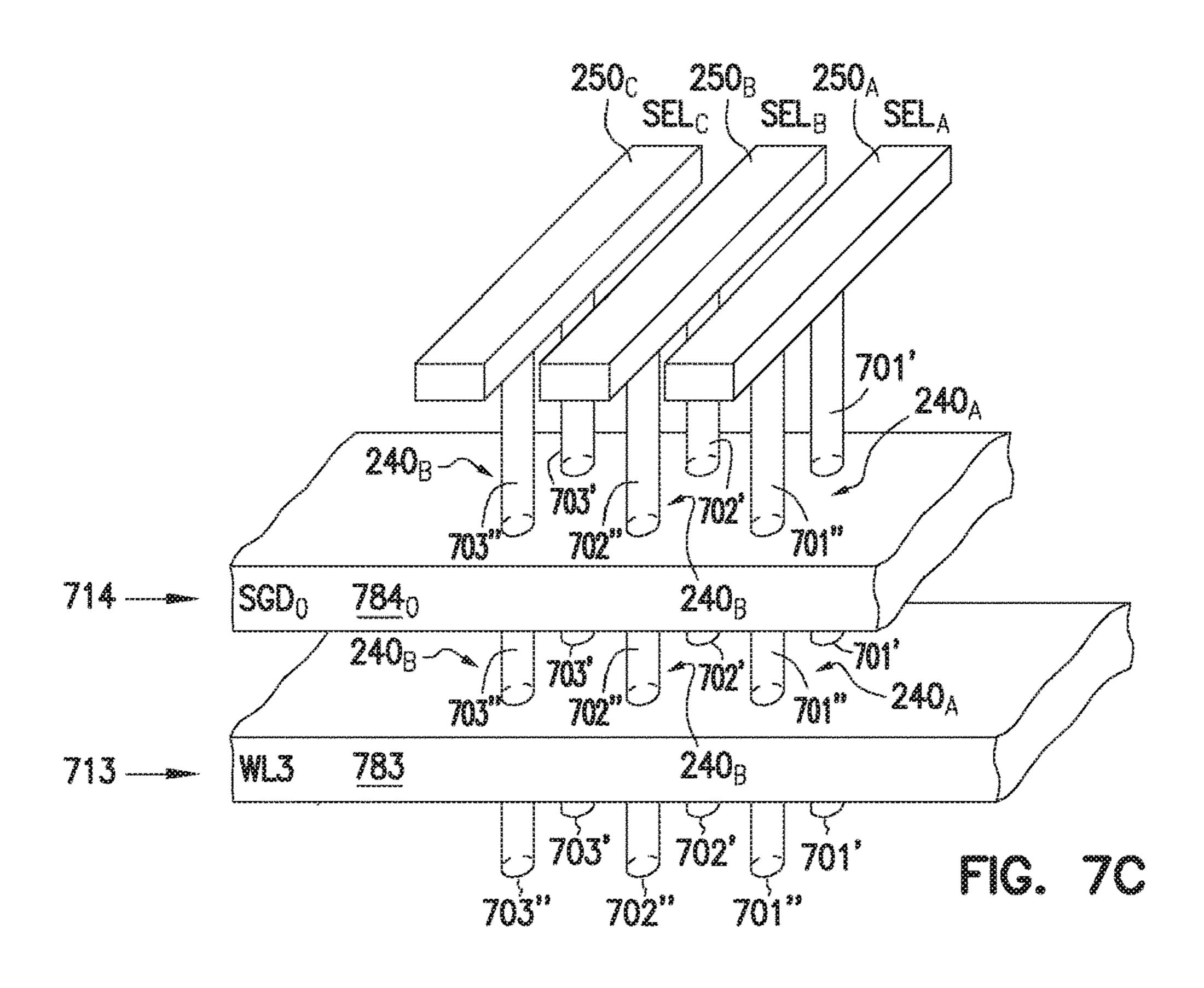

FIG. 7C shows a perspective view of a portion of the memory device of FIG. 7A and FIG. 7B including pass transistors and associated gate structures, according to some embodiments described herein.

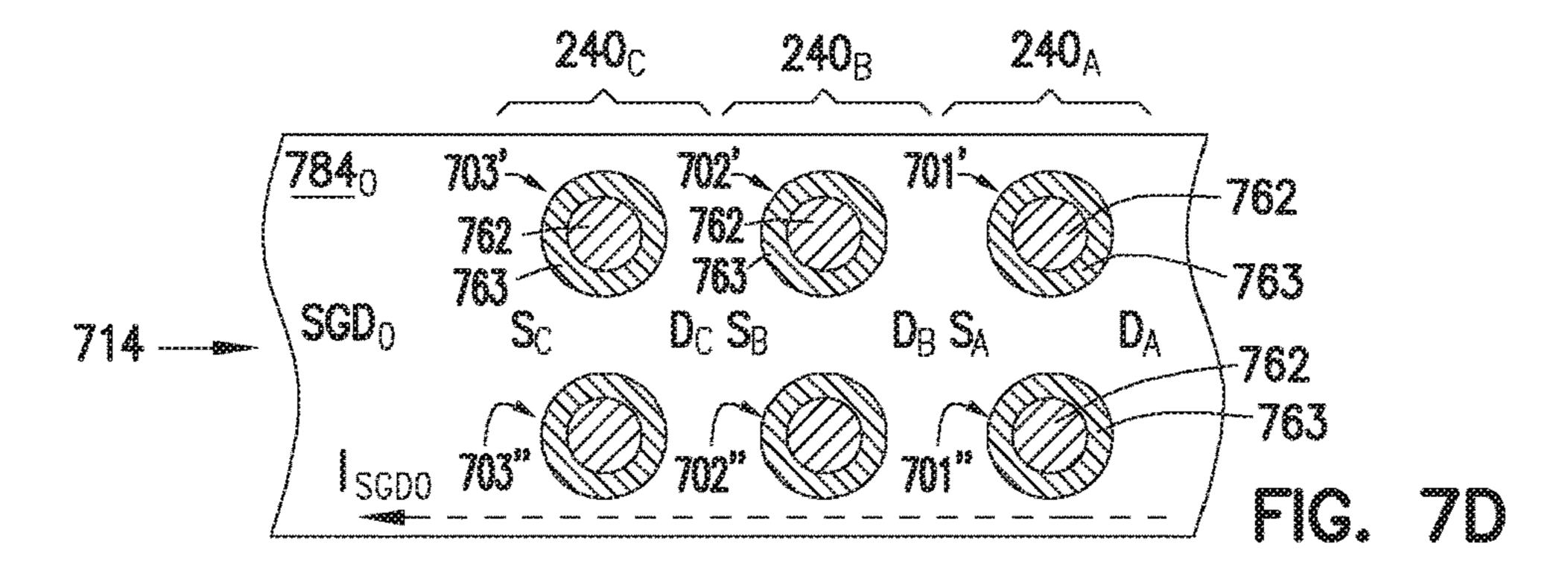

FIG. 7D shows a top view of a level (e.g., a tier) of the portion of the memory device of FIG. 7C including a group of pass transistors and a select line of the memory device, according to some embodiments described herein.

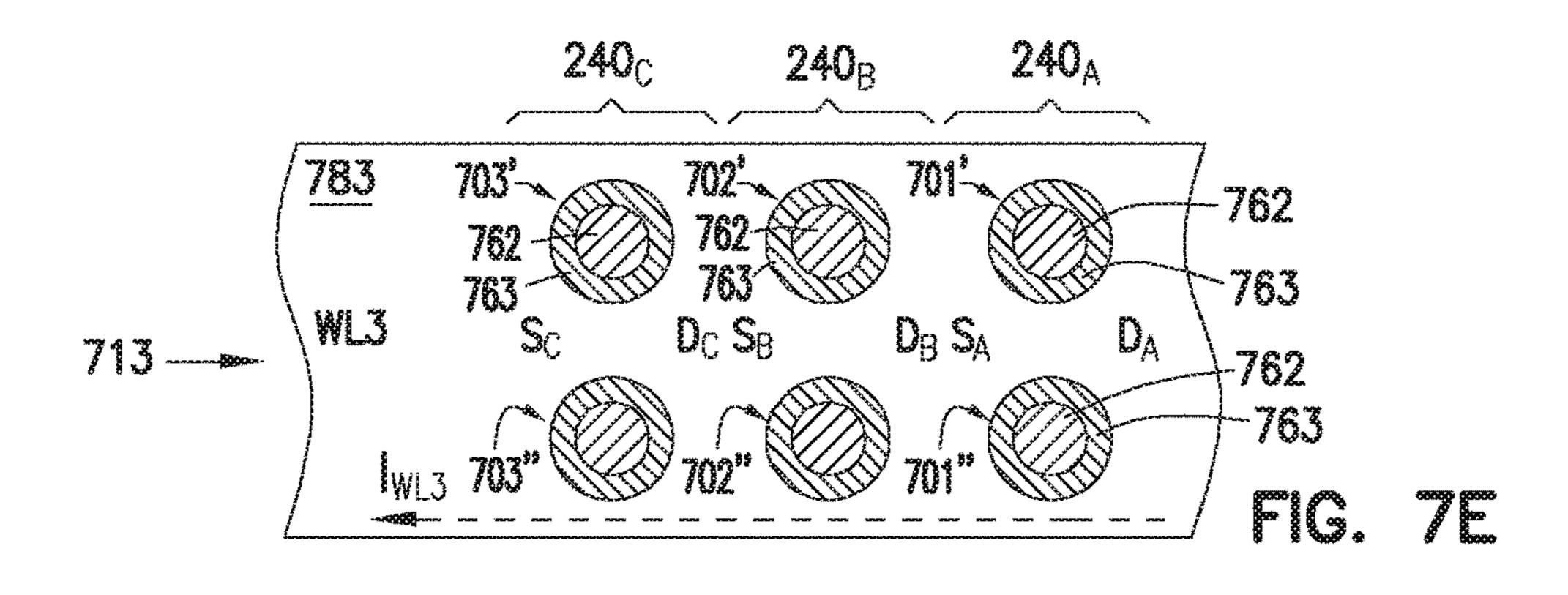

FIG. 7E shows a top view of another level (e.g., another tier) of the portion of the memory device of FIG. 7C including another group of pass transistors and a control line of the memory device, according to some embodiments described herein.

FIG. 8 is a flowchart showing a method of operating a memory device, according to some embodiments described herein.

#### DETAILED DESCRIPTION

FIG. 1 shows a block diagram of an apparatus in the form

of a memory device 100 including memory cells and pass

transistors formed in the same memory array (memory cell

array), according to some embodiments described herein.

Memory device 100 can include a memory array (or multiple memory arrays) 101 containing memory cells 110. In

the physical structure of memory device 100, memory cells

110 can be arranged vertically (e.g., stacked over each other)

over a substrate of memory device 100 (e.g., a semiconductor substrate of an IC chip that includes memory device

100). Memory cells 110 can include non-volatile cells. For

example, memory cells 110 can include floating gate

memory cells, charge trap memory cells, or other types of

non-volatile memory cells.

As shown in FIG. 1, memory cells 110 can be arranged in blocks (memory cell blocks), such as blocks 190 and 191. Each of blocks 190 and 191 can include sub-blocks. For example, block 190 can include sub-blocks 1900 and 1900, and block 191 can include sub-blocks 1910 and 1910. Each of sub-blocks 1900, 1900, 1910, and 1910, can include a combination of memory cells 110. FIG. 1 shows memory device 100 having two blocks 190 and 191 and two sub-blocks in each of blocks 190 and 191 as an example. Memory device 100 can have more than two blocks and more than two sub-blocks in each of the blocks.

As shown in FIG. 1, memory device 100 can include transistors (labeled as "Ts") 140 in the sub-blocks of each of blocks 190 and 191. Transistors 140 can be formed in the same memory array over the substrate of memory device 100 where memory cells 110 are formed. Transistors 140 can operate as pass transistors to provide signals to respective blocks (e.g., blocks 190 and 191) of memory device 100. Transistors 140 can include the transistors described in more detail with reference to FIG. 2A through FIG. 8.

As shown in FIG. 1, memory device 100 can include access lines (which can include word lines) 150 and data lines (which can include bit lines) 170. Access lines 150 can carry signals (e.g., word line signals) WL0 through WLm. Data lines 170 can carry signals (e.g., bit line signals) BL0 through BLn. Memory device 100 can use access lines 150 to selectively access sub-blocks 190<sub>0</sub>, 190<sub>n</sub>, 191<sub>0</sub>, and 191<sub>n</sub> of blocks 190 and 191 and data lines 170 to selectively exchange information (e.g., data) with memory cells 110 of blocks 190 and 191.

Memory device 100 can include an address register 107 to receive address information (e.g., address signals) ADDR on lines (e.g., address lines) 103. Memory device 100 can include row access circuitry 108 and column access circuitry 109 (e.g., part of decoder circuitry of memory device 100) 5 that can decode address information from address register **107**. Based on decoded address information, memory device 100 can determine which memory cells 110 of which sub-blocks of blocks 190 and 191 are to be accessed during a memory operation. Memory device 100 can perform a read 10 operation to read (e.g., sense) information (e.g., previously stored information) in memory cells 110, or a write (e.g., program) operation to store (e.g., program) information in memory cells 110. Memory device 100 can use data lines 170 associated with signals BL0 through BLn to provide 15 information to be stored in memory cells 110 or obtain information read (e.g., sensed) from memory cells 110. Memory device 100 can also perform an erase operation to erase information from some or all of memory cells 110 of blocks **190** and **191**.

Memory device 100 can include a control unit 118 (which can include components such as a state machine (e.g., finite state machine), register circuits, and other components) configured to control memory operations (e.g., read, write, and erase operations) of memory device 100 based on 25 control signals on lines 104. Examples of the control signals on lines 104 include one or more clock signals and other signals (e.g., a chip-enable signal CE#, a write-enable signal WE#) to indicate which operation (e.g., read, write, or erase operation) memory device 100 can perform.

Memory device 100 can include sense and buffer circuitry 120 that can include components such as sense amplifiers and page buffer circuits (e.g., data latches). Sense and buffer circuitry 120 can respond to signals BL\_SEL0 through buffer circuitry 120 can be configured to determine (e.g., by sensing) the value of information read from memory cells 110 (e.g., during a read operation) of blocks 190 and 191 and provide the value of the information to lines (e.g., global data lines) 175. Sense and buffer circuitry 120 can also be 40 configured to use signals on lines 175 to determine the value of information to be stored (e.g., programmed) in memory cells 110 of blocks 190 and 191 (e.g., during a write operation) based on the values (e.g., voltage values) of signals on lines 175 (e.g., during a write operation).

Memory device 100 can include input/output (I/O) circuitry 117 to exchange information between memory cells 110 of blocks 190 and 191 and lines (e.g., I/O lines) 105. Signals DQ0 through DQN on lines 105 can represent information read from or stored in memory cells 110 of 50 blocks 190 and 191. Lines 105 can include nodes within memory device 100 or pins (or solder balls) on a package where memory device 100 can reside. Other devices external to memory device 100 (e.g., a memory controller or a processor) can communicate with memory device 100 55 through lines 103, 104, and 105.

Memory device 100 can receive a supply voltage, including supply voltages Vcc and Vss. Supply voltage Vss can operate at a ground potential (e.g., having a value of approximately zero volts). Supply voltage Vcc can include 60 an external voltage supplied to memory device 100 from an external power source such as a battery or alternating current to direct current (AC-DC) converter circuitry.

Each of memory cells 110 can be programmed to store information representing a value of at most a single bit, or 65 a value of multiple bits such as two, three, four, or another number of bits. For example, each of memory cells 110 can

be programmed to store information representing a binary value "0" or "1" of a single bit. The single bit per cell is sometimes called a single-level cell. In another example, each of memory cells 110 can be programmed to store information representing a value for multiple bits, such as one of four possible values "00", "01", "10", and "11" of two bits, one of eight possible values "000", "001", "010", "011", "100", "101", "110", and "111" of three bits, or one of other values of another number of multiple bits. A cell that has the ability to store multiple bits is sometimes called a multi-level cell (or multi-state cell).

Memory device 100 can include a non-volatile memory device, such that memory cells 110 can retain information stored thereon when power (e.g., voltage Vcc, Vss, or both) is disconnected from memory device 100. For example, memory device 100 can be a flash memory device, such as a NAND flash (e.g., 3-directional (3-D) NAND) or a NOR flash memory device, or another kind of memory device, such as a variable resistance memory device (e.g., a phase 20 change memory device or a resistive RAM (Random Access Memory) device). One of ordinary skill in the art may recognize that memory device 100 may include other components, several of which are not shown in FIG. 1 so as not to obscure the example embodiments described herein.

At least a portion of memory device 100 can include structures and perform operations similar to or identical to the structures and operations of any of the memory devices described below with reference to FIG. 2A through FIG. 8.

Structuring and operating a memory device (e.g., memory device 100) as described herein allows the memory device to have improvements over some conventional memory devices. Such improvements include a lower number of sub-blocks, a lower number of pages per block, and a higher number of blocks for a given device area (e.g., pitch area). BL\_SELn from column access circuitry 109. Sense and 35 In comparison with some conventional memory devices, these improvements can lead to a lower energy consumption for charging access lines (e.g., word lines) during memory operations (e.g., read and write operations) and shorter time for some other memory operations (e.g., garbage collection operations) of memory device 100.

> FIG. 2A shows a block diagram of a portion of a memory device 200 including block 0 through block 7 (memory cell blocks) and associated transistors, according to some embodiments described herein. Memory device 200 can also 45 include data lines (e.g., bit lines) 270, 271, and 272 to carry respective signals (e.g., bit line signals) BL0, BL1, and BLn, routing circuitry 201, switch circuitry 202, and block select control circuitry 203. Memory device 200 can correspond to memory device 100, such that block 0 through block 7 can correspond to the blocks (e.g., block 190 and 191) of memory device 100 of FIG. 1. FIG. 2A shows memory device 200 including eight blocks 0 through 7 as an example. However, memory device 200 can include numerous blocks (e.g., hundreds or thousands of blocks).

Block 0 through block 7 share data lines 270, 271, and 272. During a memory operation (e.g., read or write operation) of memory device 200, only one block (e.g., a selected block) among block 0 through block 7 can be selected at a time. The selected block can exchange information (e.g., data) with data lines 270, 271, and 272. The blocks that are not selected are called unselected (e.g., deselected) blocks. For example, if block 0 is selected, then block 1 through block 7 are unselected (e.g., deselected) blocks. In another example, if block 1 is selected, then block 0 and block 2 through block 7 are unselected blocks.

In this description, a selected block is a block that is selected by memory device 200 to store information in (e.g.,

in a write operation) or read information from (e.g., in a read operation) a memory cell (or memory cells) of that selected block. An unselected block is a block that is not selected by memory device 200 during a memory operation. During a memory operation (e.g., performed on a selected block), 5 information may not be stored in or read from memory cells of an unselected block.

For simplicity, the following description focuses on block 0 and its associated components. Other blocks (e.g., block 1 through block 7) of memory device 200 have structures and 10 operations similar to that of block 0. The description of block 1 through block 7 follows the description of block 0.

As shown in FIG. 2A, block 0 can include transistors  $240_A$ ,  $240_B$ , and  $240_C$  coupled in series with each other and coupled in series between a select line  $280_0$  and a select line 15 **280**'<sub>0</sub>. Transistors **240**<sub>A</sub>, **240**<sub>B</sub>, and **240**<sub>C</sub> can be field effect transistors (FETs). Select line  $280_{\circ}$  can be one of local select lines (e.g., conductive lines that are mainly located in a memory cell array) of block 0. Select line 280' can be one of global select lines (e.g., conductive lines that are mainly 20 located outside a memory cell array) of block 0. Memory device 200 can provide a signal (e.g., voltage signal) to a global select line (e.g.,  $280'_{0}$ ). Transistors  $240_{A}$ ,  $240_{B}$ , and  $240_{\rm C}$  can be controlled (e.g., turned on) to pass the signal from the global select line (e.g., **280**'<sub>0</sub>) to a corresponding 25 local select line (e.g.,  $280_0$ ) if block 0 is a selected block. Thus, transistors  $240_A$ ,  $240_B$ , and  $240_C$  can be called pass transistors. Controlling of transistors  $240_A$ ,  $240_B$ , and  $240_C$ can be based on decoding of information ADDR (e.g., address information). Thus, transistors  $240_A$ ,  $240_B$ , and  $240_C$  30 can be alternatively called decoding transistors. Transistors  $240_A$ ,  $240_B$ , and  $240_C$  can correspond to some of transistors 140 in one of blocks 190 and 191 of memory device of FIG.

In FIG. 2A, block 0 also includes additional pass transis- 35 tors (not shown in FIG. 2A for simplicity) similar to transistors  $240_A$ ,  $240_B$ , and  $240_C$ . Detailed description of the pass transistors (e.g., transistors  $240_A$ ,  $240_B$ , and  $240_C$  and the additional pass transistors) and other components of block 0 is discussed below with reference to FIG. 6A 40 through FIG. 7E.

In FIG. 2A, memory device 200 can use select line  $280_{\odot}$ to control (e.g., turn on or turn off) a select gate (not shown in FIG. 2A) of block 0 in order to couple memory cell strings (not shown) of block 0 to respective data lines 270, 271, and 45 272 during memory operation if block 0 is a selected block. During a memory operation of memory device 200, all of transistors  $240_A$ ,  $240_B$ , and  $240_C$  can be turned on to form a conductive path (e.g., current path) between select lines **280**<sub>o</sub> and **280**'<sub>o</sub> (through the turned-on transistors **240**<sub>A</sub>, **240**<sub>8</sub>, 50 and  $240_C$ ) if block 0 is a selected block. The conductive path allows a signal provided on select line (e.g., global select line) 280' to be passed to select line (e.g., local select line)  $280_0$  in order to turn on the select gate (not shown) of block **0**. Turning on the select gate is part of a memory operation 55 of storing information in or reading information from memory cells of the selected block (e.g., block 0). In FIG. 2A, at least one (meaning one, two, or all three) of transistors  $240_A$ ,  $240_B$ , and  $240_C$  can be turned off in order not to form a conductive path (e.g., break a conductive path) between 60 select lines 280<sub>0</sub> and 280'<sub>0</sub> if block 0 is an unselected (e.g., deselected) block during a memory operation of memory device 200.

As shown in FIG. 2A, block 0 can include separate transistor gate lines  $250_A$ ,  $250_B$ , and  $250_C$  that can carry 65 respective signals (e.g., block select signals)  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$ . Transistor gate lines  $250_A$ ,  $250_B$ , and  $250_C$  can be

6

structured as conductive lines that are electrically uncoupled to each other. In this description, "electrically uncoupled to each other" means "not electrically coupled to each other". Transistors  $240_A$ ,  $240_B$ , and  $240_C$  can have separate gates (transistor gates that are electrically uncoupled to each other) coupled to respective transistor gate lines  $250_A$ ,  $250_B$ , and  $250_C$ . Memory device 200 can use transistor gate lines  $250_A$ ,  $250_B$ , and  $250_C$  to control (e.g., turn on or turn off) respective transistors  $240_A$ ,  $240_B$ , and  $240_C$ .

Signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> can be provided with different voltage values, depending on whether block  $\bf 0$  is a selected block during a memory operation of memory device  $\bf 200$ . For example, each of signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> can be provided with a voltage (e.g., a positive voltage) to turn on all of transistors  $\bf 240_A$ ,  $\bf 240_B$ , and  $\bf 240_C$  in order to form a conductive path between select lines  $\bf 280_0$  and  $\bf 280_0$  if block  $\bf 0$  is a selected block during that memory operation. In another example, at least one of signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> can be provided with another voltage (e.g., zero volts (ground) or alternatively a negative voltage) to turn off at least one of transistors  $\bf 240_A$ ,  $\bf 240_B$ , and  $\bf 240_C$  in order not to form (e.g., or to break) a conductive path between select lines  $\bf 280_0$  and  $\bf 280_0$  if block  $\bf 0$  is an unselected block during that memory operation.

As shown in FIG. 2A, routing circuitry 201 can include conductive lines 201' and conductive lines 250'<sub>A</sub>, and 250'<sub>B</sub>, and 250'<sub>C</sub> coupled to conductive lines 201' and conductive lines 250'<sub>A</sub>, 250'<sub>B</sub>, and 250'<sub>C</sub> coupled to conductive lines 201' and to respective transistor gate lines 250<sub>A</sub>, 250<sub>B</sub>, and 250<sub>C</sub> of block 0. The values of voltages provided to signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> on respective transistor gate lines 250<sub>A</sub>, 250<sub>B</sub>, and 250<sub>C</sub> are based on the values of voltages provided to signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> on respective transistor gate lines 250<sub>A</sub>, 250<sub>B</sub>, and 250<sub>C</sub> are based on the values of voltages provided to signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>C</sub> and signals SEL<sub>2</sub>, SEL\*<sub>3</sub>, SEL\*<sub>4</sub>, SEL\*<sub>4</sub>,

In FIG. 2A, switch circuitry 202 can operate to selectively provide different voltages to signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub>, depending on which block among block 0 through block 7 is selected during a memory operation. Switch circuitry 202 can include switches SW1 through SW6. Each of switches SW1 through SW6 can operate to provide either a voltage V0 or a voltage V1 to a respective signal among signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub>. For example, switch SW1 can provide either voltage V0 or voltage V1 to signal  $SEL_1$ . In another example, switch SW4 can to provide either voltage V0 or voltage V1 to signal SEL\*<sub>1</sub>. The value of voltage V0 is less than the value of voltage V1. Voltage V0 can be zero or can have a negative value (that can cause transistors  $240_A$ ,  $240_B$ , and 240<sub>C</sub> to turn off). Voltage V1 can have a positive value (that can cause transistors  $240_A$ ,  $240_B$ , and  $240_C$  to turn on).

Switches SW1 and SW4 can operate such that signal SEL<sub>1</sub> (provided at the output node of switch SW1) and signal SEL\*<sub>1</sub> (provided at the output node of switch SW4) can have different voltages (e.g., V0 and V1, respectively, or V1 and V0, respectively) during the same time interval of a memory operation of memory device 200. For example, if signal SEL<sub>1</sub> is provided with voltage V0 during a particular time interval, then signal SEL\*<sub>1</sub> is provided with voltage V1 during that particular time interval. In another example, if signal SEL<sub>1</sub> is provided with voltage V1 during a particular time interval, then signal SEL\*<sub>1</sub> is provided with voltage V0 during that particular time interval.

Similarly, switches SW2 and SW5 can operate such that signals SEL<sub>2</sub> and SEL\*<sub>2</sub> can have different voltages (e.g., V0 and V1, respectively, or V1 and V0, respectively) during a

particular time interval of a memory operation of memory device 200. Switches SW3 and SW6 can operate such that signals SEL<sub>3</sub> and SEL\*<sub>3</sub> can have different voltages (e.g., V0 and V1, respectively, or V1 and V0, respectively) during a particular time interval of a memory operation of memory 5 device 200.

Block select control circuitry 203 can control switches SW1 through SW6 based on information ADDR in order to cause each of switches SW1 through SW6 to provide either voltage V0 or V1 (e.g., based on decoding of information 10 ADDR by block select control circuitry 203). Information ADDR can be provided by an address register of memory device 100 (e.g., similar to address register 107 of FIG. 1). In FIG. 2A, controlling switches SW1 through SW6 can include causing each of switches SW1 through SW6 to 15 couple its output node (e.g., a node that provides one of signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub>) to either the node that has voltage V0 or the node that has voltage V1.

Information ADDR can have a value (e.g., a value of a 20 combination of bits) to indicate which block among block 0 through block 7 is selected during a memory operation. For example, information ADDR can have one value if block 0 is selected and another value if block 1 is selected, and so on.

The above description concentrates on block 0 of memory 25 device 200 in FIG. 2A. Similarly, each of block 1 through block 7 of memory device 200 has structures and operations similar to that of block 0 described above.

For example, as shown in FIG. 2A, block 1 can include transistors (e.g., pass transistors)  $241_A$ ,  $241_B$ , and  $241_C$  30 coupled in series with each other and coupled in series between a select line  $281_0$  (e.g., one of local select lines of block 1) and a select line 281'<sub>0</sub> (e.g., one of the global select lines of block 1). Memory device 200 can use select line to couple memory cell strings (not shown) of block 1 to respective data lines 270, 271, and 272 during a memory operation if block 1 is a selected block.

Block 1 can include separate transistor gate lines  $251_{A}$ ,  $251_B$ , and  $251_C$  (conductive lines that are electrically 40 uncoupled to each other) that can carry respective signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$ , which are different from signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$  of block 0. Transistors 241<sub>A</sub>, 241<sub>B</sub>, and 241<sub>c</sub> can have separate gates (transistor gates that are electrically uncoupled to each other) coupled to respective 45 transistor gate lines  $251_A$ ,  $251_B$ , and  $251_C$ . Memory device 200 can use transistor gate lines  $251_A$ ,  $251_B$ , and  $251_C$  to control (e.g., turn on or turn off) respective transistors  $241_{A}$ ,  $241_R$ , and  $241_C$ . During a memory operation of memory device 200, all of transistors  $241_A$ ,  $241_B$ , and  $241_C$  can be 50 turned on to form a conductive path (e.g., current path) between select lines  $281_0$  and  $281_0$  (through the turned-on transistors  $241_A$ ,  $241_B$ , and  $241_C$ ) if block 1 is a selected block. At least one of transistors  $241_A$ ,  $241_B$ , and  $241_C$  can be turned off in order not to form a conductive path (e.g., 55) break a conductive path) between select lines 281<sub>0</sub> and 281'<sub>0</sub> if block 1 is an unselected (e.g., deselected) block during a memory operation of memory device 200.

In another example shown in FIG. 2A, block 7 can include transistors  $247_A$ ,  $247_B$ , and  $247_C$  (e.g., pass transistors) 60 coupled in series with each other and coupled in series between a select line 287<sub>0</sub> (e.g., one of the local select lines of block 7) and a select line 287'<sub>0</sub> (e.g., one of the global select lines of block 7). Memory device 200 can use select line 287<sub>0</sub> to control a select gate (not shown) of block 7 in 65 order to couple memory cell strings (not shown) of block 7 to respective data lines 270, 271, and 272.

Block 7 can include separate transistor gate lines  $257_{A}$ ,  $257_B$ , and  $257_C$  (conductive lines that are electrically uncoupled to each other) that can carry respective signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$ , which are different from signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$  of block 0 and block 1. Transistors  $247_A$ ,  $247_B$ , and  $247_C$  can have separate gates (transistor gates that are electrically uncoupled to each other) coupled to respective transistor gate lines  $257_A$ ,  $257_B$ , and  $257_C$ . Memory device 200 can use transistor gate lines  $257_A$ ,  $257_B$ , and 257<sub>C</sub> to control (e.g., turn on or turn off) respective transistors  $247_A$ ,  $247_B$ , and  $247_C$ . During a memory operation of memory device 200, all of transistors  $247_A$ ,  $247_B$ , and 247<sub>C</sub> can be turned on to form a conductive path (e.g., current path) between select lines 287<sub>0</sub> and 287'<sub>0</sub> (through the turned-on transistors  $247_A$ ,  $247_B$ , and  $247_C$ ) if block 7 is a selected block. At least one of transistors  $247_A$ ,  $247_B$ , and 247<sub>c</sub> can be turned off in order not to form a conductive path (e.g., break a conductive path) between select lines 287<sub>0</sub> and 287'<sub>0</sub> if block 7 is an unselected (e.g., deselected) block during a memory operation of memory device 200.

As shown in FIG. 2A, transistor select lines (e.g.,  $250_{A}$ ,  $250_B$ , and  $250_C$ ) of one block (e.g., block 0) are separate from (e.g., electrically uncoupled to) transistor select lines (e.g.,  $251_A$ ,  $251_B$ , and  $251_C$ ) of another block (e.g., block 1). For simplicity, the same labels (e.g.,  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$ ) are given for the signals (e.g., signals  $SEL_A$ ,  $SEL_B$ , and SEL<sub>C</sub>) provided to transistor gate lines of block 0 through block 7. However, during a memory operation of memory device 200, signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$  of one block (e.g., block 0) are provided with voltages different from the voltages provided to signals  $SEL_A$ ,  $SEL_B$ , and SEL<sub>C</sub> of other blocks (e.g., block 1 through block 7). This difference in voltages allows all of the pass transistors of only one of block 0 through block 7 (e.g., a selected block) 281<sub>0</sub> to control a select gate (not shown) of block 1 in order 35 to be turned on during a memory operation of memory device 200, so that only one of block 0 through block 7 can be allowed to exchange information with data lines 270, 271, and 272 during that memory operation.

> FIG. 2B is a chart (e.g., table) 245 showing a unique combination of signals based on a mapping of signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$  of each of block 0 through block 7 and respectively signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*3, according to some embodiments described herein. The physical connections between transistor gate lines (e.g.,  $250_A$ ,  $250_B$ , and  $250_C$ ) of each of block 0 through block 7 and conductive lines 201' of routing circuitry 201 in FIG. 2A can be based on the mapping shown in chart **245** of FIG. **2**B.

> FIG. 2B shows an example of eight unique combinations of six different signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and  $SEL_3$ . Signals  $SEL_A$ ,  $SEL_B$ , and SEL of each of block 0 through block 7 can be mapped (e.g., assigned) to a unique combination of signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub>. For example, signals SEL<sub>4</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> of block 0 can be mapped to signals SEL<sub>1</sub>, SEL<sub>2</sub>, and SEL<sub>3</sub>. In another example, signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$  of block 1 can be mapped to signals SEL<sub>1</sub>, SEL<sub>2</sub>, and SEL\*<sub>3</sub>. In a further example, signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$  of block 2 can be mapped to signals SEL<sub>1</sub>, SEL\*<sub>2</sub>, and SEL<sub>3</sub>. As described above, during a memory operation of memory device 200, signals SEL<sub>1</sub> and SEL\*<sub>1</sub> can be provided with different voltages (e.g., V0 and V1), signals SEL, and SEL\*, can be provided with different voltages (e.g., V0 and V1), and signals SEL<sub>3</sub> and SEL\*<sub>3</sub> can be provided with different voltages (e.g., V0 and V1).

FIG. 2C shows a chart illustrating relationships between voltages provided to signals SEL<sub>1</sub>, SEL<sub>2</sub>, and SEL<sub>3</sub> and voltages provided to signals SEL\*1, SEL\*2, and SEL\*3 of FIG. 2A and FIG. 2B, according to some embodiments described herein. Based on chart 245 in FIG. 2B and the relationships between signals SEL<sub>1</sub>, SEL<sub>2</sub>, and SEL<sub>3</sub> and SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub> in FIG. 2C, memory device 200 can determine which voltage (e.g., either V0 or V1) to provide to each of signals SEL<sub>1</sub>, SEL<sub>2</sub>, and SEL<sub>3</sub> and SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub>, so that all pass transistors (e.g., 240<sub>A</sub>, 240<sub>B</sub>, and 240<sub>C</sub>) of only the selected block among block 0 through block 7 are turned on.

FIG. 3A is a chart 301 showing an example of different unique combinations of voltages V0 and V1 provided to signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$  if block 0 is selected (i.e., blocks 1 through block 7 are unselected) during an example memory operation of memory device 200 of FIG. 2A, 15 provided with voltage V0. according to some embodiments described herein. In this example, since block 0 is selected, memory device 200 can cause all transistors  $240_A$ ,  $240_B$ , and  $240_C$  (FIG. 2A) of block **0** to turn on. Thus, each of signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$ in FIG. 2A (provided to transistor gate lines  $250_A$ ,  $250_B$ , and 20250<sub>C</sub> that control transistors 240<sub>A</sub>, 240<sub>B</sub>, and 240<sub>C</sub>, respectively) can be provided with voltage V1 to turn on all of transistors  $240_A$ ,  $240_B$ , and  $240_C$  in order to form a conductive path between a local select line (e.g.,  $280_{\circ}$ ) and a global select line (e.g., 280'<sub>0</sub>) in block 0. Therefore, in this example, <sup>25</sup> memory device 200 can cause switch SW1 (FIG. 2A) to couple its output node (e.g., a node that provides signal SEL<sub>1</sub>) to the node that has voltage V1 in order to provide voltage V1 to signal SEL<sub>1</sub>. This in turn provides voltage V1 to signal  $SEL_A$  because transistor gate line  $250_A$  is coupled <sup>30</sup> off. to one of conductive lines 201 that provides signal SEL<sub>1</sub> (as shown in FIG. 2A). Similarly, in this example, memory device 200 can cause each of switches SW2 and SW3 to couple their respective output nodes (e.g., nodes that provide signals SEL<sub>2</sub> and SEL<sub>3</sub>) to the node that has voltage V1 in order to provide voltage V1 to each of signals SEL<sub>2</sub> and SEL<sub>3</sub>. This in turn provides voltage V1 to each of signals  $SEL_B$  and  $SEL_C$  because transistor gate lines 250S and 250<sub>C</sub> are coupled to respective conductive lines (among conduc- 40 tive lines 201) that provide signal SEL<sub>2</sub> and SEL<sub>3</sub> (as shown in FIG. **2**A).

FIG. 3A shows that each of signals  $SEL_A$ ,  $SEL_B$ , and SEL<sub>C</sub> of block 0 (the selected block in the above example) is provided with voltage V1 in order to turn on all of the 45 off. transistors (e.g., pass transistors)  $240_A$ ,  $240_B$ , and  $240_C$  of block 0, as described above. In the above example where block 0 is selected, block 1 through block 7 are unselected. Thus, at least one pass transistors in each of block 1 through block 7 can be turned off in order not to form a conductive 50 path between a local select line and a global select line of the unselected block. In the example where block 0 is selected, at least one of transistors  $241_A$ ,  $241_B$ , and  $241_C$  of block 1 in FIG. 2A can be turned off, and at least one of transistors  $247_A$ ,  $247_B$ , and  $247_C$  of block 7 in FIG. 2A can be turned 55 off. FIG. 3A shows that at least one of signals  $SEL_A$ ,  $SEL_B$ , and SEL<sub>C</sub> of each of block 1 through block 7 is provided with voltage V0. This means that at least one pass transistor (i.e., the transistor provided with voltage V0) in each of block 1 through block 7 can be turned off. As shown in FIG. 60 3A, up to two of signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$  may be provided with voltage V0 in an unselected block. Thus, up to two of the pass transistors (e.g., two of transistors  $240_{A}$ ,  $240_B$ , and  $240_C$ ) in an unselected block may be turned on (i.e., the transistors provided with voltage V1). However, 65 since at least one of the pass transistors in an unselected block is turned off, no conductive path may be formed

through the pass transistors (e.g., through transistors  $240_A$ ,  $240_B$ , and  $240_C$ ) because at least one of the pass transistors is turned off.

Thus, in the above example where block 0 is selected, memory device 200 can cause at least one of switches SW4, SW5, and SW6 to couple their respective output nodes (e.g., nodes that provide signals SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub>) to the node that has voltage V0 in order to provide voltage V0 to at least one of signals SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub>. Therefore, at least one of signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> of block 1 through block 7 can also be provided with voltage V0. This allows at least one of the pass transistors of block 1 through 7 to turn off. As shown in FIG. 3A, at least one of signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> of blocks block 1 through block 7 is provided with voltage V0.

FIG. 3B is a chart 302 showing an example of different unique combinations of voltages V0 and V1 provided to signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> if block 1 is selected (i.e., block 0 and block 2 through block 7 are unselected) during another example memory operation of memory device 200 of FIG. 2A, according to some embodiments described herein. Similar to the example associated with FIG. 3A, each of signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> of block 1 (selected block) is provided with voltage V1 while at least one of signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> of block 0 and block 2 through block 7 is provided with voltage V0. Thus, in this example, all of transistors 241<sub>A</sub>, 241<sub>B</sub>, and 241<sub>C</sub> of block 1 are turned on while at least one of the pass transistors of each of block 0 and block 2 through block 7 (unselected blocks) is turned off.

FIG. 3C is a chart 303 showing an example of different unique combinations of voltages V0 and V1 provided to signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> if block 4 is selected (i.e., block 1, block 2, and block 3 through block 7 are unselected) during another example memory operation of memory device 200 of FIG. 2A, according to some embodiments described herein. As shown in FIG. 3C, each of signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> of block 4 (selected block) is provided with voltage V1 while at least one of signals SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub> of block 1, block 2, and block 3 through block 7 is provided with voltage V0. Thus, in this example, all of the pass transistors of block 4 are turned on while at least one of the pass transistors of each of block 1, block 2, and block 3 through block 3 through block 7 (unselected blocks) is turned off

FIG. 2A through FIG. 3C describe an example of memory device 200 having a certain number of components (e.g., blocks, pass transistors, transistor gate lines, and switches). However, the number of such components can vary.

FIG. 4A shows a block diagram of a portion of a memory device 400 including blocks (memory cell blocks) 0 through 15 and associated transistors (e.g., pass transistors 440<sub>A</sub>, 440<sub>B</sub>, 440<sub>C</sub>, 440<sub>D</sub>, 441<sub>A</sub>, 441<sub>B</sub>, 441<sub>C</sub>, and 441<sub>D</sub>, and 455<sub>A</sub>, 455<sub>B</sub>, 455<sub>C</sub>, and 455<sub>D</sub>), according to some embodiments described herein. Memory device 400 can include data lines 270, 271, and 272 to carry respective signals BL0, BL1, and BLn, and routing circuitry 401, switch circuitry 402, and block select control circuitry 403. Memory device 400 can include similar or identical elements as those shown in FIG. 2A. Thus, similar or the same components between memory devices 200 and 400 are not repeated.

Differences between memory devices 200 and 400 include a difference in the numbers of blocks, pass transistors, transistor gate lines and associated signals (e.g., block select signals) SEL<sub>A</sub>, SEL<sub>B</sub>, SEL<sub>C</sub>, and SEL<sub>D</sub>, and switches SW1 through SW8. For example, memory device 400 can include 16 blocks (block 0 through block 15), four pass

transistors (e.g., 440<sub>A</sub>, 440<sub>B</sub>, 440<sub>C</sub>, and 440<sub>D</sub>; or 441<sub>A</sub>, 441<sub>B</sub>, 441<sub>C</sub>, and 441<sub>D</sub>: or 455<sub>A</sub>, 455<sub>B</sub>, 455<sub>C</sub>, and 455<sub>D</sub>), in each block; four transistor gate lines and four associated signals SEL<sub>A</sub>, SEL<sub>B</sub>, SEL<sub>C</sub>, and SEL<sub>D</sub> in each block; eight switches SW1 through SW8 and eight associated signals SEL<sub>1</sub>, SEL<sub>2</sub>, 5 SEL<sub>3</sub>, and SEL<sub>4</sub>, and SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, SEL\*<sub>3</sub>, and SEL\*<sub>4</sub>. For simplicity, details of connections between transistor gate lines of blocks 0 through 15 and conductive lines 401' of routing circuitry 401 are omitted from FIG. 4A. However, such connections can be based on the chart shown in FIG. 10 4B.

FIG. 4B is a chart (e.g., table) 445 showing unique combinations of signals based on a mapping of SEL<sub>A</sub>, SEL<sub>B</sub>, SEL<sub>C</sub>, and SEL<sub>D</sub> of each of block 0 through block 15 and signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL<sub>4</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, SEL\*<sub>3</sub>, 15 and SEL\*<sub>4</sub> of FIG. 4A, according to some embodiments described herein. FIG. 4B shows an example of 16 unique combinations of eight different signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL<sub>4</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, SEL\*<sub>3</sub>, and SEL\*<sub>4</sub>. Signals SEL<sub>A</sub>, SEL<sub>B</sub>, SEL<sub>C</sub>, and SEL<sub>D</sub> of each of block 0 through block 15 20 can be mapped to a unique combination of signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL<sub>4</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, SEL\*<sub>3</sub>, and SEL\*<sub>4</sub>. This allows all of the pass transistors of only the selected block among block 0 through block 15 to turn on during a memory operation of memory device 400.

FIG. 4C shows charts illustrating relationships between voltages provided to signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, and SEL<sub>4</sub> and voltages provided to signals SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, SEL\*<sub>3</sub>, and SEL\*<sub>4</sub> of FIG. 4A and FIG. 4B, according to some embodiments described herein. Based on chart 445 in FIG. 4B and 30 the relationships between signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, and SEL<sub>4</sub> and signals SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, SEL\*<sub>3</sub>, and SEL\*<sub>4</sub> in FIG. 4B and FIG. 4C, memory device 400 can determine which voltage (e.g., either V0 or V1) to provide to each of signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL<sub>4</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, SEL\*<sub>3</sub>, and 35 SEL\*<sub>4</sub>, so that all pass transistors (e.g., 240<sub>A</sub>, 240<sub>B</sub>, and 240<sub>C</sub>,) of only the selected block (e.g., block 0) among block 0 through block 15 are turned on while at least one of the pass transistors of each of the unselected blocks (e.g., block 1 through block 15) is turned off.

FIG. 5 is a chart showing relationships between the numbers (quantities) of blocks, transistor gate lines in each block, and switches in a memory device (e.g., memory devices 200 and 400), according to some embodiments described herein. Row 502 in FIG. 5 shows the relationships 45 between the number of components of memory device 200 (FIG. 2A through FIG. 3C). Row 504 in FIG. 5 shows the relationships between the number of components of memory device 400 (FIG. 4A through FIG. 4C). Row 506 of FIG. 5 shows the formulas for relationships between the numbers of 50 blocks, transistor gate lines, and switches of a memory device similar to memory devices 200 and 400.

As shown in row **502**, the number of blocks is 8=2³, the number of transistor gate lines is 3, and the number of switches to provide signals (e.g., SEL<sub>A</sub>, SEL<sub>B</sub>, and SEL<sub>C</sub>) to 55 the blocks is 6=2\*<sub>3</sub>. Thus, the number of switches is less than the number of blocks (6<8). In row **504**, the number blocks is 16=2⁴, the number of transistor gate lines in each block is 4, and the number of switches is 8=2\*4. Thus, the number of switches is less than the number of blocks (16<8). 60 In row **506**, the number blocks is B=2' (where T is the number of switches is S=2\*T. Since the number of signals (e.g., three of six signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub> in FIG. **2**B) received by each block is equal to the 65 number of transistor gate lines (e.g., three transistor gate lines **250**<sub>4</sub>, **250**<sub>B</sub>, and **250**<sub>C</sub> in FIG. **2**A), and since S=2\*T,

12

the number of switches (S) can also be equal to two times the number of signals received by each block. For example, if X is the number of signals received by each block, then S=2\*X.

In general, the memory device (e.g., memory device 200 or 400) described herein can include S switches, where S is an integer. For example, S can be six in the example of FIG. 2A where memory device 200 includes six switches SW1 through SW6. In another example, S can be eight in the example of FIG. 4A where memory device 400 includes eight switches SW1 through SW8.

The S switches can provide N signals, where N is an integer. For example, N can be six in the example of FIG. **2**A where six switches SW1 through SW6 provide six signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub>, respectively. In another example, N can be eight in the example of FIG. **4**A where eight switches SW1 through SW8 provide eight signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL<sub>4</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, SEL\*<sub>3</sub>, and SEL\*<sub>4</sub>, respectively.

The N signals can be provided to B blocks of the memory device (e.g., memory device 200 or 400) where B is an integer. For example, B can be eight in the example of FIG. 2A where memory device 200 includes eight blocks (e.g., block 0 through block 7). In another example, B can be 16 in the example of FIG. 4A where memory device 400 includes 16 blocks (e.g., block 0 through block 15).

As described above with reference to FIG. 2B and FIG. 4B, the memory device (e.g., memory device 200 or 400) described herein can provide C unique combinations of the N signals. For example, C can be eight (eight unique combinations of the N signals) in the example of FIG. 2A. In another example, C can be 16 (16 unique combinations of the N signals) in the example of FIG. 4A.

As also described above with reference to FIG. **2**B and FIG. **4**A, each of the C unique combinations of the N signals can include X signals, where X is an integer. For example, X can be three (e.g., three of six signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub>) in the example of FIG. **2**A (where C=8). In another example, X can be four (e.g., four of eight signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL<sub>4</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, SEL\*<sub>3</sub>, and SEL\*<sub>4</sub>) in the example of FIG. **4**A (where C=16).

FIG. 6A shows a block diagram of memory device 200 of FIG. 2A including sub-blocks 640<sub>0</sub>, 640<sub>1</sub>, 640<sub>2</sub>, and 640<sub>3</sub> of block 0, according to some embodiments described herein. FIG. 6A shows block 0 including four sub-blocks 640<sub>0</sub>, 640<sub>1</sub>, 640<sub>2</sub>, and 640<sub>3</sub> as an example. The number of sub-blocks of block 0 can vary.

As shown in FIG. 6A, sub-blocks  $640_0$ ,  $640_1$ ,  $640_2$ , and 640<sub>3</sub> can share data lines 270, 271, and 272. Transistor gate lines  $250_A$ ,  $250_B$ , and  $250_C$ , conductive connections  $250'_A$ , 250'<sub>B</sub>, and 250'<sub>C</sub>, global select line 280'<sub>O</sub>, and switch circuitry 202 are the same as those described above with reference to FIG. 2A. For simplicity, description of the same components of memory device 200 shown in FIG. 2A and FIG. 6A are not repeated. In FIG. 6A, sub-blocks 640<sub>0</sub>, 640<sub>1</sub>,  $640_2$ , and  $640_3$  can exchange information with data lines 270, 271, 272 one sub-block at a time if block 0 is a selected block during a memory operation of memory device 200. Sub-blocks  $640_0$ ,  $640_1$ ,  $640_2$ , and  $640_3$  have separate select lines (e.g., global drain select lines) 280'<sub>0</sub>, 280'<sub>1</sub>, 280'<sub>2</sub>, and 280'<sub>3</sub>. Select lines 280'<sub>0</sub>, 280'<sub>1</sub>, 280'<sub>2</sub>, and 280'<sub>3</sub> are electrically uncoupled to each other. Sub-blocks  $640_0$ ,  $640_1$ ,  $640_2$ , and 640<sub>3</sub> can share a select line (e.g., global source select lines) 289' and share access lines (e.g., global access lines) 220', 221', 222', and 223'.

Memory device 200 can include driver circuitry 605 to provide signals GSGD<sub>0</sub>, GSGD<sub>1</sub>, GSGD<sub>2</sub>, and GSGD<sub>3</sub> on respective select lines **280**'<sub>0</sub>, **280**'<sub>1</sub>, **280**'<sub>2</sub>, and **280**'<sub>3</sub>, a signal GSGS on select line 289', and signals GWL0, GWL1, GWL2, and GWL3 on respective access lines 220', 221', 5 222', and 223'. Driver circuitry 605 can activate (e.g., provide a positive voltage to) one of signals  $GSGD_0$ , GSGD<sub>1</sub>, GSGD<sub>2</sub>, and GSGD<sub>3</sub> associated with a sub-block that is selected and deactivate (e.g., provide zero volts to) the sub-blocks that are not selected. For example, if sub-block 10  $640_0$  is selected (to store information in or read information from memory cells (shown in FIG. 6B) of sub-block  $640_0$ ), then driver circuitry 605 can activate signal GSGD<sub>o</sub> while deactivating signals GSGD<sub>1</sub>, GSGD<sub>2</sub>, and GSGD<sub>3</sub>.

In this description, a selected sub-block of a selected 15 block is a sub-block that is selected by memory device 200 to store information in (e.g., in a write operation) or read (e.g., sense) information from (e.g., in a read operation) a memory cell (or memory cells) of that selected sub-block. An unselected sub-block of a selected block is sub-block 20 that is not selected by memory device **200** during a memory operation.

FIG. 6B shows schematic diagrams of sub-block 640<sub>0</sub> of block 0 of memory device 200 of FIG. 6A, according to some embodiments described herein. As shown in FIG. 6B, 25 memory device 200 can include memory cells 210, 211, 212, and 213. Memory cells 210, 211, 212, and 213 can correspond to memory cells 110 of FIG. 1. Thus, memory cells 210, 211, 212, and 213 can include non-volatile memory cells (e.g., floating gate memory cells, charge trap memory 30 cells, or other types of non-volatile memory cells).

As shown in FIG. 6B, memory cells 210, 211, 212, and 213 can be arranged in memory cell strings  $230_0$ ,  $231_0$ , and  $232_0$ . Each of the memory cell strings  $230_0$ ,  $231_0$ , and  $232_0$ 211, one of memory cells 212, and one of memory cells 213. FIG. 6B shows an example where memory device 200 has four levels (e.g., four tiers) of respective memory cells 210, 211, 212, and 213 and four memory cells in each of the memory cell strings. The number of levels (e.g., tiers) of 40 memory cells, and the number of memory cells in each memory cell string, can vary.

Memory device 200 can include select gates (e.g., drain select gates)  $260_0$ , a select line (e.g., local drain select line)  $280_0$  and associated signal SGD<sub>0</sub>, select gates (e.g., source 45) select gate) 260'<sub>0</sub>, a select line (e.g., local source select line) 289 and associated signal SGS, and a source (e.g., source line) 299 that can carry a signal SRC. In memory device 200, a select line (e.g., select line  $280_0$  or 289) can include a conductive material to carry a signal (e.g., signal SGD<sub>0</sub> or 50 SGS), but a select line does not operate like a transistor. A select gate (e.g., one of select gates  $260_0$  or one of select gates 260'<sub>0</sub>) can receive a signal from a respective select line and can operate like a transistor (e.g., a FET).

As shown in FIG. 6B, memory device 200 can include 55 control lines (e.g., local access lines) 220, 221, 222, and 223 that can carry corresponding signals (e.g., word line signals) WL0, WL1, WL2, and WL3. FIG. 2A shows four control lines (e.g., 220, 221, 222, and 223) as an example. The number of control lines of memory device 200 can vary.

In this description, a line (e.g., any of local drain select lines  $280_0$ ,  $280_1$ ,  $280_2$ ,  $280_3$ ,  $281_0$ , and  $287_0$ ; any of global drain select lines 280'<sub>0</sub>, 280'<sub>1</sub>, 280'<sub>2</sub>, 280'<sub>3</sub>, 281'<sub>0</sub>, and 287'<sub>0</sub>; source select line 289; any of transistor gate lines  $250_{A}$ ,  $250_B$ ,  $250_C$ ,  $251_A$ ,  $251_B$ ,  $251_C$ ,  $257_A$ ,  $257_B$ ,  $257_C$ ; any of 65 control lines 220, 221, 222, and 223; and any of global access lines 220', 221', 222', and 223') includes a piece of

14

conductive material, a region of conductive material, a layer of conductive material, or any shape of a structure that can carry an electrical signal. Thus, in this description, a line (e.g., a select line, a transistor gate line, or a control line) includes a "line" shape structure and any other structural shapes (e.g., a region of any shape, a layer shape, and other shapes).

As shown in FIG. 6B, memory device 200 can include different groups of three transistors  $240_A$ ,  $240_B$ , and  $240_C$ coupled in series with each other and coupled in series between two respective lines. For example, memory device 200 includes a group of transistors  $240_A$ ,  $240_B$ , and  $240_C$ coupled in series with each other and coupled in series between select lines  $280_0$  and  $280'_0$ . In another example, memory device 200 includes a group of transistors  $240_A$ ,  $240_B$ , and  $240_C$  coupled in series with each other and coupled in series between select lines 289 and 280'<sub>0</sub>. Similarly, memory device 200 includes transistors  $240_A$ ,  $240_B$ , and 240<sub>c</sub> coupled in series with each other and coupled in series between each of control lines 221, 222, and 223 and a respective access line (e.g., global access line) among access lines 220', 221', 222', and 223'.

As shown in FIG. 2B, transistors  $240_{A}$  have gates that are electrically uncoupled to the gates of transistors  $240_B$ . The gates of transistors  $240_B$  are also electrically uncoupled to the gates of transistors  $240_{C}$ .

The gates of transistors  $240_{A}$  can be coupled to transistor gate line  $250_{4}$ . Thus, the same signal (e.g., signal SEL<sub>4</sub>) provided to transistor gate line  $250_{A}$  can be used to control (e.g., turn on and turn off) transistors  $240_{A}$  at the same time. This means that transistors  $240_A$  can be concurrently turned on (e.g., turned on at the same time) or currently turned off (e.g., turned off at the same time).

Similarly, gates of transistors  $240_B$  can be coupled to can include one of memory cells 210, one of memory cells 35 transistor gate line  $250_B$ . Thus, the same signal (e.g., signal  $SEL_B$ ) provided to transistor gate line 250 can be used to control (e.g., turn on and turn off) transistors  $240_B$  at the same time. This means that transistors  $240_B$  can be concurrently turned on (e.g., turned on at the same time) or currently turned off (e.g., turned off at the same time). The gates of transistors  $240_C$  can be coupled to transistor gate line 250<sub>C</sub>. Thus, the same signal (e.g., signal SEL<sub>C</sub>) provided to transistor gate line  $250_C$  can be used to control (e.g., turn on and turn off) transistors  $240_{C}$  at the same time. This means that transistors  $240_C$  can be concurrently turned on (e.g., turned on at the same time) or currently turned off (e.g., turned off at the same time). As described above with reference to FIG. 2A, signals  $SEL_A$ ,  $SEL_B$ , and  $SEL_C$  can be provided from switches SW1 through SW6 by a unique combination of signals SEL<sub>1</sub>, SEL<sub>2</sub>, SEL<sub>3</sub>, SEL\*<sub>1</sub>, SEL\*<sub>2</sub>, and SEL\*<sub>3</sub> at output nodes of switches SW1 through SW6 (FIG. **2**A).

During a memory operation, memory device 200 can use control lines 220, 221, 222, and 223 to access memory cells of memory cell strings  $230_0$ ,  $231_0$ , and  $232_0$ . For example, if block 0 (which includes sub-block 640<sub>0</sub> of FIG. 6B) is a selected block during a memory operation (e.g., read or write) of memory device 200, all of transistors  $240_A$ ,  $240_B$ , and  $240_C$  can be turned on. Control lines 220, 221, 222, and 223 can be activated (e.g., provided with positive voltages) to access a selected memory cell (or selected memory cells) of a selected memory cell string (or strings) among memory cell strings  $230_0$ ,  $231_0$ , and  $232_0$ . In this example, information can be stored in a memory cell (or memory cells) of the selected memory cell string (or memory cell strings) if the memory operation is a write (e.g., program) operation. In this example, information can be read (e.g., sensed) from a

memory cell (or memory cells) of the selected memory cell string (or memory cell strings) of selected block 0 if the memory operation is a read operation. In another example, if block 0 is an unselected block during a memory operation of memory device 200, one of the following sets of transistors can be turned off: transistors  $240_A$ ; transistors  $240_B$ ; transistors  $240_C$ ; transistors  $240_A$  and transistors  $240_B$ ; transistors  $240_C$ ; or all of transistors  $240_A$ , transistors  $240_B$ , and transistors  $240_C$ ; or all of transistors  $240_A$ , transistors  $240_B$ , and transistors  $240_C$ . Control lines 220, 221, 222, and 223 can be 10 deactivated (e.g., provided with zero volts (e.g., ground potential)). Thus, in this example (block 0 is unselected), no information is stored in or read from the memory cells of memory cell strings  $230_O$ ,  $231_O$ , and  $232_O$  of block 0.

During a memory operation of memory device 200, if 15 block 0 is a selected block and sub-block  $640_0$  is a selected sub-block, one or both select gates can be activated (e.g., by turning on the select gates), depending on which memory operation (e.g., a read or write) memory device 200 performs on the selected sub-block. Activating select gates  $260_0$  20 during a memory operation of memory device 200 can include providing (e.g., applying) a voltage having a positive value to signal GSGD<sub>o</sub> on select line **280**'<sub>o</sub> and turning on all of transistors  $240_A$ ,  $240_B$ , and  $240_C$  coupled to select lines  $280_0$  and  $280_0$ . This allows the voltage (e.g., a positive 25) voltage) from select line (e.g., global drain select line) 280' to be passed from select line 280' to select line (e.g., local drain select line)  $280_{\circ}$  through transistors  $240_{\circ}$ ,  $240_{\circ}$ , and  $240_{\rm C}$  (that are turned on). The positive voltage provided to select line  $280_0$  can activate (e.g., turn on) select gates  $260_0$ . 30 This forms conductive paths (e.g., current paths) between memory cell strings  $230_0$ ,  $231_0$ , and  $232_0$  and data lines 270, 271, and 272, respectively.

Similarly, activating select gates 260' during a memory operation of memory device 200 can include providing (e.g., 35 applying) a voltage having a positive value to signal GSGS and turning on all of transistors  $240_A$ ,  $240_B$ , and  $240_C$ coupled to select line 289. This allows the voltage (e.g., a positive voltage) from select line (e.g., global source select line) 289' to be passed from select line 289' to select line 40 (e.g., local source select line) 289 through transistors  $240_A$ ,  $240_B$ , and  $240_C$  (that are turned on). The positive voltage provided to select line 289 can activate (e.g., turn on) select gates 260'<sub>0</sub>. This forms conductive paths (e.g., current paths) between memory cell strings  $230_0$ ,  $231_0$ , and  $232_0$  and 45 source 299. During a write operation of memory device 200, if sub-block  $640_0$  is a selected sub-block, memory device 200 can concurrently select memory cells of different memory cell strings (e.g., memory cells coupled to the same control line) of sub-block  $640_0$  in order to store information 50 in the selected memory cells. During a read operation of memory device 200, if sub-block  $640_0$  is a selected subblock, memory device 200 can concurrently select memory cells of different memory cell strings (e.g., memory cells coupled to the same control line) of sub-block  $640_0$  in order 55 to read information in the selected memory cells.

FIG. 6C, FIG. 6D, and FIG. 6E show schematic diagrams of sub-blocks 640<sub>1</sub>, 640<sub>2</sub>, and 640<sub>3</sub>, respectively, of block 0 of memory device 200 of FIG. 6A, according to some embodiments described herein. Sub-blocks 640<sub>1</sub>, 640<sub>2</sub>, and 60 640<sub>3</sub> include elements that are similar to or the same as the elements of sub-block 640<sub>0</sub> of FIG. 6B. Some of the elements of sub-blocks 640<sub>0</sub> are shared with sub-blocks 640<sub>1</sub>, 640<sub>2</sub>, and 640<sub>3</sub>. Thus, for simplicity, descriptions of similar or the same elements or shared elements among sub-block 65 640<sub>0</sub> (FIG. 6B) and sub-blocks 640<sub>1</sub>, 640<sub>2</sub>, and 640<sub>3</sub> are not repeated.

**16**

As shown in FIG. 6C, sub-block 640<sub>1</sub> can include control lines 220, 221, 222, and 223 (and associated signals WL0, WL1, WL2, and WL3), select line 289 (and associated signal SGS), and source 299 (and associated signal SRC). Sub-block 640<sub>1</sub> of memory device 200 can include memory cells 210, 211, 212, and 213 arranged in memory cell strings 230<sub>1</sub>, 231<sub>1</sub>, and 232<sub>1</sub>, which are different from memory cell strings 230<sub>0</sub>, 231<sub>0</sub>, and 232<sub>0</sub> of sub-block 640<sub>0</sub> of FIG. 6B. Sub-block 640<sub>1</sub> of FIG. 6C can include select gates (e.g., drain select gates) 260<sub>1</sub>, a select line (e.g., local drain select line) 280<sub>1</sub> and associated signal SGD<sub>1</sub>, and select gates (e.g., source select gate) 260'<sub>1</sub>.

As shown in FIG. 6D, sub-block 640<sub>2</sub> can include control lines 220, 221, 222, and 223 (and associated signals WL0, WL1, WL2, and WL3), select line 289 (and associated signal SGS), and source 299 (and associated signal SRC). Sub-block 640<sub>2</sub> of memory device 200 can include memory cells 210, 211, 212, and 213 arranged in memory cell strings 230<sub>2</sub>, 231<sub>2</sub>, and 232<sub>2</sub>, which are different from memory cell strings 230<sub>1</sub>, 231<sub>1</sub>, and 232<sub>1</sub> of sub-block 640<sub>1</sub> of FIG. 6C. Sub-block 640<sub>3</sub> of FIG. 6D can include select gates (e.g., drain select gates) 260<sub>2</sub>, a select line (e.g., local drain select line) 280<sub>2</sub> and associated signal SGD<sub>2</sub>, and select gates (e.g., source select gate) 260'<sub>2</sub>.

As shown in FIG. 6E, sub-block 640<sub>3</sub> can include control lines 220, 221, 222, and 223 (and associated signals WL0, WL1, WL2, and WL3), select line 289 (and associated signal SGS), and source 299 (and associated signal SRC). Sub-block 640<sub>3</sub> of memory device 200 can include memory cells 210, 211, 212, and 213 arranged in memory cell strings 230<sub>3</sub>, 231<sub>3</sub>, and 232<sub>3</sub>, which are different from memory cell strings 230<sub>2</sub>, 231<sub>2</sub>, and 232<sub>2</sub> of sub-block 640<sub>2</sub> of FIG. 6D. Sub-block 640<sub>3</sub> of FIG. 6E can include select gates (e.g., drain select gates) 260<sub>3</sub>, a select line (e.g., local drain select line) 280<sub>3</sub> and associated signal SGD<sub>3</sub>, and select gates (e.g., source select gate) 260'<sub>3</sub>.

Memory device 200 of FIG. 2A described above with reference to FIG. 2A through FIG. 6E may include only one pass transistor or two pass transistors (instead of three pass transistors  $240_A$ ,  $240_B$ , and  $240_C$ ) in each of block 0 through block 7. However, in comparison with some conventional memory devices, the inclusion of three (or more) pass transistors in each of block 0 through block 7 can allow the memory device described herein (e.g., memory device 200 or 400) to have fewer switches (e.g., fewer switches in switch circuitry 202 of FIG. 2A or in switch circuitry 402 of FIG. 4A) to select a relatively higher number of blocks. For example, some conventional memory devices may have techniques to select a given number of blocks in which the number of switches may have a one-to-one relationship with the number of blocks. As an example, to select one of eight blocks in some conventional memory devices, eight (or more) switches may be needed in order to provide signals (e.g., eight or more signals) to select the blocks in such conventional memory devices. In another example, to select one of 16 blocks in some conventional memory devices, 16 (or more) switches may be needed in order to provide signals (e.g., 16 or more signals) to select the blocks in such conventional memory devices.