#### US010120613B2

### (12) United States Patent

#### Sinclair et al.

# (54) SYSTEM AND METHOD FOR RESCHEDULING HOST AND MAINTENANCE OPERATIONS IN A NON-VOLATILE MEMORY

(71) Applicant: SanDisk Technologies Inc., Plano, TX (US)

(72) Inventors: Alan Welsh Sinclair, Falkirk (GB); Sergey Anatolievich Gorobets,

Edinburgh (GB)

(73) Assignee: SanDisk Technologies LLC, Plano, TX

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 14/928,649

(22) Filed: Oct. 30, 2015

(65) Prior Publication Data

US 2017/0123726 A1 May 4, 2017

(51) **Int. Cl.**

G06F 12/02 (2006.01) G06F 3/06 (2006.01)

(52) **U.S. Cl.**

CPC ...... *G06F 3/0659* (2013.01); *G06F 3/0611* (2013.01); *G06F 3/0679* (2013.01); *G06F 3/0688* (2013.01); *G06F 12/02* (2013.01)

(58) Field of Classification Search

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

5,535,369 A 7/1996 Wells et al. 5,570,315 A 10/1996 Tanaka et al. 5,630,093 A 5/1997 Holzhammer et al.

#### (10) Patent No.: US 10,120,613 B2

(45) Date of Patent:

Nov. 6, 2018

5,696,917 A 12/1997 Mills et al. 5,774,397 A 6/1998 Endoh et al. 5,860,124 A 1/1999 Matthews et al. 5,869,845 A 2/1999 Vander Wagt et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

EP 1143455 A2 10/2001 EP 1389755 A2 2/2004 (Continued)

#### OTHER PUBLICATIONS

Commonly owned related application for U.S. Appl. No. 14/928,582, filed Oct. 30, 2015, 103 pgs.

(Continued)

Primary Examiner — Daniel C Chappell Assistant Examiner — Gautam Sain

(74) Attorney, Agent, or Firm — Brinks Gilson & Lione

#### (57) ABSTRACT

Systems and methods for balancing maintenance and programming host data across multiple maintenance source blocks in a non-volatile memory are disclosed. A memory system may include non-volatile memory and a controller configured to execute one or more of the steps of selecting a fixed plurality of maintenance source blocks for executing a balance cycle of maintenance and host writes across the selected fixed plurality of maintenance source blocks. The method interleaves moving of valid data from source blocks with host data writes to achieve a balance of free space generation and consumption for the balance cycle, while periodically reevaluating an overall interleave ratio and/or substituting other previously programmed blocks for one of the previously selected plurality during the balance cycle.

#### 16 Claims, 24 Drawing Sheets

### US 10,120,613 B2 Page 2

| (56) References Cited               |         |                                              | 2007/0156998 A1                    |                  | Gorobets<br>Sincloin et al      |

|-------------------------------------|---------|----------------------------------------------|------------------------------------|------------------|---------------------------------|

| U.S.                                | PATENT  | DOCUMENTS                                    | 2007/0186032 A1<br>2007/0186065 A1 |                  | Sinclair et al.<br>Lee et al.   |

| 0.2.                                |         |                                              | 2007/0239928 A1                    | 10/2007          | Gera et al.                     |

| 5,930,167 A                         | 7/1999  | Lee et al.                                   | 2008/0034154 A1                    |                  | Lee et al.                      |

| 5,960,169 A                         |         | Styczinski                                   | 2008/0067573 A1                    |                  | Jang et al.                     |

| , ,                                 |         | Mills et al.                                 | 2008/0084739 A1<br>2008/0094952 A1 |                  | Chae et al.<br>Brondijk et al.  |

| 6,046,935 A<br>6,069,827 A          |         | Takeuchi et al.<br>Sinclair                  | 2008/0054552 A1<br>2008/0155175 A1 |                  | Sinclair et al.                 |

| 6,373,746 B1                        |         | Takeuchi et al.                              | 2008/0155176 A1                    |                  | Sinclair et al.                 |

| 6,456,528 B1                        | 9/2002  |                                              | 2008/0155177 A1                    |                  | Sinclair et al.                 |

| 6,522,580 B2                        | 2/2003  | Chen et al.                                  | 2008/0155178 A1                    |                  | Sinclair et al.                 |

| 6,622,199 B1                        |         | Spall et al.                                 | 2008/0155227 A1<br>2008/0155228 A1 |                  | Sinclair et al.                 |

| 6,715,027 B2                        |         | Kim et al.                                   | 2008/0133228 A1<br>2008/0307158 A1 |                  |                                 |

| 6,725,321 B1<br>6,771,536 B2        |         | Sinclair et al.<br>Li et al.                 | 2008/0307164 A1                    | 12/2008          |                                 |

| 6,781,877 B2                        |         |                                              | 2008/0307192 A1                    | 12/2008          | Sinclair et al.                 |

| 7,154,781 B2                        | 12/2006 | Lakhani et al.                               | 2008/0316815 A1                    | 12/2008          |                                 |

| 7,336,531 B2                        |         | Roohparvar                                   | 2008/0320209 A1<br>2009/0132758 A1 |                  | Lee et al.<br>Jiang et al.      |

| 7,409,489 B2                        |         | Sinclair                                     | 2009/0132738 A1<br>2009/0157994 A1 |                  | Hampel et al.                   |

| 7,420,867 B2<br>7,433,993 B2        |         | Sinclair                                     | 2009/0164745 A1                    |                  | Sinclair et al.                 |

| 7,133,333 B2<br>7,444,462 B2        |         | Traister et al.                              | 2009/0172258 A1                    |                  | Olbrich et al.                  |

| , ,                                 |         | Naamad et al.                                | 2009/0172263 A1                    |                  | Olbrich et al.                  |

| 7,865,658 B2                        |         |                                              | 2009/0182791 A1                    |                  | Gorobets                        |

| 7,903,459 B2                        |         | Yu et al.                                    | 2009/0196102 A1<br>2009/0210614 A1 | 8/2009<br>8/2009 | Gorobets                        |

| 7,930,468 B2<br>7,984,084 B2        |         | Caulkins<br>Sinclair                         | 2009/0218614 A1                    |                  |                                 |

| 7,984,084 B2<br>7,996,642 B1        |         |                                              | 2009/0248952 A1                    |                  | Radke et al.                    |

| 8,095,735 B2                        |         | Brewer et al.                                | 2009/0259799 A1                    | 10/2009          | <u> </u>                        |

| 8,209,503 B1                        |         | Smith                                        | 2009/0262577 A1                    | 10/2009          |                                 |

| 8,228,728 B1                        |         | Yang et al.                                  | 2009/0271562 A1<br>2009/0300269 A1 | 10/2009          | Sinciair<br>Radke et al.        |

| 8,239,617 B1                        |         | Linnell                                      | 2010/0125695 A1                    |                  | Wu et al.                       |

| 8,412,752 B2<br>8,429,352 B2        |         | Dodge<br>Sinclair                            | 2010/0146197 A1                    |                  | Gorobets                        |

| 8,473,669 B2                        |         | Sinclair                                     | 2010/0153631 A1                    |                  | Moon et al.                     |

| 8,537,613 B2                        |         | Sinclair et al.                              | 2010/0169540 A1                    |                  | Sinclair                        |

| •                                   |         | Karamcheti et al.                            | 2010/0169588 A1<br>2010/0172179 A1 |                  | Sinclair<br>Gorobets et al.     |

| 8,689,042 B1                        |         | Kanapathippillai et al.                      | 2010/01/21/9 A1<br>2010/0174846 A1 |                  | Paley et al.                    |

| 8,706,932 B1<br>8,850,091 B1        |         | Kanapathippillai et al.<br>Karamcheti et al. | 2010/0205352 A1                    |                  | Chu et al.                      |

| 8,873,284 B2                        |         | Sinclair et al.                              | 2010/0217926 A1                    |                  | Sinclair                        |

| 9,223,693 B2                        |         |                                              | 2010/0223423 A1                    |                  | Sinclair et al.                 |

| 2002/0172081 A1                     |         | Mukaida et al.                               | 2010/0262765 A1                    |                  | Cheon et al.                    |

| 2003/0109093 A1                     |         | Harari et al.                                | 2010/0274952 A1<br>2011/0022778 A1 | 10/2010          | Schibilla et al.                |

| 2003/0147278 A1<br>2003/0229753 A1  |         | Tanaka et al.<br>Hwang                       | 2011/0055455 A1                    |                  | Post et al.                     |

| 2004/0030847 A1                     |         | Tremaine                                     | 2011/0107042 A1                    | 5/2011           | Herron                          |

| 2004/0073748 A1                     |         | Rudelic                                      | 2011/0138100 A1                    |                  | Sinclair                        |

| 2004/0260957 A1                     |         | Jeddeloh et al.                              | 2011/0149650 A1                    |                  | Huang et al.                    |

| 2005/0144361 A1                     |         | Gonzalez et al.                              | 2011/0161621 A1<br>2011/0219180 A1 |                  | Sinclair et al.<br>Cheon et al. |

| 2005/0144363 A1<br>2005/0195635 A1  |         | Sinclair<br>Conley et al.                    | 2011/0213180 A1                    |                  | Segal et al.                    |

| 2005/0175035 A1<br>2005/0278479 A1  |         | Wu et al.                                    | 2011/0296089 A1                    |                  | Seol et al.                     |

| 2006/0020744 A1                     |         | Sinclair et al.                              | 2012/0005405 A1                    |                  | Wu et al.                       |

| 2006/0031593 A1                     |         | Sinclair                                     | 2012/0017038 A1                    |                  | Gorobets et al.                 |

| 2006/0047800 A1                     |         | Caveney et al.                               | 2012/0030409 A1<br>2012/0066443 A1 |                  | Post et al.<br>Li et al.        |

| 2006/0149891 A1*                    | 7/2006  | Rudelic G06F 12/0246<br>711/103              | 2012/0080443 A1                    |                  | Gorobets et al.                 |

| 2006/0161724 A1                     | 7/2006  | Bennett et al.                               | 2012/0151124 A1                    | 6/2012           | Baek et al.                     |

| 2006/0161724 A1                     |         | Bennett et al.                               | 2012/0221784 A1                    | 8/2012           |                                 |

| 2006/0184718 A1                     | 8/2006  | Sinclair et al.                              | 2012/0239851 A1*                   | 9/2012           | Calvert G06F 11/1441            |

| 2006/0184719 A1                     |         | Sinclair                                     | 2012/0246391 A1                    | 0/2012           | 711/103<br>Meir et al.          |

| 2006/0184720 A1                     |         | Sinclair et al.                              | 2012/0240391 A1<br>2012/0254574 A1 |                  | Sinclair et al.                 |

| 2006/0184722 A1<br>2006/0184723 A1  |         | Sinclair<br>Sinclair et al.                  | 2012/0260028 A1                    |                  | Lee et al.                      |

| 2006/0184723 A1<br>2006/0285397 A1  |         | Nishihara et al.                             | 2012/0297121 A1                    | 11/2012          | Gorobets et al.                 |

| 2007/0016756 A1                     |         | Hsieh et al.                                 | 2012/0297122 A1                    |                  | Gorobets et al.                 |

| 2007/0030734 A1                     |         | Sinclair et al.                              | 2012/0311197 A1                    |                  | Larson et al.                   |

| 2007/0033323 A1                     |         | Gorobets                                     | 2012/0311237 A1<br>2013/0013853 A1 | 12/2012          |                                 |

| 2007/0033324 A1<br>2007/0033325 A1* |         | Sinclair<br>Sinclair G06F 3/0605             | 2013/0013833 A1<br>2013/0019051 A1 |                  | Somanache et al.                |

| 2007/0033323 AT                     | 2/200/  | 711/103                                      | 2013/0019051 A1<br>2013/0019058 A1 |                  | Caraccio et al.                 |

| 2007/0033329 A1                     | 2/2007  | Sinclair et al.                              | 2013/0024641 A1                    |                  | Talagala et al.                 |

| 2007/0033330 A1                     | 2/2007  | Sinclair et al.                              | 2013/0042067 A1                    |                  | Thomas                          |

| 2007/0033376 A1                     |         | Sinclair et al.                              | 2013/0138912 A1                    |                  | Bux et al.                      |

| 2007/0033378 A1                     |         | Sinclair et al.                              | 2013/0159601 A1                    |                  | Lassa et al.                    |

| 2007/0101096 A1                     |         | Gorobets<br>Sinclair                         | 2013/0173844 A1                    |                  | Chen et al.                     |

| 2007/0136555 A1                     | 0/200/  | Sinclair                                     | 2013/0173874 A1                    | 1/2013           | Sprouse et al.                  |

## US 10,120,613 B2 Page 3

| (56) References Cited                                 |                                                                            | WO WO 2007/019155 A1 2/2007<br>WO WO 2007/019217 A1 2/2007                                                                                    |  |  |

|-------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| U.S. I                                                | PATENT DOCUMENTS                                                           | WO WO 2009/107426 A1 9/2009                                                                                                                   |  |  |

| 2013/0219146 A1<br>2013/0265825 A1                    | 8/2013 Confalonieri<br>10/2013 Lassa                                       | WO WO 2012/158521 A1 11/2012<br>WO WO 2012/161659 A1 11/2012                                                                                  |  |  |

| 2014/0006898 A1<br>2014/0068152 A1                    | 1/2014 Sharon et al.<br>3/2014 Sinclair                                    | OTHER PUBLICATIONS                                                                                                                            |  |  |

| 2014/0143483 A1<br>2014/0185376 A1<br>2014/0189205 A1 | 5/2014 Meir et al.<br>7/2014 Sinclair et al.<br>7/2014 Sinclair et al.     | Commonly owned related application for U.S. Appl. No. 14/928,606, filed Oct. 30, 2015, 106 pgs.                                               |  |  |

| 2014/0189203 A1<br>2014/0189206 A1<br>2014/0189207 A1 | 7/2014 Sinclair et al.<br>7/2014 Sinclair et al.<br>7/2014 Sinclair et al. | Commonly owned related application for U.S. Appl. No. 14/928,732, filed Oct. 30, 2015, 104 pgs.                                               |  |  |

| 2014/0189208 A1*                                      |                                                                            | filed Oct. 30, 2015, 105 pgs.                                                                                                                 |  |  |

| 2014/0189209 A1                                       | 7/2014 Sinclair et al.                                                     | Office Action in co-pending U.S. Appl. No. 14/928,732 dated Apr.                                                                              |  |  |

| 2014/0189210 A1<br>2014/0223087 A1<br>2014/0237169 A1 | 7/2014 Sinclair et al.<br>8/2014 Caraccio et al.<br>8/2014 Manning         | 13, 2017 (20 pages). Office Action in co-pending U.S. Appl. No. 14/928,582 dated Aug. 31, 2017 (19 pages).                                    |  |  |

| 2016/0321171 A1                                       | 11/2016 Kanno                                                              | Hui Sun, et al., Measuring and Analyzing Write Amplification Characteristics of Solid State Disks, 2013, IEEE, 21 <sup>st</sup> International |  |  |

| FOREIG                                                | N PATENT DOCUMENTS                                                         | Symposium on Modeling, Analysis & Simulation of Computer and Telecommunication System, pp. 212-221.                                           |  |  |

|                                                       | 759 A2 8/2006<br>2995 A1 4/2009                                            | * cited by examiner                                                                                                                           |  |  |

FIG. 1B

FIG. 1C

FIG. 3

FIG. 4

FIG. SB

FIG. 7

FIG. 11

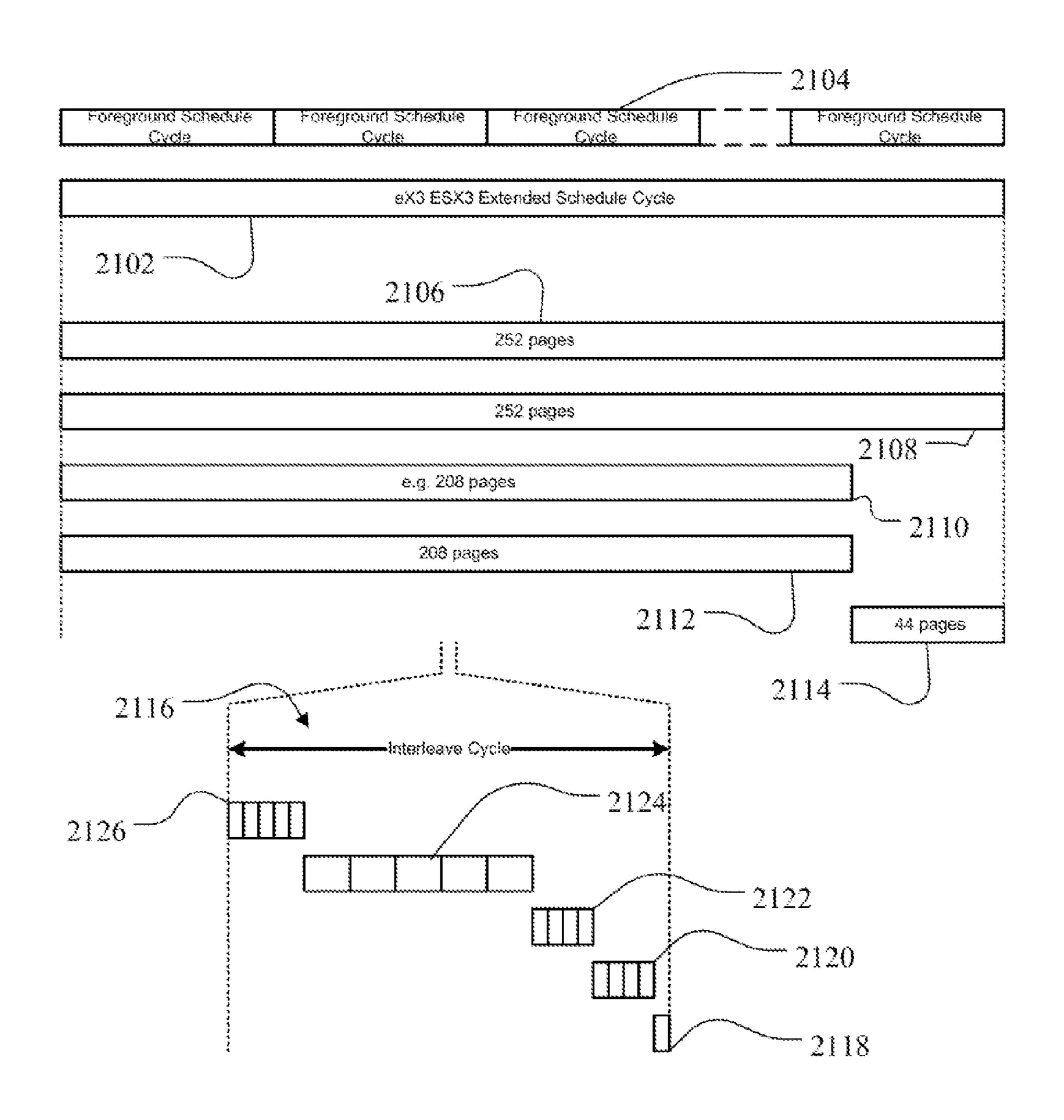

FIG. 21

FIG. 25

#### SYSTEM AND METHOD FOR RESCHEDULING HOST AND MAINTENANCE OPERATIONS IN A **NON-VOLATILE MEMORY**

#### BACKGROUND

Non-volatile memory systems, such as flash memory, have been widely adopted for use in consumer products. Flash memory may be found in different forms, for example 10 in the form of a portable memory card that can be carried between host devices or as a solid state disk (SSD) embedded in a host device. Flash memory generally provides is lowest, such as binary flash, also known as single level cell (SLC) flash that stores one bit per cell. Flash memory that is configured to store more than one bit per cell, known as multi-level cell (MLC) flash, can store two or more bits of information per cell. While SLC flash memory is gener- 20 ally known for having better read and write performance (e.g., speed and endurance) than MLC flash, MLC flash provides more storage capacity and is generally less expensive to produce. The endurance and performance of MLC flash tends to decrease as the number of bits per cell of a 25 given MLC configuration increases.

In a number of existing non-volatile memory systems, SLC and MLC are used together to try and capitalize on the advantages of each type of memory. The SLC memory may be used for its faster performance and the MLC for its 30 greater storage density. For example, an SLC portion of a memory may be used as a buffer for data being written to the MLC memory, to support fast burst writes of data received from a host, and as the storage area of choice for frequently updated data in a memory system. Regardless of the type of 35 non-volatile memory, the responsiveness of a non-volatile memory system may be affected by its ability to manage internal maintenance operations to generate or maintain enough free blocks to handle subsequent host write requests.

#### BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1A is a block diagram of an example non-volatile memory system.

- FIG. 1B is a block diagram illustrating an exemplary 45 storage module.

- FIG. 1C is a block diagram illustrating a hierarchical storage system.

- FIG. 2A is a block diagram illustrating exemplary components of a controller of a non-volatile memory system.

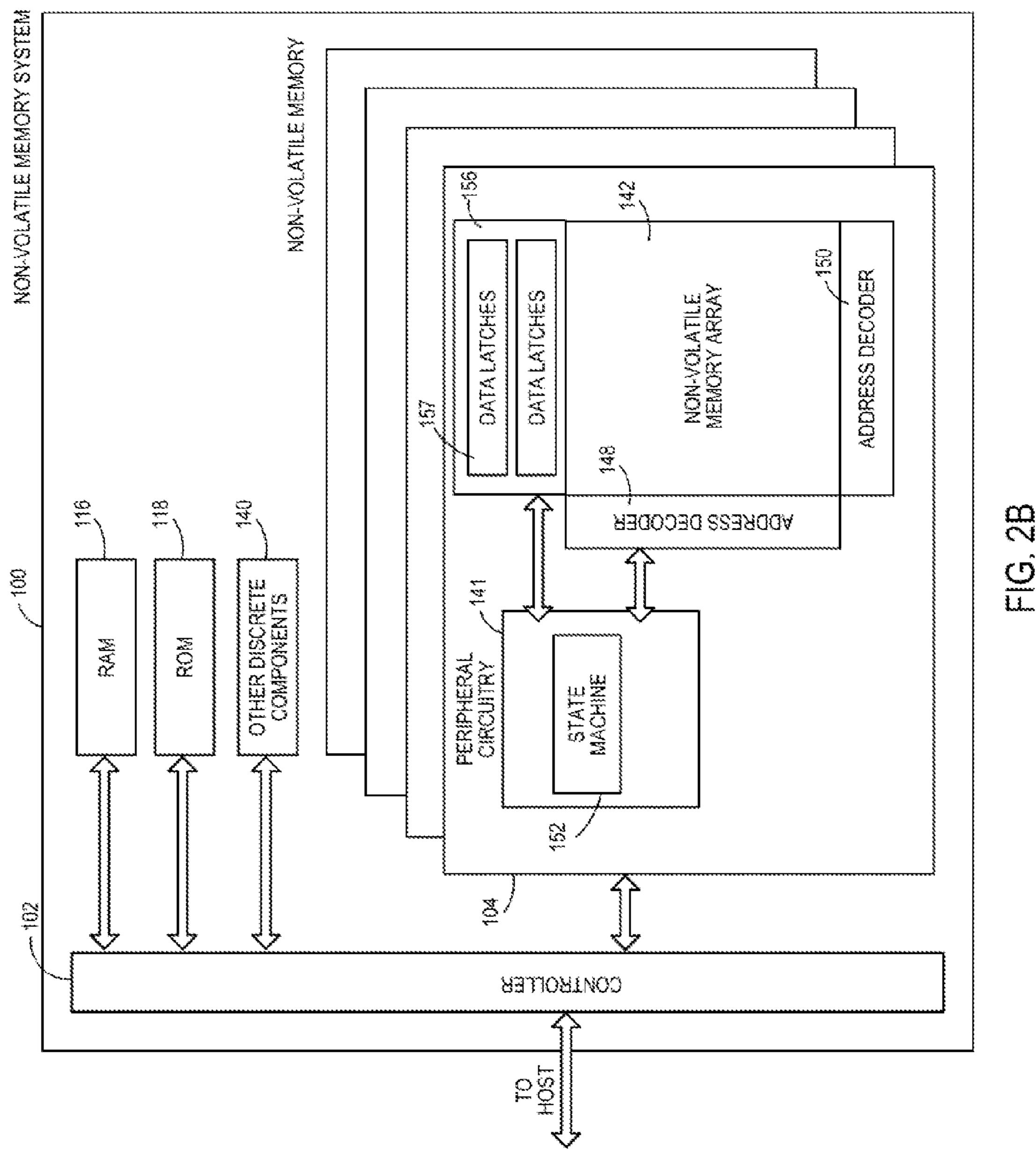

- FIG. 2B is a block diagram illustrating exemplary components of a non-volatile memory of a non-volatile memory storage system.

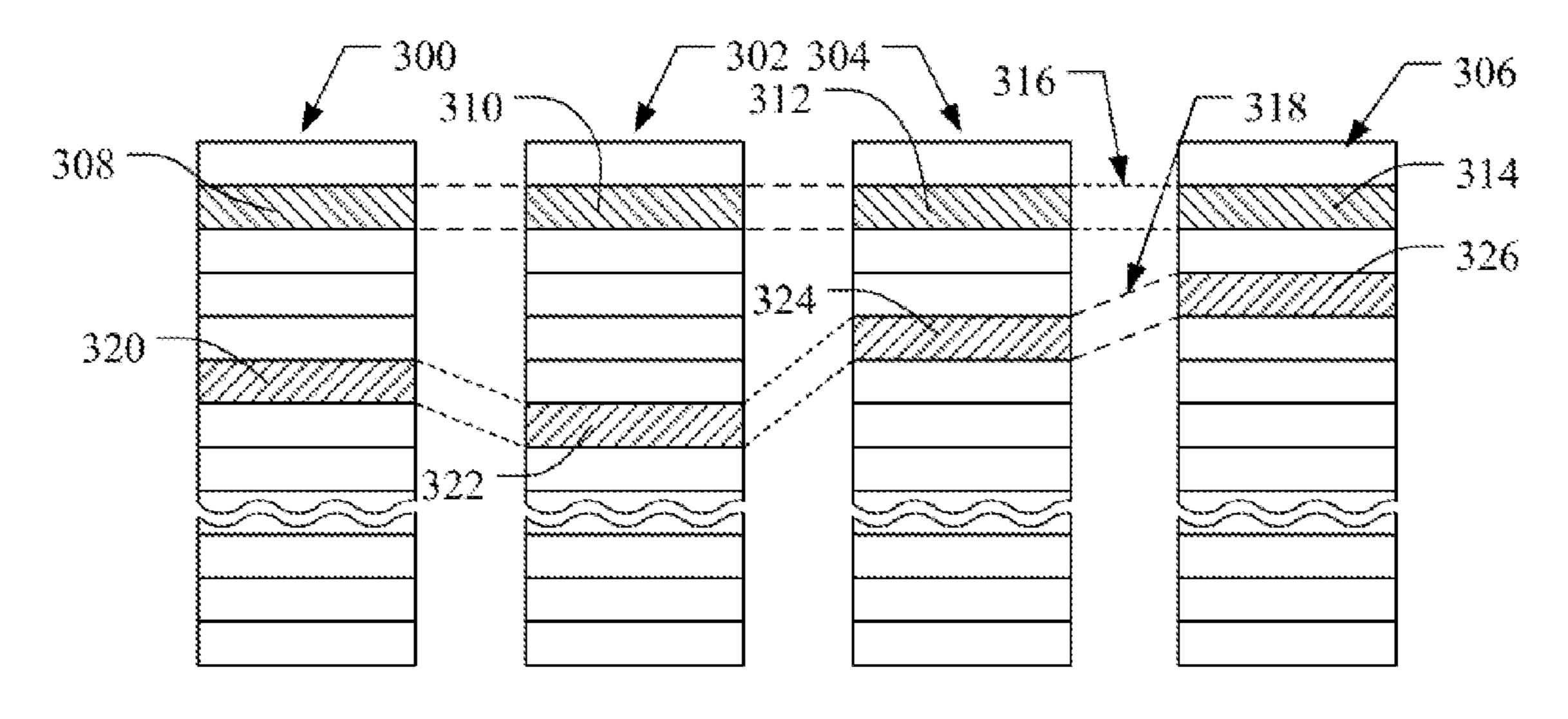

- FIG. 3 illustrates an example physical memory organization of the non-volatile memory system of FIG. 1A.

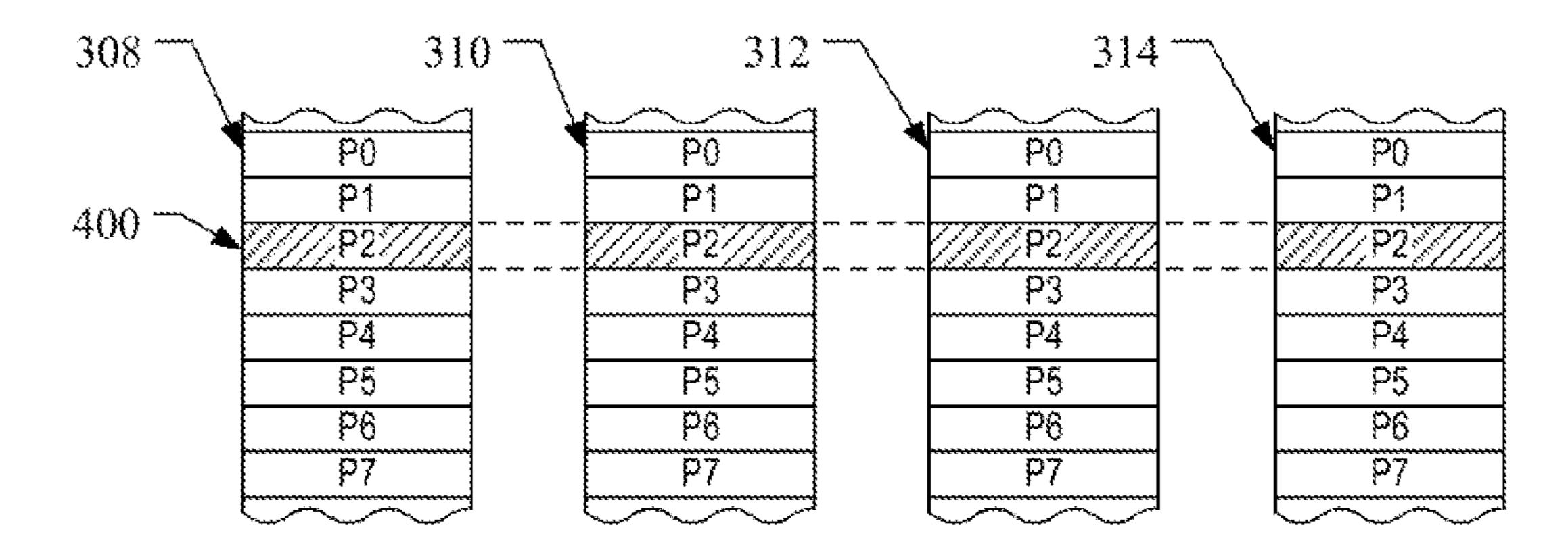

- FIG. 4 shows an expanded view of a portion of the physical memory of FIG. 3.

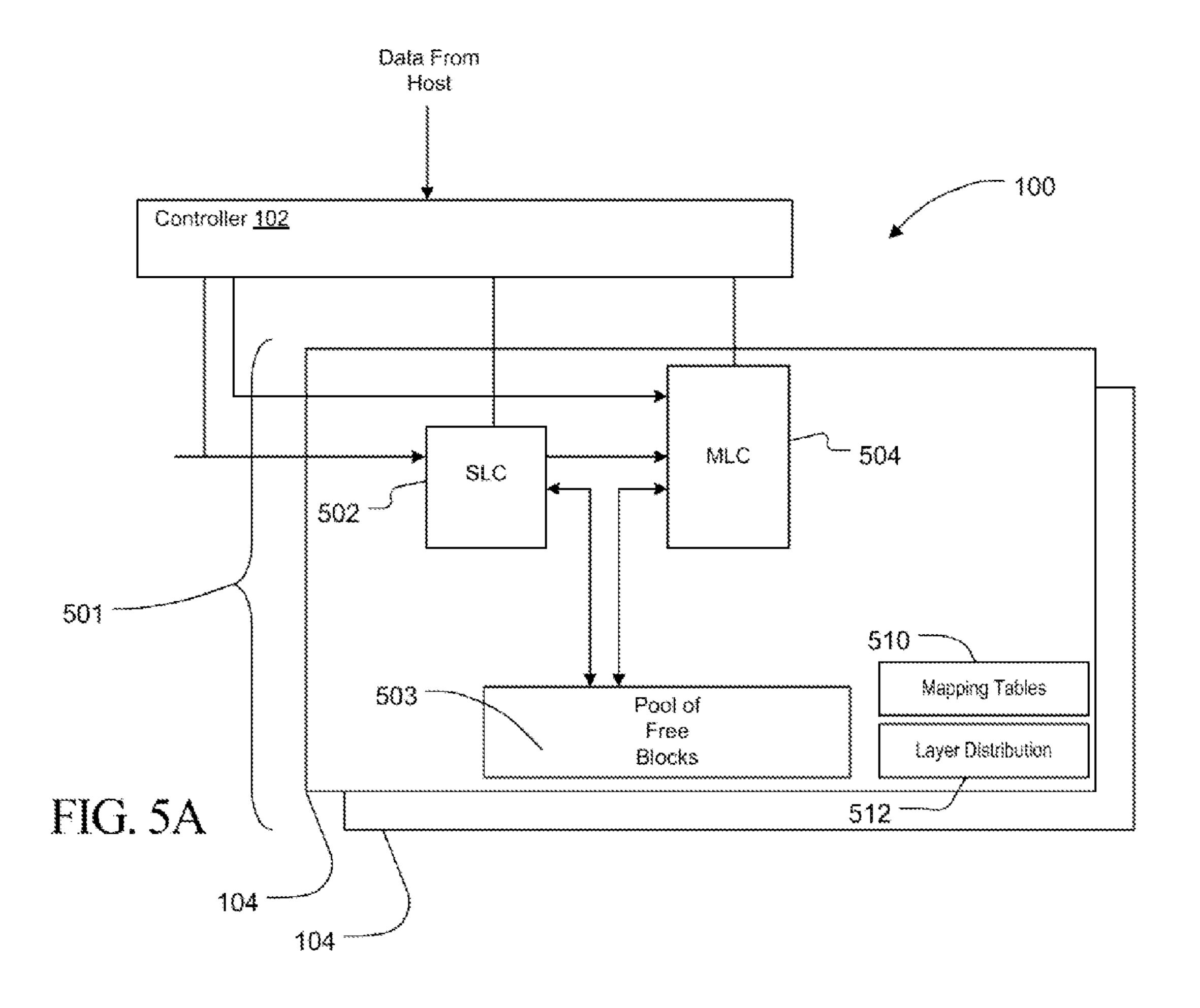

- FIG. 5A illustrates an embodiment of the non-volatile memory storage system of FIG. 1A with a non-volatile memory having cells programmable into different bit-per- 60 cell capacities.

- FIG. **5**B illustrates an arrangement of the storage system of FIG. 5A with a non-volatile memory having two layers contained in each non-volatile memory die within the nonvolatile memory, where each layer is made up cells having 65 a particular bit-per-cell capacity and each layer has a different bit-per-cell capacity.

- FIG. 5C is an alternative arrangement of the storage system of FIG. 5A, where the non-volatile memory of the storage system includes independently managed sets of non-volatile memory die having two layers of different bit-per-cell capacity cells that span across all the nonvolatile memory die in the independently managed set.

- FIG. 6 illustrates an example array of non-volatile memory die organized into banks of memory according to channels.

- FIG. 7 is an embodiment of a data management module usable with the non-volatile memory system of FIG. 2A.

- FIG. 8 is an example distribution of schedule cycles consisting of maintenance operations and host write operahighest performance when the number of data bits per cell 15 tions among different non-volatile memory die in a nonvolatile memory system.

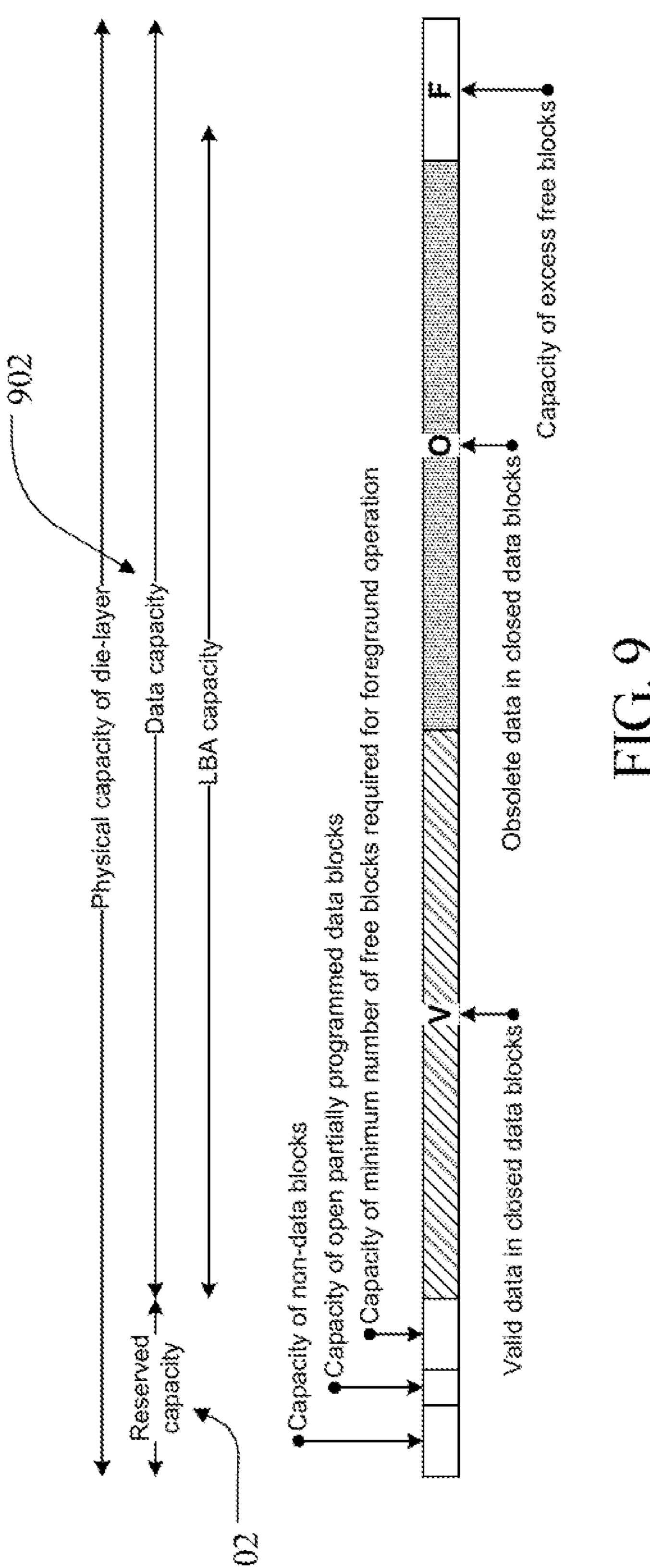

- FIG. 9 shows an example data capacity distribution within a die layer of a given non-volatile memory die.

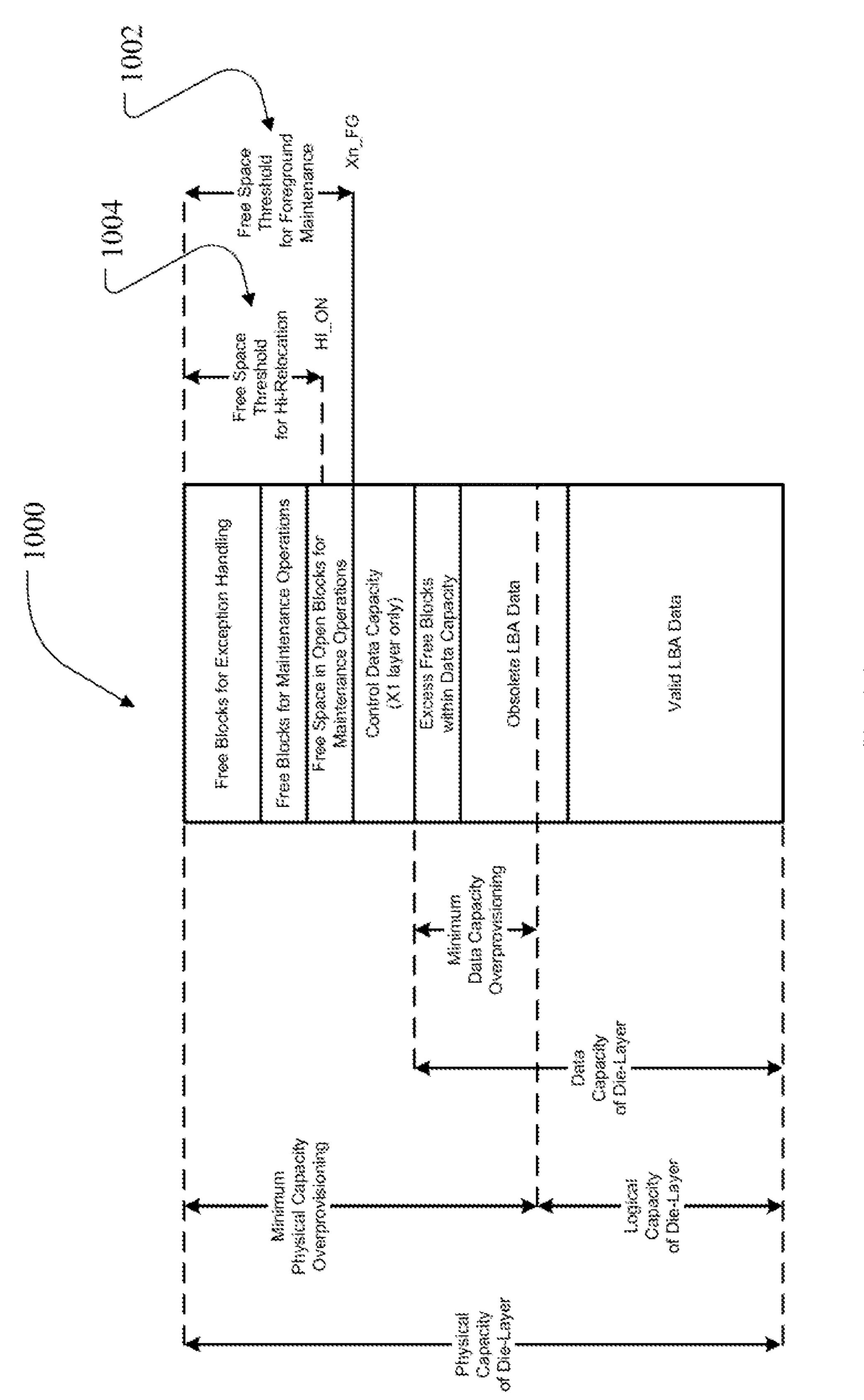

- FIG. 10 is a more detailed die layer capacity distribution of the distribution shown in FIG. 9.

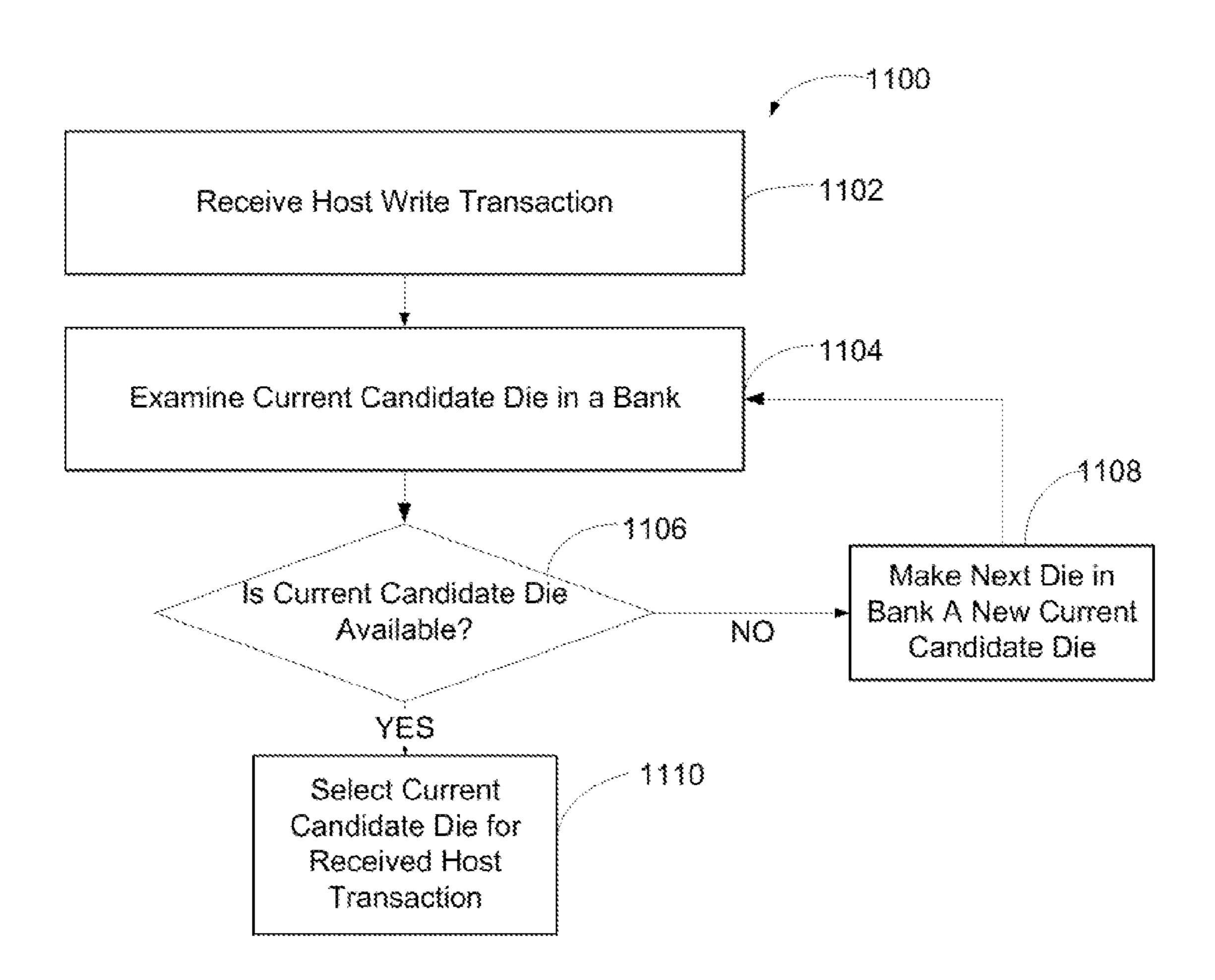

- FIG. 11 is a flow diagram showing an example nonvolatile memory die selection process in a bank of a nonvolatile memory array such as shown in FIG. 6.

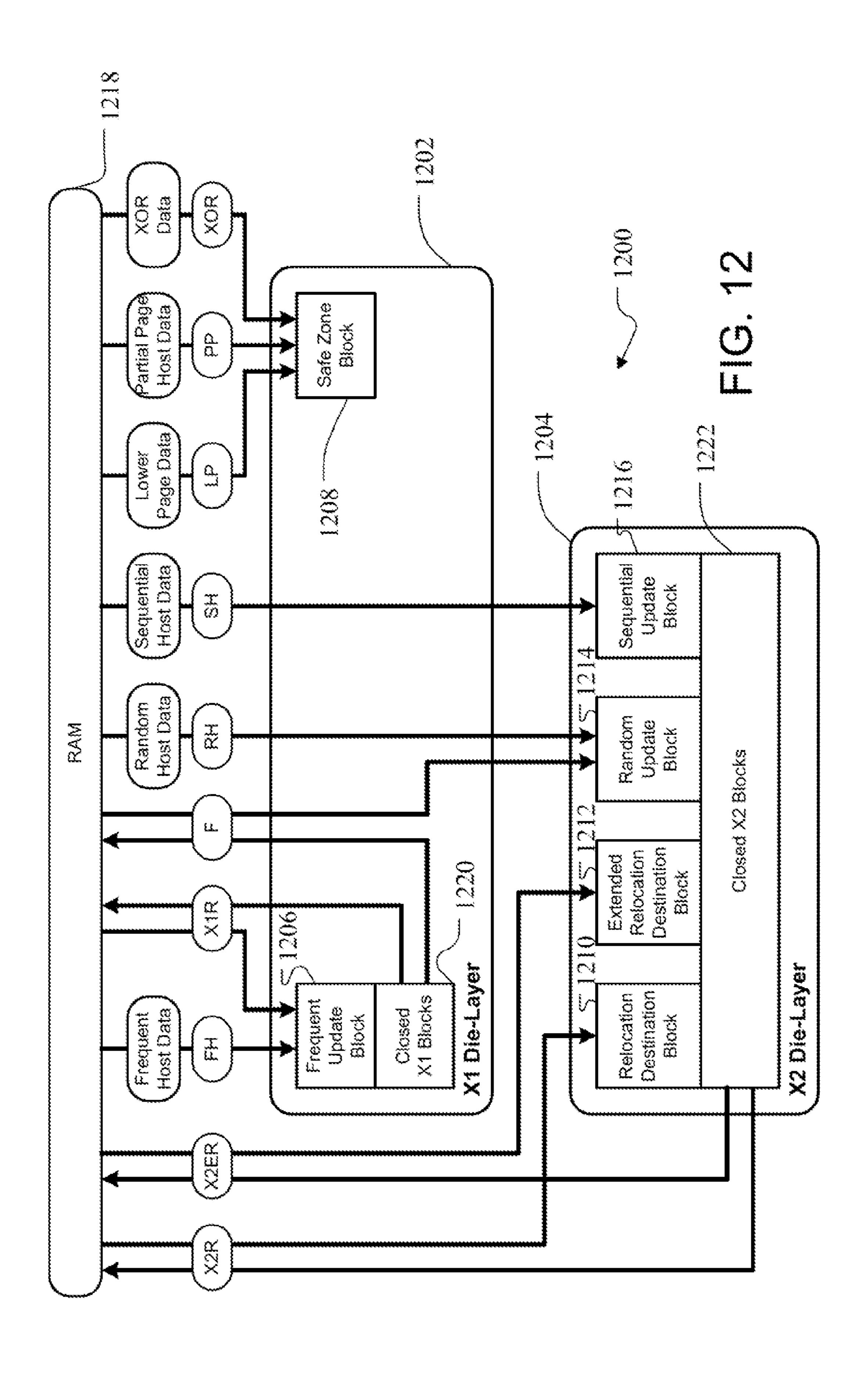

- FIG. 12 illustrates an example block and data path arrangement in a non-volatile memory die having one bit per cell and two bit per cell die layers.

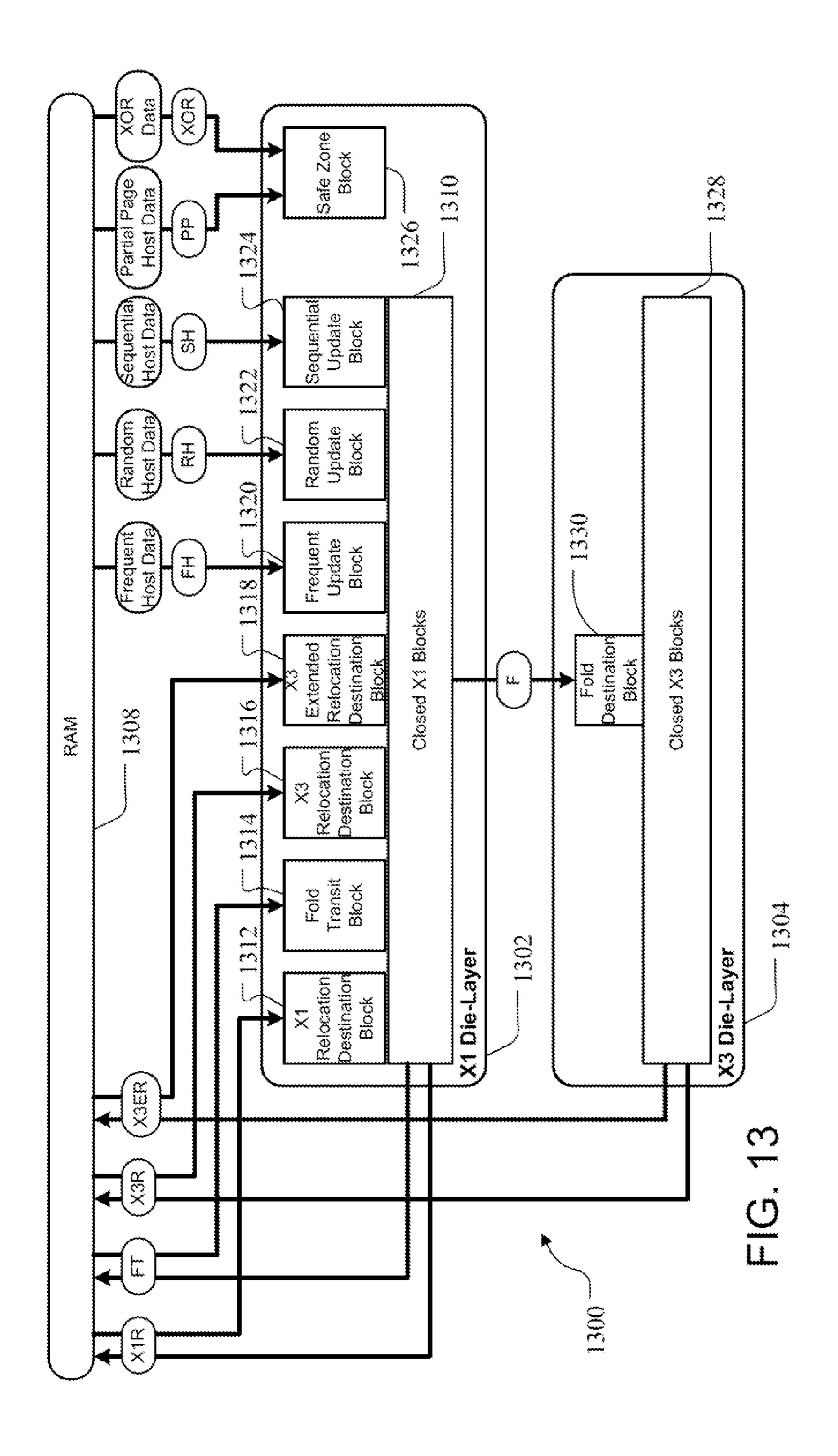

- FIG. 13 illustrates an example block and data path arrangement in a non-volatile memory die having one bit per cell and three bit per cell die layers.

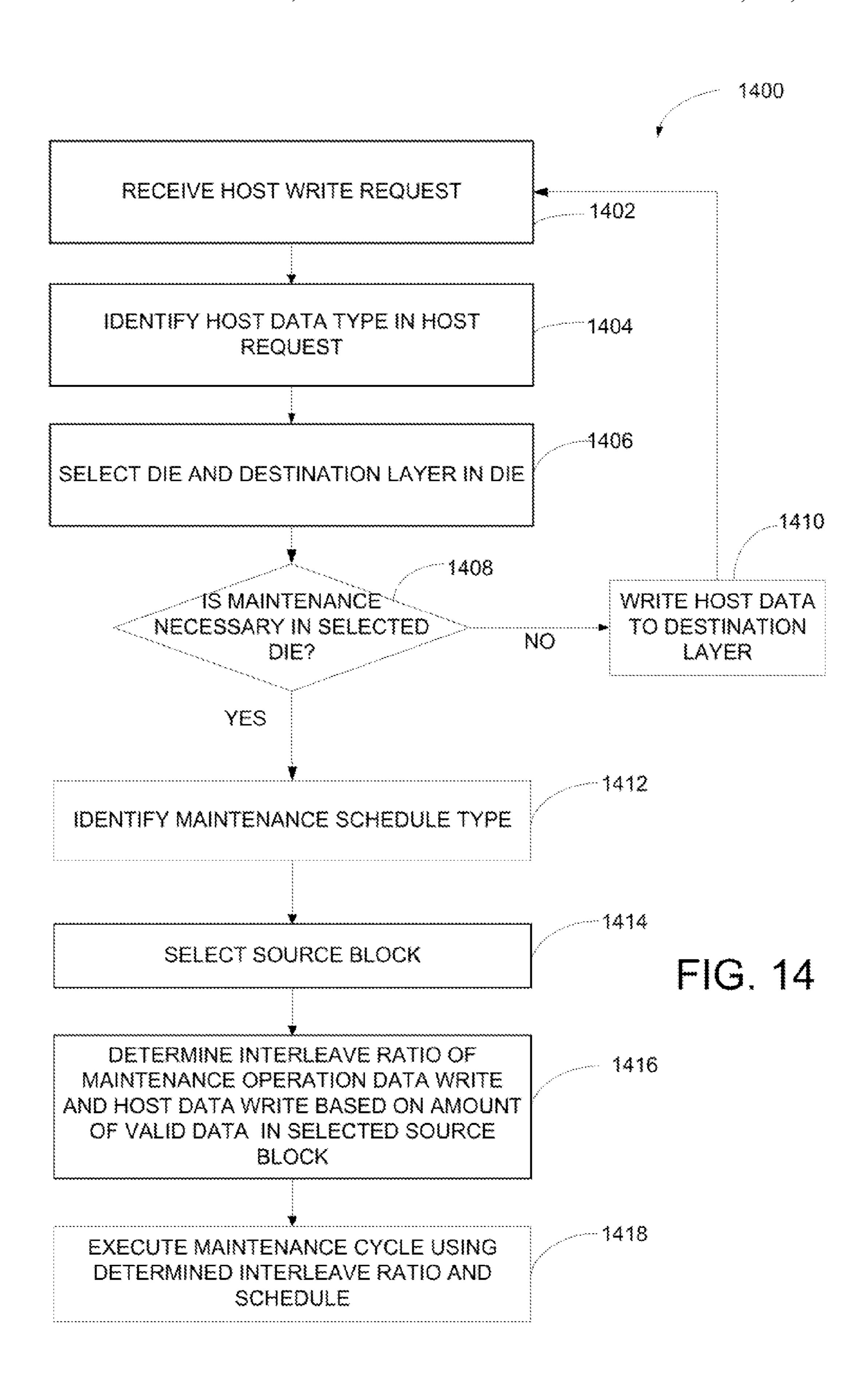

- FIG. 14 is a flow diagram of an embodiment of a schedule cycle generation and execution process in a non-volatile memory system.

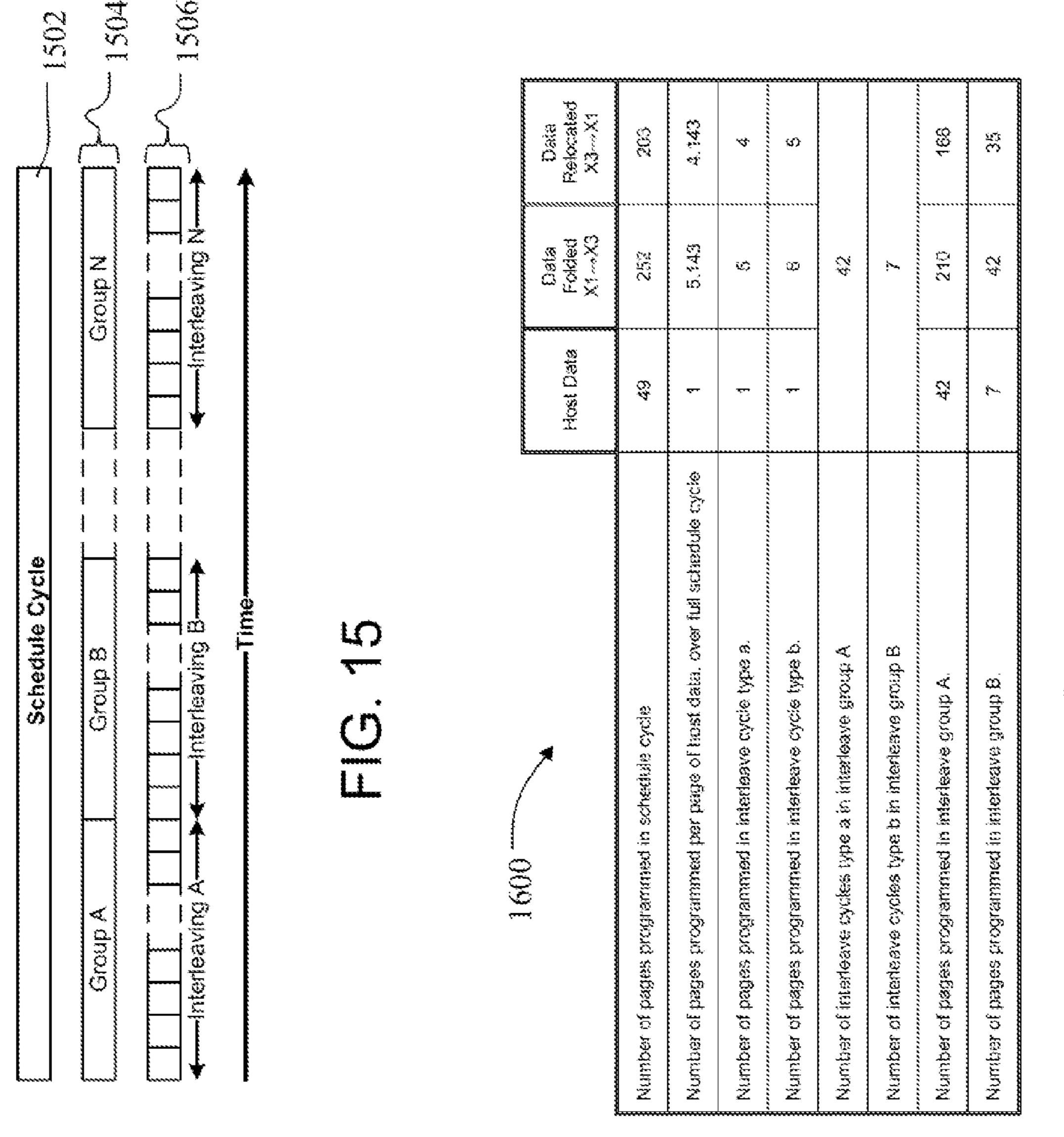

- FIG. 15 is a diagram illustrating programming schedule cycle interleaving executable as part of the process of FIG.

- FIG. 16 is chart of example interleave cycles and interleave groups for a schedule cycle based on a schedule cycle type and source block selected according to the process of 40 FIG. **14**.

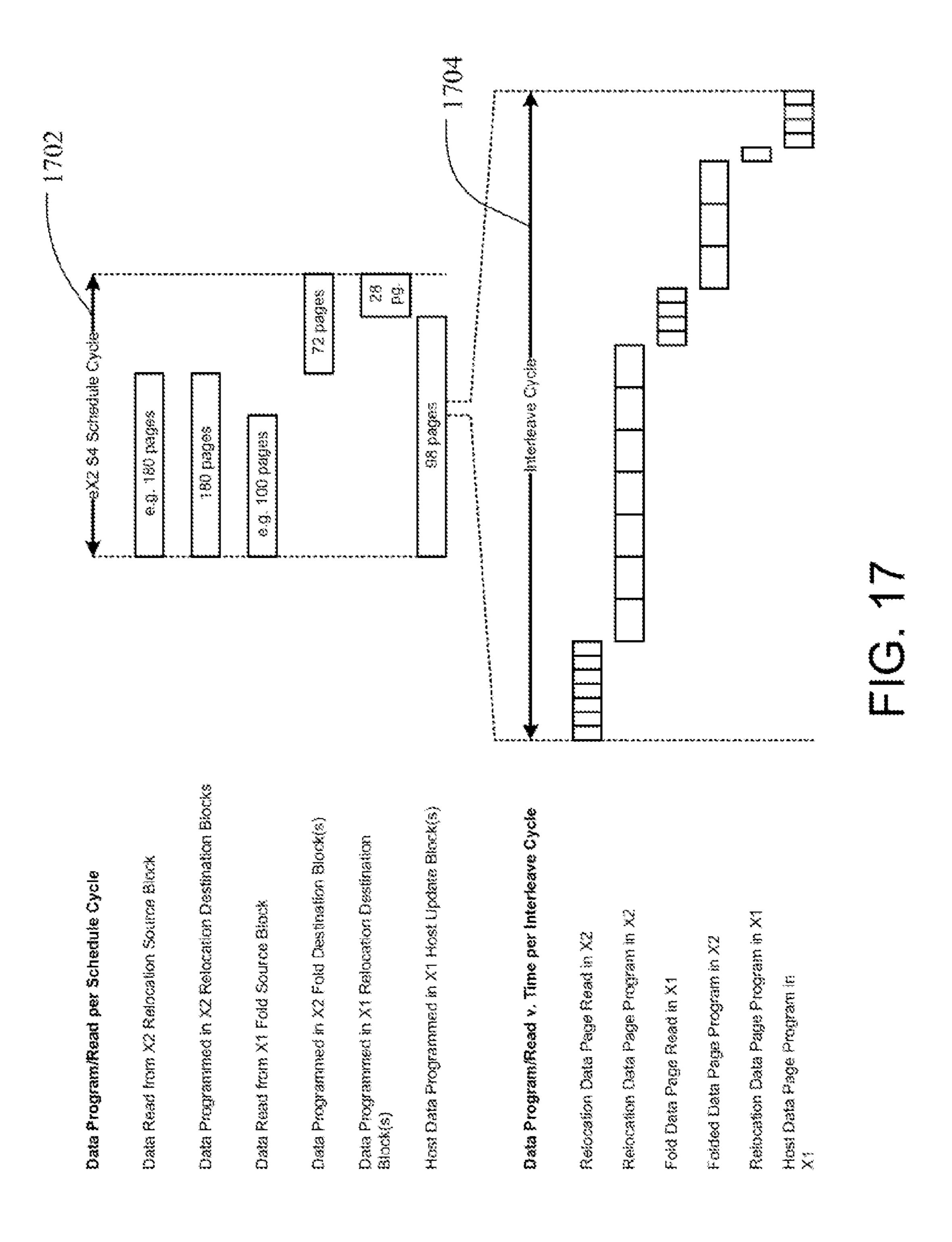

- FIG. 17 is a chart of an alternative schedule cycle and interleave cycle determined according to the process of FIG. **14**.

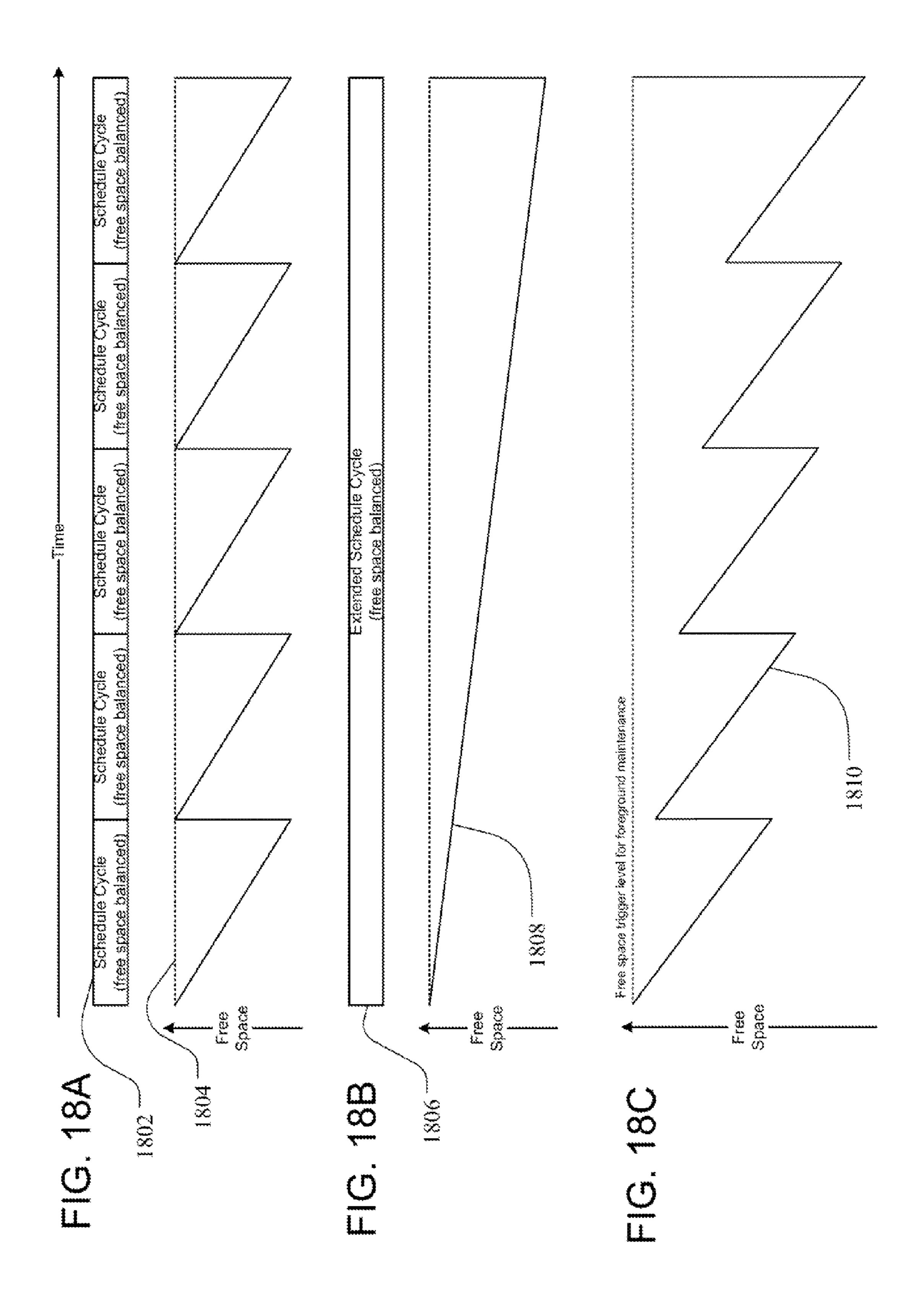

- FIGS. 18A-18C illustrate an example free space creation and consumption charts for individual schedule cycles, extended schedule cycles and a composite of schedule cycles and an extended schedule cycle.

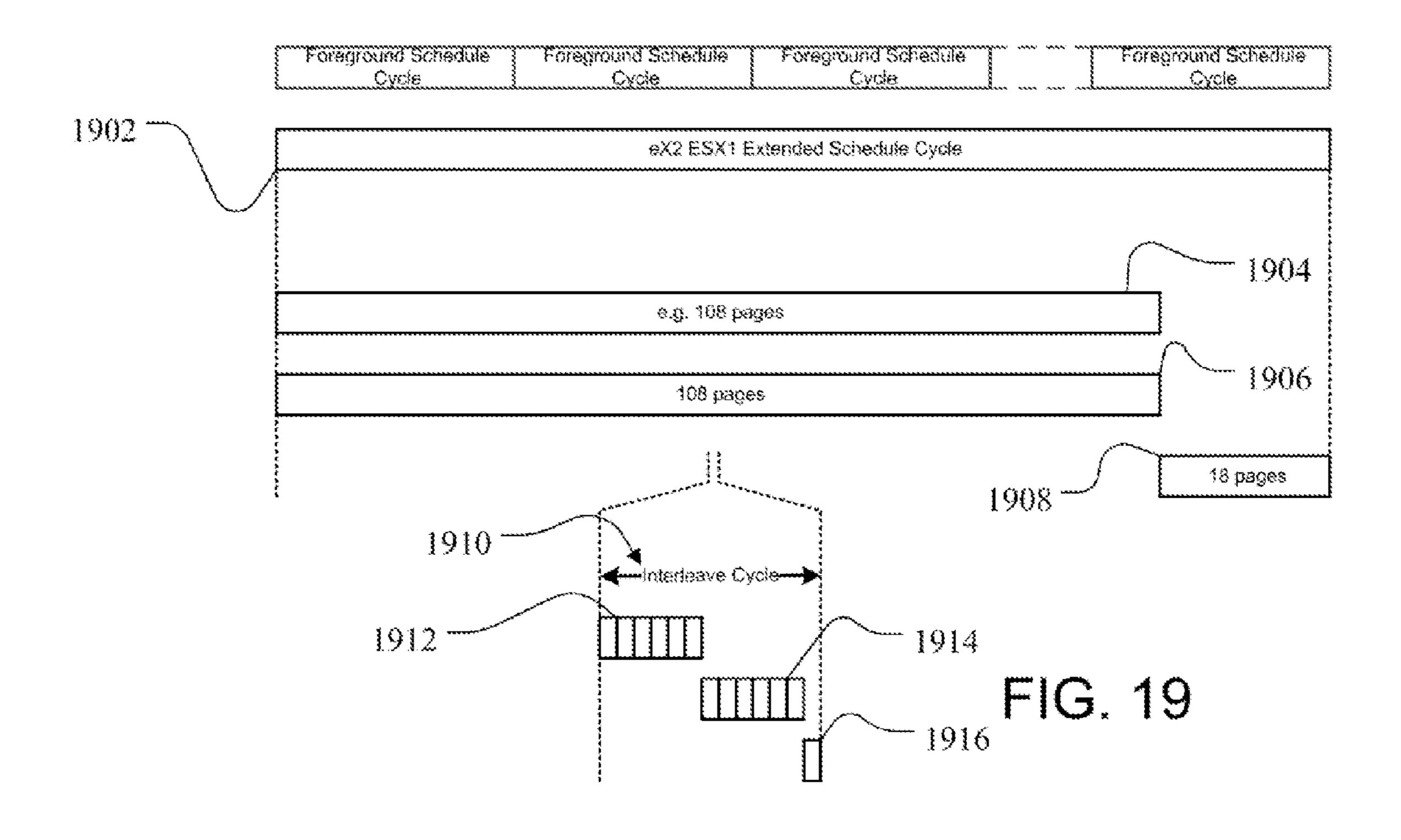

- FIG. 19 illustrates an example extended maintenance schedule and associated interleave cycle in a one bit per cell 50 die layer of a non-volatile memory die having one bit per cell and two bit per cell die layers.

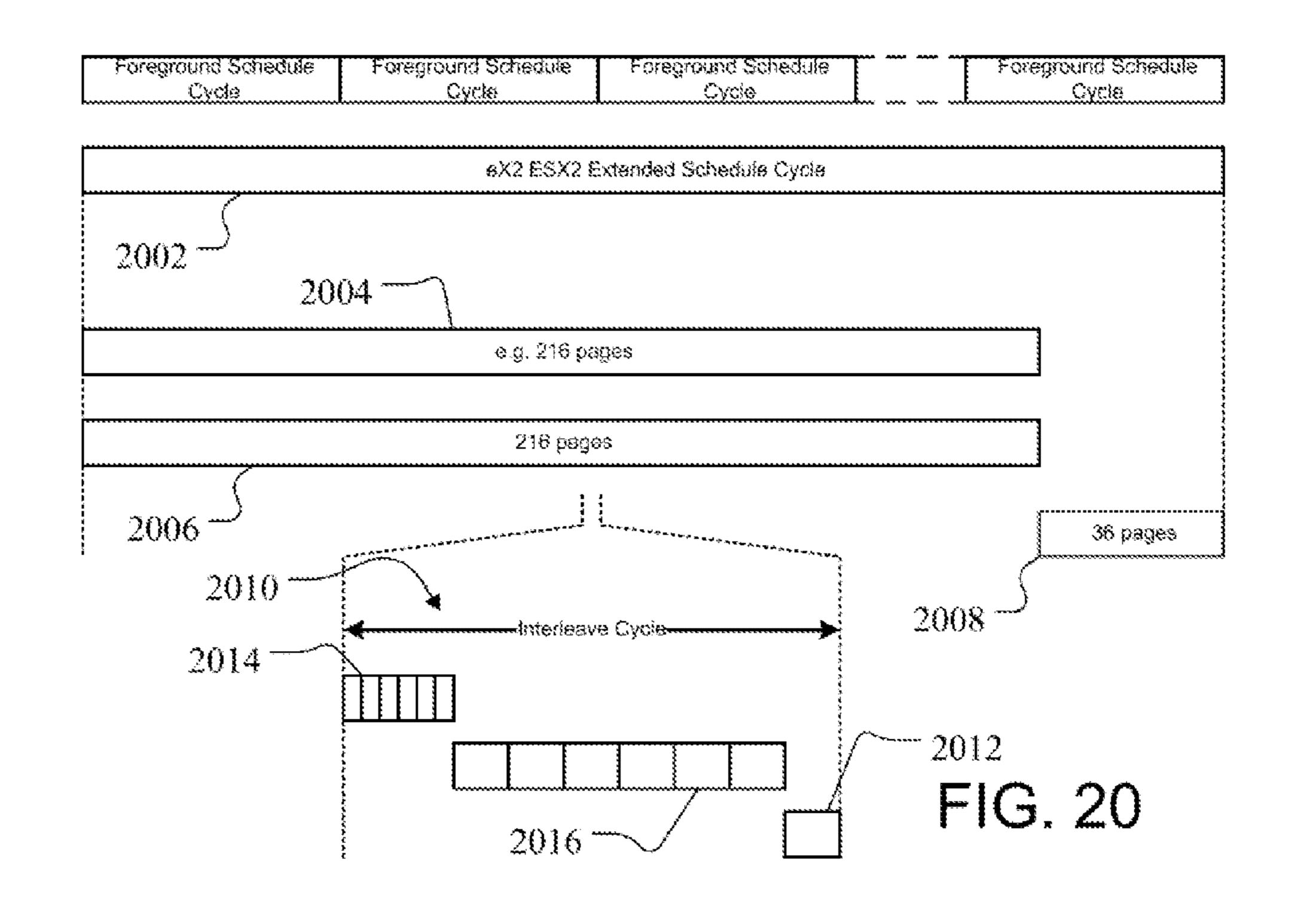

- FIG. 20 illustrates an example extended maintenance schedule and associated interleave cycle in a two bit per cell die layer of a non-volatile memory die having one bit per 55 cell and two bit per cell die layers.

- FIG. 21 illustrates and example extended maintenance schedule and associated interleave cycle in a three bit per cell die layer of a non-volatile memory die having one bit per cell and three bit per cell die layers.

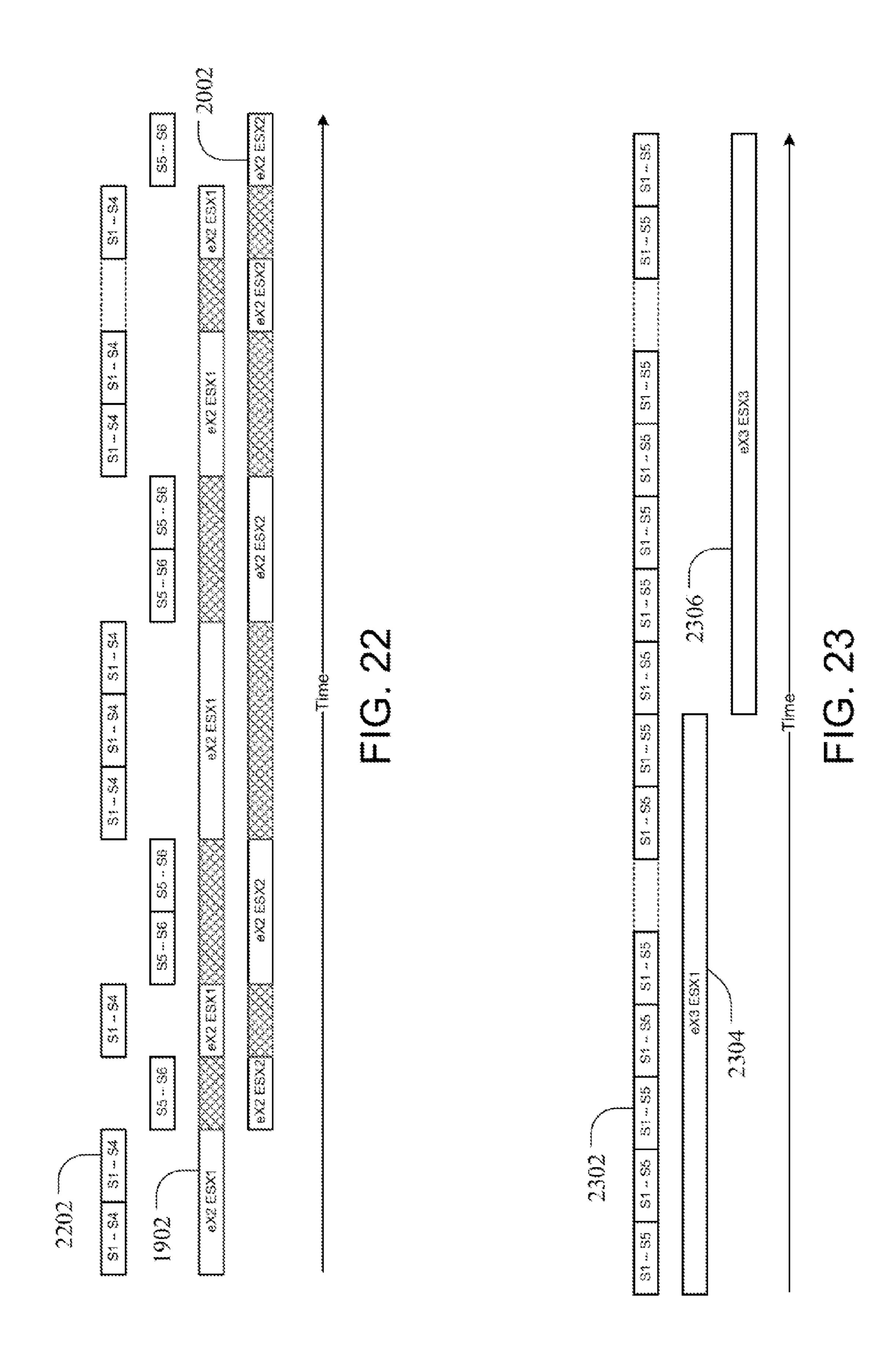

- FIG. 22 illustrates an example timeline of foreground schedule cycles and concurrent extended maintenance cycles executing in an embodiment of a non-volatile memory die having both one and two bit per cell die layers.

- FIG. 23 illustrates an example timeline of foreground schedule cycles and concurrent extended maintenance cycles executing in an embodiment of a non-volatile memory die having both one and three bit per cell die layers.

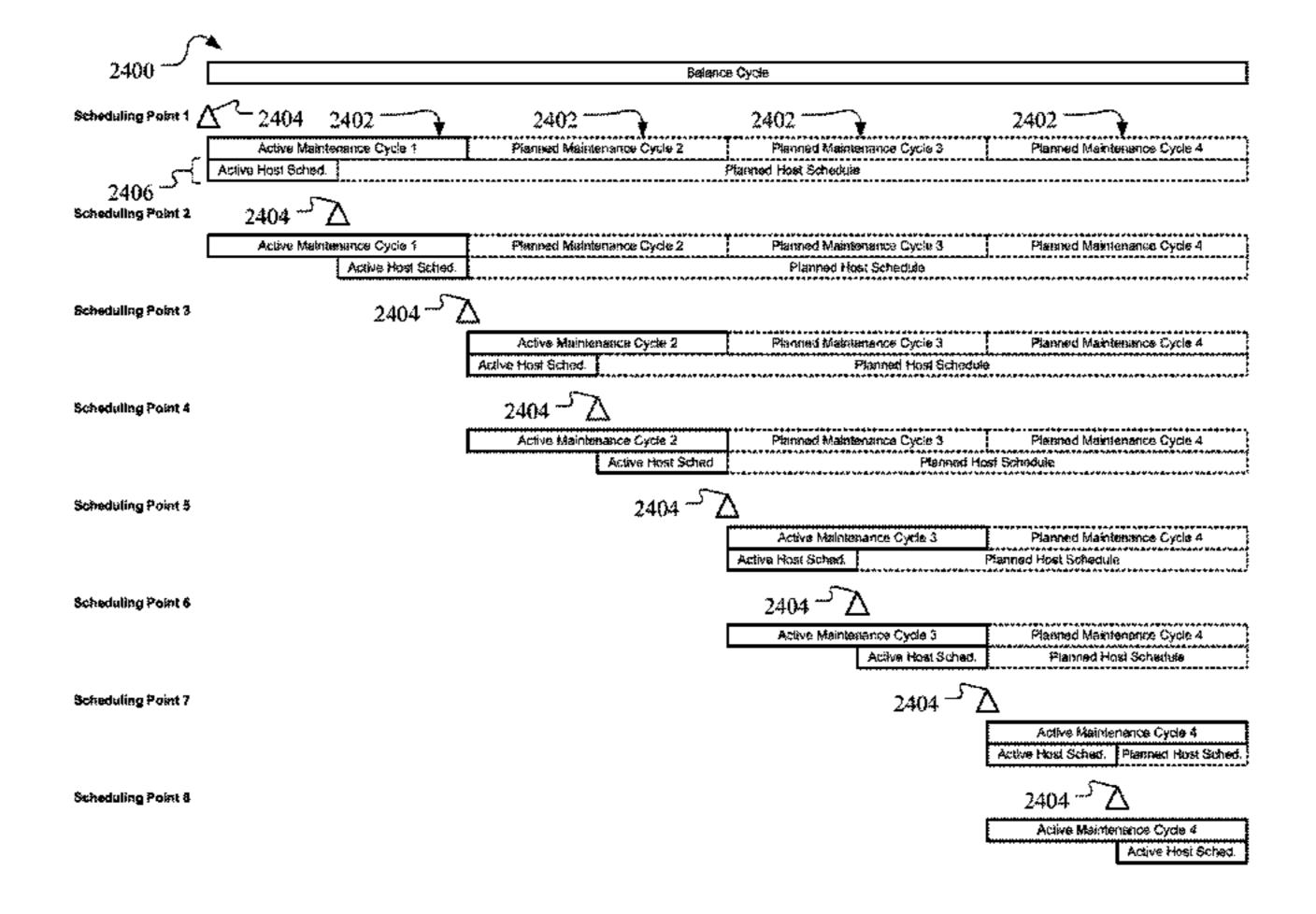

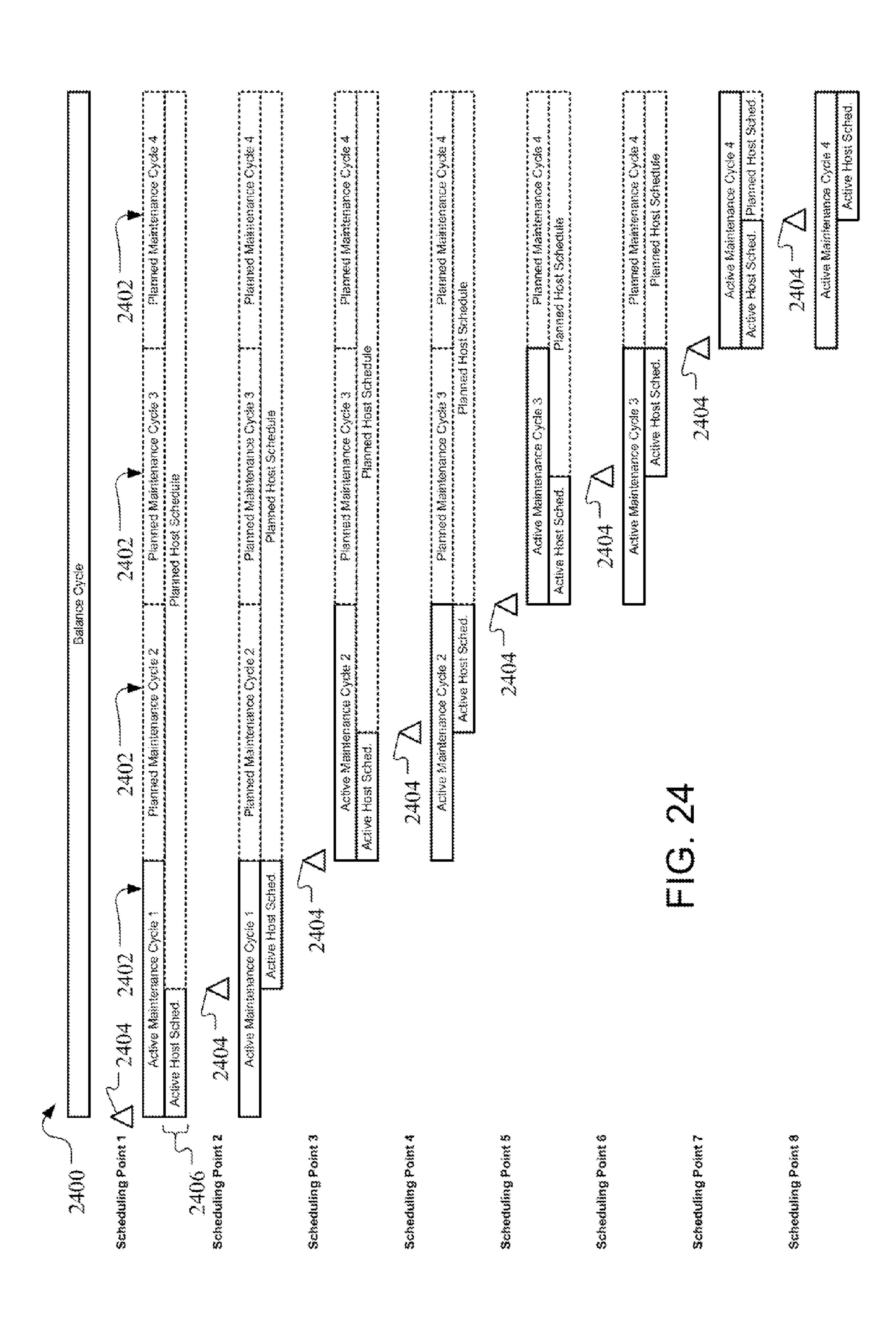

FIG. 24 illustrates on example of a balance cycle and the progression of scheduling points in each of a plurality of maintenance cycles in the balance cycle.

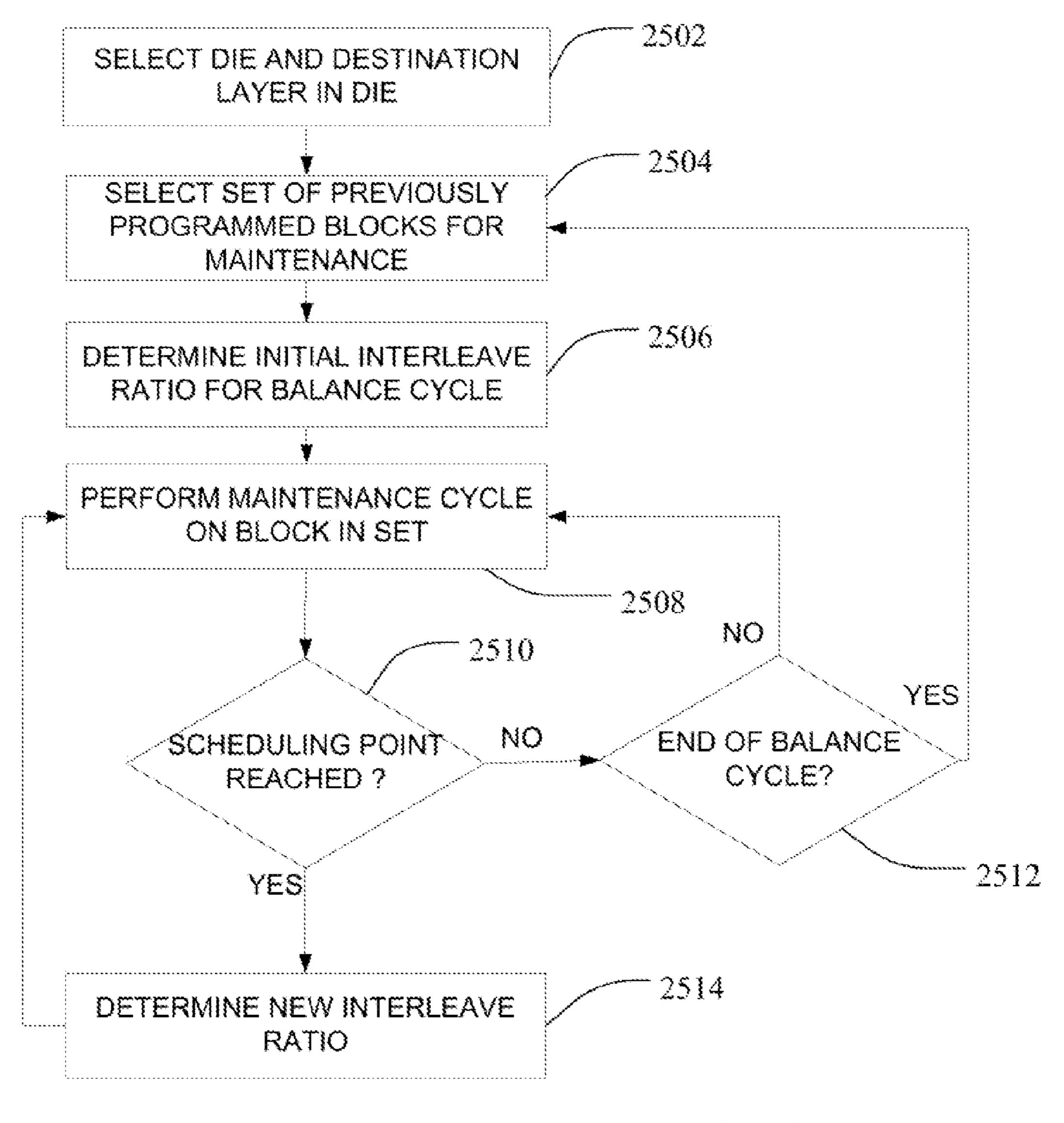

FIG. **25** is a flow diagram of an embodiment for generation and execution of a balance cycle of maintenance cycles, 5 such as illustrated in FIG. **24**, in a non-volatile memory system.

#### DETAILED DESCRIPTION

By way of introduction, the below embodiments relate to systems and methods for managing programming schedules in non-volatile memory so that impact on responsiveness to host commands may be reduced. As set forth in greater detail below, the concept of foreground maintenance schedule 15 cycles is introduced where foreground maintenance operations to generate free space in a given non-volatile memory die of a memory system are interleaved with host data writes. More particularly, the concept of a balance cycle that combines foreground maintenance for a predetermined 20 number of schedule cycles is discussed that may provide less variation of host data write speed than individual foreground maintenance schedule cycles. Methods for determining interleaving techniques for the balance cycle of maintenance and host write operations, and for adjusting interleave ratios 25 and/or the source maintenance blocks during a balance cycle are discussed.

In one embodiment, a method of managing data includes performing, in a non-volatile memory system having a non-volatile memory with a plurality of layers and a con- 30 troller in communication with the at least one non-volatile memory, each of the plurality of layers having a different bit-per-cell data capacity, the step of identifying a layer in the plurality of layers for performing a balance cycle of maintenance operations. The non-volatile memory system 35 selects a fixed plurality of previously programmed blocks in the identified layer for the balance cycle, determines a balance cycle interleave ratio of host data writes to maintenance writes based on a total amount of valid data in the fixed plurality of previously programmed blocks and initi- 40 ates a maintenance operation on a first block of the fixed plurality of previously programmed blocks using the determined balance cycle interleave ratio. At each of a plurality of predetermined scheduling points in the balance cycle of maintenance operations, the non-volatile memory system 45 determines an updated balance cycle interleave ratio based on a current remaining amount of valid data in the fixed plurality of previously programmed blocks. The updated balance cycle interleave ratio is then applied to remaining maintenance operations in the balance cycle of maintenance 50 operations.

In some variations, selecting the fixed plurality of previously programmed blocks includes selecting previously programmed blocks having a least amount of valid data. Also, the balance cycle of maintenance operations includes operations to move all valid data from each of the fixed plurality of previously programmed blocks selected for the balance cycle, interleaved with writing an amount of host data equal to an amount of obsolete data in the plurality of previously programmed blocks, such that an amount of free space 60 created by moving the valid data from the fixed plurality of previously programmed blocks balances an amount of free space consumed by host writes during the balance cycle.

In one embodiment, determining the updated balance cycle interleave ratio may include determining, when a 65 predetermined scheduling point is reached in the balance cycle, whether a change has occurred in an amount of valid

4

data in any of the fixed plurality of previously programmed blocks still awaiting a maintenance operation in the balance cycle. When a change has occurred, the non-volatile memory system may update the balance cycle interleave ratio to increase the ratio of host writes to maintenance writes in a remainder of the balance cycle based on the change.

Alternatively determining the updated balance cycle interleave ratio may include determining, when a predetermined scheduling point is reached in the balance cycle, whether an amount of valid data in another previously programmed block in the layer is less than an amount of valid data in a remaining one of the fixed plurality of previously programmed blocks awaiting a maintenance operation. When the amount of valid data in the another previously programmed block is less than the amount of valid data in the remaining one, the remaining one of the fixed plurality of previously programmed blocks awaiting the maintenance operation may be replaced with the another previously programmed block to form a current remaining set of the fixed plurality of previously programmed blocks awaiting the maintenance operation. Additionally, the non-volatile memory system may then re-evaluate the balance cycle interleave ratio based on a current remaining amount of valid data in the current remaining set and apply that updated interleave ratio to remaining maintenance operations in the balance cycle.

In another embodiment, a method of managing data includes, in a non-volatile memory system having a nonvolatile memory with a plurality of layers and a controller in communication with the at least one non-volatile memory, selecting a fixed plurality of previously programmed blocks in the non-volatile memory for executing a balance cycle of maintenance operations. A balance cycle interleave ratio of host data writes to maintenance writes is determined based on a total amount of valid data in the fixed plurality of previously programmed blocks. A maintenance operation is initiated on a first block of the fixed plurality of previously programmed blocks using the determined balance cycle interleave ratio. After initiating the maintenance operation, and in response to reaching a predetermined scheduling point in the balance cycle, the non-volatile memory system determines whether to substitute a different previously programmed block for one of the fixed plurality of previously programmed blocks.

Determining whether to substitute the different previously programmed block for one of the fixed plurality of previously programmed blocks may include determining whether to substitute the different previously programmed block based on a change in an amount of valid data in the different previously programmed block. The non-volatile memory system may then substitute the different previously programmed block for one of the fixed plurality of previously programmed blocks when the different previously programmed blocks contains less valid data than the one of the fixed plurality.

Alternatively, determining whether to substitute the different previously programmed block for one of the fixed plurality of previously programmed blocks may include determining whether to substitute the different previously programmed block based on a change in an amount of valid data in one of the fixed plurality of previously programmed blocks. The non-volatile memory system may then substitute the different previously programmed block for one of the fixed plurality of previously programmed blocks when

the amount of valid data in one of the fixed plurality decreases prior to initiating a maintenance operation on that one of the fixed plurality.

In yet another embodiment, a memory system is described. The memory system includes at least one nonvolatile memory having a plurality of layers, each of the plurality of layers having a different bit-per-cell data capacity and a plurality of memory blocks. Data management circuitry is in communication with the non-volatile memory, and the data management circuitry is configured to select a 10 fixed plurality of previously programmed blocks in one of the plurality of layers layer for a balance cycle of maintenance operations, the balance cycle comprising a set of maintenance cycles for the fixed plurality of previously programmed blocks. The memory system also includes 15 program interleave circuitry configured to determine a balance cycle interleave ratio of host data writes to maintenance writes based on a total amount of valid data in the fixed plurality of previously programmed blocks. The program interleave circuitry is further configured to, upon determin- 20 ing the balance cycle interleave ratio, initiate a maintenance operation on a first block of the fixed plurality of previously programmed blocks using the determined balance cycle interleave ratio. At each of a plurality of predetermined scheduling points in the balance cycle of maintenance 25 operations, the program interleave circuitry is configured to determine an updated balance cycle interleave ratio based on a current remaining amount of valid data in the fixed plurality of previously programmed blocks. The program interleave circuitry is then configured to apply the updated 30 balance cycle interleave ratio to remaining maintenance operations in the balance cycle of maintenance operations until reaching a next scheduling point for the balance cycle.

In some embodiments, the memory is a three-dimensional memory and/or the memory system is embedded in a host or is removably connected to a host.

Other embodiments are possible, and each of the embodiments can be used alone or together in combination. Accordingly, various embodiments will now be described with reference to the attached drawings.

#### Exemplary Embodiments

Described herein are systems and methods for managing programming schedules in non-volatile memory so that 45 impact on responsiveness to host commands may be reduced. As set forth in greater detail below, the concept of schedule cycles is introduced where foreground maintenance operations to generate more free space in a given non-volatile memory die of a memory system are inter- 50 leaved with host data writes. A predetermined number of schedule cycle types, some that do not require maintenance operations and others that require interleaving maintenance operations with host write operations, may be preset for a given type of non-volatile memory die. Each schedule cycle 55 type that includes maintenance operations may be based on freeing one block of previously programmed data rather than on writing any fixed amount of host data. Methods for selecting the die and the schedule cycle type needed for the selected die are disclosed, as well as interleaving techniques 60 for the maintenance and host write operations of schedule types having both host write and maintenance operations.

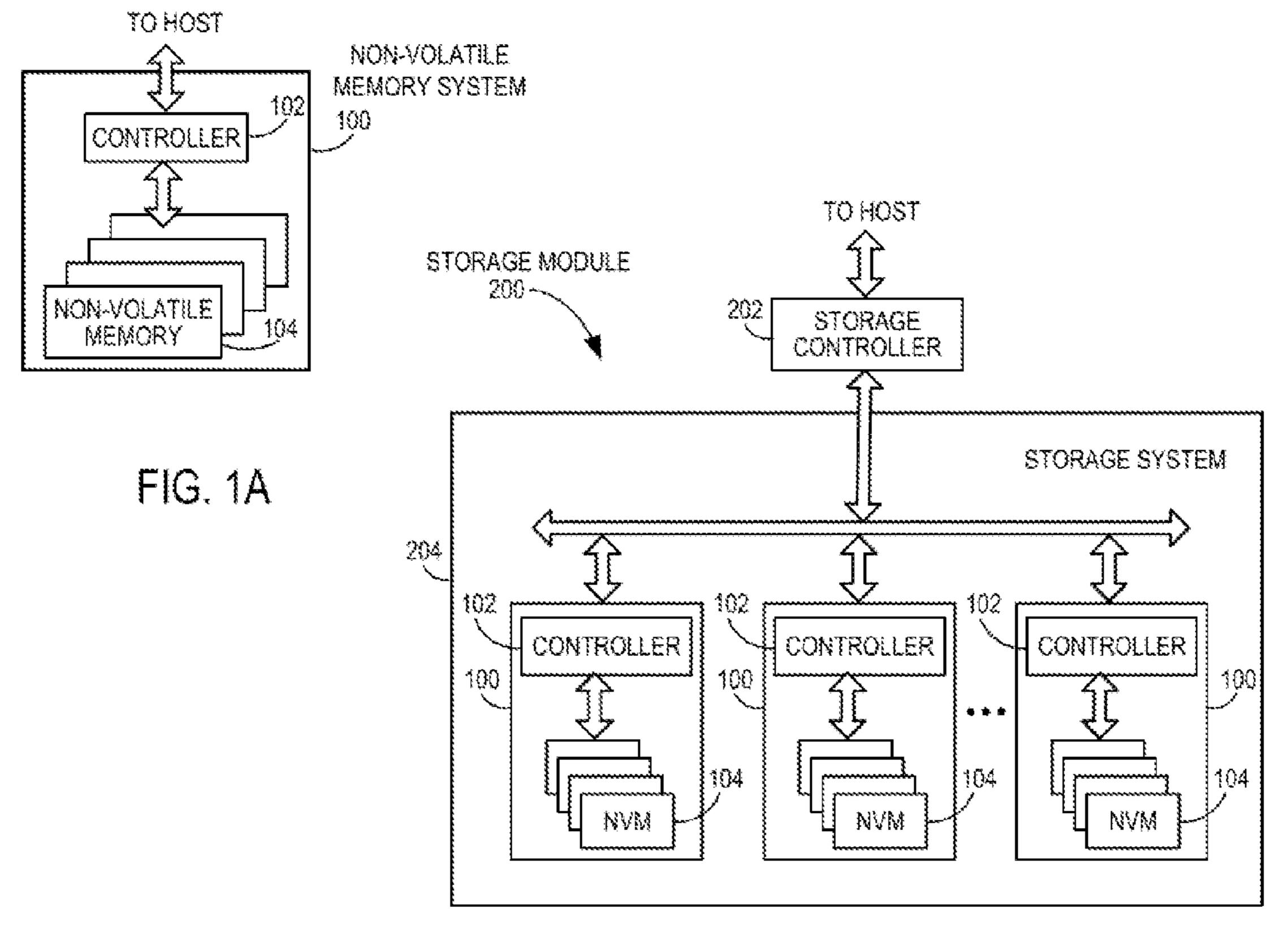

Examples of suitable non-volatile memory arrangements in which the systems and methods disclosed herein may be used are illustrated in FIGS. 1A-1C. FIG. 1A is a block 65 diagram illustrating a non-volatile memory system. The non-volatile memory system 100 includes a controller 102

6

and non-volatile memory that may be made up of one or more non-volatile memory die 104. As used herein, the term die refers to the set of non-volatile memory cells, and associated circuitry for managing the physical operation of those non-volatile memory cells, that are formed on a single semiconductor substrate. Controller 102 interfaces with a host system and transmits command sequences for read, program, and erase operations to non-volatile memory die 104.

The controller 102 (which may be a flash memory controller) can take the form of processing circuitry, a microprocessor or processor, and a computer-readable medium that stores computer-readable program code (e.g., software or firmware) executable by the (micro)processor, logic gates, switches, an application specific integrated circuit (ASIC), a programmable logic controller, and an embedded microcontroller, for example. The controller 102 can be configured with hardware and/or firmware to perform the various functions described below and shown in the flow diagrams. Also, some of the components shown as being internal to the controller can also be stored external to the controller, and other components can be used. Additionally, the phrase "operatively in communication with" could mean directly in communication with or indirectly (wired or wireless) in communication with through one or more components, which may or may not be shown or described herein.

As used herein, a flash memory controller is a device that manages data stored on flash memory and communicates with a host, such as a computer or electronic device. A flash memory controller can have functionality in addition to the specific functionality described herein. For example, the flash memory controller can format the flash memory to ensure the memory is operating properly, map out bad flash memory cells, and allocate spare cells to be substituted for future failed cells. Some part of the spare cells can be used to hold firmware to operate the flash memory controller and implement other features. In operation, when a host needs to read data from or write data to the flash memory, it will 40 communicate with the flash memory controller. If the host provides a logical address to which data is to be read/written, the flash memory controller can convert the logical address received from the host to a physical address in the flash memory. (Alternatively, the host can provide the physical address). The flash memory controller can also perform various memory management functions, such as, but not limited to, wear leveling (distributing writes to avoid wearing out specific blocks of memory that would otherwise be repeatedly written to) and garbage collection (after a block is full, moving only the valid pages of data to a new block, so the full block can be erased and reused).

Non-volatile memory die 104 may include any suitable non-volatile storage medium, including NAND flash memory cells and/or NOR flash memory cells. The memory cells can take the form of solid-state (e.g., flash) memory cells and can be one-time programmable, few-time programmable, or many-time programmable. The memory cells can also be single-level cells (SLC), multiple-level cells (MLC), triple-level cells (TLC), or use other memory technologies, now known or later developed. Also, the memory cells can be arranged in a two-dimensional or three-dimensional fashion.

The interface between controller 102 and non-volatile memory die 104 may be any suitable flash interface, such as Toggle Mode 200, 400, or 800. In one embodiment, memory system 100 may be a card based system, such as a secure digital (SD) or a micro secure digital (micro-SD) card. In an

alternate embodiment, memory system 100 may be part of an embedded memory system.

Although, in the example illustrated in FIG. 1A, non-volatile memory system 100 includes a single channel between controller 102 and non-volatile memory die 104, 5 the subject matter described herein is not limited to having a single memory channel. For example, in some NAND memory system architectures, 2, 4, 8 or more NAND channels may exist between the controller and the NAND memory device, depending on controller capabilities. In any 10 of the embodiments described herein, more than a single channel may exist between the controller and the memory die, even if a single channel is shown in the drawings.

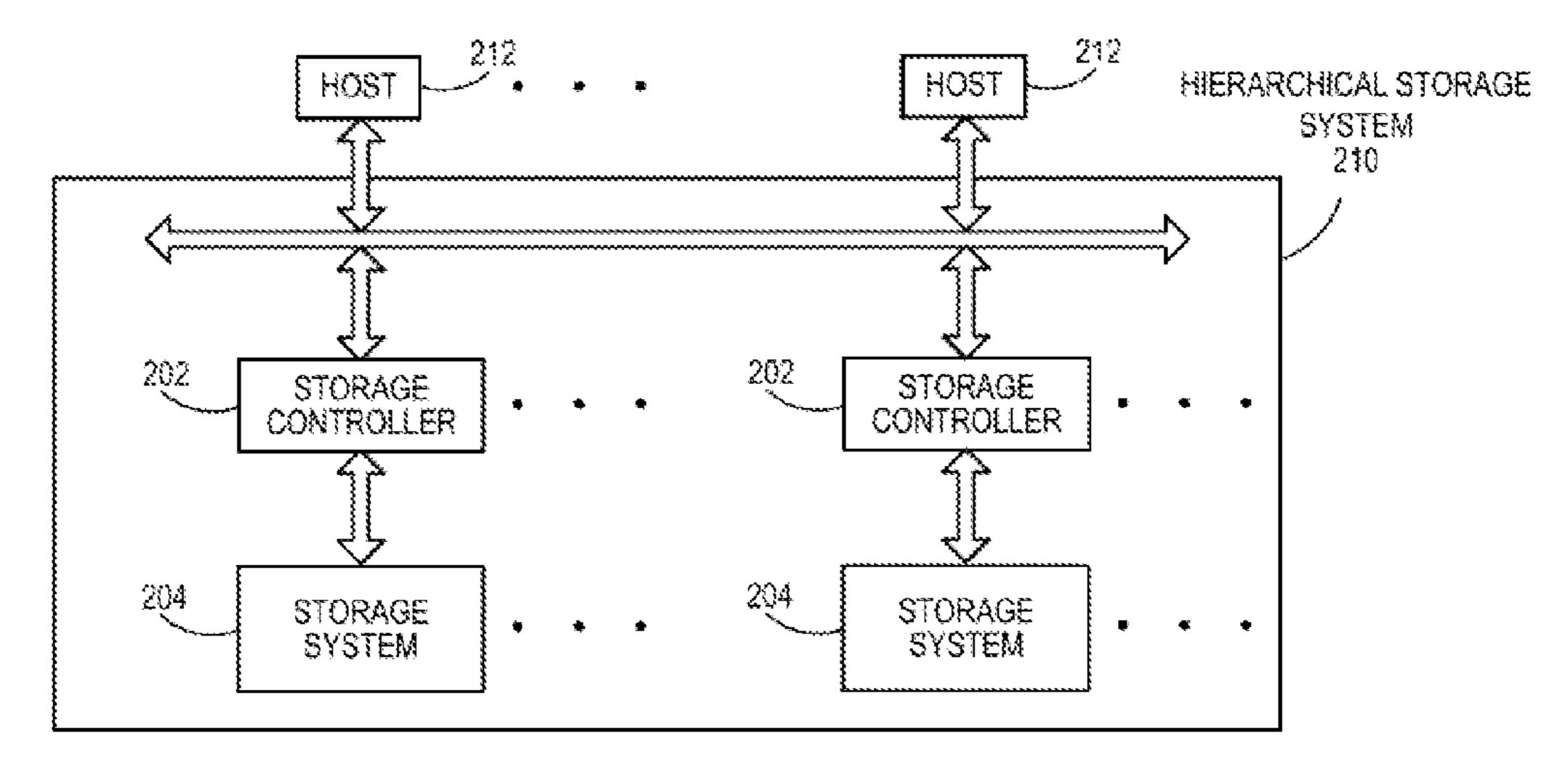

FIG. 1B illustrates a storage module 200 that includes plural non-volatile memory systems 100. As such, storage 15 module 200 may include a storage controller 202 that interfaces with a host and with storage system 204, which includes a plurality of non-volatile memory systems 100. The interface between storage controller 202 and non-volatile memory systems 100 may be a bus interface, such 20 as a serial advanced technology attachment (SATA) or peripheral component interface express (PCIe) interface. Storage module 200, in one embodiment, may be a solid state drive (SSD), such as found in portable computing devices, such as laptop computers, and tablet computers.

FIG. 1C is a block diagram illustrating a hierarchical storage system. A hierarchical storage system 210 includes a plurality of storage controllers 202, each of which control a respective storage system 204. Host systems 212 may access memories within the hierarchical storage system via 30 a bus interface. In one embodiment, the bus interface may be a non-volatile memory express (NVMe) or a fiber channel over Ethernet (FCoE) interface. In one embodiment, the system illustrated in FIG. 1C may be a rack mountable mass storage system that is accessible by multiple host computers, 35 such as would be found in a data center or other location where mass storage is needed.

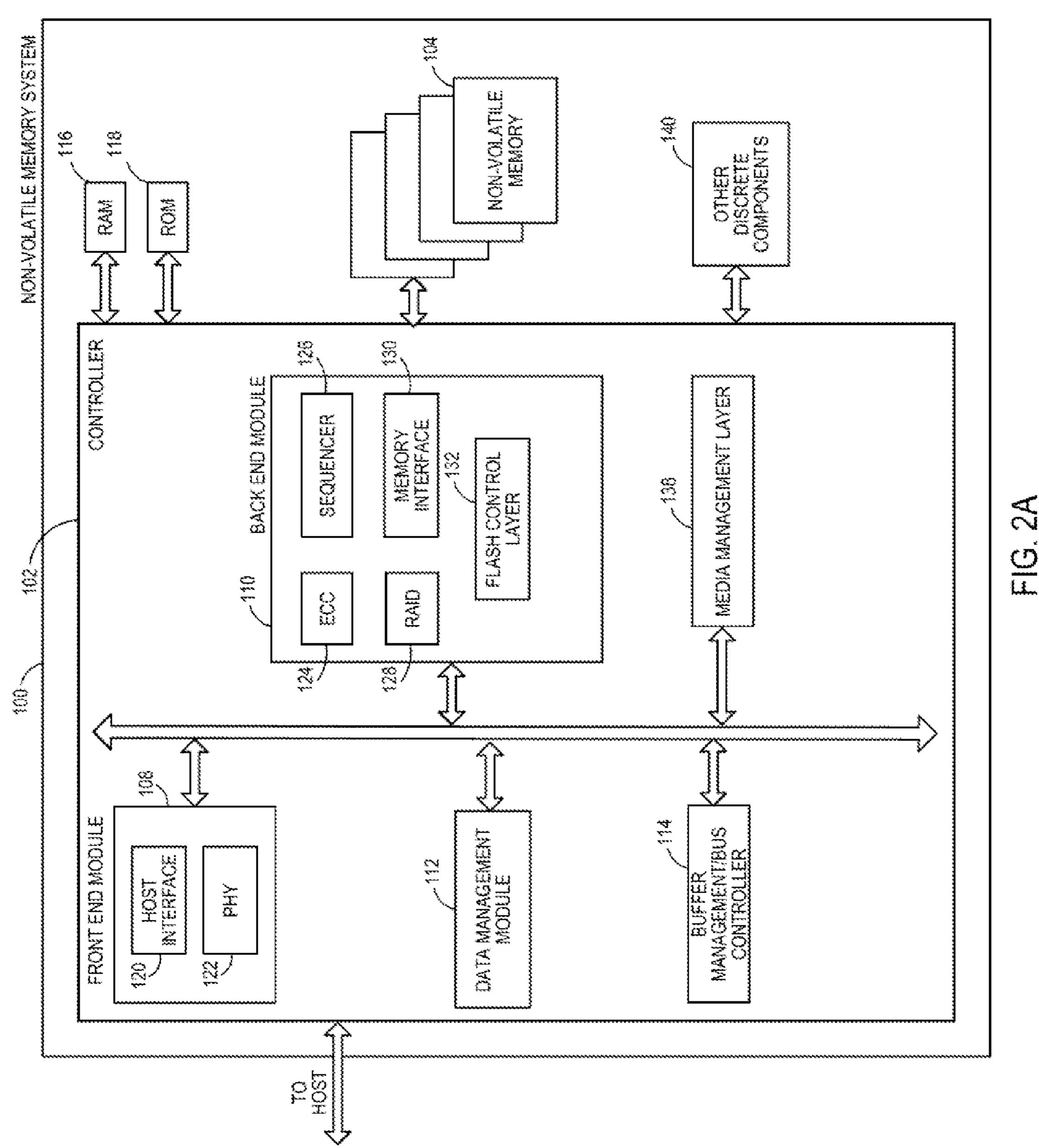

FIG. 2A is a block diagram illustrating exemplary components of controller 102 in more detail. Controller 102 includes a front end module 108 that interfaces with a host, 40 a back end module 110 that interfaces with the one or more non-volatile memory die 104, and various other modules that perform functions which will now be described in detail.

A module may take the form of a packaged functional hardware unit designed for use with other components, a 45 portion of a program code (e.g., software or firmware) executable by a (micro)processor or processing circuitry that usually performs a particular function of related functions, or a self-contained hardware or software component that interfaces with a larger system, for example.

Modules of the controller 102 may include a data management module 112 present on the die of the controller 102. As explained in more detail below in conjunction with FIGS. 5-6 and 17, the data management module 112 may implement the programming and maintenance operations of a 55 bank of non-volatile memory to each non-volatile memory die in the bank. The data management module **112** handles the scheduling of maintenance and host write operations in a schedule cycle for the non-volatile memory such that the schedule cycle balances consumption of space with creation 60 of free space. As described in greater detail below, in embodiments having a non-volatile memory with a plurality of non-volatile memory die, the non-volatile memory die are operated asynchronously and independently such that multiple non-volatile memory die may concurrently have sched- 65 ule cycles balancing consumption and creation of free space in each respective non-volatile memory die.

8

Referring again to modules of the controller 102, a buffer manager/bus controller 114 manages buffers in random access memory (RAM) 116 and controls the internal bus arbitration of controller 102. A read only memory (ROM) 118 stores system boot code. Although illustrated in FIG. 2A as located separately from the controller 102, in other embodiments one or both of the RAM 116 and ROM 118 may be located within the controller. In yet other embodiments, portions of RAM and ROM may be located both within the controller 102 and outside the controller 102. Further, in some implementations, the controller 102, RAM 116, and ROM 118 may be located on separate semiconductor die.

Front end module 108 includes a host interface 120 and a physical layer interface (PHY) 122 that provide the electrical interface with the host or next level storage controller. The choice of the type of host interface 120 can depend on the type of memory being used. Examples of host interfaces 120 include, but are not limited to, SATA, SATA Express, SAS, Fibre Channel, USB, PCIe, and NVMe. The host interface 120 typically facilitates transfer for data, control signals, and timing signals.

Back end module 110 includes an error correction controller (ECC) engine 124 that encodes the data bytes 25 received from the host, and decodes and error corrects the data bytes read from the non-volatile memory. A command sequencer 126 generates command sequences, such as program and erase command sequences, to be transmitted to non-volatile memory die 104. A RAID (Redundant Array of Independent Drives) module 128 manages generation of RAID parity and recovery of failed data. The RAID parity may be used as an additional level of integrity protection for the data being written into the memory device **104**. In some cases, the RAID module 128 may be a part of the ECC engine 124. A memory interface 130 provides the command sequences to non-volatile memory die 104 and receives status information from non-volatile memory die **104**. In one embodiment, memory interface 130 may be a double data rate (DDR) interface, such as a Toggle Mode 200, 400, or **800** interface. A flash control layer **132** controls the overall operation of back end module 110.

Additional components of system 100 illustrated in FIG. 2A include media management layer 138, which performs wear leveling of memory cells of non-volatile memory die 104. System 100 also includes other discrete components 140, such as external electrical interfaces, external RAM, resistors, capacitors, or other components that may interface with controller 102. In alternative embodiments, one or more of the physical layer interface 122, RAID module 128, media management layer 138 and buffer management/bus controller 114 are optional components that are not necessary in the controller 102.

FIG. 2B is a block diagram illustrating exemplary components of non-volatile memory die 104 in more detail. Non-volatile memory die 104 includes peripheral circuitry 141 and non-volatile memory array 142. Non-volatile memory array 142 includes the non-volatile memory cells used to store data. The non-volatile memory cells may be any suitable non-volatile memory cells, including NAND flash memory cells and/or NOR flash memory cells in a two dimensional and/or three dimensional configuration. Peripheral circuitry 141 includes a state machine 152 that provides status information to controller 102. Non-volatile memory die 104 further includes a data cache 156 that caches data. The data cache comprises sets of latches 157 for each bit of data in a memory page of the non-volatile memory array 142. Thus, each set of latches 157 is a page in width and a

plurality of sets of latches 157 may be included in the data cache 156. The controller 102 may be implemented in a single integrated circuit chip and may communicate with the different layers of memory in the non-volatile memory die 104 over one or more command channels. Controller executable code for implementing memory management instructions such as described herein may be stored in the non-volatile flash memory.

The non-volatile flash memory array 142 may be arranged in blocks of memory cells. A block of memory cells is the 10 unit of erase, i.e., the smallest number of memory cells that are physically erasable together. For increased parallelism, however, the blocks may be operated in larger metablock units. One block from each of at least two planes of memory cells may be logically linked together to form a metablock. 15 Referring to FIG. 3, a conceptual illustration of a representative flash memory cell array is shown. Four planes or sub-arrays 300, 302, 304 and 306 of memory cells may be on a single integrated memory cell chip, on two chips (two of the planes on each chip) or on four separate chips. The 20 specific arrangement is not important to the discussion below and other numbers of planes may exist in a system. The planes are individually divided into blocks of memory cells shown in FIG. 3 by rectangles, such as blocks 308, 310, 312 and 314, located in respective planes 300, 302, 304 and 25 306. There may be dozens or hundreds of blocks in each plane. Blocks may be logically linked together to form a metablock that may be erased as a single unit. For example, blocks 308, 310, 312 and 314 may form a first metablock **316**. The blocks used to form a metablock need not be 30 restricted to the same relative locations within their respective planes, as is shown in the second metablock 318 made up of blocks 320, 322, 324 and 326.

The individual blocks are in turn divided for operational purposes into pages of memory cells, as illustrated in FIG. 35 4. The memory cells of each of blocks 308, 310, 312, and **314**, for example, are each divided into eight pages P0-P7. Alternately, there may be 16, 32 or more pages of memory cells within each block. A page is the unit of data programming within a block, containing the minimum amount of 40 data that are programmed at one time. The minimum unit of data that can be read at one time may be less than a page. A metapage 400 is illustrated in FIG. 4 as formed of one physical page for each of the four blocks 308, 310, 312 and **314**. The metapage **400** includes the page P2 in each of the 45 four blocks but the pages of a metapage need not necessarily have the same relative position within each of the blocks. A metapage is the maximum unit of programming. The blocks disclosed in FIGS. 3-4 are referred to herein as physical blocks because they relate to groups of physical memory 50 cells as discussed above. As used herein, a logical block is a virtual unit of address space defined to have the same size as a physical block. Each logical block includes a range of logical block addresses (LBAs) that are associated with data received from a host. The LBAs are then mapped to one or 55 more physical blocks in the non-volatile memory system 100 where the data is physically stored.

Referring now to FIG. 5A, an embodiment of the non-volatile memory system 100 of FIG. 1 is shown having non-volatile memory 501 consisting of one or more non-volatile memory die 104, where each die, or group of die that are managed together as an independent managed set (also referred to herein as a metadie), includes a common pool 503 of free blocks of non-volatile memory cells programmable into any of two or more layers 502, 504 in the 65 non-volatile memory 501. Each layer 502, 504, also referred to herein as a die layer, includes only blocks of memory cells

**10**

configured with a same bit per cell capacity and each layer having a different bit-per-cell capacity than the other layer.

Also, as explained in greater detail with respect to FIGS. 5B and 5C below, the non-volatile memory 501 of the general example of FIG. 5A may be arranged as individually managed non-volatile memory die 104, a whole number set of non-volatile die that are managed together, or a combination of the two. Each layer of a non-volatile memory die (FIG. 5B) or an independently managed set of non-volatile memory die (FIG. 5C) has memory cells of a different bit per cell capacity than each other layer in the non-volatile memory die or independently managed set.

For example, a first memory layer 502 may be configured as binary layer having blocks of non-volatile memory cells with a single bit per cell capacity, also referred to herein as a single level cell (SLC) or X1 layer. A second memory layer 504 may be configured with blocks of non-volatile memory cells having more than one bit per cell storage capacity, sometimes referred to as multi-level cell (MLC) flash memory. In one implementation the MLC memory layer 504 may be a two bit per cell memory, also referred to herein as X2 memory, while in other embodiments the MLC memory layer 504 may be three bit per cell memory, also referred to herein as X3 memory. Other combinations of bit per cell capacity layers are also contemplated. More than two layers are also contemplated in other implementations.

In one implementation, the separate layers 502, 504 are not fixed in size and may be dynamically resized through block reclaim operations and retasking free blocks from the free block pool 503 into either of the layers at the appropriate bit per cell capacity utilized by each respective layer. Alternatively, the layers may be fixed in size and each have a separate free block pool 503 exclusively associated with that particular layer. Also, as used herein, the die layers 502, 504 refer to groups of blocks having memory cells configured in a particular bit-per-cell capacity and do not require any particular physical arrangement of the cells or layers with respect to one another.

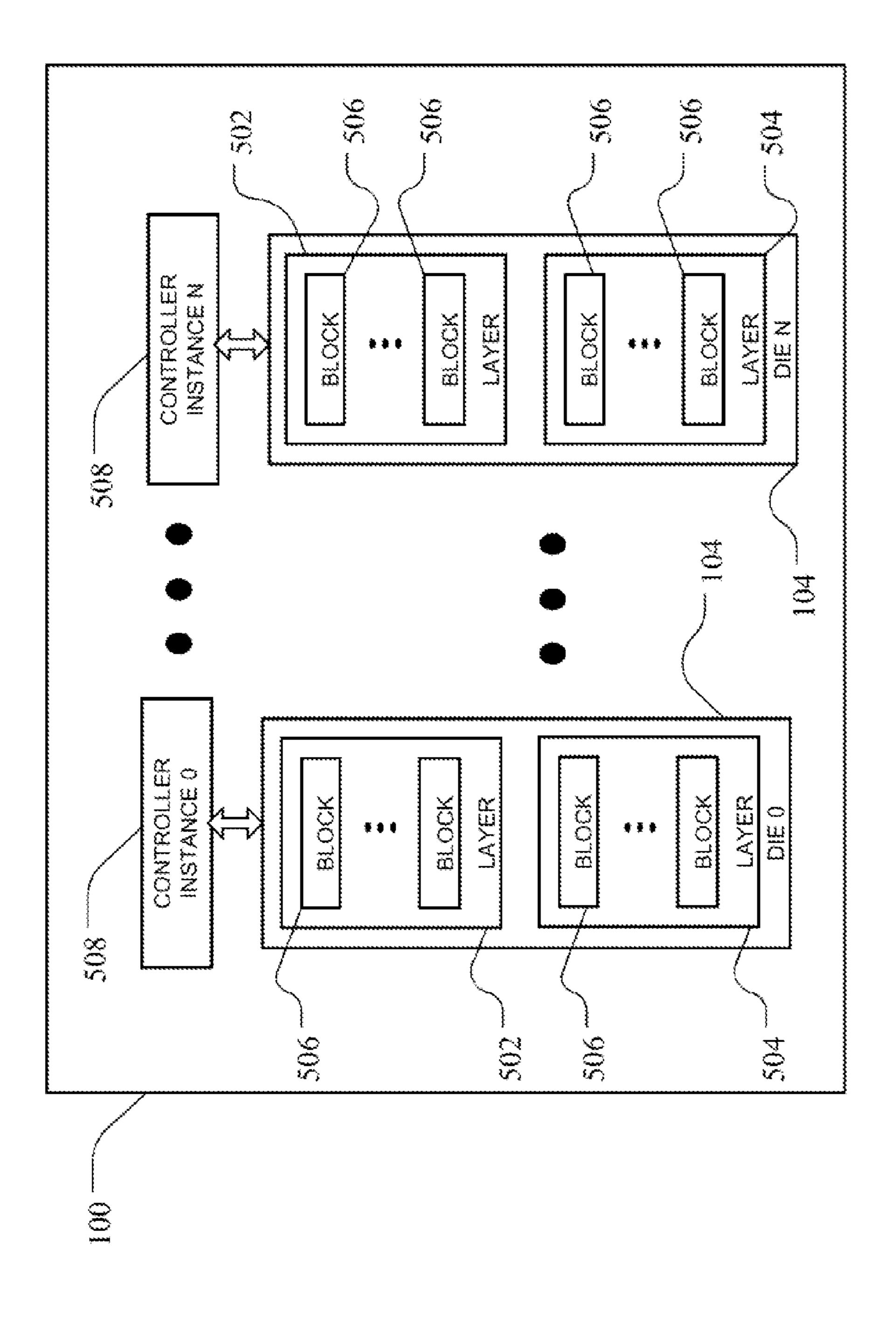

Referring to FIG. 5B, an example non-volatile memory 501 in the non-volatile memory system 100 is shown having each die 104 independently managed by its own controller instance 508. In this embodiment, each layer 502, 504 is defined by a blocks 506 of a particular bit per cell capacity that are within the single die 104. Each die 104 may be independently and asynchronously managed by a separate instance 508 of the controller 102 of the non-volatile memory system 100. A controller 508 instance may be a separate thread of a single controller 102, or a separate hardware of firmware implementation. Also, each nonvolatile memory die in FIG. 5B handles its own multiple layers independently of the layers in each other die. As used herein, the term die refers to the set of non-volatile memory cells, and associated circuitry for managing the physical operation of those non-volatile memory cells, that are formed on a single semiconductor substrate.

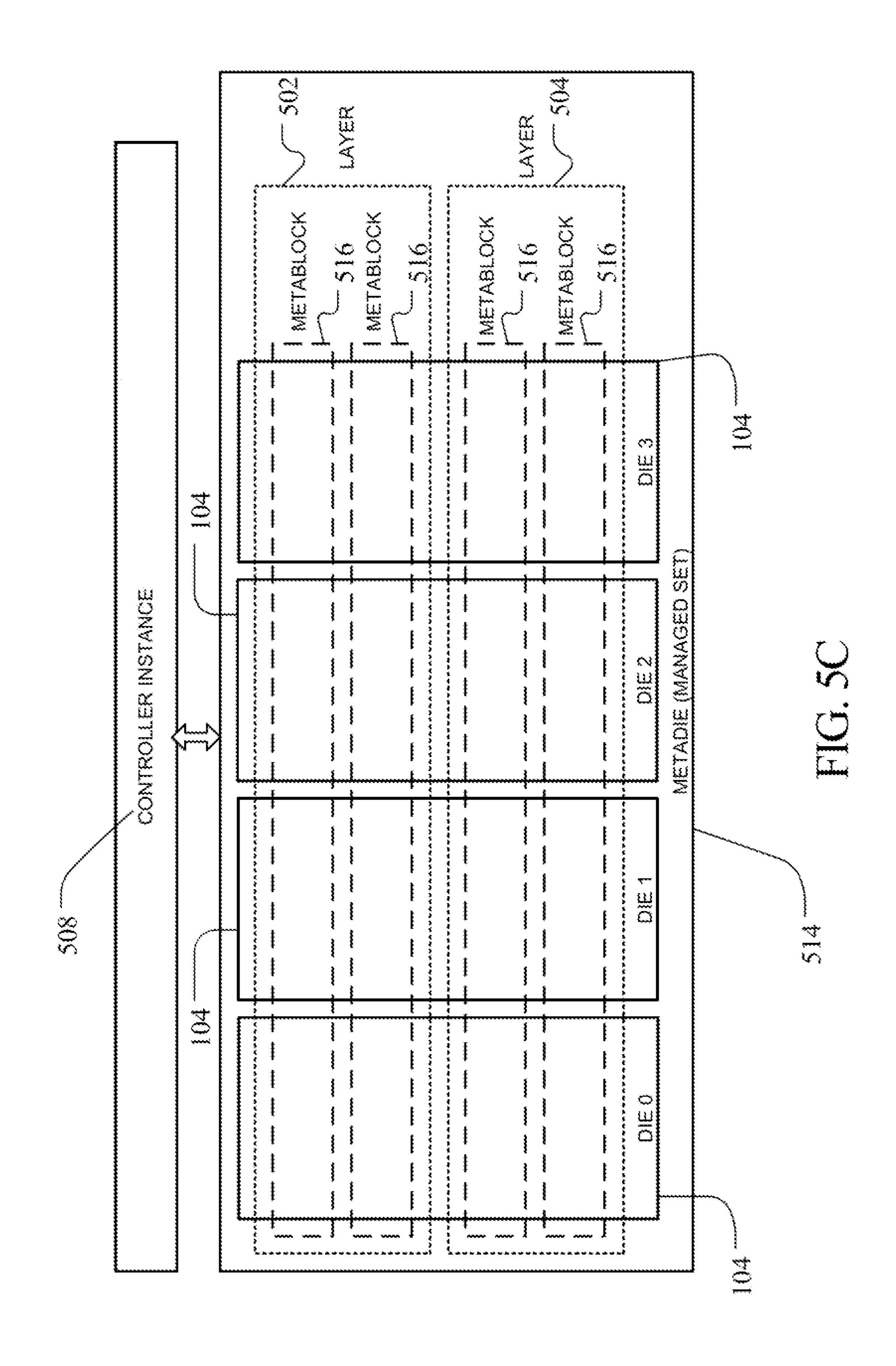

Referring to FIG. 5C, in other embodiments the non-volatile memory is arranged in one or more independently managed sets of non-volatile memory die, where each managed set, also referred to as a metadie, is a whole number of non-volatile memory die 104 being managed as a single unit by a separate controller instance 508. For an independently managed set 514 of non-volatile memory die, the memory layers 502, 504 may be formed across the multiple separate non-volatile memory die 104 in the managed set 514. Thus, in contrast to the layers in the individually managed die of FIG. 5B that are made up of blocks 506 completely contained within each independently managed

die 104, the layers 502 and 504 in the embodiment of FIG. 5C are made up of metablocks 516 that include at least one block on each of the non-volatile memory die in the independently managed set 514 of die (or metadie).

A single independently managed set of die is shown in 5 FIG. 5C, but multiple independently managed sets could be included in a single non-volatile memory system 100. Additionally, a mix of single die with multiple layers contained within that die and independently managed sets of two or more non-volatile memory die with multiple layers across that managed set are also contemplated in a single nonvolatile memory system 100. In embodiments with multiple independently managed sets of non-volatile memory die, the layers in each of the independently managed sets are 15 handled separately from the layers in any other independently managed set. Although specific bit per cell configurations of SLC and MLC are illustrated in FIG. 5A, other combinations are contemplated where the first memory layer has a lower bit per cell configuration than the second flash 20 memory layer. If more than two layers are present in a die or metadie, then each additional layer, in turn, may have a higher bit per cell configuration than the prior memory layer.

Referring again to the generic representation in FIG. 5A of the different single die and multiple die layer structures in 25 FIGS. 5B and 5C, one or more mapping tables 510, such as logical-to-physical mapping tables, storage address tables and so on, may be stored in non-volatile memory cells of any of the layers 502, 504 of the non-volatile memory 501. Additionally, a memory layer distribution data structure 512 30 (such as a table) or a memory layer distribution algorithm representing a predetermined desired physical capacity and overprovisioning for each memory layer at different storage system fullness levels, may be stored in one or more of the layers 502, 504.

It is contemplated that the mapping tables 510 and memory layer distribution data structure **512** may be specific to each non-volatile memory die 104 or metadie 514. Additionally, the free block pool 503 present in each die 104 or metadie 514 may be a single pool such that any block 40 from the free block pool may be assigned to a particular layer, reconfiguring the free block as necessary for use at the appropriate bit-per-cell capacity of the destination layer. In embodiments where one or more portions of the non-volatile memory in the non-volatile memory system 100 are orga- 45 nized as a metadie **514** as in FIG. **5**C, then the free block pool 503 in each die of that managed set would contribute to a metablock, comprising at least one block in each of the die in the managed set, that would be configured to the bit-per-cell configuration of the destination layer. Alterna- 50 tively, each die or metadie may have a different free block pools for each layer.

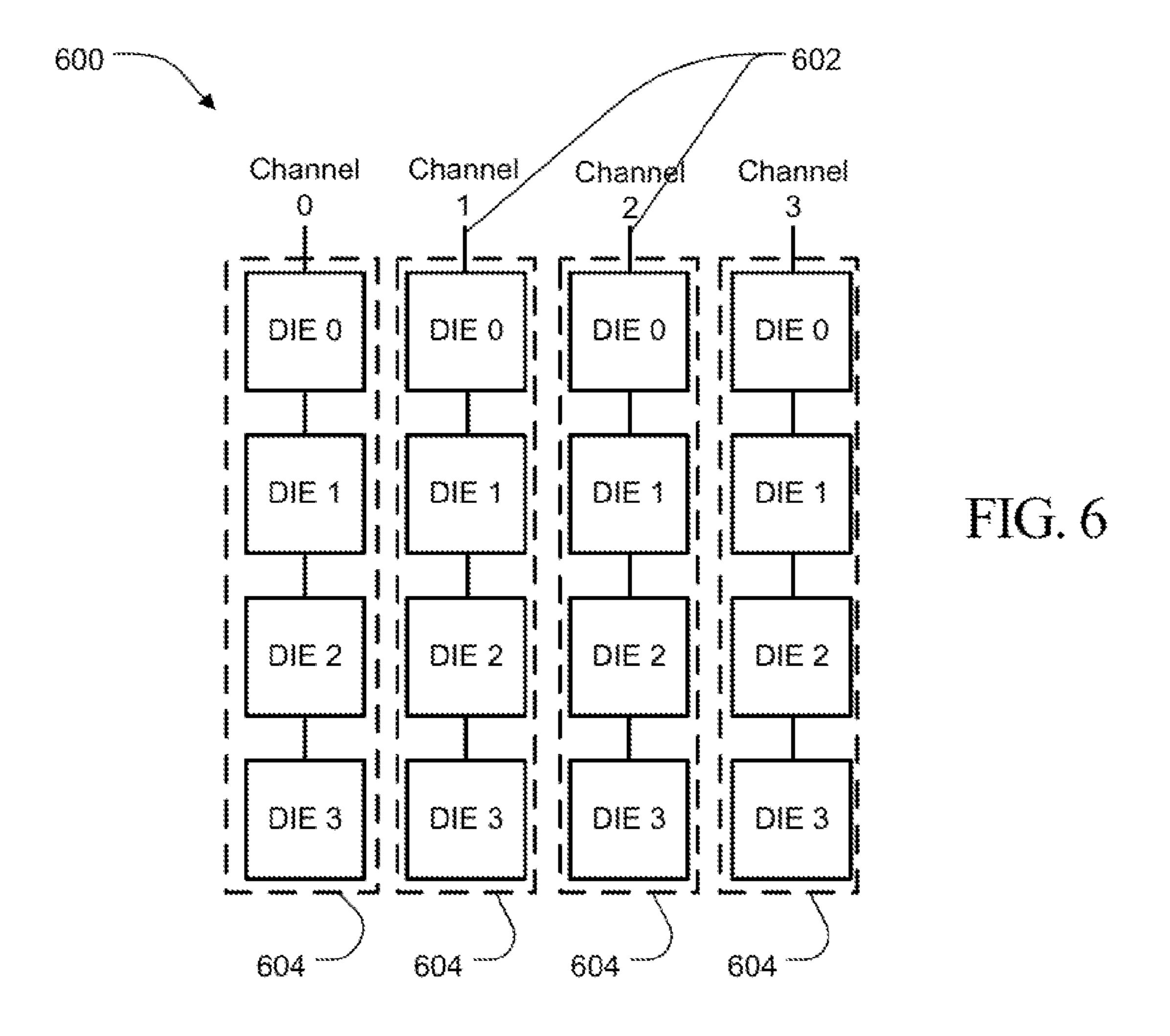

Although a small group of individually managed non-volatile memory die 104, and an individual metadie 514, are shown in FIGS. 5B and 5C, arrays of memory die are 55 contemplated such as shown in FIG. 6. The array 600 of non-volatile memory die may be made up of non-volatile memory die organized on separate channels 602, where all the die on a channel 602 comprises a memory bank 604, such that four memory banks are illustrated in FIG. 6. 60 Alternatively, die in a memory bank may also be located across multiple memory channels. Each channel 602 may be associated with a separate controller 102 or all channels may be associated with a single controller 102. With reference to FIG. 6, the die (DIE 0-DIE 3) on each channel 602 may 65 represent either individual non-volatile memory die 104 or metadie 514.

12

Asynchronous Management

In order to increase performance of a memory system, the memory system may operate each of the non-volatile memory die or metadie asynchronously and independently of each other non-volatile memory die or metadie. Referring to FIG. 6, if each channel 602 is managed as a separate bank 604 and each channel has a separate controller instance 508 (FIG. 5B), the controller instance may handle data programming on a die-by-die level, including selection of the best die on the single channel for a particular operation based on its availability.

In a multiple controller embodiment, such as shown in FIG. 5B, the controller instances 508 may use any of a number of address translation algorithms for managing movement of data to, within and between die layers as set forth below. Each controller instance may be assigned a particular LBA address range for host data and manage data in that range in the die or metadie associated with that controller. In implementations of a memory system having a single controller, the controller manages all die on one or many channels 602, the controller may be the same type of controller with the same algorithms as a multi-controller embodiment. The single controller embodiment simply manages the full address mapping for die and channel for all data in the non-volatile memory array 600 rather than receiving data in a specific LBA address range associated with a particular controller/channel as discussed with respect to the multi-controller embodiments having a separate controller per channel.

The data management module 112 in the controller 102 may include an asynchronous die algorithm, in which write transactions throughout the system 100 relate to the programming parallelism of one die, designated a die-page. Metablocks are formed across planes within a single die 104. Multiple die can operate concurrently on contiguous operations, or can operate asynchronously with each performing unrelated operations.

Each write transaction for data from a host may be issued to the relevant die layer 502, 504 in any die 104. The die that will allow highest data throughput to be maintained may be selected, based on status information about the die layer. The asynchronous die algorithm is designed to provide reduced latency for execution of host commands and improved performance with workloads having irregular I/O size or mixed read/write characteristics. Unlike controllers configured for synchronous operations that utilize metablocks spanning multiple die, asynchronous die operations can allow all good metablocks within each die to be used and can make use of the full physical overhead available to it, thereby maximizing the performance of the memory system.

For ease of illustration, and to avoid repetition, the features described below are generally explained in the context of the multiple controller arrangement of FIGS. 5B and 6, where each controller instance 508 manages a separate die or bank of die independently of each other die or bank of die. It should be understood, however, that all of the features disclosed herein are equally applicable to the single controller embodiment that handles all banks 604.

In one embodiment of the present invention, each controller instance 508 includes an asynchronous die algorithm, in which data programming parallelism and write transactions throughout the system 100 are managed in units of the maximum programming parallelism achievable within one die, which is typically 32 KB in a 2-plane die. Each controller instance 508 is associated with die on only one channel 602, rather than die on separate channels as in a synchronous architecture. In this manner, multiple die can operate fully in parallel when required, or can operate

asynchronously with each performing unrelated operations. Additionally, the asynchronous operation permits the controller instance for each set of die it manages on the same channel 602 (bank 604) to select the die that is best suited for receiving the data, for example the die having the shortest queue of data to be written. In a single controller embodiment, the controller 102 would manage all die an all channels 602 and can select any die that is best suited for receiving data.

Asynchronous operation of each die associated with a 10 given controller allows all good blocks within each die to be active. The performance of each die may be maximized by making use of the full physical overhead available to it, thereby maximizing the performance of the memory system. The die selection criteria implemented by the asynchronous 15 die algorithm may include the controller selecting a die only if the die's status information indicates that the required interleaving of maintenance copy operations with host data program operations of the same class (e.g. data type of random or sequential) as the pending transaction has been 20 met. Other criteria, which may be used alone or in combination, may include selecting a die only if the number of outstanding transactions for the target class (e.g. the queue for random write transactions) does not exceed a specified limit; selecting the available die with the lowest number of 25 outstanding transactions; and/or selecting the available die with the lowest logical fullness.

While a specific controller, in non-volatile memory system 100 having multiple controller instances, manages data with LBAs only within a specific subset of host LBA address 30 space, there is no correlation between LBA and die number within a controller instance. Similarly, there is no correlation between the die numbers used by successive controllers to sequentially program successive LBA metapages within a controllers. Although each controller independently manages its own die on one particular controller channel in one embodiment of an asynchronous architecture, the asynchronous die algorithm can also achieve full parallelism across controllers for data transfer and NAND command execution. 40 A NAND read or program operation on an LBA metapage can be executed in each of the controllers, with fully synchronous data transfer and access operations. This allows fully synchronous execution of read and program operations relating to an LBA address stripe spanning all controllers, 45 such as occur in sequential read and write modes of operation.

Read and program operations relating to two successive LBA stripes spanning an LBA range associated with a controller implementing asynchronous die management can 50 be executed concurrently in two die on the same channel **602**, but not fully in parallel. Data transfers to or from the two die is typically serialized, because they are sharing the same channel. The read or program operations in the two die may therefore be overlapped.

The type of inputs received by an asynchronous die algorithm running in each of the controllers may include read, write and trim commands. In embodiments where the asynchronous die algorithm is used in a multi die layer memory system having multiple partitions per die layer, the 60 write commands received may be further divided into write commands for different data types, such as the random and sequential data types described above. In one embodiment, the execution of certain transactions may be ordered such that read transactions are immediately processed, while 65 write and trim commands are processed in the order received. In embodiments where a die metapage is 32 KB,

**14**

a read transaction may be for any multiple of 2 KB up to a maximum of one die metapage, write transactions are one metapage and a trim transaction has a data payload length of one metapage.

The controller 102 may implement an address translation algorithm within each non-volatile memory die (independently managed as in FIG. 5B), or metadie (set of non-volatile memory die managed as a single unit as in FIG. 5C) to enhance the efficiency of data transfer and memory usage. Any of a number of known memory management techniques may be used to implement the storage system described herein. One advantage of some address translation algorithms is the ability to increase performance of storage systems in random write applications, random write applications being characterized by the need to write short bursts of data to unrelated areas in the logical block address (LBA) address space of a device, that may be experienced in solid state disk (SSD) applications in personal computers.

In one implementation of an address translation algorithm, host data is mapped from a first logical address assigned by the host (also known as a host logical block address) to blocks of contiguous logical addresses in a second logical address space (also known as a virtual logical block address). As data associated with fully programmed blocks of addresses is made obsolete, a data relocation procedure is initiated where the controller selects a previously fully programmed block in a die having the least amount of valid data, or having less than a threshold amount of valid data, and relocates the valid data in those blocks to free up those blocks for use in writing more data. The relocated data is contiguously written to a relocation block in the same die in the order it occurred in the source block needing data relocation regardless of the logical address assigned by the host. In this manner, overhead may be stripe of LBAs spanning the separate die managed by two 35 reduced by not purposely consolidating logical address runs assigned by the host (as in typical garbage collection).

One or more storage address tables (SAT) may be used to track the mapping between the host logical address assigned by the host and the virtual logical address assigned by the storage system and subsequent changes in the mapping due to subsequent relocation. Similarly, storage address tables may be used to track mapping between the virtual logical address assigned by the storage system and the physical address at a die where data is actually stored.

Concurrently with accepting data from the host, the controller reclaims blocks in a maintenance operation by copying valid data from previously programmed blocks having both valid and obsolete data and then recycling the blocks from which all the valid data was copied. This block reclaiming procedure may be in the form of a standard garbage collection technique where groups of data are kept together and consolidated as new data in the same address run is received, or may be a relocation procedure where data is not consolidated into the same address groupings.

Data Management Module

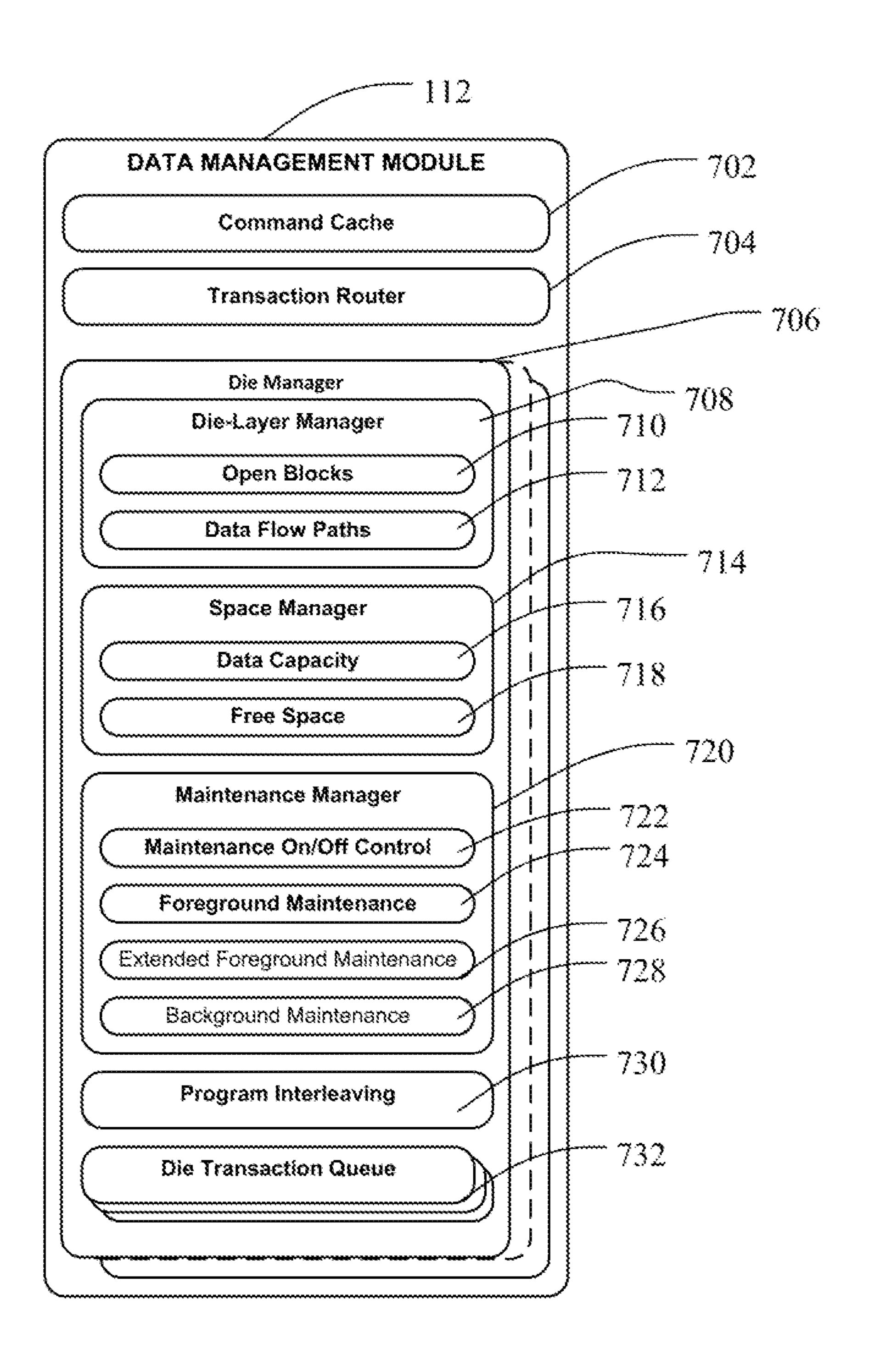

Referring to FIG. 7, a more detailed illustration of the data management module 112 of FIG. 2A is shown. The data management module may be configured as firmware, hardware, or a combination of the two to execute data management algorithms. As noted previously, the data management module 112 may be part of or outside of the media management layer 138 in the controller. The data management module includes a command cache 702 containing pending host commands from the command manager layer. A transaction router 704 is configured to route transactions to a selected non-volatile memory die in the bank. In one implementation, a separate die manager 706 exists for each

non-volatile memory die being managed by the data management module 112. For example, if one data management module 112 is associated with a bank 604 such as the example of FIG. 6 where the bank is configured as the column of four non-volatile memory die 104 associated with 5 channel 0, then four instances of the die manager 706, one for each die in the bank 604, would be present in the data management module 112 for channel 0.

Within each die manager 706, a die layer manager 708 manages the data flows within and between die layers for a 10 particular non-volatile memory die. The die layer manager 708 may include an open block list 710 identifying any open write or maintenance blocks in the die layer and a list of possible data flow paths 712. The types of data flow paths 712 supported may vary based on the type of non-volatile 15 memory die and example data flow paths 712 are provided for embodiments of different non-volatile memory die in FIGS. 12 and 13 below. A space manager 714 in the die manager 706 includes information on the data capacity 716 and free space 718 available in each die layer of the die 20 associated with the die manager 706. The free space 718 may be in the form of a free block list for each die layer in the non-volatile memory die being managed by the die manager 706. A maintenance manager 720 implements the maintenance techniques discussed herein. The maintenance 25 manager 720 may include an on/off control 722, a foreground maintenance algorithm 724, an extended foreground maintenance algorithm 726 and a background maintenance algorithm **828** that each manage maintenance operations for the creation of free space. A program interleaving module 30 730 in each die manager 706 controls the interleaving of host data writes and maintenance operation writes in the schedule cycles discussed further herein.

A die transaction queue 732 buffers host read, program sequencer layer 126 of the back end module. The queue 732 thus includes lists of pending host commands that are awaiting execution on each non-volatile memory die and may be used as part of the non-volatile memory die selection process. By accessing the queue in each bank of the memory 40 system to assist in selecting a die for an operation, the data management module may optimize utilization of each die. As noted above, the die transaction queue 732 for each die managed by a particular controller may be used in the die selection process for a given schedule cycle.

Again, a separate instance of a data management module 112 may exist for each memory bank in the system, where a memory bank 604 comprises a subset of the total number of physical die in a non-volatile memory system 100 (e.g. all die on a whole number of channels). The data management 50 module 112 may map a predefined subset of logical address space (a logical bank) to a predefined subset of physical address space (a physical bank). Alternatively, a single instance of the data management module 112 may manage all die in the system 100, which is equivalent to there being 55 only a single bank, both logical and physical.

The data management module 112 maps a unique logical address space to a unique physical address space comprising an integral number of die. It is desirable to produce uniformity of response times to commands within any host work- 60 load while avoiding idle time in non-volatile memory die. The data management algorithm executed by the data management module 112 utilizes the non-volatile memory die asynchronously and independently, as discussed above, to increase the utilization of non-volatile memory die and to 65 assist with overall performance of the non-volatile memory system. In addition, as set forth below, the data management

**16**

module 112 incorporates the use of schedule cycles to balance consumption and creation of free space in each die in an effort to improve uniformity of response times to a host.

Maintenance in a non-volatile memory may consist of 1) operations to re-program valid data from source blocks containing obsolete data to destination blocks, in order to recover usable free space previously occupied by the obsolete data; and 2) operations to manage non-volatile memory characteristics (for example NAND flash memory characteristics), such as wear levelling and read scrub operations. Maintenance operations may also be performed on control data structures such as any mapping tables used in the memory system.

In one implementation, the data management module may generate a schedule for maintenance operations to be interleaved with host write operations for each individual die. The need for maintenance may be determined independently in each die layer, when the die layer must import data and its available free space is below a threshold value. Host data write operations are interleaved with foreground maintenance operations to provide better uniformity of response times to host data write transactions, where foreground maintenance operations are defined herein as those maintenance operations that are implemented when there are pending host commands.

In one implementation, the interleave ratio for a schedule cycle is defined to balance the consumption of free space by host data write operations with the creation of net free space by maintenance operations. The schedule cycle defined herein is based on freeing a selected source block by moving the valid data from the selected source block to a relocation block and then only allowing an amount of host data to be written to a host write block up to the amount of obsolete and erase transactions for execution in the low level 35 data that was in the selected source block. In other words, a schedule cycle is completed when the valid data of a selected source block has been moved. During the schedule cycle, an amount of host data up to the amount of obsolete data that existed in the selected source block may be written so that there is a creation of one free block (the selected source block after the valid data is moved) and consumption of no more than one block's worth of capacity (the sum of the valid data moved and the host data accepted) in any given schedule cycle.

With respect to a multi-layer non-volatile memory die, a schedule cycle is a schedule of operations which allows data to cascade between die layers or to be relocated within a die layer, as a consequence of host data being imported by the first of the die layers. More specifically, a maintenance operation in a die layer may be a relocation operation, in which all valid data in a selected relocation source block is re-programmed in a relocation destination block within the same die layer, or a folding operation, in which all valid data from a folding source block is re-programmed into a folding destination block in a different die layer.

Within a given schedule cycle, a non-volatile memory die operates to achieve an overall required interleave ratio between host program operations and maintenance operations in zero, one or two die layers. A new schedule cycle is started whenever the source block for data being programmed during a maintenance operation no longer contains valid data, thus the selection of operations is made on a source block by source block basis.

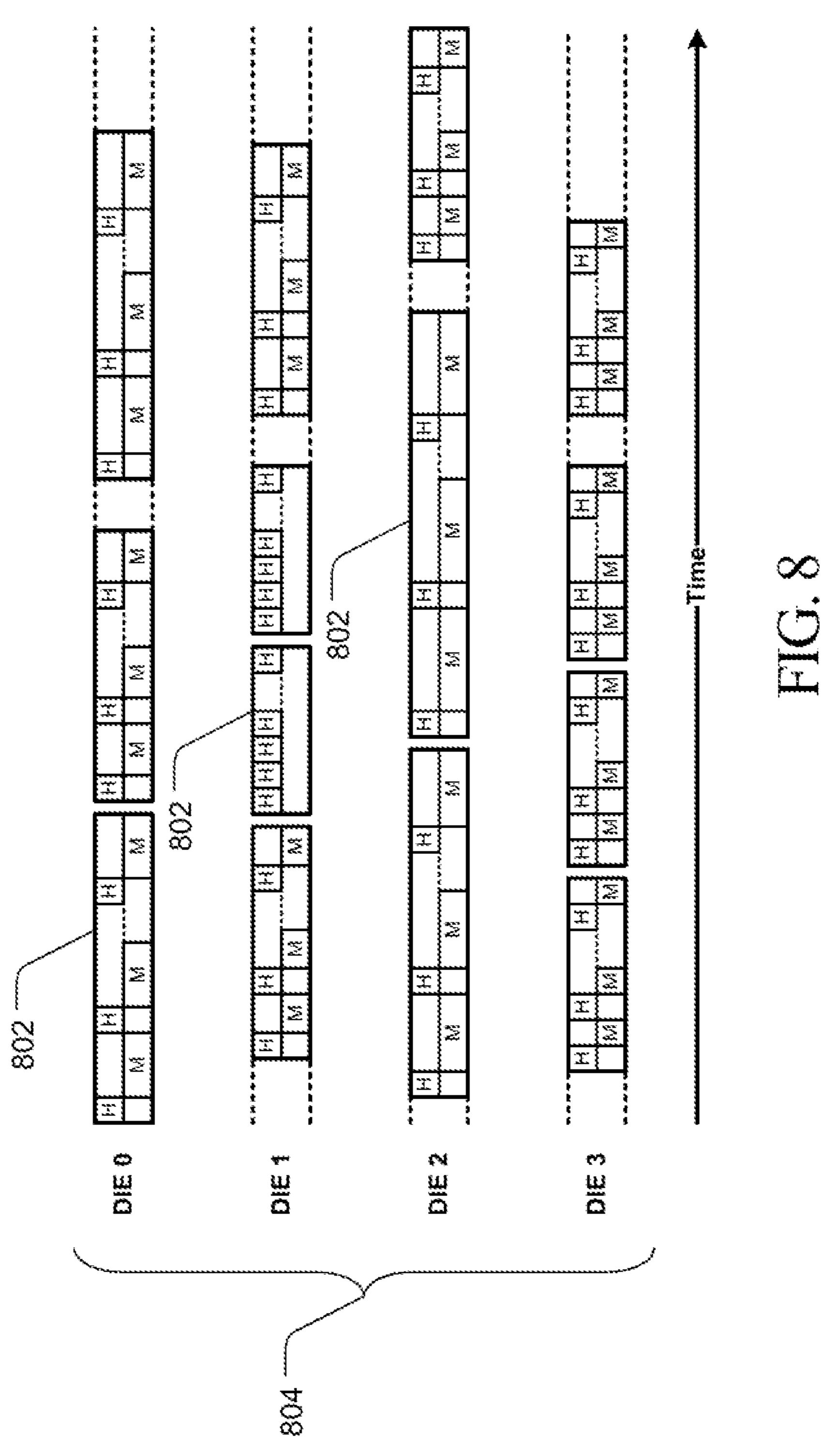

An example of one possible group of schedule cycles for multiple asynchronously operating non-volatile memory die within one bank are illustrated in FIG. 8. FIG. 8 shows an example of the timing of host operations and maintenance

operations for a 4 die bank **804** similar to bank **604** in FIG. **6**. Each of Die 0 through Die 3 is being operated asynchronously in this example, where the time axis progresses from left to right. Each schedule cycle **802** is separately calculated for each non-volatile memory die based on the selected 5 source block for maintenance in that particular die as described in greater detail below. The die manager 706 of the data management module 112 managing the bank 804, for each die in the bank, interleaves host data writes (H), and maintenance operations (M) such as relocation of valid data 10 from a selected source block in the die to achieve the overall required interleave ratio determined for each die at the beginning of each schedule cycle. Thus, as illustrated in FIG. 8, the interleave ratio of host writes H to maintenance operations M for each schedule cycle **802** will change within 15 a die or between each die depending on the source block selected for maintenance.

Trigger for a Schedule Cycle